Изобретение относится к вычислительной технике и может-быть использовано в системах передачи и обработки дискретной информации.

Известно устройство кодека сверточного кода с алгоритмом декодирования Витер- би. содержащее на передающей стороне регистр, два сумматора по модулю два и переключающее устройство, на приемной стороне - синхронизатор, устройство вычисления метрики, устройство обновления, сравнения и хранения метрик путей, устройство обновления и хранения информационных последовательностей, выходное решающее устройство, устройство управления и тактирования 1

Недостатком указанного устройства является низкая его помехоустойчивость при допустимой аппаратурной сложности.

Известно также устройство кодека кода Рида-Маллера первого порядка, содержащее на передающей стороне блок задержки, первый - k-й информационные и

тактовые входы которого являются одноименными входами передающей стороны (k- разрядность входного информационного слова) и первый и второй блоки суммирования по модулю два, на приемной стороне - первый декодер кода Рида-Маллера первого порядка (РМ1), первый блок амплитудных детекторов и первый вычислитель максимума 2.

Недостатком этого устройства является низкая помехоустойчивость передачи информации.

Цель изобретения повышение помехоустойчивости передачи информации.

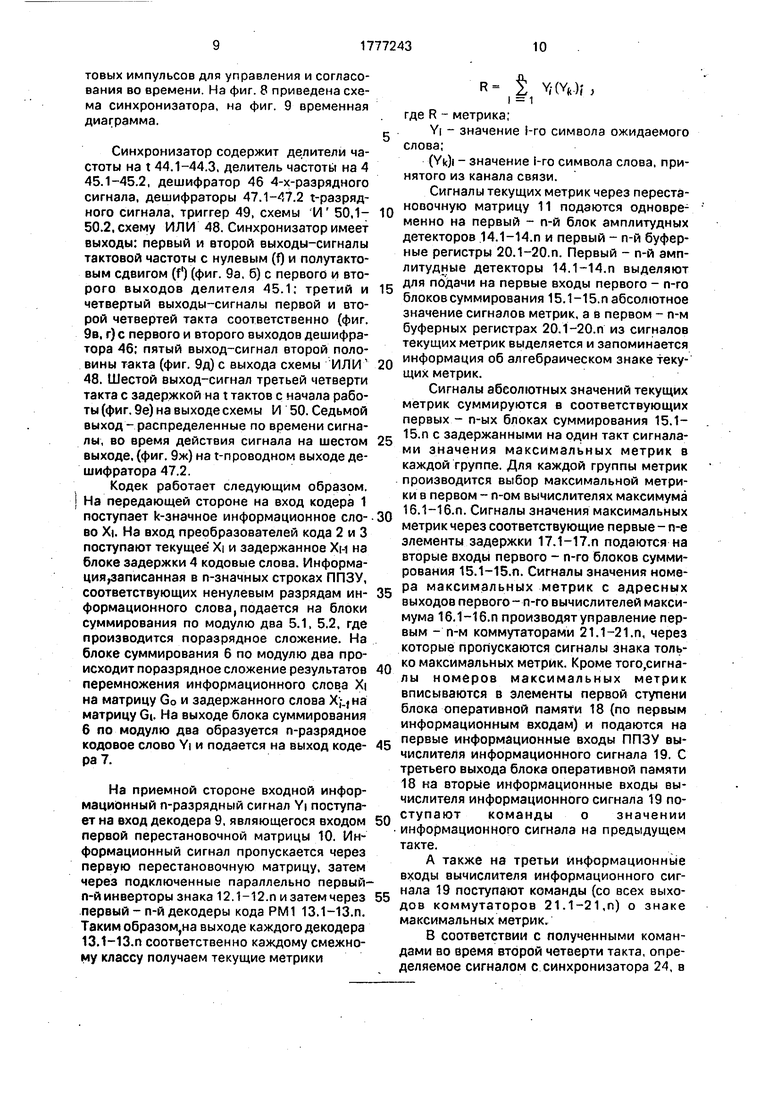

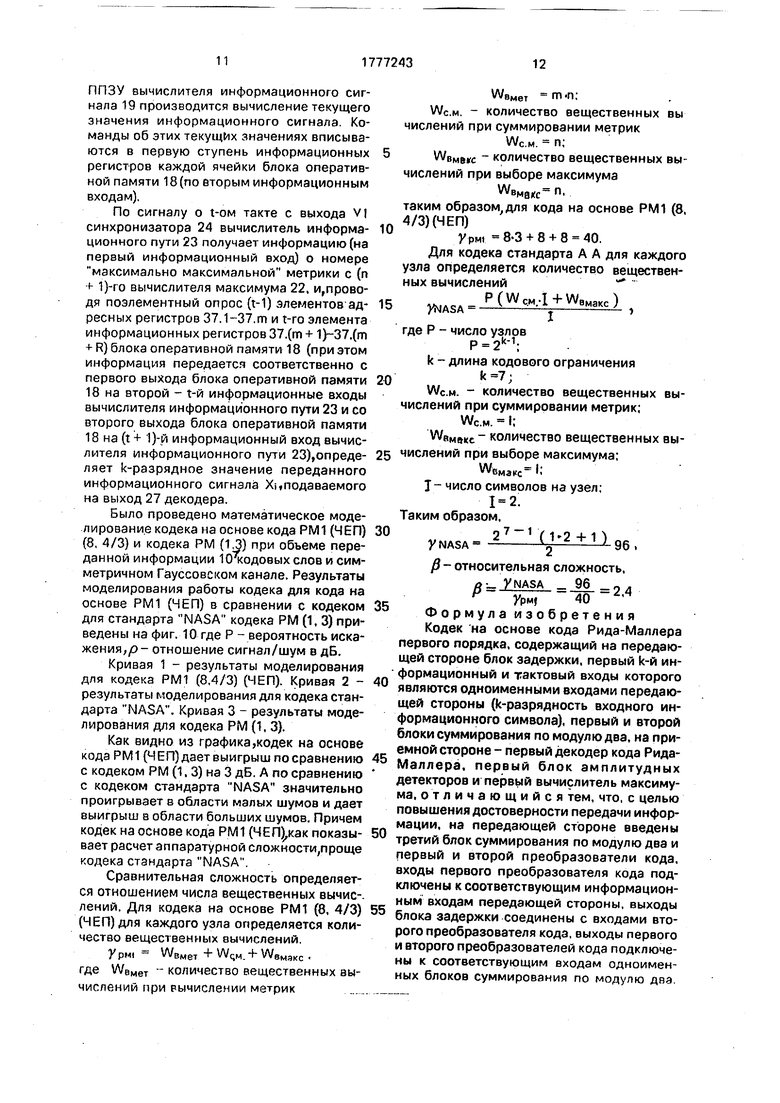

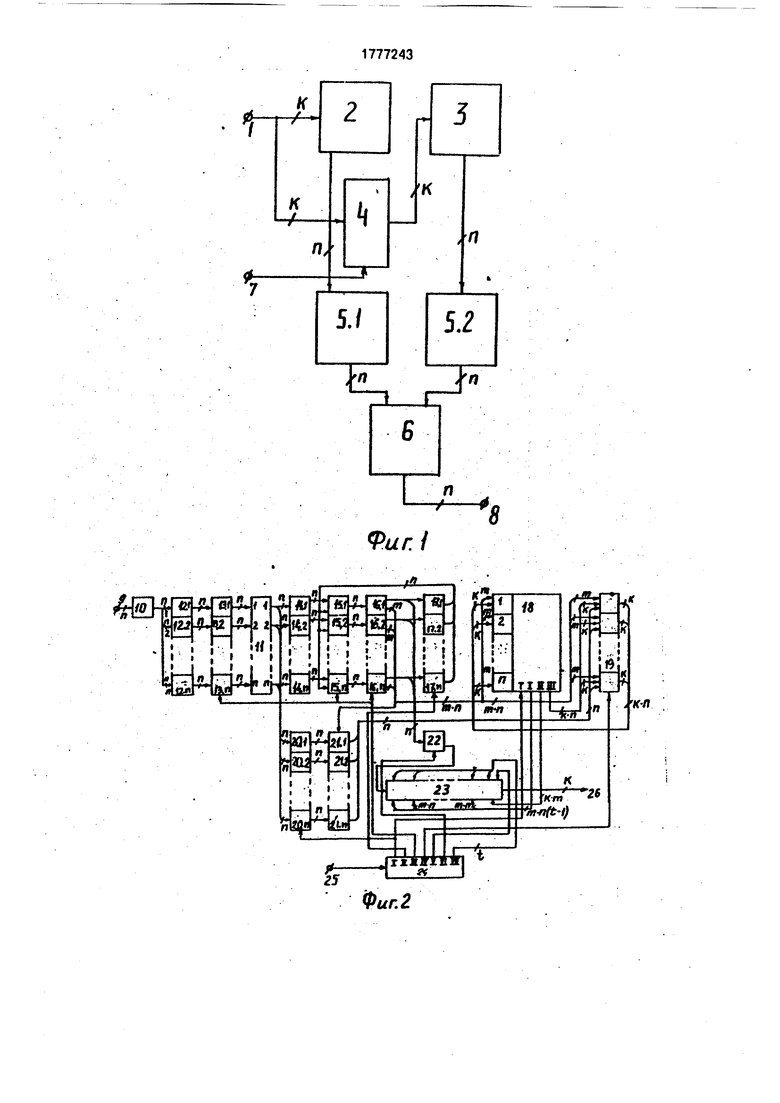

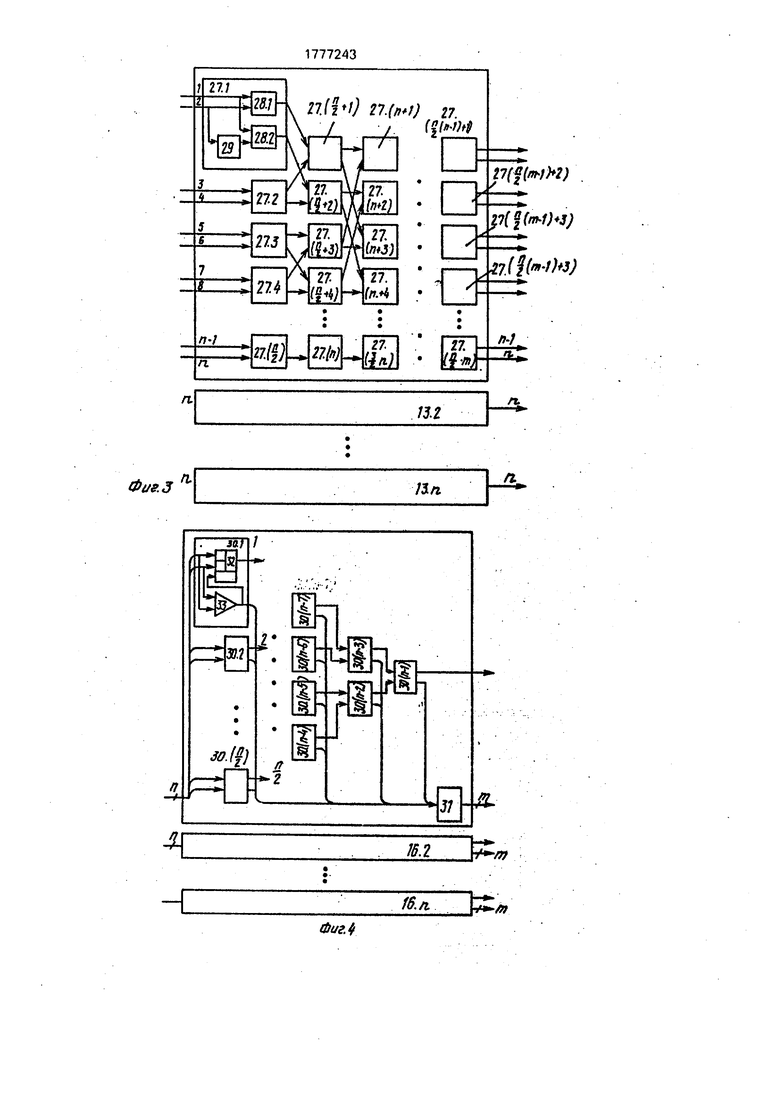

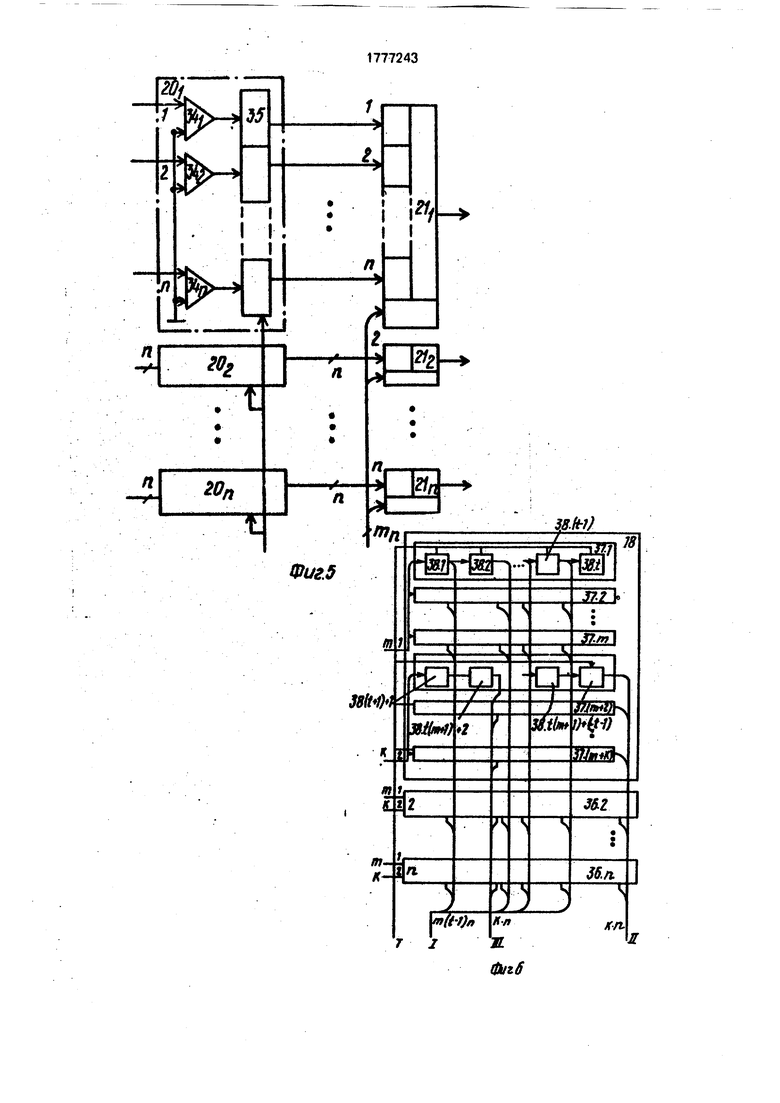

На фиг. 1 и 2 изображены передающая и приемная части кодека; на фиг. 3 - первый -n-й декодеры кода РМ1; на фиг. 4-первый

-n-й вычислители максимума; на фиг. 5 - первый - n-й буферные регистры и первый

-n-й коммутаторы; на фиг. 6 - блок оперативной памяти; на фиг. 7 - вычислитель информационного пути; на фиг 8 - синхронизатор; на фиг. 9 - временные д iarfe

д

VJ

ч| ю со

раммы, поясняющие работу устройства; на фиг. 10 - результаты математического моделирования.

Кодек содержит на передающей стороне: первый и второй преобразователи кода 2, 3, блок задержки 4, блоки суммирования по модулю два 5.1, 5.2, 6.

На приемной стороне: первую и вторую перестановочные матрицы 10. 11, первый - n-й инверторы знака 12.1-12.п. первый-п-й декодеры кода РМ1 13.1-13.п, первый - п-й б/тки амплитудных детекторов 14.1-14.П, первый - n-й блоки суммирования 15.1-15.П, первый - (п 1)-й вычислители максимума 16.1-16.П. 22, первый - n-й элементы задержки 17.1-17.П, блок оперативной памяти 18, вычислитель информационного сигнала 19. первый - n-й буферные регистры 20.1-20.ti, первый - n-й коммутаторы 21.1-21 .п, вычислитель информационного пути 23 и синхронизатор 24.

На фиг. 1 обозначены информационный 1 и синхронизационный 7 входы и информационный выход 8. На фиг. 2 обозначены информационный 10 и синхронизационный 27 входы и информационный выход 28 приемника.

Кодек предназначен для обработки ин- формации,закодированной кодом на основе кода РМ1 (Сверточным кодом с частичной единичной памятью (ЧЕП)). Этот код может быть представлен

Yi XiGo t- ХмО,, где YJ - кодовое слово;

Х| - информационное слово;

} - момент времени:

Go и GI - производящие матрицы.

Матрицы Go и GI могут быть представлены в виде

I ОО

Ь01

Gi

Gf0 G 11

где Goo и G ю-koxn- невырожденные матри- 45 цы;

Go и GH - kix«- матрицы, причем k ko+ki и.6н ||oj|

где n - длина кодового слова;

k - количество информационных символов.

Данный код строится на базе кода Ри-. да-Маллера первого порядка, который обоз- 55 начается РМ(1, т), длина кода равна г 2т, тогда параметры кода (m. k/k0) 2Ш, т + 1/тп)

Goi G(o,m) - единичная строка длины

оГП.

GOO Ј m матрица размера m x 2т. образованная базисными векторами кода РМ1, которые порождают линейную матрицу Адамара порядка 2т; т.е. все возможные векторы дли 2т, взятые в некотором порядке

0

5

5

0

5

0

5

0

5

г(0 Gwm G,o G(l)m,

где Uwm - некоторая матрица, которая получена из сЧп перестановкой стобцов.

Описанный класс кода на основе кода РМ1 является сверточным кодом с частичной единичной памятью (ЧЕП). декодирование которого производится по максимуму правдоподобия.

Кодовое расстояние для этих кодов:

1)РМ(1,т)

d ,

2) для кода (2т, т + 1 /т)

dfree 2т; d(t dx(Ej {2 Cf:r 2rrH- 0 ,

где dfree mlne-d(6JS

d(0 минимальное расстояние для данного кода глубины 6 наименьшее целое, большее х.

Каждый из преобразователей кода 2, 3 представляет собой постоянное программируемое запоминающее устройство (ППЗУ) и содержит k строк длины п, в память который заложены матрицы Go и GI соответственно.

Блоки суммирования по модулю два 5.1, 5.2 содержат no n k-входовых сумматоров по модулю два. Преобразователь кода 2 и блок суммирования по модулю два 5.1, а также преобразователь кода 3 и блок суммирования по модулю два 5.2 попарно составляют кодер РМ1. В каждом кодере производится перемножение k-значного информационного слова с матрицей (G0|G|), которая хранится в ППЗУ.

Блок задержки 4 служит для задержки k-разрядного информационного слова на 1 такт и выполнен на k-разрядном параллельном регистре.

Блок суммирования по модулю два б служит для потактового сложения результатов перемножения информационного слова с матрицей Go и задержанного информационного слова с матрицей GI и выполнен на п двухвходовых сумматорах по модулю два.

Первая перестановочная матрица 10 и первый-п-й инверторы знака 12.1-12.п позволяют использовать для получения метрик декодеры кода РМ1 на основе быстрого преобразования Уолша-Адамара.

Перестановочная матрица 10 выполнена по правилу приведения G0 к и представляет собой кроссировочное устройство с л входами и л выходами. Первый - п-й инверторы знака 12.1-12.п представляют jX)6ou л-входовые инверторы соответствующие лидерам смежных классов, полученным из GI и приведенным по правилу приведения перестановочной матрицы 10, так как данный код представляет смежные классы кода РМ1.

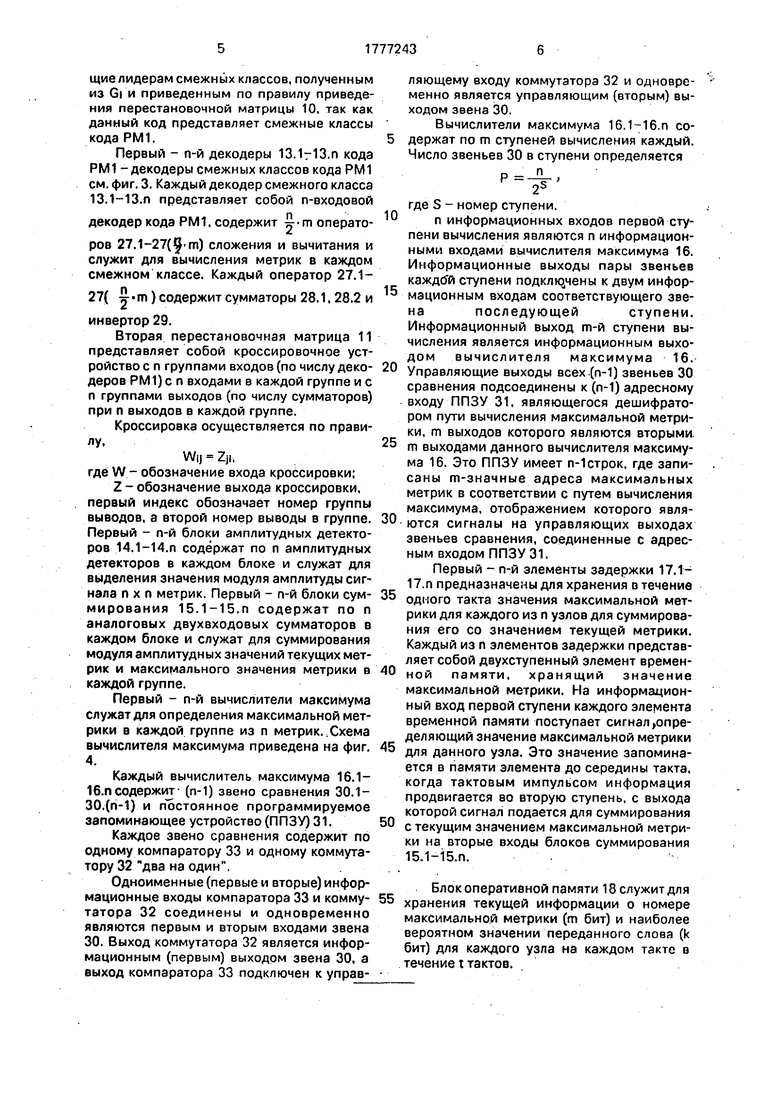

Первый - n-й декодеры 13.1г13.п кода РМ1 -декодеры смежных классов кода РМ1 см, фиг. 3. Каждый декодер смежного класса 13.1-13.п представляет собой п-входовой

декодер кода РМ1, содержит j-m операторов 27.1-27(§-т) сложения и вычитания и служит для вычисления метрик в каждом смежном классе. Каждый оператор 27.127( 5- m) содержит сумматоры 28.1. 28.2 и

инвертор 29.

Вторая перестановочная матрица 11 представляет собой кроссировочное устройство с п группами входов (по числу декодеров РМ1) с п входами в каждой группе и с п группами выходов (по числу сумматоров) при п выходов в каждой группе.

Кроссировка осуществляется по правилу.

Wij Zji, где W - обозначение входа кроссировки;

Z - обозначение выхода кроссировки, первый индекс обозначает номер группы выводов, а второй номер выводы в группе. Первый - n-й блоки амплитудных детекторов 14.1-14.п содержат по п амплитудных детекторов в каждом блоке и служат для выделения значения модуля амплитуды сигнала п х п метрик. Первый - n-й блоки суммирования 15.1-15.п содержат по п аналоговых двухвходовых сумматоров в каждом блоке и служат для суммирования модуля амплитудных значений текущих метрик и максимального значения метрики в каждой группе.

Первый - n-й вычислители максимума служат для определения максимальной метрики в каждой группе из п метрик. Схема вычислителя максимума приведена на фиг. 4.

Каждый вычислитель максимума 16.1- 16.Псодержит- (п-1) звено сравнения 30.1- 30.(п-1) и постоянное программируемое запоминающее устройство (ППЗУ) 31.

Каждое звено сравнения содержит по одному компаратору 33 и одному коммутатору 32 два на один.

Одноименные (первые и вторые) информационные входы компаратора 33 и коммутатора 32 соединены и одновременно являются первым и вторым входами звена 30. Выход коммутатора 32 является информационным (первым) выходом звена 30, а выход компаратора 33 подключен к управ0

5

0

5

0

5

0

5

0

ляющему входу коммутатора 32 и одновременно является управляющим (вторым) выходом звена 30.

Вычислители максимума 16.1-16.п содержат по m ступеней вычисления каждый. Число звеньев 30 в ступени определяется

2s

где S - номер ступени.

п информационных входов первой ступени вычисления являются п информационными входами вычислителя максимума 16. Информационные выходы пары звеньев каждо й ступени подключены к двум информационным входам соответствующего звенапоследующейступени. Информационный выход m-й ступени вычисления является информационным выходом вычислителя максимума 16. Управляющие выходы всех (п-1) звеньев 30 сравнения подсоединены к (п-1) адресному входу ППЗУ 31. являющегося дешифратором пути вычисления максимальной метрики, m выходов которого являются вторыми m выходами данного вычислителя максимума 16. Это ППЗУ имеет п-1 строк, где записаны m-значные адреса максимальных метрик в соответствии с путем вычисления максимума, отображением которого являются сигналы на управляющих выходах звеньев сравнения, соединенные с адресным входом ППЗУ 31.

Первый - n-й элементы задержки 17.1- 17.п предназначены для хранения в течение одного такта значения максимальной метрики для каждого из п узлов для суммирования его со значением текущей метрики. Каждый из п элементов задержки представляет собой двухступенный элемент временной памяти, хранящий значение максимальной метрики. На информационный вход первой ступени каждого элемента временной памяти поступает сигнал ,опре- деляющий значение максимальной метрики для данного узла. Это значение запоминается в памяти элемента до середины такта, когда тактовым импульсом информация продвигается во вторую ступень, с выхода которой сигнал подается для суммирования с текущим значением максимальной метрики на вторые входы блоков суммирования 15.1-15.П.

Блок оперативной памяти 18 служит для хранения текущей информации о номере максимальной метрики (т бит) и наиболее вероятном значении переданного слова (к бит) для каждого узла на каждом такте в течение t тактов.

Блок оперативной памяти содержит п ячеек памяти. Схема блока оперативной памяти приведена на фиг. 6. Каждая ячейка памяти 36.1-36.п содержит (т + kj-элемент- ных регистров сдвига 37.1-37.(m + k), т-ад- ресных и k-информационных.

В адресных регистрах 37.1-37.m содержится информация о значении номера мак- симальной метрики, А в информационных регистрах З7.(т + 1)-37.(т + k) содержится информация об наиболее вероятном значении переданного слова. Эта информация вписывается в первые ячейки 38 соответствующих регистров и продвигается слева направо тактовыми импульсами. Выходы первых (t-1) элементов адресных регистров каждой ячейки памяти составляют первый (m-n-(t-1)) проводный выход блока оперативной памяти. Выходы вторых элементов информационных регистров каждой ячейки памяти составляют третий () проводный выход блока оперативной памяти. Выходы-t элементов информационных регистров каждой ячейки памяти составляют второй k-n проводный выход блока оперативной памя- ти.

Вычислитель информационного сигнала 19 предназначен для вычисления текущего информационного сигнала для каждого из п узлов и состоит из п ППЗУ, содержащих строк по k элементов в каждой. В каждом ППЗУ хранятся k-значные значения текущих информационных сигналов Xi в соответствии с значениями N m-значным номером максимальной метрики, Xf-i-k-значным информационным сигналом для предыдущего момента времени и однозначным обозначением алгебраического знака максимальной метрики.

Значение Xi вычисляется из соотноше- ния

Xi (Y, + XW-G,)G0 ,

где Yt- кодовое слово определяется из N и знака метрики для каждого ППЗУ. На выходе каждого ППЗУ выдается k-значная вели- чина Х|. Первый - n-й буферные регистры 20.1-20п (см. фиг. 5} служат для выделения и хранения в течение такта информации об алгебраическом знаке каждой метрики. Каждый из буферных регистров 20.1-20.п содержит по n-значному параллельному регистру памяти 35 и на входе каждого регистра по п детекторов знака 34.1-34.п, выполненных на компараторах с одним за- нуленным входом.

Первый - n-й коммутаторы 21.1-21.П служат для выбора информации об алгебраическом знаке соответствующей максимальной метрике для каждого из п узлов и представляют собой п коммутаторов п на

один, на адресный m-значный вход каждого из которых поступает m-значный сигнал о номере максимальной метрики для данного узла.

(п + 1)-й вычислитель максимума 22 служит для вычисления максимального значения из п текущих максимальных метрик для момента времени I t, где t - число тактов, характеризующее глубину обработки кодового сигнала, определяющее объем памяти блока оперативной памяти 18.

На информационные входы (п + 1)-го вычислителя максимума подаются выходные сигналы с первого - п-го вычислителей максимума 16.1-16.п, а на управляющий вход сигнал с синхронизатора 24 (выход У1).

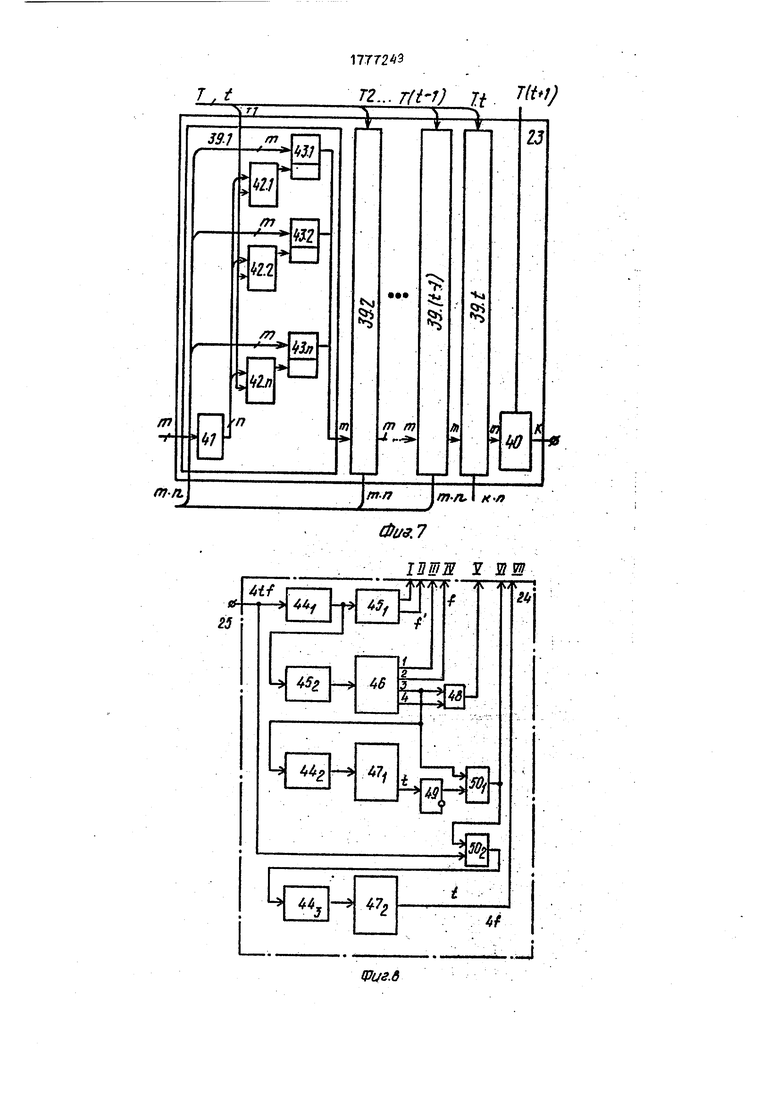

Вычислитель информационного пути 23 предназначен для определения информационного сигнала методом максимального правдоподобия по совокупности t принятых слов. Вычислитель информационного пути 23 производит пошаговый опрос блока опе: ративной памяти 18 от первой до t-й ступени, причем решение об опросе данной ячейки 1-й ступени (I l,t) принимается на основе информации;содержащейся в ячейке (1-1)-й ступени. Схема вычислителя информационного пути 23 приведена на фиг. 7. Вычислитель информационного пути 23 представляет собой t-ступенный коммутатор. Поочередное включение ступеней 39.1- 39.t производится в соответствии с тактовыми импульсами,подаваемыми на тактовый вход с синхронизатора 24 (выход VII).

Каждая ступень вычислителя 39.1-39.1 содержит дешифратор 41 m-разрядного сигнала, п коммутаторов (m x т) с параллельным управлением и п двухвходовых схем И 42.1-42.п, через которые осуществляется тактируемое управление коммутаторов с n-проводного выхода дешифратора, т-про- водные выходы п коммутаторов каждой ступени запараллелены и подаются на адресный вход следующей ступени, На информационные входы коммутаторов (Н)-х ступеней подаются п проводных шин с адресных выходов соответствующих ячеек (этой ступени) блока оперативной памяти, а на информационные входы коммутаторов t- й ступени подаются п k-проводных шин с информационных выходов соответствующих ячеек t-й ступени блока оперативной памяти,

К-проводные выходы п коммутаторов каждой ступени запараллелены и через k разрядный параллельный буферный регистр 40 подаются на k-проводный выход декодера 26. Синхронизатор 24 предназначен для формирования управляющих и тактовых импульсов для управления и согласования во времени. На фиг. 8 приведена схема синхронизатора, на фиг. 9 временная диаграмма.

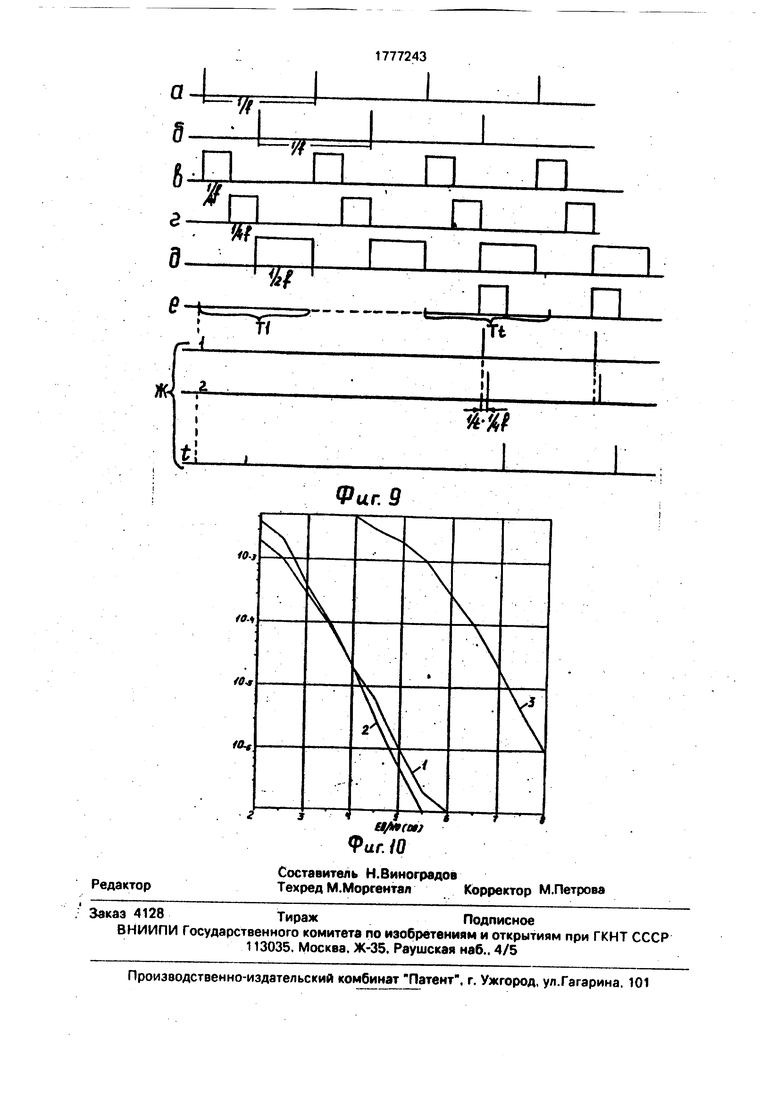

Синхронизатор содержит делители частоты на 144.1-44.3, делитель частоты на 4 45.1-45.2, дешифратор 46 4-х-разрядного сигнала, дешифраторы 47.1-47.2 t-разряд- ного сигнала, триггер 49, схемы И 50,1- 50.2, схему ИЛИ 48. Синхронизатор имеет выходы: первый и второй выходы-сигналы тактовой частоты с нулевым (f) и полутактовым сдвигом (f1) (фиг. 9а, б) с первого и второго выходов делителя 45.1; третий и четвертый выходы-сигналы первой и второй четвертей такта соответственно (фиг. 9в, г) с первого и второго выходов дешифратора 46; пятый выход-сигнал второй половины такта (фиг. 9д) с выхода схемы ИЛИ 48. Шестой выход-сигнал третьей четверти такта с задержкой на t тактов с начала работы (фиг. 9е) на выходе схемы И 50. Седьмой выход - распределенные по времени сигналы, во время действия сигнала на шестом выходе, (фиг. 9ж) на t-проводном выходе дешифратора 47.2.

Кодек работает следующим образом. На передающей стороне на вход кодера 1 поступает k-значное информационное ело- во Х|. На вход преобразователей кода 2 и 3 поступают текущее Х| и задержанное Хм на блоке задержки 4 кодовые слова. Информа- ция записанная в n-значных строках ППЗУ, соответствующих ненулевым разрядам ин- формационного слова, подается на блоки суммирования по модулю два 5.1, 5.2, где производится поразрядное сложение. На блоке суммирования 6 по модулю два происходит поразрядное сложение результатов перемножения информационного слова Х| на матрицу Go и задержанного слова Х,-.,на матрицу GI. На выходе блока суммирования 6 по модулю два образуется п-разрядное кодовое слово YI и подается на выход коде- ра7.

На приемной стороне входной информационный n-разрядный сигнал YI поступает на вход декодера 9, являющегося входом первой перестановочной матрицы 10. Информационный сигнал пропускается через первую перестановочную матрицу, затем через подключенные параллельно первый п-й инверторы знака 12.1-12.п и затем через первый - n-й декодеры кода РМ1 13.1-13.п. Таким образом,на выходе каждого декодера 13.1-13.rt соответственно каждому смежному классу получаем текущие метрики

R- Ј W)i,

i 1 где R - метрика;

YI - значение 1-го символа ожидаемого слова;

(Yk)i - значение 1-го символа слова, принятого из какала связи.

Сигналы текущих метрик через перестановочную матрицу 11 подаются одновременно на первый - n-й блок амплитудных детекторов 14.1-14.п и первый - n-й буферные регистры 20.1-20.п. Первый - n-й амплитудные детекторы 14.1-14.п выделяют для подачи на первые входы первого - п-го блоков суммирования 15.1-15.п абсолютное значение сигналов метрик, а в первом - п-м буферных регистрах 20.1-20.ri из сигналов текущих метрик выделяется и запоминается информация об алгебраическом знаке текущих метрик.

Сигналы абсолютных значений текущих метрик суммируются в соответствующих первых - n-ых блоках суммирования 15.1- 15.п с задержанными на один такт сигналами значения максимальных метрик в каждой группе. Для каждой группы метрик производится выбор максимальной метрики в первом - n-ом вычислителях максимума 16.1-16.rt. Сигналы значения максимальных метрик через соответствующие первые - п-е элементы задержки 17.1-17.П подаются на вторые входы первого - п-го блоков суммирования 15.1-15.П. Сигналы значения номера максимальных метрик с адресных выходов первого- п-го вычислителей максимума 16,1-16.п производят управление первым - n-м коммутаторами 21.1-21.П, через которые пропускаются сигналы знака только максимальных метрик. Кроме того,сигна- лы номеров максимальных метрик вписываются в элементы первой ступени блока оперативной памяти 18 (по первым информационным входам) и подаются на первые информационные входы ППЗУ вычислителя информационного сигнала 19. С третьего выхода блока оперативной памяти 18 ка вторые информационные входы вычислителя информационного сигнала 19 поступают команды о значении информационного сигнала на предыдущем такте.

А также на третьи информационные входы вычислителя информационного сигнала 19 поступают команды (со всех выходов коммутаторов 21.1-21,п) о знаке максимальных метрик,

В соответствии с полученными командами во время второй четверти такта, определяемое сигналом с синхронизатора 24, в

ППЗУ вычислителя информационного сигнала 19 производится вычисление текущего значения информационного сигнала. Команды об этих текущих значениях вписываются в первую ступень информационных регистров каждой ячейки блока оперативной памяти 18 (по вторым информационным входам).

По сигналу о t-ом такте с выхода vj синхронизатора 24 вычислитель информа- ционного пути 23 получает информацию (на первый информационный вход) о номере максимально максимальной метрики с (п + 1)-го вычислителя максимума 22, и,прово- дя поэлементный опрос (t-1) элементов ад- ресных регистров 37.1-37.rn и t-ro элемента информационных регистров З7.(т + 1)-37.(т + R) блока оперативной памяти 18 (при этом информация передается соответственно с первого выхода блока оперативной памяти 18 на второй - t-й информационные входы вычислителя информационного пути 23 и со второго выхода блока оперативной памяти 18 на (t + 1)-й информационный вход вычислителя информационного пути 23),опреде- ляет k-разрядное значение переданного информационного сигнала Xi,подаваемого на выход 27 декодера.

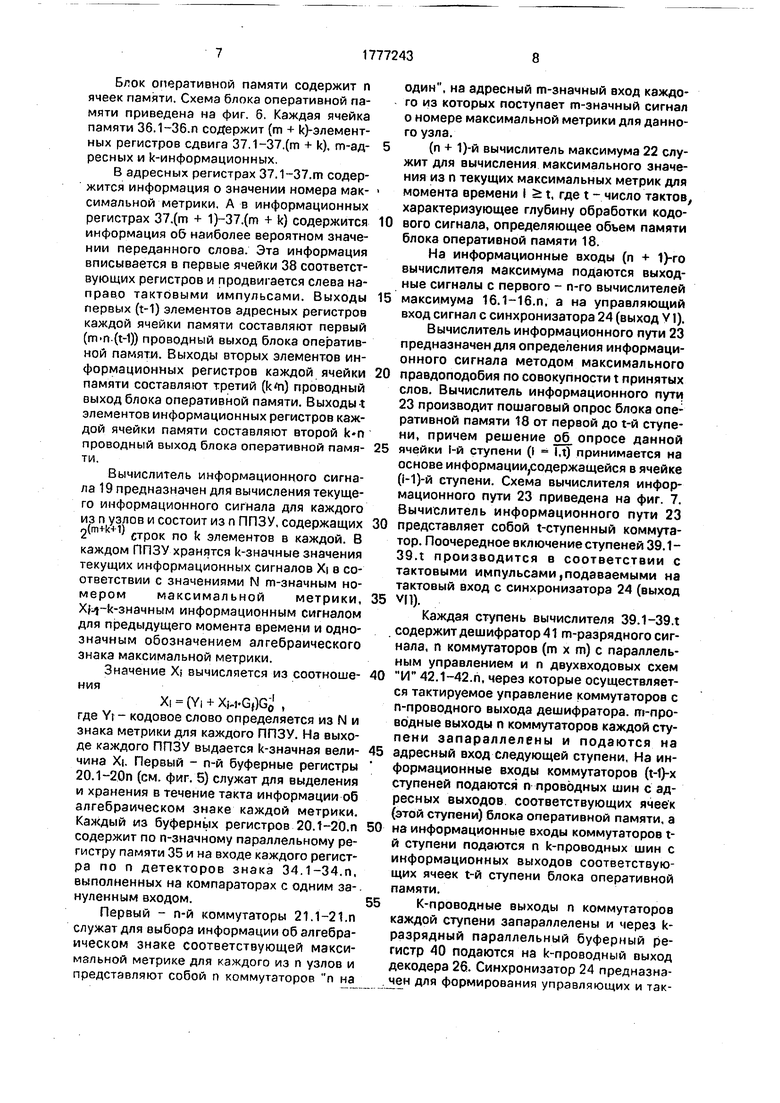

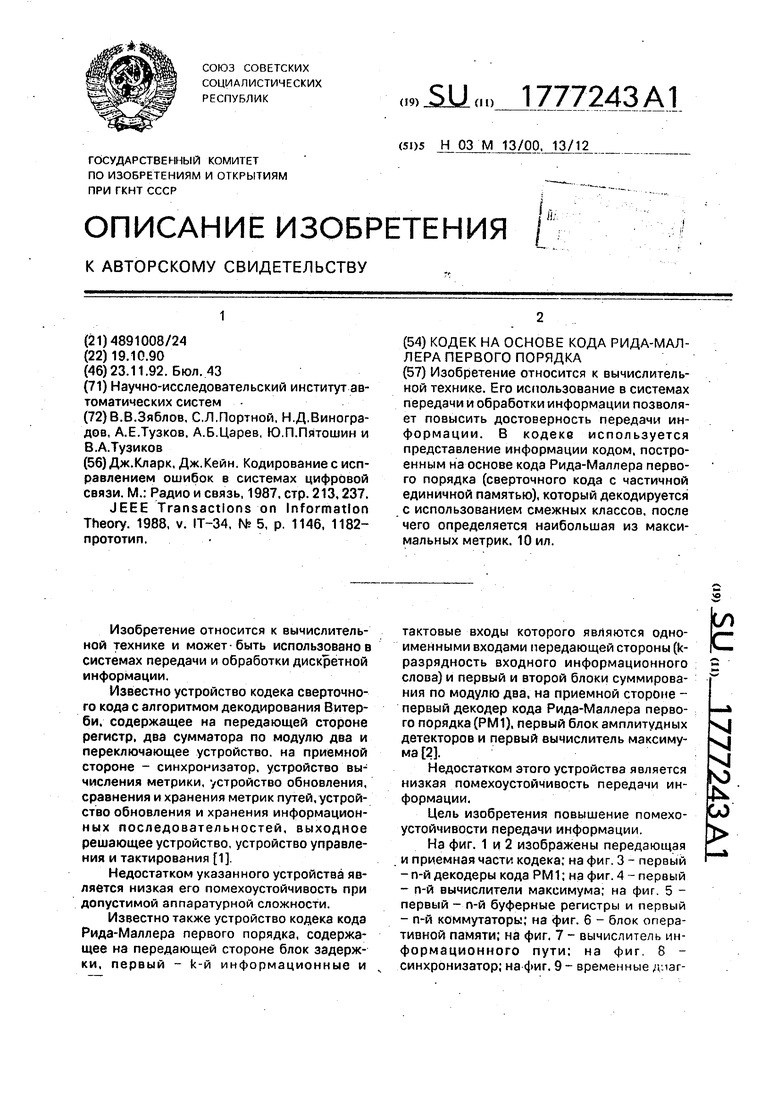

Было проведено математическое моделирование кодека на основе кода РМ1 (ЧЕП) (8, 4/3) и кодека РМ (1,3) при объеме переданной информации 10водовых слов и симметричном Гауссовском канале. Результаты моделирования работы кодека для кода на основе РМ1 (ЧЕП) в сравнении с кодеком для стандарта NASA кодека РМ (1, 3) приведены на фиг. 10 где Р - вероятность искажения,/:)- отношение сигнал/шум в дБ.

Кривая 1 - результаты моделирования для кодека РМ1 (8,4/3) (ЧЕП). Кривая 2результаты моделирования для кодека стандарта NASA. Кривая 3 - результаты моделирования для кодека РМ (1, 3).

Как видно из графика,кодек на основе кода РМ1(ЧЕП)даетвыигрышпосравнению с кодеком РМ (1. 3) на 3 дБ. А по сравнению с кодеком стандарта NASA значительно проигрывает в области малых шумов и дает выигрыш в области больших шумов. Причем кодек на основе кода РМ1 (ЧЕП},как показы- вает расчет аппаратурной сложности,проще кодека стандарта NASA.

Сравнительная сложность определяется отношением числа вещественных вычислений. Для кодека на основе РМ1 (8, 4/3) (ЧЕП) для каждого узла определяется количество вещественных вычислений.

УРМ. WBM6T + .+ WeM3Kc

где WBMeT количество вещественных вычислений при вычислении метрик

Wewer ГП П:

WC.M. - количество вещественных вы числений при суммировании метрик

WC.M. п;

Мвмвк количество вещественных вычислений при выборе максимума

W

вмахс

п,

таким образом, для кода на основе РМ 4/3) (ЧЕП)

урм 8-3 + 8 + 8 40.

Для кодека стандарта А А для кажд узла определяется количество веществных вычислений

) Р(.НЗКС) ,

где Р - число узлов Р 2Ы; k - длина кодового ограничения

WC.M. - количество вещественных числений при суммировании метрик;

WC.M. I;

WBMeKC - количество вещественных числений при выборе максимума:

WcMaKC l; J- число символов на узел;

1 2. Таким образом.

,7-1

У NASA

(1-2 + 1)

96

ft-относительная сложность,

tf- У NASA

Урм

Формула изобретения Кодек на основе кода Рида-Маллера первого порядка, содержащий на передающей стороне блок задержки, первый k-й информационный и тактовый входы которого являются одноименными входами передающей стороны (k-разрядность входного информационного символа), первый и второй блоки суммирования по модулю два, на приемной стороне - первый декодер кода Рида- Маллера, первый блок амплитудных детекторов и первый вычислитель максимума, отличающийся тем, что, с целью повышения достоверности передачи информации, на передающей стороне введены третий блок суммирования по модулю два и первый и второй преобразователи кода, входы первого преобразователя кода подключены к соответствующим информационным входам передающей стороны, выходы блока задержки соединены с входами второго преобразователя кода, выходы первого и второго преобразователей кода подключены к соответствующим входам одноименных блоков суммирования по модулю два.

выходы которых соединены с первыми и вторыми входами третьего блока суммирования по модулю два, выходы которого являются выходами передающей стороны, на приемной стороне введены первая и вторая перестановочные матрицы, второй - n-й декодеры кода Рида-Маллера (п-разрядность кода Рида-Маллера), первый - n-й инверторы знака, второй - n-й блоки амплитудных детекторов, первый - n-й блоки суммирова- ния, второй - п + 1)-й вычислители максимума, первый - n-й буферные регистры, первый - n-й коммутаторы, первый - п-й элементы задержки, блок оперативной памяти, вычислитель информационного сигна- ла. вычислитель информационного пути и синхронизатор, вход которого является входом синхронизации приемной стороны, первый - n-й входы первой перестановочной матрицы являются соответствующими информационными входами приемной стороны, выходы первой перестановочной матрицы соединены с соответствующими входами 1-го инвертора знака (I TjJ), выходы которого соединены с соответствующи- ми информационными входами одноименного декодера кода Рида-Маллера, выходы которого подключены к соответствующим разрядам 1-х входов второй перестановочной матрицы, 1-е выходы кото- рой соединены с входами 1-го амплитудного детектора и информационными входами 1-го буферного регистра, выходы первого - п-го амплитудных детекторов подключены к первым входам одноименных блоков суммиро- вания, выходы которых соединены с информационными входами одноименных первого - п-го вычислителей максимума, первые выходы которых соединены с соответствующими входами (п + 1)-го вычислите- ля максимума и информационными входами одноименных элементов задержки, выходы которых соединены с вторыми входами одноименных блоков суммирования, выход (п + 1)-го вычислителя максимума подключен к первому информационному входу вычислителя информационного пути, вторые выходы первого - п-го вычислителей максимума соединены с управляющими входами первого - п-го коммутаторов, первыми информационными входами вычислителя информационного сигнала и первыми информационными входами блока оперативной памяти, первые и вторые выходы которого подключены соответственно к вторым - t-м информационным входам и к (t + 1}-м информационным входам вычислителя информационного пути (t- глубина обработки кодового слова), третьи выходы блока оперативной памяти соединены с вторыми информационными входами вычислителя информационного сигнала, выходы которого подключены к вторым информационным входам блока оперативной памяти, выходы первого - п-го буферных регистров соединены с соответствующими информационными входами всех коммутаторов, выходы которых подключены к третьим информационным входам вычислителя информационного сигнала, первый выход синхронизатора соединен с тактовыми входами блока оперативной памяти и всех буферных регистров, второй выход синхронизатора подключен к тактовым входам всех блоков задержки, третий выход синхронизатора соединен с тактовыми входами всех декодеров кода Рида-Маллера, всех блоков суммирования и первого - п-го вычислителей максимума, четвертый выход синхронизатора подключен к тактовому входу вычислителя информационного слова, пятый выход синхронизатора соединен с входом синхронизации вычислителя информационного пути, шестой выход синхронизатора подключен к тактовому входу (п + 1)-го вычислителя максимума, седьмые выходы син- хронизаторасоединеныс

соответствующими тактовыми входами вычислителя информационного пути, выходы которого являются выходами приемной стороны.

ii

(&+%

а„ ,ш

- -|«м в

ЕЈ

м

в;

t«

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек блочной сигнально-кодовой конструкции | 1989 |

|

SU1711337A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Кодек двоичных блочных кодов | 1986 |

|

SU1408532A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Декодер кода Рида-Маллера первого порядка по максимуму правдоподобия | 1990 |

|

SU1775857A1 |

| Кодек для системы связи с многократной фазовой модуляцией | 1987 |

|

SU1629992A1 |

| Система передачи и приема цифровых сигналов | 1985 |

|

SU1314463A1 |

| Устройство для декодирования кода Нордстрома-Робинсона в дискретном канале | 1989 |

|

SU1736008A1 |

Изобретение относится к вычислительной технике. Его использование в системах передачи и обработки информации позволяет повысить достоверность передачи информации. В кодеке используется представление информации кодом, построенным на основе кода Рида-Маллера первого порядка (сверточного кода с частичной единичной памятью), который декодируется с использованием смежных классов, после чего определяется наибольшая из максимальных метрик. 10 ил.

.

«а

н

и

УХ

/VT

9

з-с

иЛ

Г 5

tu

ь

X

я

1

шин

г

л

Фиг.5

№Фг

MS Ј SlilSI

L (p

v-x 1/-Ш u-ui

(ft

Iff

b

;

«

(

ttrZJ-Ш

v-ш

to

u.

to

Ш

g

4

W

u/

№

w

№

ш

ttf

fj

Г1

°-W

Фаг 9

Авторы

Даты

1992-11-23—Публикация

1990-10-19—Подача