12

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| АДАПТИВНАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1999 |

|

RU2150785C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

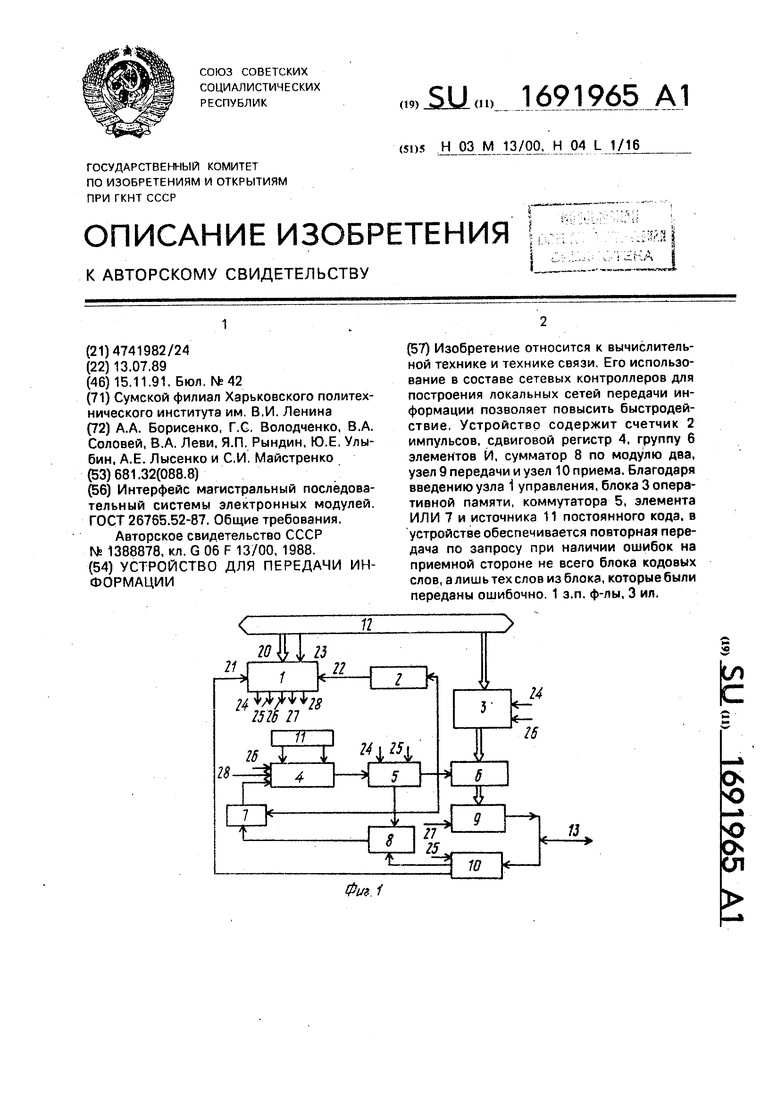

Изобретение относится к вычислительной технике и технике связи. Его использование в составе сетевых контроллеров для построения локальных сетей передачи информации позволяет повысить быстродействие. Устройство содержит счетчик 2 импульсов, сдвиговой регистр 4, группу 6 элементов И, сумматор 8 по модулю два, узел 9 передачи и узел 10 приема. Благодаря введению узла 1 управления, блока 3 оперативной памяти, коммутатора 5, элемента ИЛИ 7 и источника 11 постоянного кода, в устройстве обеспечивается повторная передача по запросу при наличии ошибок на приемной стороне не всего блока кодовых слов, а лишь тех слов из блока, которые были переданы ошибочно. 1 з.п. ф-лы, 3 ил.

О

о

Os

ел

Изобретение относится к вычислительной технике и технике связи и может быть использовано в cociaee сетевых контролле- рор «ля пост розни /шкальных сетей передачи информации.

Цель i o jpeienun - повышение быстро- (Пействит

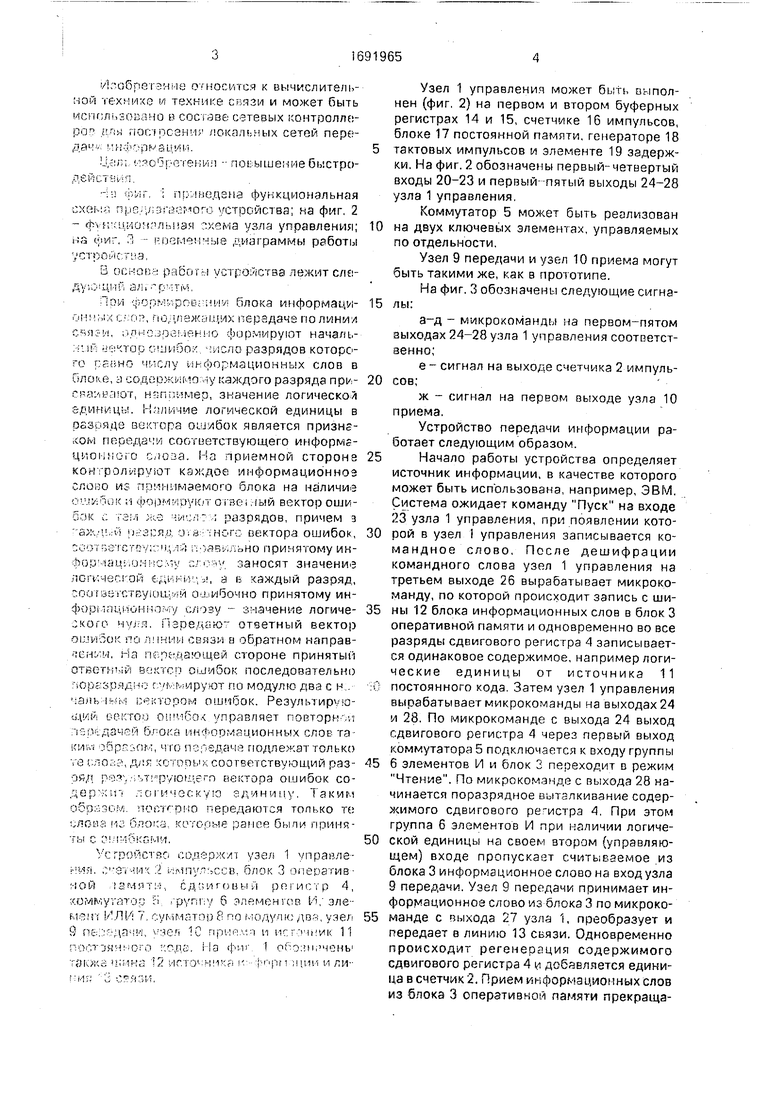

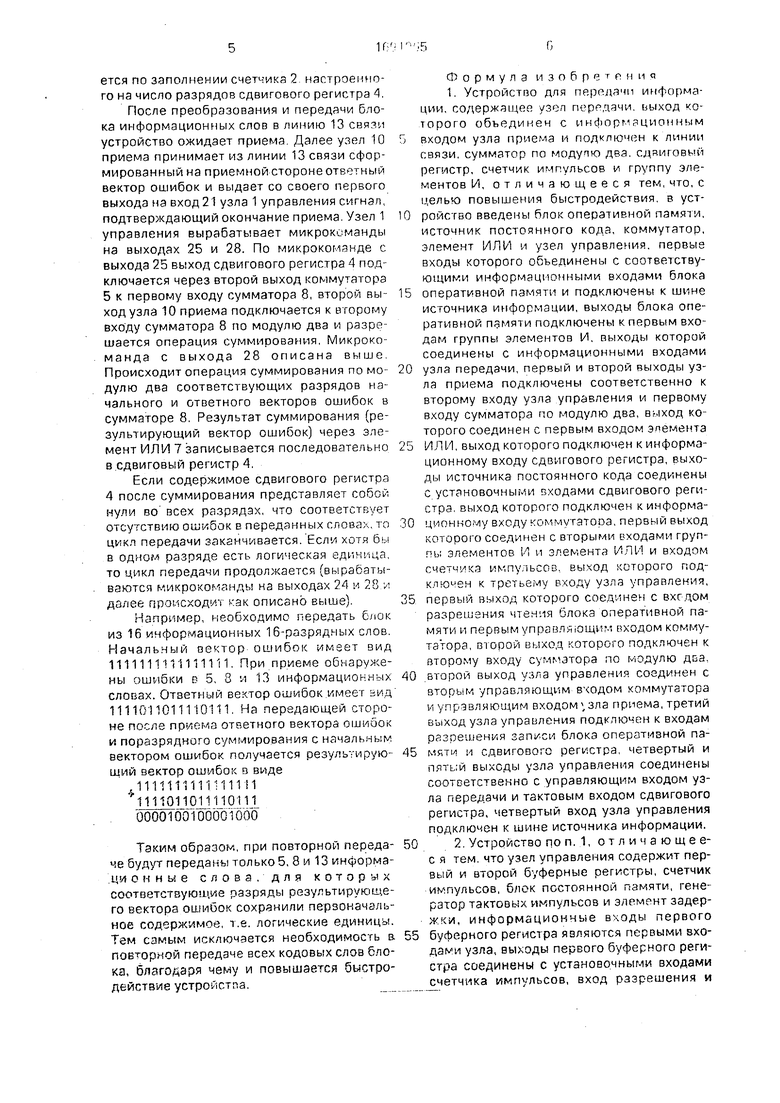

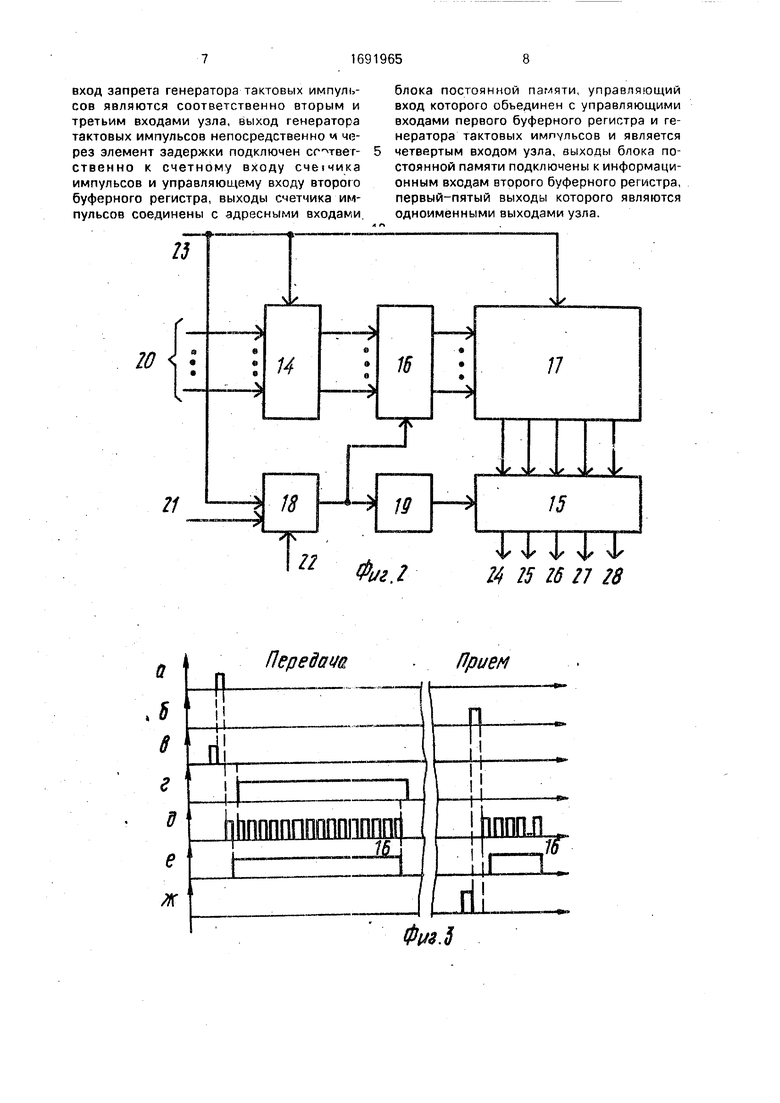

h1) г,мг 1 приведена функциональная схеМ Т. предлагаемого устройства; на фиг. 2 - функциональная схема узла управления; на фиг. П - роемепчые диаграммы работы устройства,

В ouHOBt; работы устройства лежит следующий алгоритм.

При формирос ии блока информационных и.о, подлежащих передаче по линии , опн воанрнпо формируют началь- 1й лектор ошибок, -пело разрядов которого равно числу информационных слов в Олоке, а содержимому каждого разряда при- гвзива от, нчппимер, значение логической единицы. Наличие логической единицы в разряде вектора ошибок является признаком передачи соответствующего информационного слоэа. На приемной стороне контролируют каждое информационное слово из принимаемого блока на наличие С чябок и формируют ответный вектор оши- C iK v. -зм АО J. f i1- i разрядов, причем в a jv-vi , о,в iHoro вектора ошибок, соотосгстоу щпл {.оавкльно принятому ин- Ьормашюипс лу z vy заносят значение логической , а в каждый разряд, СООТВЕТСТВУЮЩИЙ ошибочно принятому ин- форыацяинночу ьлову - значение логического нуля. Передают ответный вектор ошибок по линии связи в обратном направлении. На передающей стороне принятый ответный в е кто о ошибок последовательно юразрядис сд ммируют по модулю два с н ,- «-альчым сектором ошибок. Результирующий иектоо ошибок управляет повторили передачей блока информационных слов та- KMivf образом, ч го передаче подлежат только 1(з елопа, для четном соответствующий раз- ояд р9ч ,,тирующего вектора ошибок со- огическую единицу. Таким о разогл. ПОСТ-DUO передаются только те ьяова ил блока которые ранее были приняты С СН ШОКГ МИ

Устройство со, узел 1 управле- t я. ,4-3i 2 ifMnyrscoB, блок 3 оперэтив- мой тамяти сдзиговый pei истр 4, fOMMyraioo 5 ipyniy б элементов И, эле- м иг1/ЛИ7 сумматор 8 по модулю дв,ч узел 9 яьос.ца1 м, 3еп 10 и источник 11 ГУЛОЯМНОГО ода. На фи 1 обо точены i;;i4S 2 ь поччигя и i ч)рм зцин и ли ПЯ 3 ЯЗИ.

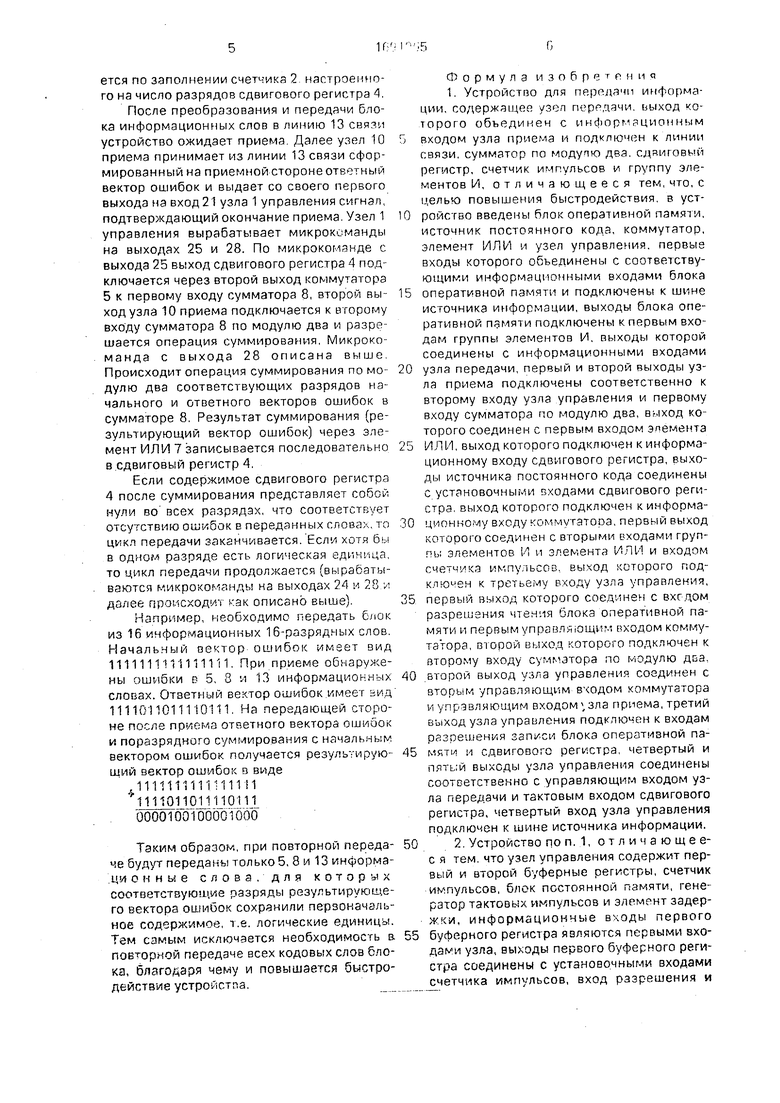

Узел 1 управления может быть выполнен (фиг. 2) на первом и втором буферных регистрах 14 и 15, счетчике 16 импульсов, блоке 17 постоянной памяти, генераторе 18

тактовых импульсов и элементе 19 задержки. На фиг. 2 обозначены первый-четвертый входы 20-23 и первый-пятый выходы 24-28 узла 1 управления.

Коммутатор 5 может быть реализован

0 на двух ключевых элементах, управляемых по отдельности.

Узел 9 передачи и узел 10 приема могут быть такими же, как в прототипе.

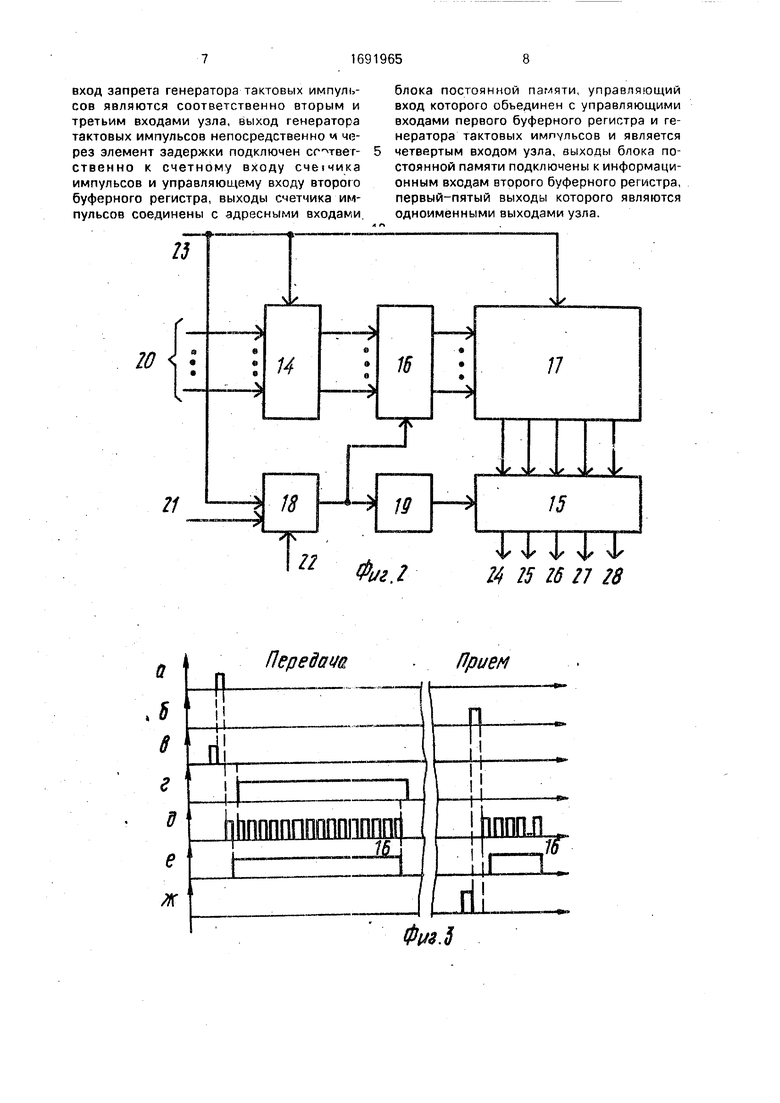

На фиг, 3 обозначены следующие сигна5 лы:

а-д - микрокоманды на первом-пятом выходах 24-28 узла 1 управления соответственно;

е - сигнал на выходе счетчика 2 импуль0 сов;

ж - сигнал на первом выходе узла 10 приема.

Устройство передачи информации работает следующим образом.

5Начало работы устройства определяет

источник информации, в качестве которого может быть использована, например, ЭВМ. Система ожидает команду Пуск на входе 23 узла 1 управления, при появлении кото0 рой в узел 1 управления записывается командное слово, После дешифрации командного слова узел 1 управления на третьем выходе 26 вырабатывает микрокоманду, по которой происходит запись с ши5 ны 12 блока информационных слов в блок 3 оперативной памяти и одновременно во все разряды сдвигового регистра 4 записывается одинаковое содержимое, например логические единицы от источника 11

О постоянного кода. Затем узел 1 управления вырабатывает микрокоманды на выходах 24 и 28. По микрокоманде с выхода 24 выход сдвигового регистра 4 через первый выход коммутатора 5 подключается к входу группы

5 6 элементов И и блок 3 переходит в режим Чтение. По микрокоманде с выхода 28 начинается поразрядное выталкивание содержимого сдвигового регистра 4. При этом группа 6 элементов И при наличии логиче0 ской единицы на своем втором (управляющем) входе пропускает считываемое из блока 3 информационное слово на вход узла 9 передачи, Узел 9 передачи принимает информационное слово из блока 3 по микроко5 манде с выхода 27 узла 1, преобразует и передает в линию 13 связи. Одновременно происходит регенерация содержимого сдвигового регистра 4 и добавляется единица в счетчик 2. Прием информационных слов из блока 3 оперативкой памяти гтрекращается по заполнении счетчика 2 настроенного на число разрядов сдвигового регистра 4.

После преобразования и передачи блока информационных слов в линию 13 связи устройство ожидает приема Далее узел 10 приема принимает из линии 13 связи сформированный на приемной стороне ответный вектор ошибок и выдает со своего первого выхода на вход 21 узла 1 управления сигнал, подтверждающий окончание приема. Узел 1 управления вырабатывает микрокоманды на выходах 25 и 28. По микрокоманде с выхода 25 выход сдвигового регистра 4 подключается через второй выход коммутатора 5 к первому входу сумматора 8, второй вы- ход узла 10 приема подключается к второму входу сумматора 8 по модулю два и разрешается операция суммирования. Микрокоманда с выхода 28 описана выше. Происходит операция суммирования по мо- дулю два соответствующих разрядов начального и ответного векторов ошибок в сумматоре 8. Результат суммирования (результирующий вектор ошибок) через элемент ИЛИ 7 записывается последовательно в сдвиговый регистр 4.

Если содержимое сдвигового регистра А после суммирования представляет собой нули во всех разрядах, что соответствует отсутствию ошибок в переданных словах, то цикл передачи заканчивается. Если хотя бы в одном разряде есть логическая единица, то цикл передачи продолжается (вырабатываются микрокоманды на выходах 24 и 28 и далее происходит k-ак описано выше).

Например, необходимо передать блок из 16 информационных 16-разрядных слов. Начальный вектор ошибок имеет вид 1111111111111111. При приеме обнаружены ошибки в 5, 8 и 13 информационных словах. Ответный вектор ошибок имеет вид 11110110111 10111. На передающей стороне после приема ответного вектора ошибок и поразрядного суммирования с начальным вектором ошибок получается результирую- ший вектор ошибок в виде

1111111111111111

1111011011110111

0000100100001000

Таким образом, при повторной переда- че будут переданы только 5, 8 и 13 информа- ционные слова, для которых соответствующие разряды результирующего вектора ошибок сохранили первоначальное содержимое, т.е. логические единицы. Тем самым исключается необходимость а повторной передаче всех кодовых слов блока, благодаря чему и повышается быстродействие устройства.

Формула изобретения

вход запрета генератора тактовых импульсов являются соответственно вторым и третьим входами узла, выход генератора тактовых импульсов непосредственно ч через элемент задержки подключен сгтвет- ственно к счетному входу импульсов и управляющему входу второго буферного регистра, выходы счетчика импульсов соединены с адресными входами

Т

22

Q

6 в

г

д е

ж

Передача

блока постоянной памяти, управляющий вход которого обьединен с управляющими входами первого буферного регистра и генератора тактовых импульсов и является четвертым входом узла, выходы блока постоянной памяти подключены к информационным входам второго буферного регистра, первый-пятый выходы которого являются одноименными выходами узла,

Фиг.2

ч г у 1 ч Ц 15 26 27 28

ii

| Интерфейс магистральный последовательный системы электронных модулей | |||

| Приспособление круглым вязальным машинам для сигнализации о поломке пятки | 1931 |

|

SU26765A1 |

| Общие требования | |||

| Устройство для сопряжения абонента с каналом связи | 1986 |

|

SU1388878A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-15—Публикация

1989-07-13—Подача