соединен с входом сброса регистра, информационный вход которого соединен с первым входом блокаг начальной установки, первый выход которого соединен с выходом регистра, а первый вход блока начальной установки соединен также с входом формирователя импульсов установки и первым входом многоразрядного переключателя, второй вход, управляющий вход и выход которого соединены соответственно с вторым входом блошка начальной установки, выходом формирователя импульсов установки, который является дополнительным выходом блока начальной установки и вторым выходом блока начальной установки, а управляющий вход формирователя импульсов установки соединен с управляющим входом блока начальной установки.

3, Счетчик по п.1, о т л и ч а ю щ и и с я тем, что буферное запоминающее устройство содержит регистр из триггеров, элементы И и элемент ИЛИ, выход которого является выходом буферного запоминающег устройства, входы которого соединены с входами установки триггеров регистра, выходы которых соединены с первыми входами соответствующих элементов И, выходы которых соединены с входом сброса того же тригге

ра регистра и соответствующим уходом элемента ИЛИ, а вторые входы элементов И соединены с управляющим входом буферного запомина ощего устройства.

4. Счетчик по П.1, отличающийся- тем, что устройство управления содержит первый и второй распределители и счетчик адреса, выходы которого являются адресным выходом устройства управления, тактовый вход которого соединен с тактовым входом первого распределителя, выходы которого соединены с выходами установки, вспомогательным и дополнительным выходами устройства управления И входом счетчика адреса, который соединен с тактовым входом второго распределителя, входы которого и выход счетчика адреса я вляются.управляющими выходами устройства управления.

5. Счетчик по п.1, отличающийся тем, что коммутирующий элемент содержит элемент ИЛИ и дополнительный элемент И, первый и второй входы элемента ИЛИ соединены с первым и вторым входами коммутирующего элемента, выход элемента ИЛИ соединен с первым входом дополнитель ног.о элемента И, выход и второй вход которого соединены соответственно с выходом и третьим входом коммутирующего элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 2014 |

|

RU2538342C1 |

| Многоканальный фотометр | 1988 |

|

SU1569584A1 |

| Генератор псевдослучайных сигналов | 1987 |

|

SU1437974A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| Многоканальный счетчик импульсов | 1987 |

|

SU1508342A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Многоканальная стабилизирующая система электропитания | 1987 |

|

SU1444736A1 |

| Имитатор канала | 1987 |

|

SU1467556A1 |

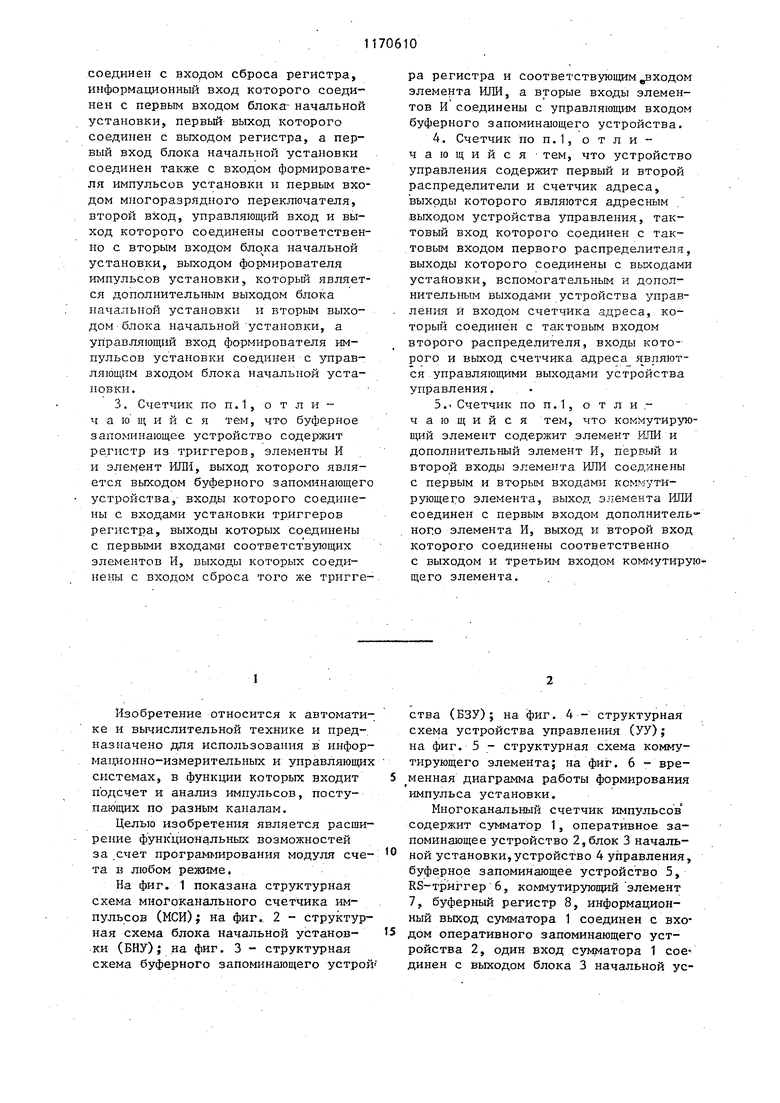

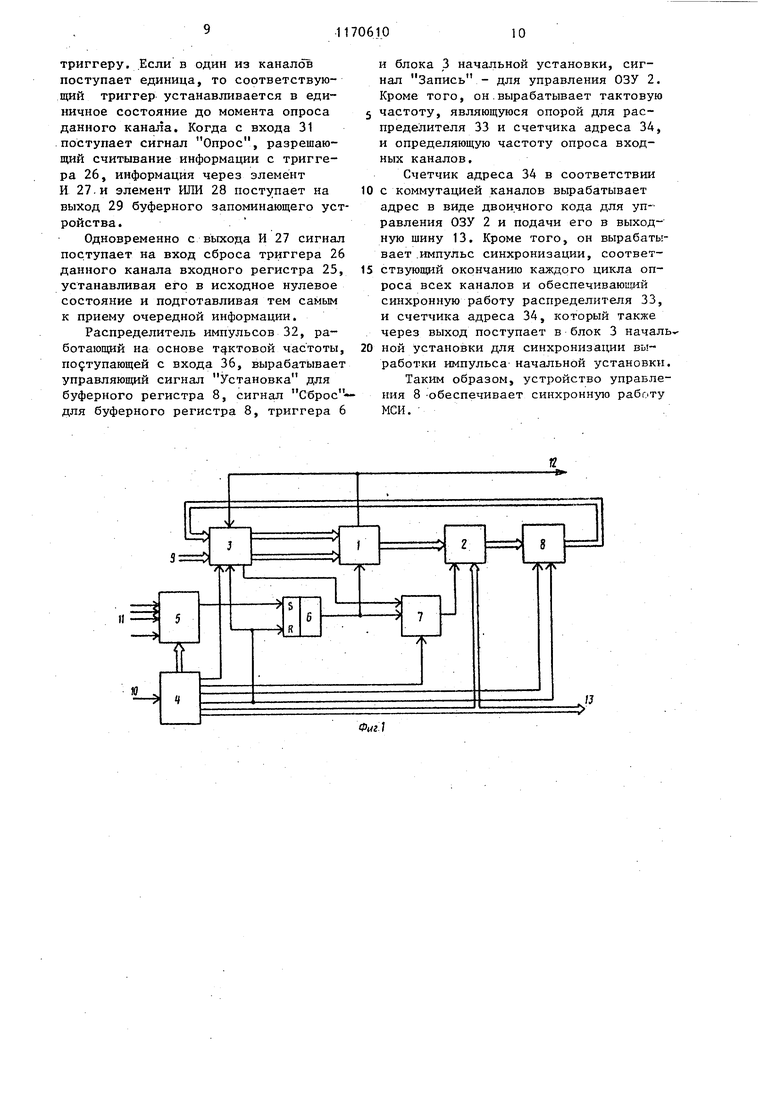

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в информационно-измерительных и управляющих системах, в функции которых входит подсчет и анализ импульсов, поступающих по разным каналам. Целью изобретения является расширение функциональных возможностей за .счет програ шрования модуля счета в любом режиме. На фиг. 1 показана структурная схема многоканального счетчика импульсов (МОИ); на фиг.. 2 - структурная схема блока начальной установки (БНУ); на фиг. 3 - структурная схема буферного запоминающего устрой ства (БЗУ); на фиг. 4 - структурная схема устройства управления (УУ); на фиг. 5 - структурная схема коммутирующего элемента; на фиг. 6 - временная диаграмма работы формирования импульса установки. Многоканальньп счетчик импульсов содержит сумматор 1, оперативное запоминающее устройство 2,блок 3 начальной установки,устройство 4 управления, буферное запоминающее устройство 5, RS-триггер 6, коммутирующийэлемент 7, буферный регистр 8, информационный выход сумматора 1 соединен с входом оперативного запоминающего устройства 2, один вход сумматора 1 сов динен с выходом блока 3 начальной усановки, первый вход которого соедиен с внешней шиной 9, управляющие ыходы устройства управления 4 соедиены с управляющими входами буферного запоминающего устройства 5 и блока 5 3 начальной установки и оперативного запоминающего устройства 2, а тактовый вход устройства управления 4 соеинен с внешней тактовой.шиной 10, информационные входы буферного запоминающего устройства 5 соединены с информационными шинами 11, вход установки RS-триггера 6 соединен с выходом буферного запоминающего устройства 5, вход сброса RS-триггера 6 соединен с вспомогательным выходом устройства управления 4, который соединен с дополнительными входами блока 3 начальной установки и буферного регистра 8, вход установки регистра 8 соединен с выходом установки устройства управления 4, выход оперативного запоминающего устройства

2через буферный регистр 8 соединен с вторым информационным входом блока

3начальной установки, выход RS-триггера 6 соединен с входом переноса сумматора 1 и первым входом коммутирующего элемента 7, второй и третий входы которого соединены с дополни- 30 тельными вькодами блока 3 начальной установки и устройства управления 4,

а выход коммутирующего элемента 7 соединен с входом записи оперативного запоминающего устройства 2, выход 35 переполнения сумматора 1 соединен с входом переполнения блока 3 начальной установки и с выходной шиной 12 переполнения, адресный выход устройства управления 4 соединен с адрес;- 40 ным входом оперативного запоминающего устройства 2 и выходной адресной шиной 13, второй информационный выход блока 3 начальной установки соединен с вторым информационным вхо 45 дом сумматора 1.

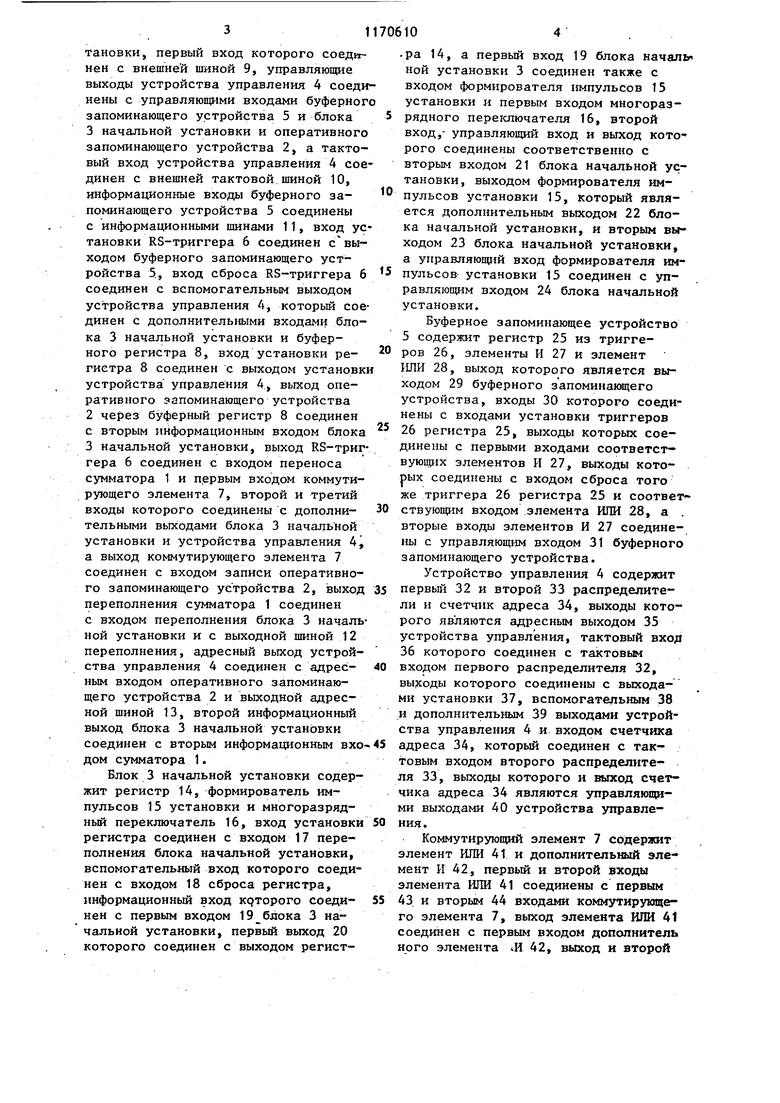

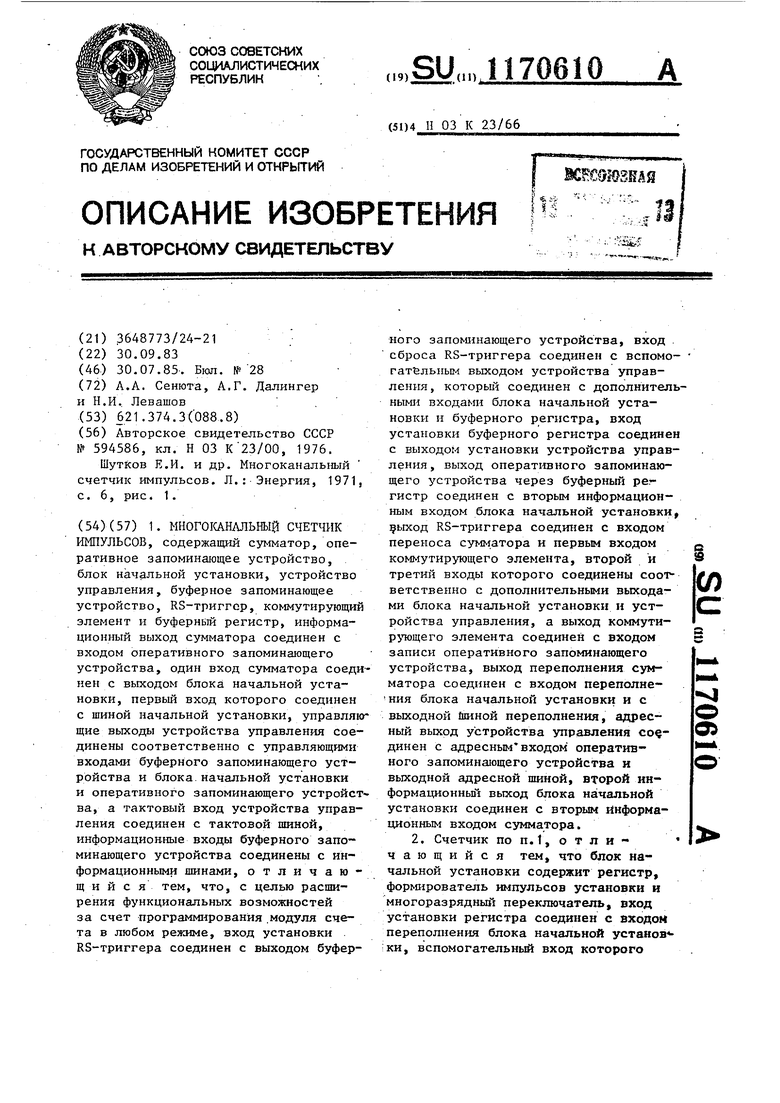

Блок 3 начальной установки содержит регистр 14, формирователь импульсов 15 установки и многоразрядный переключатель 16, вход установки 50 регистра соединен с входом 17 переполнения блока начальной установки, вспомогательный вход которого соединен с входом 18 сброса регистра, информационный вход крторого соеди- 55 нен с первым входом 19 блока 3 начальной установки, первый выход 20 которого соединен с выходом регистра 14, а первый вход 19 блока начал ной установки 3 соединен также с входом формирователя импульсов 15 установки и первым входом многоразрядного переключателя 16, второй вход,- управляющий вход и выход которого соединены соответственно с вторым входом 21 блока начальной установки, выходом формирователя импульсов установки 15, который является дополнительным выходом 22 блока начальной установки, и вторым выходом 23 блока начальной установки, а управляющий вход формирователя импульсов установки 15 соединен с управляющим входом 24 блока начальной установки.

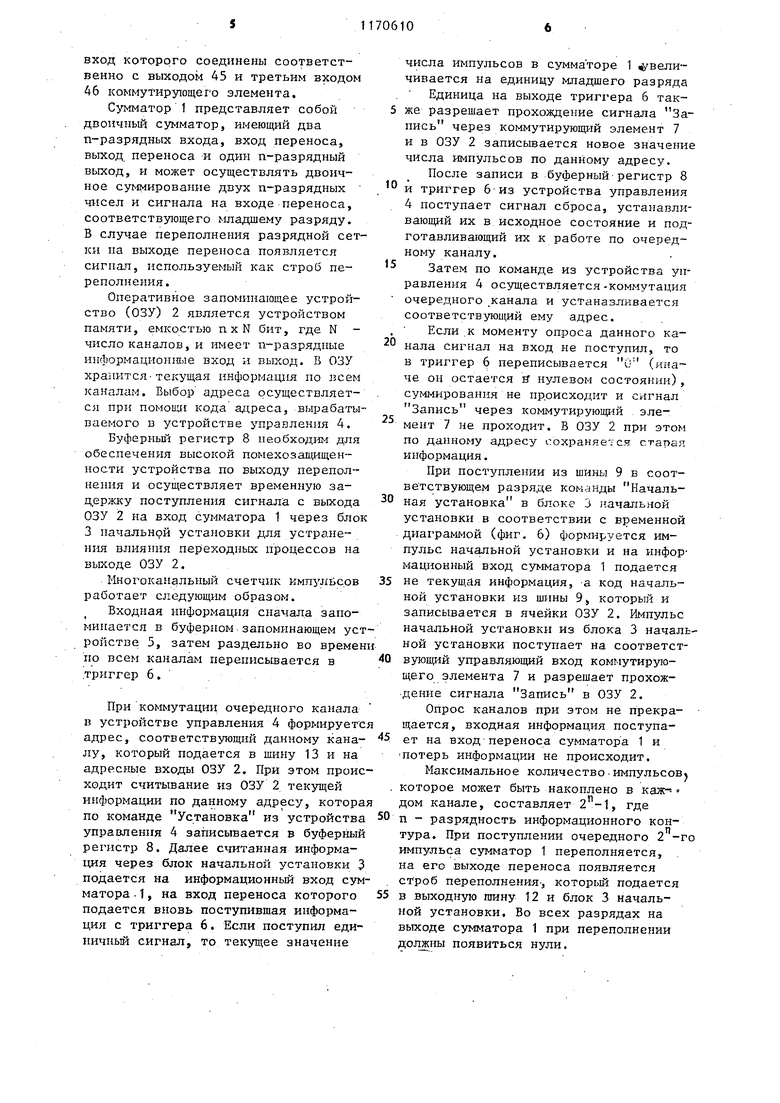

Буферное запоминающее устройство 5 содержит регистр 25 из триггеров 26, элементы И 27 и элемент ИЛИ 28, выход которого является выходом 29 буферного запоминакицего устройства, входы 30 которого соединены с входами установки триггеров 26 регистра 25, выходы которых соединены с первыми входами соответствующих элементов И 27, выходы которых соединены с входом сброса того же триггера 26 регистра 25 и соответствующим входом элемента ИЛИ 28, а вторые входы элементов И 27 соединены с управляющим входом 31 буферного запоминающего устройства.

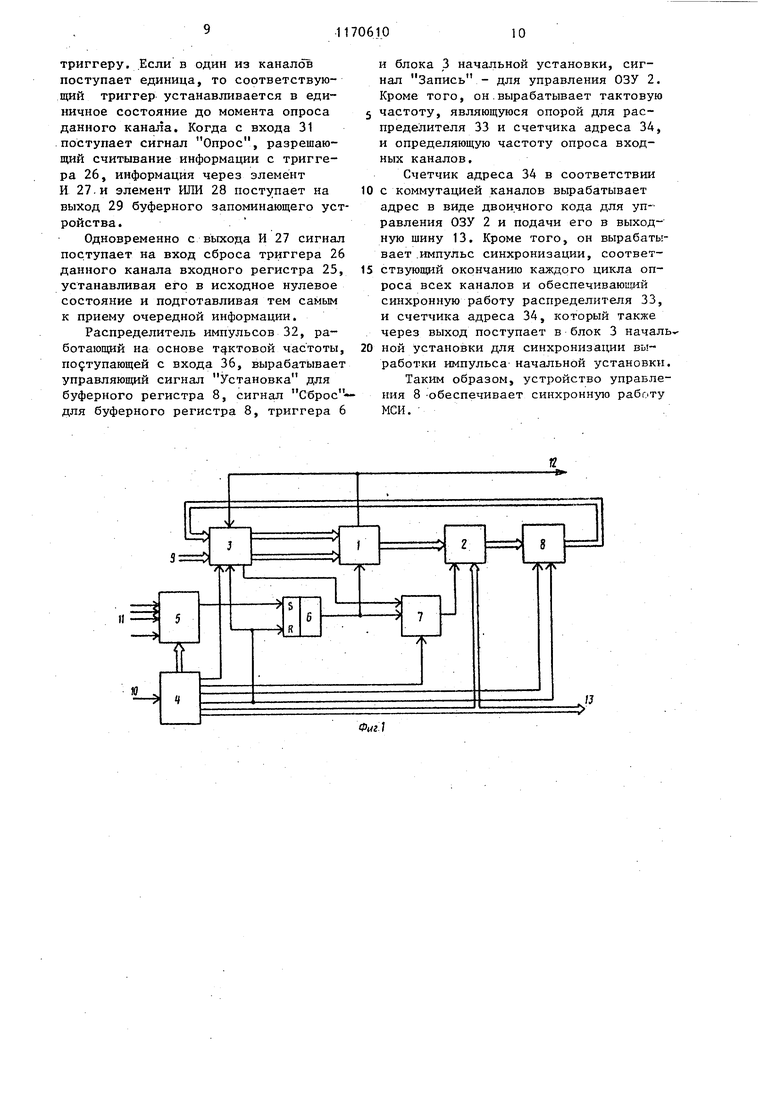

Устройство управления 4 содержит первьш 32 и второй 33 распределители и счетчик адреса 34, выходы которого являются адресным выходом 35 устройства управления, тактовый вход 36 которого соединен с тактовым входом первого распределителя 32, выходы которого соединены с выходами установки 37, вспомогательным 38 и дополнительным 39 выходами устройства управления 4 и входом счетчика адреса 34, который соединен с тактовым входом второго распределителя 33, выходы которого и выход счетчика адреса 34 являются управ1ляющими выходами 40 устройства управления .

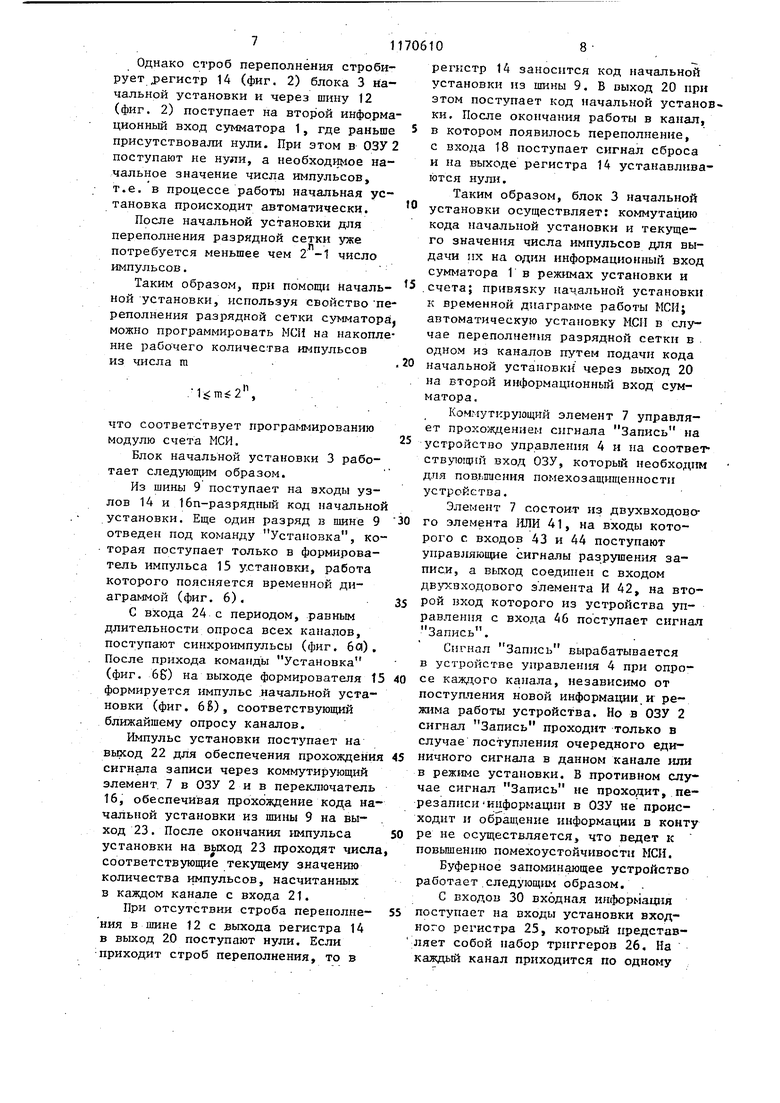

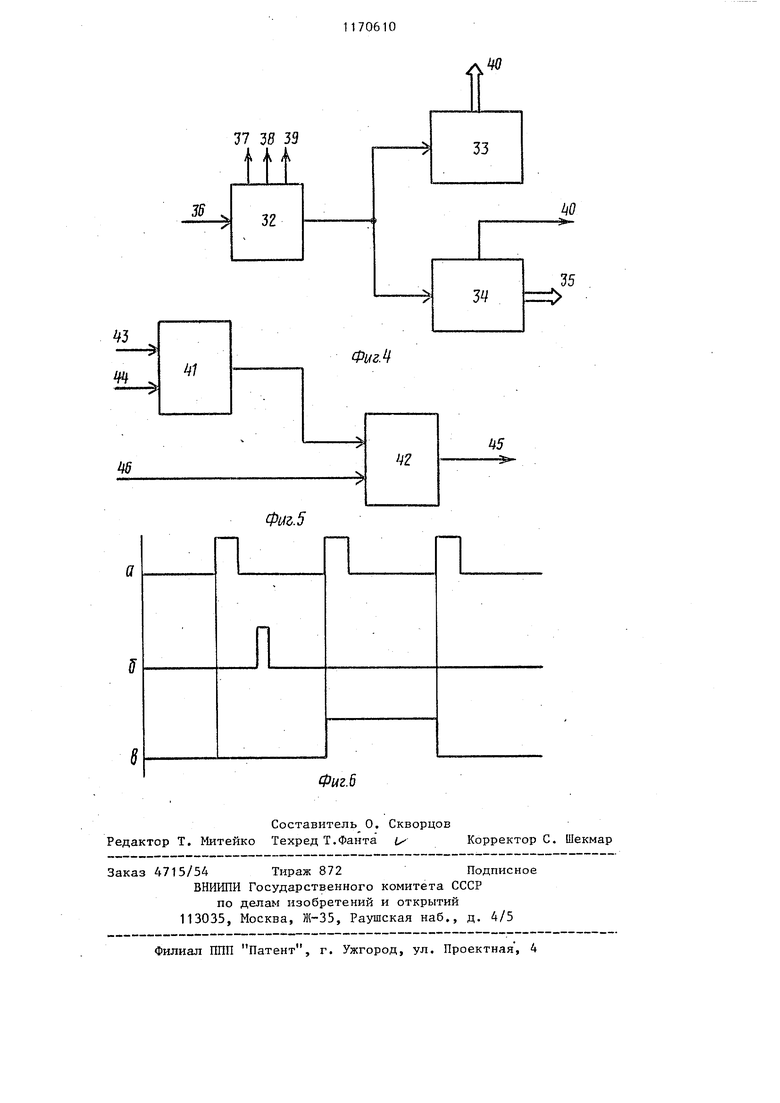

Коммутирующий элемент 7 содержит элемент ИЛИ 41 и дополнительный элемент И 42, первый и второй входы элемента ИЛИ 41 соединены с первым 43 и вторым 44 входами коммутирующего элемента 7, выход элемента ИЛИ 41 соединен с первым входом дополнитель ного элемента iH 42, выход и второй вход которого соединены соответственно с выходом 45 и третьим входом 46 коммутирующего элемента. Сумматор 1 представляет собой двончный сумматор, имеющий два п-разрядных входа, вход переноса, выход, переноса и один п-разрядный выход, и может осуществлять двоичное суммирование двух п-разрядных чисел и сигнала на входе переноса, соответствз щвго младшему разряду. В случае переполнения разрядной сетки на выходе переноса появляется сигнал, используемый как строб переполнения. Оперативное запоминающее устройство (ОЗУ) 2 является устройством памяти, емкостью nxN бит, где N число каналов, и имеет п-разрядные информационш 1е вход и выход. В ОЗУ хранится-текущая информация по ззсем каналгхм. Выбор адреса осуществляется при помощи кода адреса, вырабаты ваемого в устройстве управления 4. Буферньш регистр 8 необходим для обеспечения высокой помехозаа(ищенности устройства по выходу переполнения и осуществляет временную задержку поступления сигнала с выхода ОЗУ 2 на вход сумматора 1 через бло 3 начальной установки для устранения влияния переходных процессов на ОЗУ 2. Многоканальный счетчик имщльсрв работает следующим образом. Входная информация сначала запоминается в буферном запоминающем ус ройстве 5, затем раздельно во време по всем каналам переписьшается в триггер 6. Прикоммутации очередного канала в устройстве управления 4 формирует адрес, соответствующий данному кана лу, который подается в шину 13 и на адресные входы ОЗУ 2. При этом прои ходит считывание из ОЗУ 2 текущей информации по данному адресу, котор по команде Установка из устройств управления 4 записывается в буферны регистр 8. Далее считанная информация через блок начальной установки подается на информационный вход сум матора -1, на вход переноса которого подается вновь поступившая информация с триггера 6. Если поступил еди ничньй сигнал, то текущее значение числа импульсов в сумматоре 1 вели чивается на единицу младшего разряда Единица на выходе триггера 6 также разрешает прохождение сигнала Запись через коммутирующий элемент 7 и в ОЗУ 2 записывается новое значение числа импульсов по данному адресу. После записи в буферный регистр 8 и триггер 6-из устройства управления 4 поступает сигнал сброса, устанавливающий их в исходное состояние и подготавливающий их к работе по очередному каналу. Затем по команде из устройства управления 4 осуществляется-коммутация очередного .канала и устанавливается соответствующий ему адрес. Если к моменту опроса данного канала сигнал на вход не поступил, то в триггер 6 переписывается О (иначе он остается и нулевом состоянии) , суммирования не происходит и сигнал Запись через коммутирующий элемент 7 не проходит. В ОЗУ 2 при этом по данному адресу сохраняемся старая информация. При поступлении из шины 9 в соответствующем разряде команды Начальная установка в блоке 3 начальной установки в соответствии с временной диаграммой (фиг, 6) формируется импульс начальной установки и на информационный вход сумматора 1 подается не текущая информация, -а код начальной установки из шины 9, который и записывается в ячейки ОЗУ 2. Импульс начальной установки из блока 3 начальной установки поступает на соответствующий управляющий вход коммутирующего элемента 7 и разрешает прохождение сигнала Запись в ОЗУ 2. Опрос каналов при этом не прекращается, входная информация поступает на входпереноса сумматора 1 и Потерь информации не происходит. Максимальное количество -импyльcoвJ которое может быть накоплено в каж-- дом канале, составляет , где п - разрядность информационного контура. При поступлении очередного 2 -го импульса сумматор 1 переполняется, на его выходе переноса появляется строб переполнения-, который подается в выходную шину 12 и блок 3 начальной установки. Во всех разрядах на выходе сумматора 1 при переполнении должны появиться нули. Однако строб переполнения строби рует регистр 14 (фиг. 2) блока 3 на чальной установки и через шину 12 (фиг. 2) поступает на второй информ ционный вход сумматора 1, где раньш присутствовали нули. При этом в ОЗУ поступают не нули, а необходщюе на чальное значение числа импульсов, т.е. в процессе работы начальная ус тановка происходит автоматически. После начальной установки для переполнения разрядной сетки уже потребуется меньшее чем 2-1 число импульсов. Таким образом, при помощи Началь ной установки, используя свойство п реполнения разрядной сетки сумматор можно программировать МСИ на накопл ние рабочего количества импульсов из числа га .что соответствует программированию модулю счета МСИ. Блок начальной установки 3 работает следующим образом. Из шины 9 поступает на входы узлов 14 и 16п-разрядный код начально установки. Еще один разряд в шине 9 отведен под команду Установка, ко торая поступает только в формирователь импульса 15 установки, работа которого поясняется временной диаграммой (фиг. 6). С входа 24 с периодом, равным длительности опроса всех каналов, поступают синхроимпульсы (фиг. ) . После прихода команды Установка (фиг. 6S) на выходе формирователя 1 формируется импульс .начальной установки (фиг. 68), соответствующий ближайшему опросу каналов. Импульс установки поступает на выход 22 для обеспечения прохождени сигнала записи через коммутирующий элемент. 7 в ОЗУ 2 и в переключатель 16, обеспечивая прохождение кода на чальной установки из шины 9 на выход 23. После окончания импульса установки на выход 23 проходят числ соответствующие текущему значению количества импульсов, насчитанных в каждом канале с входа 21. При отсутствии строба переиолне- ния в шине 12 с выхода регистра 14 в выход 20 поступают нули. Если приходит строб переполнения, то в регистр 14 заносится код начальной установки из шины 9. В выход 20 при этом поступает код начальной установки. После окончания работы в канал, в котором появилось переполнение, с входа 18 поступает сигнал сброса и на выходе регистра 14 устанавливаются нули. Таким образом, блок 3 начальной установки осуществляет: коммутацию кода начальной установки и текущего значения числа импульсов для выдачи их на один информационный вход сумматора Г в режимах установки и счета; привязку начальной установки к временной диаграмме работы МСИ; автоматическую установку МСИ в случае переполнения разрядной сетки в одном из каналов путем подачи кода начальной установки через выход 20 на второй информационный вход сумматора. Коммутирующий элемент 7 управляет прохождением сигнала Запись на устройство управления 4 и на соответCTByioiqjn вход ОЗУ, которьй необходим для повышения помехозащищенности устройства. Элемент 7 состоит из двухвходового элемента ИЛИ 41, на входы которого с входов 43 и 44 поступают управляющие сигналы разрушения записи, а выход соединен с входом двухвходового элемента И 42, на второй вход которого из устройства управления с входа 46 поступает сигнал Запись. Сигнал Запись вырабатывается в устройстве управления 4 при опросе казвдого капала, независимо от поступления новой информации,и режима работы устройства. Но в ОЗУ 2 сигнал Запись проходит только в случае поступления очередного единичного сигнала в данном канапе или в режиме установки. В противном случае сигнал Запись не проходит, перезаписи информации в ОЗУ не происходит и обращение информации в конту ре не осуществляется, что редет к повьппению помехоустойчивости ЫСИ. Буферное запоминающее устройство работает .следующим образом. . С входов 30 входная инс}юрмацня поступает на входы установки входного регистра 25, который представляет собой набор триггеров 26. На каждый канал приходится по одному

триггеру. Если в один из каналов поступает единица, то соответствующий триггер устанавливается в единичное состояние до момента опроса данного канала. Когда с входа 31 поступает сигнал Опрос, разрешающий считывание информации с триггера 26, информация через элемент И 27.и элемент ИЛИ 28 поступает на выход 29 буферного запоминающего устройства.

Одновременно с выхода И 27 сигнал поступает на вход сброса триггера 26 данного канала входного регистра 25, устанавливая его в исходное нулевое состояние и подготавливая тем самым к приему очередной информации.

Распределитель импульсов 32, работающий на основе тактовой частоты, поступающей с входа 36, вырабатывает управляющий сигнал Установка для буферного регистра 8, сигнал Сброс - для буферного регистра 8, триггера 6

и блока 3 начальной установки, сигнал Запись - для управления ОЗУ 2. Кроме того, он.вырабатывает тактовую 5 частоту, являющуюся опорой для распределителя 33 и счетчика адреса 34, и определяющую частоту опроса входных каналов.

Счетчик адреса 34 в соответствии

10 с коммутацией каналов вырабатывает адрес в виде двоичного кода для управления ОЗУ 2 и подачи его в выходную шину 13. Кроме того, он вырабатывает .импульс синхронизации, соответствующий окончанию каждого цикла опроса всех каналов и обеспечивающий синхронную работу распределителя 33, и счетчика адреса 34, который также через выход поступает в блок 3 начал

20 ной установки для синхронизации вы работки импульса начальной установки Таким образом, устройство управления 8 -обеспечивает синхронную работу

мси.

37 30 33

Фм.5

| Многоканальный счетчик импульсов | 1976 |

|

SU594586A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шутков Е.И | |||

| и др | |||

| Многоканальный счетчик импульсов | |||

| Л.: Энергия, 1971, с | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-07-30—Публикация

1983-09-30—Подача