Изобретение относится к области радиотехники, в частности к системам связи с широкополосными сигналами, в которых расширение спектра осуществляется манипуляцией фазы сигнала по закону псевдослучайной последовательности (ПСП). Такие сигналы находят широкое применение в системах связи с кодовым разделением каналов (CDMA). Системы связи с CDMA имеют значительные преимущества в аспектах емкости, частотного планирования, скрытности, защиты от помех и развиваются наиболее быстро по сравнению с другими системами.

Отличительной особенностью систем связи CDMA является необходимость точной временной синхронизации между входным и опорным сигналами. Процесс достижения синхронизации основан на вычислении значений корреляции между входным и опорным сигналами при различных значениях относительного временного сдвига между ними. Область неопределенности временных задержек в системах связи CDMA может быть весьма значительной. Поэтому процесс установления синхронизации связан со значительными аппаратными и временными затратами.

Наиболее эффективными способами приема в этих условиях являются способы и устройства, основанные на применении многоканальных корреляторов и согласованных фильтров, позволяющих значительно ускорить процесс установления синхронизации, а также осуществлять прием широкополосного сигнала в условиях неопределенности его задержки. При этом во многих случаях отдается предпочтение способам и устройствам, основанным на обработке сигнала в полосе видеочастот [1.Andrew J. Viterbi, CDMA Principles of Spread Spectrum Communication. Addison-Wesley Communication Series. 1995], [2. E. A. Sourour, S.C. Gupta. Direct Sequence Spread-Spectrum Parallel Acquisition in a Fading Mobile Channel. IEEE Transactions on Communications, Vol. 38, N 7, Yuly, 1990].

Такие способы и устройства легко сочетаются с цифровыми методами обработки сигнала, которые дают широкие возможности применения современной технологии проектирования и позволяют разрабатывать дешевое компактное оборудование систем связи с высокими техническими характеристиками.

Наиболее общий способ приема сигнала [1. Andrew J. Viterbi, CDMA Principles of Spread Spectrum Communication. Addison-Wesley Communication Series. 1995] в этом случае состоит в том, что входной сигнал демодулируется, при этом в условиях неопределенности фазы входного сигнала образуются два канала его последующей обработки - синфазный и квадратурный. Демодулированный сигнал в синфазном и квадратурном каналах дискретизируется по времени и преобразуется в цифровую форму. Затем в обоих каналах вычисляется корреляция между входным и опорным сигналами для каждого значения относительного временного сдвига между ними. Оценка корреляции для каждого из значений относительного временного сдвига формируется путем суммирования соответствующих квадратичных значений корреляции, полученных в синфазном и квадратурном каналах. Из множества полученных значений оценки корреляции выбирается максимальная величина и сравнивается с порогом. После этого принимается решение об отсутствии или наличии сигнала со значением временной задержки, соответствующей максимальному сигналу. Значения корреляции, полученные в синфазном и квадратурном каналах, могут использоваться для формирования оценок других параметров сигнала, например амплитуды, фазы или частоты.

Реализация такого способа может быть основана на применении согласованного фильтра, который представляет собой устройство памяти типа линии задержки или регистра сдвига с отводами. На тактовые входы устройства памяти подаются тактовые импульсы с частотой, большей или равной частоте следования элементарных символов (чипов) ПСП. Входной сигнал поступает на вход устройства памяти и перемещается на одну ячейку по направлению к выходу при поступлении каждого тактового импульса. При этом на отводах устройства памяти формируются копии отсчетов сигнала, задержанные друг относительно друга на период тактовых импульсов. Сигналы с отводов устройства памяти перемножаются на соответствующие значения отсчетов опорного сигнала. Результаты перемножения суммируются. Таким образом, при поступлении каждого тактового импульса на выходе сумматора формируется величина корреляции между входным и опорным сигналами при соответствующем относительном временном сдвиге.

При использовании в системе связи двухфазных сигналов (BPSK) описанное выше устройство устанавливается в синфазном и квадратурном каналах, образуя две ветви согласованной фильтрации. При использовании 4-фазных (QPSK) и многофазных сигналов для реализации согласованного фильтра описанным методом также требуются 2 ветви согласованной фильтрации - по одной в синфазном и квадратурном каналах. Однако при этом необходимо использовать комплексное перемножение отсчетов входного и опорного сигналов, что потребует введения четырех перемножителей увеличенной разрядности и усложнения генератора опорного сигнала.

В свою очередь сложность реализации одной ветви согласованного фильтра увеличивается с увеличением тактовой частоты ПСП, длины линии задержки и разрядности представления отсчетов сигнала, так как приводит к увеличению количества операций умножения и суммирования, которые требуется выполнить за малый промежуток времени между двумя тактовыми импульсами. Поскольку развитие и совершенствование систем связи CDMA осуществляется в направлении увеличения полосы частот, а также предполагает использование фазоманипулированных сигналов с количеством уровней квантования фазы 4 и более, то непосредственная реализация такого способа приводит к очень сложному техническому решению и задача снижения сложности реализации является весьма актуальной.

Наиболее известный способ снижения сложности реализации согласованного фильтра состоит в сокращении разрядности представления входного сигнала. Однако представление сигнала одним-двумя битами приводит к снижению эффективности приема и в то же время не устраняет необходимость иметь несколько ветвей согласованной фильтрации при обработке многофазных сигналов.

В патенте [3. Патент US 3831013 CORRELATORS USING SHIFT REGISTERS, August, 20, 1974] предлагается упростить реализацию согласованного фильтра за счет аналогового метода выполнения операции суммирования. Недостатком такого решения является то, что при необходимости проводить оценки параметров сигнала (фазы, частоты, амплитуды) может потребоваться обратное цифроаналоговое преобразование, что усложняет реализацию. Кроме того, при использовании в системе многофазных сигналов сложность реализации этого решения значительно увеличивается, так как появляется необходимость увеличивать количество ветвей согласованной фильтрации.

Известен также способ [4. Патент US 5184135 Phase measurement of received pseudonoise sequence using digital correlation], [5. Патент US 5566202 System using a split correlator for frequency compensating a phase modulated pseudonoise sequence signal], позволяющий упростить реализацию согласованного фильтра за счет сокращения разрядности представления демодулированного сигнала. Данный способ предполагает использовать квантование фазы сигнала на 2S (S=1,2,...) уровней, а затем представлять отсчеты синфазной и квадратурной составляющих демодулированного сигнала цифровыми значениями в зависимости от величины фазы. При этом появляется возможность снизить количество разрядов цифровых отсчетов сигнала при незначительном снижении эффективности.

Наиболее близким к заявляемому решению является патент [4. Патент US 5184135 Phase measurement of received pseudonoise sequence using digital correlation] . Данный способ приема широкополосного сигнала заключается в том, что

1. осуществляют квадратурную демодуляцию принимаемого сигнала, формируя синфазную и квадратурную составляющие комплексного входного сигнала,

2. осуществляют дискретизацию по времени синфазной и квадратурной составляющих комплексного входного сигнала, образуя последовательность отсчетов комплексного входного сигнала,

3. по последовательности отсчетов комплексного входного сигнала формируют последовательность цифровых значений фазы комплексного входного сигнала, причем квантование фазы осуществляют на n=2S уровней (S > 1 - целое число), затем по каждому значению фазы определяют соответствующую пару чисел, представляющих цифровые значения синфазной и квадратурной составляющих входного сигнала, формируя, таким образом, последовательность цифровых отсчетов комплексного входного сигнала,

4. формируют последовательность цифровых отсчетов комплексного опорного сигнала,

5. вычисляют множество L значений комплексной корреляции между входным и опорным сигналами путем перемножения и суммирования комплексных цифровых отсчетов входного и опорного сигналов на интервале обнаружения сигнала при L возможных значениях относительного временного сдвига между ними, при этом

6. формируют последовательность комплексных значений корреляции между входным и опорным сигналами для L значений относительного временного сдвига между ними путем изменения относительного временного сдвига между входным и опорным сигналами и повторения операций перемножения и суммирования комплексных цифровых отсчетов входного и опорного сигналов на интервале обнаружения сигнала,

7. по каждому комплексному значению корреляции вычисляют действительную оценку корреляции, которую сравнивают с заданной величиной порога и по результатам сравнения принимают решение об обнаружении или отсутствии сигнала.

Блок-схема устройства для реализации данного способа представлена на фиг. 1 и содержит последовательно соединенные блок обработки высокочастотного сигнала 1 и квадратурный демодулятор 2, а также квантователь фазы 3, цифровой коррелятор 4, векторный сумматор 13 и решающую схему 14. Первый выход цифрового коррелятора 4 соединен с синфазным входом ZI векторного сумматора 13 и вторым входом решающей схемы. Второй выход цифрового коррелятора 4 соединен с квадратурным входом ZQ векторного сумматора 13 и первым входом решающей схемы 14. Выход векторного сумматора 13 соединен с третьим входом решающей схемы 14, выход которой является выходом устройства. Цифровой коррелятор 4 содержит регистры сдвига 5 и 10 синфазного I и квадратурного Q каналов, L выходов каждого из которых соединены соответственно с каждым из L входов первого множества входов соответствующего блока побитовых компараторов 6 или 9, каждый из L входов второго множества L входов каждого из блоков побитовых компараторов 6 или 9 соединен с соответствующим выходом регистра опорного сигнала 8. Выходы каждого из блоков побитовых компараторов 6 и 9 соединены c L входами сумматоров 11 и 12 соответственно, причем выход первого сумматора 11 является первым, а выход второго сумматора 12 - вторым выходами цифрового коррелятора 4.

Недостатком данных способа и устройства является, во- первых, снижение эффективности приема. Это связано с тем, что при формировании цифровых отсчетов синфазной и квадратурной составляющих демодулированного сигнала используется только информация о фазе сигнала, а информация об амплитуде не учитывается. Во-вторых, при применении данного способа для обработки сигналов с многофазной манипуляцией (QPSK, 8-PSK, 16-PSK и т. д.) сложность реализации значительно увеличивается, так как возрастает количество ветвей согласованной фильтрации.

Задача, которую решает предлагаемое изобретение, позволяет значительно упростить алгоритм приема широкополосных фазоманипулированных сигналов при сохранении высокой эффективности приема.

Для решения этой задачи в способ, заключающийся в том, что осуществляют квадратурную демодуляцию входного сигнала, формируя синфазную и квадратурную составляющие комплексного входного сигнала, осуществляют дискретизацию по времени синфазной и квадратурной составляющих комплексного входного сигнала, образуя последовательность отсчетов комплексного входного сигнала, формируют последовательность цифровых отсчетов комплексного опорного сигнала, вычисляют комплексные значения корреляции между комплексным входным и комплексным опорным сигналами при каждом из L возможных значений относительного временного сдвига между ними, образуя L комплексных значений корреляции, по каждому комплексному значению корреляции вычисляют действительную оценку корреляции, которую сравнивают с заданной величиной порога, и по результатам сравнения принимают решение об обнаружении или отсутствии сигнала,

дополнительно вводят следующие операции:

осуществляют квантование последовательности отсчетов комплексного входного сигнала, представляя каждый отсчет последовательности отсчетов комплексного входного сигнала в виде пары цифровых значений соответственно фазы и амплитуды, причем квантование фазы на интервале от 0 до 2π радиан производят на n ≥ 2 уровней, а квантование амплитуды - на m ≥ 1 уровней, осуществляют квантование последовательности отсчетов комплексного опорного сигнала, формируя последовательность цифровых значений фазы комплексного опорного сигнала, при этом квантование фазы на интервале от 0 до 2π радиан осуществляют также на n уровней, суммируют по модулю n цифровое значение фазы каждого отсчета из последовательности отсчетов комплексного входного сигнала с соответствующим ему цифровым значением фазы комплексного опорного сигнала, формируя последовательность отсчетов суммарных значений фазы, суммируют цифровые значения амплитуд отсчетов последовательности отсчетов комплексного входного сигнала, имеющих одинаковые отсчеты суммарных значений фазы, формируя суммарные величины, каждая из которых соответствует одному из n уровней суммарных значений фазы, каждое из L комплексных значений корреляции вычисляют путем весового суммирования сформированных значений суммарных величин, при этом сначала суммируют каждую из этих величин с весом, равным косинусу соответствующего суммарного значения фазы, формируя синфазную составляющую комплексного значения корреляции, затем с весом, равным синусу соответствующего суммарного значения фазы, формируя квадратурную составляющую комплексного значения корреляции.

Для решения этой же задачи разработано четыре варианта устройства, реализующих предлагаемый способ.

В устройство приема широкополосного сигнала по первому варианту, содержащее последовательно соединенные блок обработки высокочастотного сигнала, вход которого является входом устройства, и квадратурный демодулятор, а также векторный сумматор и решающую схему, третий вход которой соединен с выходом векторного сумматора, а выход решающей схемы является выходом устройства, дополнительно введены блок квантования фазы и амплитуды, формирователь суммарных величин и весовой сумматор, причем каждый из k входов весового сумматора соединен с соответствующим ему выходом формирователя суммарных величин, выходы I и Q квадратурного демодулятора соединены с соответствующими им входами блока квантования фазы и амплитуды, первый и второй выходы которого соединены с соответствующими входами формирователя суммарных величин, а первый и второй выходы весового сумматора соединены соответственно с синфазным и квадратурным входами векторного сумматора, а также с первым и вторым входами решающей схемы соответственно.

В устройство приема широкополосного сигнала по второму варианту, содержащее последовательно соединенные блок обработки высокочастотного сигнала, вход которого является входом устройства, и квадратурный демодулятор, а также векторный сумматор и решающую схему, третий вход которой соединен с выходом векторного сумматора, а выход решающей схемы является выходом устройства, дополнительно введены блок квантования фазы и амплитуды, блок формирования суммарных величин, блок суммирования и весовой сумматор, причем блок формирования суммарных величин содержит М формирователей суммарных величин, первый и второй входы каждого из которых, начиная со второго, соединены соответственно с первым и втором выходами предыдущего формирователя суммарных величин, а первый и второй входы первого формирователя суммарных величин являются входами блока формирования суммарных величин и соединены с первым и вторым выходами блока квантования фазы и амплитуды, блок суммирования содержит k сумматоров, при этом k выходов каждого из М формирователей суммарных величин соединены с входами каждого из k сумматоров блока суммирования таким образом, что j-й выход i-го формирователя суммарных величин соединен с i-м входом j-го сумматора блока суммирования, выход каждого из k сумматоров блока суммирования соединен с соответствующим входом весового сумматора, первый и второй выходы которого соединены с синфазным и квадратурным входами векторного сумматора, а также с первым и вторым входами решающей схемы соответственно.

В устройство приема широкополосного сигнала по третьему варианту, содержащее последовательно соединенные блок обработки высокочастотного сигнала, вход которого является входом устройства, и квадратурный демодулятор, а также векторный сумматор и решающую схему, третий вход которой соединен с выходом векторного сумматора, а выход решающей схемы является выходом устройства, дополнительно введены блок квантования фазы и амплитуды, М формирователей суммарных величин и соответственно им М весовых сумматоров, блок суммирования, причем первый и второй входы каждого из М формирователей суммарных величин, начиная со второго, соединены с соответствующими им первым и вторым выходами предыдущего формирователя суммарных величин, а первый и второй входы первого формирователя суммарных величин соединены с соответствующими им первым и вторым выходами блока квантования фазы и амплитуды, каждый из k выходов каждого формирователя суммарных величин соединен с соответствующим ему входом соответствующего весового сумматора, а блок суммирования содержит два сумматора с М входами и одним выходом каждый, причем каждый j-й вход первого сумматора соединен с синфазным выходом j-го весового сумматора, а каждый j-й вход второго сумматора соединен с квадратурным выходом j-го весового сумматора, выходы первого и второго сумматоров блока суммирования соединены соответственно с синфазным и квадратурным входами векторного сумматора, а также с первым и вторым входами решающей схемы.

В устройство приема широкополосного сигнала по четвертому варианту, содержащее последовательно соединенные блок обработки высокочастотного сигнала, вход которого является входом устройства, и квадратурный демодулятор, а также решающую схему, выход которой является выходом устройства, дополнительно введены блок квантования фазы и амплитуды, М формирователей суммарных величин и соответственно им М весовых и М векторных сумматоров, а также сумматор с М входами и одним выходом, первый и второй входы каждого из М формирователей суммарных величин, начиная со второго, соединены соответственно с первым и вторым выходами предыдущего формирователя суммарных величин, а входы первого формирователя суммарных величин соединены с соответствующими первым и вторым выходами блока квантования фазы и амплитуды, каждый из k выходов каждого формирователя суммарных величин соединен с соответствующим ему входом соответствующего весового сумматора, а первый и второй выходы каждого весового сумматора соединены соответственно с синфазным и квадратурным входами соответствующего векторного сумматора и соответствующим входом решающей схемы, а выход каждого из М векторных сумматоров соединен с соответствующим входом сумматора, выход которого соединен с первым входом решающей схемы.

Сопоставительный анализ способа приема широкополосного сигнала с прототипом показывает, что предлагаемое изобретение существенно отличается от прототипа, так как позволяет значительно упростить алгоритм приема широкополосных фазоманипулированных сигналов при сохранении высокой эффективности приема.

Сопоставительный анализ заявляемого способа с другими техническими решениями в данной области техники не позволил выявить признаки, заявленные в отличительной части формулы изобретения. Следовательно, заявляемый способ приема широкополосного сигнала отвечает критериям "новизна", "техническое решение задачи", "существенные отличия" и обладает неочевидностью решения.

Сравнение вариантов заявляемого устройства приема широкополосного сигнала с другими известными техническими решениями в данной области техники не позволило выявить признаки, заявленные в отличительной части формулы изобретения, следовательно, предлагаемое изобретение также отвечает критериям изобретения: "новизна", "техническое решение задачи", "существенные отличия" и обладает неочевидностью.

Графические материалы, поясняющие предлагаемое изобретение.

Фиг. 1 - блок-схема устройства-прототипа.

Фиг. 2 - блок-схема первого варианта предлагаемого устройства.

Фиг. 3 - пример выполнения формирователя суммарных величин.

Фиг. 4 - пример выполнения сумматора амплитуд в составе формирователя суммарных величин.

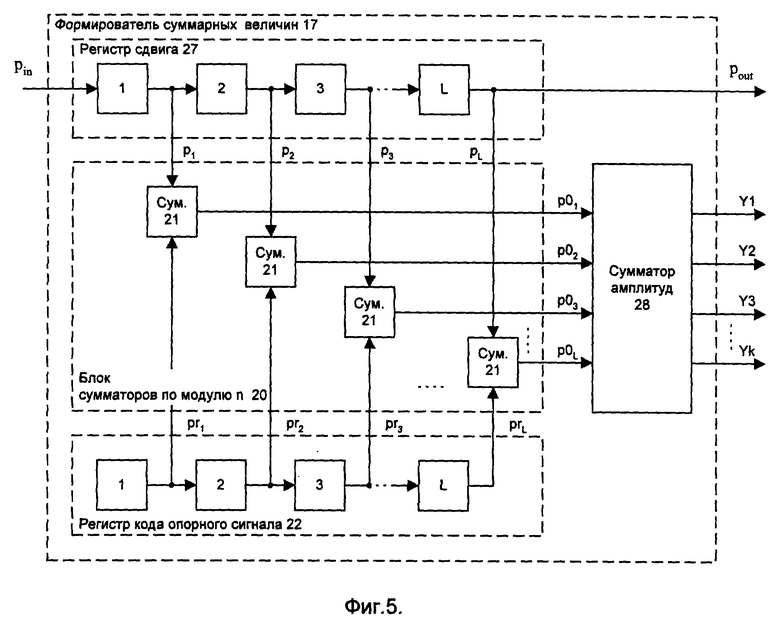

Фиг. 5 - пример выполнения формирователя суммарных величин при уровне квантования амплитуды m=1.

Фиг. 6 - пример выполнения сумматора амплитуд в составе формирователя суммарных величин при одном (m=1) уровне квантования амплитуды.

Фиг. 7 - пример выполнения весового сумматора.

Фиг. 8 - значения кода фазы в координатной плоскости для двух случаев квантования.

Фиг. 9 - пример выполнения блока квантования фазы и амплитуды.

Фиг. 10 - таблица истинности для формирователя кода фазы.

Фиг. 11 - блок-схема второго варианта предлагаемого устройства.

Фиг. 12 - блок-схема третьего варианта предлагаемого устройства.

Фиг. 13 - блок-схема четвертого варианта предлагаемого устройства.

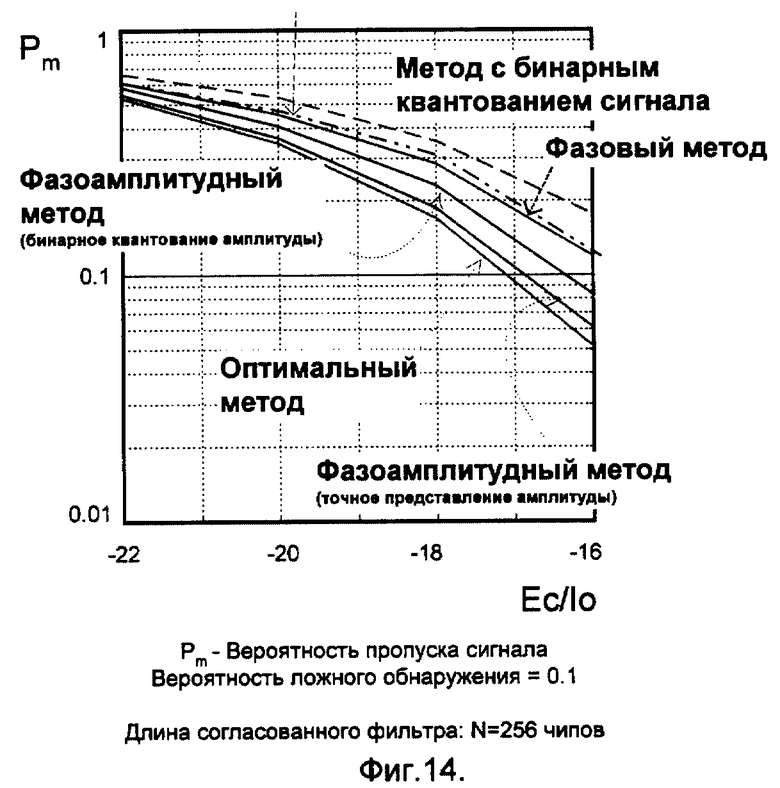

Фиг. 14 - зависимость вероятности пропуска сигнала от входного отношения сигнал/шум.

Фиг. 15 - результаты моделирования фазового метода корреляции.

Предлагаемый способ заключается в следующем.

1. Осуществляют квадратурную демодуляцию входного сигнала, формируя синфазную и квадратурную составляющие комплексного входного сигнала.

2. Осуществляют дискретизацию по времени синфазной и квадратурной составляющих комплексного входного сигнала, образуя последовательность отсчетов комплексного входного сигнала.

3. Осуществляют квантование последовательности отсчетов комплексного входного сигнала, представляя каждый отсчет последовательности отсчетов комплексного входного сигнала в виде пары цифровых значений соответственно фазы p и амплитуды а, где p и а целые числа, причем квантование фазы на интервале от 0 до 2π радиан производят на n ≥ 2 уровней, а квантование амплитуды - на m ≥ 1 уровней.

4. Формируют последовательность цифровых отсчетов комплексного опорного сигнала.

5. Осуществляют фазовое квантование последовательности отсчетов комплексного опорного сигнала, определяя при этом цифровое значение фазы pr, формируя таким образом последовательность цифровых значений фазы комплексного опорного сигнала, при этом квантование фазы на интервале от 0 до 2π радиан осуществляют на n уровней.

6. Вычисляют комплексные значения корреляции между комплексным входным и комплексным опорным сигналами путем формирования суммарных величин последовательностей отсчетов входного и опорного сигналов и последующего весового суммирования результатов при каждом из L возможных значений относительного временного сдвига между ними, образуя L комплексных значений корреляции, при этом

формирование суммарных величин последовательностей отсчетов входного и опорного сигналов выполняют, суммируя по модулю n цифровое значение фазы p каждого отсчета из последовательности отсчетов комплексного входного сигнала с соответствующим ему цифровым значением фазы pr комплексного опорного сигнала, формируя, таким образом, последовательность отсчетов суммарных значений фазы p0, а также суммируют цифровые значения амплитуд а отсчетов последовательности отсчетов комплексного входного сигнала, имеющих одинаковые отсчеты суммарных значений фазы p0, формируя суммарные величины (Y1,.. . ,Yn), каждая из которых соответствует одному из n уровней суммарных значений фазы p0,

- весовое суммирование полученных значений суммарных величин Y1,...,Yn выполняют с весами, равными соответственно косинусам значений фазы, соответствующих каждому из n уровней квантования фазы (cosϕ1...cosϕn), образуя таким образом синфазную составляющую комплексной корреляции, а также с весами, равными соответственно синусам значений фазы, соответствующих каждому из n уровней квантования фазы (sinϕ1...sinϕn), формируя таким образом квадратурную составляющую комплексной корреляции.

7. По каждому комплексному значению корреляции вычисляют действительную оценку корреляции, которую сравнивают с заданной величиной порога, и по результатам сравнения принимают решение об обнаружении или отсутствии сигнала.

Основная идея заявляемого способа состоит в таком представлении сигнала, которое позволяет значительно упростить операцию формирования корреляции между входным и опорным сигналами. Обычно демодулированный сигнал представляют комплексным числом I+j•Q.

При вычислении корреляции между входным и опорным сигналами выполняются операции комплексного умножения и суммирования комплексных отсчетов входного и опорного сигналов. При реализации такого способа вычисления корреляции, во-первых, количество операций умножения велико, причем это количество увеличивается при использовании многофазных сигналов (QPSK, 8-PSK и т. д.), во-вторых, требуется достаточно высокая разрядность представления множителей.

Демодулированный сигнал можно представить в экспоненциальной форме A•exp(j•ϕ). При таком представлении сигнала умножение отсчетов выполняется за счет умножения амплитуд и сложения фаз. При использовании фазоманипулированных сигналов амплитуда опорного сигнала постоянна, поэтому операция умножения амплитуд входного и опорного сигналов исключается из процесса обработки сигнала. При этом умножение отсчетов входного и опорного сигналов сводится только к сложению фаз, причем количество операций сложения не зависит от количества уровней фазы фазоманипулированного сигнала (QPSK, 8-PSK и т. д.). В заявляемом способе предлагается квантовать значения фазы на n ≥ 2 уровней. В предпочтительном способе реализации выбирается n = 2S. При этом величина фазы представляется S-разрядным двоичным числом. Тогда суммирование значений фазы сведется к чрезвычайно простой операции сложения целых чисел по модулю n.

При выполнении последующих операций обработки результатов перемножения используется весовое суммирование с весами, равными синусам и косинусам фактических значений фазы, соответствующих каждому из n цифровых значений фазы. Заявляемый способ предполагает возможность двух вариантов вычисления - с использованием значений амплитуды входного сигнала и без использования значений амплитуд - фазовый метод корреляции. Фазовый метод корреляции является частным случаем метода с использованием значений амплитуды входного сигнала и соответствует одному уровню квантования амплитуды (m=1). Он приводит к более простому техническому решению, однако дает незначительный проигрыш по эффективности (фиг. 14).

Таким образом, преимущество заявляемого способа состоит в следующем.

Во-первых, операция умножения отсчетов входного и опорного сигналов заменяется на более простую операцию сложения по модулю n, где n - количество уровней квантования фазы.

Во-вторых, канал согласованной фильтрации - задержки, умножения и суммирования - всегда один независимо от количества уровней фазы фазоманипулированных сигналов. При использовании обычного способа [1. Andrew J. Viterbi, CDMA Principles of Spread Spectrum Communication. Addison-Wesley Communication Series. 1995] или способа-прототипа [4. Патент US 5184135 Phase measurement of received pseudonoise sequence using digital correlation] для сигналов QPSK требуется 4 канала, для сигналов 8-PSK - 8 каналов и т. д.

В-третьих, использование квантованных значений амплитуды дает выигрыш в эффективности по сравнению со способом [4. Патент US 5184135 Phase measurement of received pseudonoise sequence using digital correlation], в котором информация об амплитуде не используется.

Предлагаемый способ можно реализовать несколькими вариантами устройств.

Первый вариант устройства приема широкополосного сигнала для реализации заявляемого способа представлен на фиг. 2 и содержит последовательно соединенные блок обработки высокочастотного сигнала 1, вход которого является входом устройства, и квадратурный демодулятор 2, два выхода которого, соответствующие синфазной I и квадратурной Q составляющим входного сигнала, соединены с соответствующими входами блока квантования фазы и амплитуды 15, выходы амплитуды а и фазы p которого соединены с аin и pin входами формирователя суммарных величин 17, и весовой сумматор 18, k входов (Y1, Y2,...,Yk) которого соединены с соответствующими выходами фазоамплитудного сумматора 17, причем количество k выходов фазоамплитудного сумматора 17 зависит от количества уровней квантования фазы сигнала n. Выходы синфазного ZI и квадратурного ZQ значений корреляции весового сумматора 18 соединены с соответствующими входами векторного сумматора 13 и решающей схемы 14, причем выход Z векторного сумматора 13 соединен с соответствующим входом решающей схемы 14, выход которой является выходом устройства.

Второй вариант устройства приема для реализации заявляемого способа представлен на фиг 11. Устройство содержит последовательно соединенные блок обработки высокочастотного сигнала 1, вход которого является входом устройства, квадратурный демодулятор 2, блок квантования фазы и амплитуды 15, блок формирования суммарных величин 42, блок суммирования 43 и весовой сумматор 18. Два входа блока квантования фазы и амплитуды 15, соответствующие синфазной I и квадратурной Q составляющим входного сигнала, соединены с соответствующими выходами квадратурного демодулятора 2. Блок формирования суммарных величин 42 состоит из М формирователей суммарных величин 17, входы ain, pin каждого из которых, начиная со второго, соединены с выходами аout, pout предыдущего формирователя суммарных величин, а входы аin, pin первого формирователя суммарных величин 17 являются входами блока формирования суммарных величин 42 и соединены с выходами блока квантования амплитуды и фазы 15. Блок суммирования 43 состоит из k сумматоров 44, имеющих по М входов и по одному выходу. Совокупность выходов Yj, i всех М формирователей суммарных величин 17 (i=1...M, j=1...k) являются выходами блока формирования суммарных величин 42 и соединены со входами сумматоров 44 таким образом, что j-й выход i-го фазоамплитудного сумматора соединен с i-м входом j-го сумматора 44. Выходы сумматоров 44 (Y1,...,Yk) соединены с соответствующими входами весового сумматора 18. Первый и второй выходы весового сумматора 18 соединены с синфазным ZI и квадратурным ZQ входами векторного сумматора 13 и с первым и вторым входами решающей схемы 14 соответственно. Выход Z векторного сумматора 13 соединен с третьим входом решающей схемы 14, выход которой является выходом устройства.

Третий вариант устройства приема широкополосного сигнала для реализации заявляемого способа представлен на фиг. 12. Устройство содержит последовательно соединенные блок обработки высокочастотного сигнала 1, вход которого является входом устройства, квадратурный демодулятор 2, блок квантования фазы и амплитуды 15, два входа которого, соответствующие синфазной I и квадратурной Q составляющим входного сигнала, соединены с соответствующими выходами квадратурного демодулятора 2, М формирователей суммарных величин 17, М весовых сумматоров 18, блок суммирования 46, векторный сумматор 13 и решающую схему 14. Входы аin, pin каждого из формирователей суммарных величин 17, начиная со второго, соединены с выходами аout, pout предыдущего формирователя суммарных величин, а входы ain, pin первого формирователя суммарных величин 17 соединены с выходами блока квантования фазы и амплитуды 15. k выходов Y1...Yk каждого из формирователей суммарных величин 17 соединены со входами соответствующего весового сумматора 18. Выходы синфазного ZIi, и квадратурного ZQi значений корреляции каждого i-го весового сумматора 18 соединены с соответствующими входами блока суммирования 46, состоящего из двух сумматоров 44, имеющих по М входов и по одному выходу. Входы первого сумматора являются входами Zli блока суммирования 46, а входы второго сумматора являются входами ZQi (i=1...М) блока суммирования 46. Выход первого сумматора 44 является выходом синфазного значения корреляции ZI, а выход второго сумматора 44 является выходом квадратурного значения корреляции ZQ блока суммирования 46. Выходы ZI и ZQ блока суммирования 46 соединены с первым и вторым входами векторного сумматора 13 и первым и вторым входами решающей схемы 14. Выход Z векторного сумматора 13 соединен с третьим входом решающей схемы 14, выход которой является выходом устройства.

Четвертый вариант устройства приема широкополосного сигнала для реализации заявляемого способа представлен на фиг. 13 и содержит последовательно соединенные блок обработки высокочастотного сигнала 1, вход которого является входом устройства, и квадратурный демодулятор 2, М формирователей суммарных величин 17, М весовых сумматоров 18, М векторных сумматоров 13, сумматор 44 с М входами и решающую схему 14. Два входа блока квантования амплитуды и фазы 15, соответствующие синфазной I и квадратурной Q составляющим входного сигнала, соединены с соответствующими выходами квадратурного демодулятора 2. Выходы амплитуды а и фазы p блока квантования амплитуды и фазы 15 соединены с аin, pin входами первого формирователя суммарных величин 17, а входы аin, pin каждого из формирователей суммарных величин 17, начиная со второго, соединены с выходами аout, pout предыдущего формирователя суммарных величин 17, k выходов каждого формирователя суммарных величин 17 соединены с входами соответствующего весового сумматора 18. Выходы ZIi, ZQi каждого i-го весового сумматора 18 соединены с соответствующими входами i-го векторного сумматора 13 и соответствующими входами решающей схемы 14, причем выход каждого из М векторных сумматоров соединен с соответствующим входом сумматора 44, выход Z которого соединен с соответствующим входом решающей схемы 14, выход которой является выходом устройства.

Работает устройство, представленное на фиг. 2, следующим образом.

Входной сигнал поступает на вход блока обработки высокочастотного сигнала 1, внутри которого осуществляются все необходимые операции по усилению и преобразованию в область промежуточной частоты (ПЧ). Выходной сигнал блока обработки высокочастотного сигнала 1 поступает на вход квадратурного демодулятора 2, на выходе которого формируются синфазная I и квадратурная Q составляющие демодулированного сигнала, которые поступают на вход блока квантования фазы и амплитуды 15.

Суть работы блока квантования фазы и амплитуды 15 состоит в преобразовании отсчетов сигнала, представленного синфазной I и квадратурной Q составляющими, в значения амплитуды а и фазы p, представленные целыми числами. Причем число а представляет результат аналого-цифрового преобразования амплитуды. Число p формируется по принципу, который проиллюстрирован на фиг. 8. Значения фазы ϕ сигнала представляют угол, образованный вектором сигнала (I, Q) с осью I. Вся координатная плоскость фиг. 8 разделена на равные угловые секторы по количеству уровней квантования фазы, количество которых равно n= 2S (S > 1, целое число). Фиг. 8(а) иллюстрирует цифровые значения фазы p для случая n = 8 (S = 3), а фиг. 8(b) - для случая n=16 (S = 4). Внутри каждого сектора показано двоичное представление его номера 0,1,2...7. Номер углового сектора служит цифровым значением p фазы сигнала.

Пример построения блока квантования фазы и амплитуды 15 приведен на фиг. 9. Для наглядности показан случай квантования фазы на n = 8 уровней, а амплитуды - на m = 2 уровня.

Формирование цифрового значения амплитуды а происходит с помощью схемы формирования амплитуды 39 и схемы сравнения 41. В схеме формирования амплитуды 39 оценивается амплитуда сигнала, представленного синфазной I и квадратурной Q составляющими. Оценка может быть сформирована любым известным способом, например вычислением суммы квадратичных значений I2+Q2 или любой монотонной функции от этой суммы. В схеме сравнения 41 оценка амплитуды сравнивается с порогом, на выходе схемы 41 формируется '1', если оценка амплитуды превышает порог, '0' - в противном случае. Порог может быть установлен исходя из известного уровня амплитуды, соответствующего случаю отсутствия сигнала на входе приемника. Все описанные операции выполняются, и результат поступает на выход блока квантования фазы и амплитуды 15 по сигналам тактовых импульсов, частота которых определяется частотой дискретизации сигнала. Генератор тактовых импульсов здесь не показан для простоты.

Формирование цифрового значения фазы p для случая 8 уровней квантования может быть выполнено с помощью трех схем сравнения 36, 37, 38 и формирователя кода фазы 40. На выходе схемы сравнения 36 формируется сигнал сравнения величин |I| и |Q|, равный '1', если |I| >= |Q|, и '0' - в противном случае. В схемах сравнения 37 и 38 значения I и Q соответственно сравниваются с нулевым уровнем, формируя таким образом двоичное представление знаков этих сигналов signum(I), signum(Q). Формирователь кода фазы представляет логическое устройство, входные и выходные значения которого связаны в соответствии с таблицей истинности, представленной на фиг. 10.

Сформированные цифровые значения амплитуды а и фазы p сигнала поступают на вход формирователя суммарных величин 17 и затем на весовой сумматор 18.

Формирователь суммарных величин 17 может быть выполнен в двух вариантах, соответствующих фазоамплитудному и фазовому методам формирования корреляции.

Формирователь суммарных величин 17, соответствующий фазоамплитудному методу, представлен на фиг. 3 и состоит из регистра сдвига 19, блока сумматоров по модулю n 20, регистра кода опорного сигнала 22, сумматора амплитуд 23. Регистр сдвига 19 имеет два входа a и p и 2L выходов al, pl...аL, pL. Входы a и p регистра сдвига 19 являются входами аin, pin, а выходы aL, рL являются выходами aout, pout формирователя суммарных величин 17.

L выходов значений фазы pl...pL регистра сдвига 19 соединены с соответствующими входами блока сумматоров по модулю n 20, остальные L входов prl... prL которого соединены с соответствующими выходами регистра кода опорного сигнала 22, a L выходов суммарных значений фазы p0l... р0L соединены с соответствующими входами сумматора амплитуд 23. Другие L выходов значений амплитуд al. . . aL регистра сдвига 19 соединены с соответствующими входами сумматора амплитуд 23, k выходов которого являются выходами Y1, Y2,...Yk формирователя суммарных величин 17, причем количество выходов k зависит от количества уровней квантования фазы в блоке квантования фазы и амплитуды 15.

Работает такой формирователь суммарных величин 17 следующим образом.

Цифровые значения фазы р и амплитуды а входного сигнала поступают на вход регистра сдвига 19, состоящего из L последовательно соединенных ячеек памяти. Каждая ячейка состоит из двух полей, предназначенных для записи значений а и р, а также имеет отводы, позволяющие читать значения а и р на выходе каждой ячейки. Множество пар отводов всех ячеек являются множеством выходов регистра сдвига al, pl...aL, pL. При подаче каждого тактового импульса на тактовый вход регистра сдвига 19 (на фигуре не показан) в каждую ячейку записывается значение на ее входе, таким образом цифровые значения амплитуды и фазы перемещаются на одну ячейку по направлению к выходу регистра сдвига, а в первую ячейку записывается входное значение. Таким образом, на выходах регистра сдвига 19 формируется множество L отсчетов сигнала, задержанных друг относительно друга на период тактовых импульсов, причем отсчеты представлены парами чисел al,pl...aL, pL. Цифровое значение фазы pi каждого из L задержанных отсчетов (i=1...L) суммируется по модулю n с цифровым значением фазы pri опорного сигнала на соответствующем выходе регистра кода опорного сигнала 22, формируя значение суммарной фазы p0i:

p0i=(pi+pri)MODn.

Суммирование осуществляется в соответствующем сумматоре 21 блока сумматоров по модулю n 20. Таким образом операция перемножения задержанных отсчетов входного сигнала и отсчетов опорного сигнала заменяется на операцию суммирования по модулю цифровых значений фазы.

Каждая пара чисел ai, p0i (i=1...L) является цифровым представлением отсчета комплексного сигнала ai•exp(j•ϕi), где фаза ϕi - фактическое значение фазового угла, соответствующего суммарной фазе p0i.

Дальнейшая обработка сигнала заключается в суммировании комплексных величин ai•exp(j•ϕi). Эти операции выполняются с помощью сумматора амплитуд 23 и весового сумматора 18.

Алгоритм работы сумматора амплитуд 23 заключается в суммировании амплитуд а отсчетов с одинаковыми цифровыми значениями суммарной фазы p0 (номер отсчета i здесь для простоты опущен):

Здесь  - значения амплитуд тех отсчетов (а, p0), для которых p0=g.

- значения амплитуд тех отсчетов (а, p0), для которых p0=g.

При таком методе суммирования максимальное количество k сформированных сумм Y1, Y2,...,Yk, а следовательно, и выходов сумматора амплитуд 22 равно количеству уровней квантования фазы n. Однако возможен второй вариант суммирования. Он состоит в следующем. Все множество цифровых значений фазы (1, 2. . . n) разбивается пополам, при этом каждому значению из первой половины соответствует одно значение из второй половины, отображающее значение фазы, отличающееся на 180 градусов. Поэтому в сумматоре амплитуд могут суммироваться с противоположным знаком значения амплитуд, соответствующие противоположным фазам. Алгоритм суммирования по второму варианту выражается формулами

При этом максимальное количество сумм k, а следовательно, и выходов сумматора амплитуд 23 равно n/2. Именно этот вариант суммирования приведен в примере реализации сумматора амплитуд 23 (см.фиг. 4).

На фиг. 4 приведен пример построения сумматора амплитуд 23 формирователя суммарных величин 17. Пример соответствует случаю, когда число уровней квантования фазы n=8.

Сумматор амплитуд 23 состоит из коммутатора 24, дешифратора 25 и блока накопления 26. Коммутатор осуществляет преобразование множества L пар значений p0i, и аi (i=1...L) из параллельной формы в последовательную. Значения p0i последовательно поступают на вход дешифратора 25. Если p0i равно одному из возможных значений, скажем h, то дешифратор 25 формирует импульс на выходе с номером h (h=1..n). Количество выходов дешифратора равно количеству уровней квантования фазы n. С выходов дешифратора импульсы поступают на входы блока накопления 26, на весовой вход которого поступает сигнал амплитуды ai. Блок накопления 26 состоит из n/2 накопительных сумматоров, имеющих по 3 входа, обозначенных на рисунке '+', '-' и 'ВЕС'. Начальное содержимое накопительных сумматоров равно 0. При поступлении импульса на вход '+' значение аi, поступающее на вход 'ВЕС', суммируется с содержимым сумматора. При поступлении импульса на вход '-' значение ai вычитается из содержимого сумматора. Таким образом, на выходах сумматора амплитуд формируются суммы значений амплитуд Y1, Y2,...,Y4 с одинаковыми или противоположными значениями фазы.

Регистр кода опорного сигнала 22 предназначен для хранения цифровых значений фазы опорного сигнала pr1 (i=1...L) на интервале обнаружения сигнала.

Цифровое значение фазы pr опорного сигнала формируется по тому же принципу, что и цифровое значение фазы p входного сигнала, который проиллюстрирован на фиг. 8 и был описан выше при описании работы блока квантования фазы и амплитуды 15.

Формирователь суммарных величин 17 при фазовом методе корреляции (m = 1) представлен на фиг. 5, состоит из регистра сдвига 27, блока сумматоров по модулю n 20, регистра кода опорного сигнала 22, сумматора амплитуд 28. В данном варианте, соответствующем фазовому методу корреляции, значения амплитуды сигнала не учитываются. При использовании фазоманипулированных сигналов значительная часть информации содержится в фазе сигнала. Поэтому проигрыш в эффективности, который дает такой способ, весьма незначителен ≤1 dB (см. фиг. 14). Реализация согласованного фильтра при этом упрощается. Поскольку значения амплитуд в этом варианте считаются постоянными а = 1, то суммирование сводится к простому подсчету количества отсчетов на выходе сумматора 20 с одинаковым значением p0.

На фиг. 6 приведен пример построения сумматора амплитуд 28 при фазовом методе корреляции формирователя суммарных величин 17. Пример соответствует случаю, когда число уровней квантования фазы n=8. Сумматор амплитуд 28 состоит из коммутатора 24, дешифратора 25 и блока счетчиков 29.

При использовании фазоманипулированных сигналов амплитуда опорного сигнала постоянна, поэтому код опорного сигнала представлен только цифровыми значениями фазы опорного сигнала. При этом учитывается, что опорный сигнал представляет комплексно-сопряженную копию входного сигнала.

В весовом сумматоре 18 осуществляется переход от цифрового представления фазы p к фактическому значению ϕ. Алгоритм работы весового сумматора 18 состоит в умножении каждой из суммарных величин Y1, Y2,...,Yk, сформированных на выходе формирователя суммарных величин 17, на синус и косинус угла ϕ, соответствующего цифровому значению фазы p на данном выходе формирователя суммарных величин 17. Результаты перемножения на cos ϕ суммируются, формируя синфазное значение корреляции ZI, результаты перемножения на sin ϕ, суммируются, формируя квадратурное значение корреляции ZQ:

Рассмотрим пример построения весового сумматора 18, соответствующий случаю, когда число уровней квантования фазы n = 8.

Если значение фазы ϕ, соответствующее ее цифровому значению p, взять на минимальной границе соответствующего углового сектора (см. фиг. 8), то при n = 8 значения cos ϕ равны соответственно cos0=1, cos π /4 = 0.707, cos π /2 = 0, cos3 π /4 = 0.707. Значения sin ϕ равны соответственно sin0=0, sin π /4 = 0.707, sin π /2 = 1, sin3 π /4 = 0.707. В соответствии с этим весовой сумматор 18 может быть выполнен, например, по схеме фиг. 7.

Весовой сумматор 18 (фиг. 7) состоит из сумматоров 30, 31, 34, 35 и перемножителей 32, 33. В сумматоре 30 вычисляется разность значений Y2-Y4 и поступает на вход перемножителя 32, где умножается на значение cos π /4 = 0.707. Результат перемножения суммируется со значением YI в сумматоре 34. Таким образом, на выходе сумматора 34 формируется синфазное значение корреляции

ZI=Y1•cos0+Y2•cos π /4+Y3•cos π /2+Y4•cos3 π /4

В сумматоре 31 вычисляется сумма значений Y2+Y4 и поступает на вход перемножителя 33, где умножается на значение sin π /4 = 0.707. Результат перемножения суммируется со значением Y3 в сумматоре 35. Таким образом, на выходе сумматора 35 формируется квадратурное значение корреляции

ZQ=Y1•sin0+Y2•sin  /4+Y3•sin π /2+Y4•sin 3 π /4

/4+Y3•sin π /2+Y4•sin 3 π /4

Конструкцию перемножителей 32 и 33 можно значительно упростить, если заменить умножение на 0.707 умножением на 0.5. В двоичном представлении эта операция сводится к простому сдвигу на один разряд. Экспериментально проверено, что проигрыш составляет не более 0.1-0.2 dB (см.фиг. 15).

Второй, третий, четвертый варианты устройства реализации заявляемого способа предназначены для увеличения длительности обрабатываемого сигнала. Они представляют три варианта каскадного соединения формирователей суммарных величин 17, весовых и векторных сумматоров, причем второй и третий варианты соответствуют когерентному, а четвертый вариант - некогерентному суммированию значений корреляции.

Значения ZI и ZQ, сформированные на выходе весового сумматора 18, поступают на входы векторного сумматора 13, где формируются значения оценок корреляции Z, равные модулю или любой монотонной функции от модуля комплексного значения корреляции Zl +j ZQ. Например, значение оценки корреляции может быть сформировано следующим образом:

Z=ZI2+ZQ2

Весь выше описанный алгоритм формирования оценки корреляции Z повторяется периодически при поступлении тактовых импульсов на входы всех составных частей описанного устройства. Формирователь тактовых импульсов, а также тактовые входы устройств для простоты не показаны. Поскольку отсчеты входного сигнала, записанные в ячейках регистра сдвига 19 (или 27) фазоамплитудного сумматора 17, продвигаются на одну ячейку по сигналам тактовых импульсов, то таким образом формируется последовательность значений оценки корреляции, соответствующих различным значениям относительного временного сдвига между входным и опорным сигналами.

Последовательность значений оценки корреляции Z поступает на вход решающей схемы 14, где сравнивается с величиной порога, и по результатам сравнения принимается решение о наличии или отсутствии сигнала, а также о задержке входного сигнала.

Во втором варианте устройства (см. фиг. 11) входной сигнал поступает на вход блока обработки высокочастотного сигнала 1, внутри которого осуществляются все необходимые операции по усилению и преобразованию в область промежуточной частоты (ПЧ). Выходной сигнал блока обработки высокочастотного сигнала 1 поступает на вход квадратурного демодулятора 2, на выходе которого формируются синфазная I и квадратурная Q составляющие демодулированного сигнала, которые поступают на вход блока квантования фазы и амплитуды 15.

В блоке квантования фазы и амплитуды 15 отсчеты сигнала, представленного синфазной I и квадратурной Q составляющими, преобразуются в цифровые значения амплитуды a и фазы p. Принципы формирования величин а и p изложены выше при описании работы устройства по первому варианту.

Сигналы a и p поступают на вход блока формирования суммарных величин 42, который состоит из М последовательно соединенных формирователей суммарных величин 17. В каждом i-м формирователе суммарных величин 17 (i= 1...М) формируются L отсчетов сигнала, задержанных друг относительно друга на период тактовых импульсов. Затем суммируются по модулю n цифровые значения фаз соответствующих отсчетов входного и опорного сигналов, формируя суммарные значения фазы p0=(p+pr)MODn. Затем суммируются значения амплитуд отсчетов сигнала с одинаковыми значениями суммарной фазы p0, образуя величины Yl,i... Yk,i на выходах каждого i-го сумматора (i=1..M). Таким образом на выходах блока формирования суммарных величин 42 формируется M•k таких величин. Подробное изложение принципа работы формирователя суммарных величин 17 приведено при описании работы устройства по первому варианту.

Сформированные значения Yl,i. ..Yk,i (i=1...М) поступают на вход блока суммирования 43. В каждом из k сумматоров блока суммирования 43 суммируются значения с одноименных выходов всех М фазоамплитудных сумматоров блока фазоамплитудных сумматоров 42:

Значения Y1...Yk поступают на вход весового сумматора 18, где формируются синфазное ZI и квадратурное ZQ значения корреляции. Алгоритм весового сумматора 18 описан при описании первого варианта устройства реализации заявляемого способа.

Значения ZI и ZQ поступают на вход векторного сумматора 13, где формируется значение оценки корреляции Z. Алгоритм формирования Z аналогичен описанному выше в первом варианте устройства реализации заявляемого способа.

Весь выше описанный алгоритм формирования оценки корреляции Z повторяется периодически при поступлении тактовых импульсов на входы всех составных частей описанного устройства. Формирователь тактовых импульсов, а также тактовые входы устройств для простоты не показаны. Поскольку отсчеты входного сигнала, записанные в ячейках регистра сдвига 19 (или 27) формирователя суммарных величин 17, продвигаются на одну ячейку по сигналам тактовых импульсов, то таким образом формируется последовательность значений оценки корреляции, соответствующих различным значениям относительного временного сдвига между входным и опорным сигналами.

Последовательность значений оценки корреляции Z поступает на вход решающей схемы 14, где сравнивается с величиной порога, и по результатам сравнения принимается решение о наличии или отсутствии сигнала, а также о задержке входного сигнала.

В третьем варианте устройства реализации (см.фиг. 12) входной сигнал поступает на вход блока обработки высокочастотного сигнала 1, внутри которого осуществляются все необходимые операции по усилению и преобразованию в область промежуточной частоты (ПЧ). Выходной сигнал блока обработки высокочастотного сигнала 1 поступает на вход квадратурного демодулятора 2, на выходе которого формируются синфазная I и квадратурная Q составляющие демодулированного сигнала, которые поступают на вход блока квантования фазы и амплитуды 15.

В блоке квантования фазы и амплитуды 15 отсчеты сигнала, представленного синфазной I и квадратурной Q составляющими, преобразуются в цифровые значения амплитуды а и фазы p. Принципы формирования величин а и p изложены выше при описании работы устройства по 1-му варианту.

Сигналы a и p поступают на вход первого из М последовательно соединенных формирователей суммарных величин 17. В каждом i-м формирователе суммарных величин 17 (i= 1...М) формируются L отсчетов сигнала, задержанных друг относительно друга на период тактовых импульсов. Затем суммируются по модулю n цифровые значения фаз соответствующих отсчетов входного и опорного сигналов, формируя суммарные значения фазы p0=(p+pr)MODn. Затем суммируются значения амплитуд отсчетов сигнала с одинаковыми значениями суммарной фазы p0, образуя суммарные величины Yl,i,...Yk,i на выходах каждого i-го сумматора (i= 1. ..M). Подробное изложение принципа работы формирователя суммарных величин 17 приведено при описании работы устройства по первому варианту.

Суммарные величины Yl,i...Yk,i, сформированные на выходе каждого формирователя суммарных величин 17 (i=1...M), поступают на входы соответствующего весового сумматора 18. В каждом i-м весовом сумматоре 18 формируются синфазное ZIi, и квадратурное ZQi значения корреляции. Алгоритм работы весового сумматора 18 описан более подробно при описании устройства по 1-му варианту реализации заявляемого способа.

Значения ZIi и ZQi поступают на входы блока суммирования 46, состоящего из двух сумматоров 44.

В первом сумматоре блока суммирования 43 суммируются синфазные Zli, а во втором - квадратурные ZQi значения корреляции, сформированные на выходах всех М весовых сумматоров 18. Таким образом формируются синфазное ZI и квадратурное ZQ значения корреляции:

Значения ZI и ZQ поступают на вход векторного сумматора 13, где формируется значение оценки корреляции Z. Алгоритм формирования Z аналогичен описанному выше в первом варианте устройства реализации заявляемого способа.

Весь выше описанный алгоритм формирования оценки корреляции Z повторяется периодически при поступлении тактовых импульсов на входы всех составных частей описанного устройства. Формирователь тактовых импульсов, а также тактовые входы устройств для простоты не показаны. Поскольку отсчеты входного сигнала, записанные в ячейках регистра сдвига 19 (или 27) фазоамплитудного сумматора 17, продвигаются на одну ячейку по сигналам тактовых импульсов, то таким образом формируется последовательность значений оценки корреляции, соответствующих различным значениям относительного временного сдвига между входным и опорным сигналами.

Последовательность значений оценки корреляции Z поступает на вход решающей схемы 14, где сравнивается с величиной порога, и по результатам сравнения принимается решение о наличии или отсутствии сигнала, а также о задержке входного сигнала.

Четвертый вариант устройства (фиг. 13) для реализации заявляемого способа аналогичен третьему варианту, с той лишь разницей, что комплексные значения корреляции, сформированные в последовательно соединенных фазоамплитудных корреляторах, суммируются некогерентно. Такой вариант предпочтителен для условий приема, при которых интервал когерентности сигнала примерно равен длительности сигнала, обрабатываемого одним формирователем суммарных величин.

Входной сигнал поступает на вход блока обработки высокочастотного сигнала 1, внутри которого осуществляются все необходимые операции по усилению и преобразованию в область промежуточной частоты (ПЧ). Выходной сигнал блока обработки высокочастотного сигнала 1 поступает на вход квадратурного демодулятора 2, на выходе которого формируются синфазная I и квадратурная Q составляющие демодулированного сигнала, которые поступают на вход блока квантования фазы и амплитуды 15.

В блоке квантования фазы и амплитуды 15 отсчеты сигнала, представленного синфазной I и квадратурной Q составляющими, преобразуются в цифровые значения амплитуды а и фазы р. Принципы формирования величин а и p изложены выше при описании работы устройства по первому варианту.

Сигналы а и p поступают на вход первого из М последовательно соединенных формирователей 17. В каждом i-м формирователе суммарных величин 17 (i= 1... М) формируются L отсчетов сигнала, задержанных друг относительно друга на период тактовых импульсов. Затем суммируются по модулю n цифровые значения фаз соответствующих отсчетов входного и опорного сигналов, формируя суммарные значения фазы p0=(p+pt)MODn. Затем суммируются значения амплитуд отсчетов сигнала с одинаковыми значениями суммарной фазы p0, образуя суммарные величины Yl,i,...Yk,i на выходах каждого i-го сумматора (i=1...М). Подробное изложение принципа работы формирователя суммарных величин 17 приведено при описании работы устройства по первому варианту.

Суммарные величины Yl,i...Yk,i, сформированные на выходе каждого фазоамплитудного сумматора, (i= 1...М) поступают на входы соответствующего весового сумматора 18. В каждом i-м весовом сумматоре 18 формируются синфазное Zli и квадратурное ZQi значения корреляции. Алгоритм работы весового сумматора 18 описан более подробно при описании устройства по 1-му варианту реализации заявляемого способа.

Значения ZIi и ZQi, сформированные на выходе каждого i-го весового сумматора 18, поступают на входы соответствующего векторного сумматора 13, где формируются значения оценок корреляции Zi равные модулю или любой монотонной функции от модуля комплексного значения корреляции ZIi +j ZQi. Например, значения оценок корреляции могут быть сформированы как квадратичные значения модулей:

Zi=(ZIi)2+(ZQi)2

Значения Zi суммируются в сумматоре 44, формируя таким образом значение оценки корреляции

Весь выше описанный алгоритм формирования оценки корреляции Z повторяется периодически при поступлении тактовых импульсов на входы всех составных частей описанного устройства. Формирователь тактовых импульсов, а также тактовые входы устройств для простоты не показаны. Поскольку отсчеты входного сигнала, записанные в ячейках регистра сдвига 19 (или 27) формирователя суммарных величин 17, продвигаются на одну ячейку по сигналам тактовых импульсов, то таким образом формируется последовательность значений оценки корреляции, соответствующих различным значениям относительного временного сдвига между входным и опорным сигналами.

Последовательность значений оценки корреляции Z поступает на вход решающей схемы 14, где сравнивается с величиной порога, и по результатам сравнения принимается решение о наличии или отсутствии сигнала, а также о задержке входного сигнала.

Изобретение относится к области радиотехники и может найти применение в системах связи с кодовым разделением каналов. Достигаемый технический результат - упрощение алгоритма приема широкополосных фазоманипулированных сигналов. В предлагаемом способе используется квантование последовательности отсчетов комплексного входного сигнала. Каждый отсчет последовательности представляют в виде пары цифровых значений фазы и амплитуды. Значение комплексной корреляции между входным и опорным сигналами определяют путем суммирования цифровых значений фазы отсчетов комплексного входного и опорного сигналов и цифровых значений амплитуд отсчетов комплексного входного сигнала и последующего весового суммирования результатов, формируя таким образом синфазную и квадратурную составляющие комплексной корреляции. Первый вариант устройства приема широкополосного сигнала позволяет реализовать предлагаемый способ за счет использования блока квантования фазы и амплитуды, формирователя суммарных величин и весового сумматора. Второй, третий и четвертый варианты устройства предназначены для увеличения длительности обрабатываемого сигнала. Они представляют три варианта каскадного соединения формирователей суммарных величин и весовых сумматоров, причем третий вариант соответствует когерентному, а четвертый вариант - некогерентному суммированию значений корреляции. 5 с.п. ф-лы, 15 ил.

| US 5184135 A, 02.02.1993 | |||

| ПРИЕМНОЕ УСТРОЙСТВО ФМ-СИГНАЛОВ | 1993 |

|

RU2085036C1 |

| Устройство для приема амплитудно-фазоманипулированных сигналов | 1990 |

|

SU1758900A1 |

| US 5566202 A, 19.04.1995 | |||

| US 3831013 A, 20.08.1974 | |||

| US 4057759 A, 08.11.1977 | |||

| Огнетушитель | 0 |

|

SU91A1 |

| 1968 |

|

SU415406A1 | |

Авторы

Даты

2000-07-27—Публикация

1999-06-03—Подача