Изобретение относится к программируемому постоянному запоминающему устройству типа электрически стираемого программируемого ПЗУ (ЭСППЗУ), запоминающие ячейки которого образованы запоминающим транзистором, имеющим изолированный электрод затвора, и включенным последовательно к нему транзистором выбора, причем вывод стока транзистора выбора соединен с разрядной шиной, вывод затвора транзистора выбора соединен с шиной слов, а на вывод управляющего затвора запоминающих транзисторов подается напряжение считывания.

Такое программируемое постоянное запоминающее устройство известно из патента США 4612630. В нем предложено изменять напряжение считывания, для определения порогового напряжения, устанавливающееся в соответствующем состоянии программирования.

В EP-A-0589266 описан микрокомпьютер с ЭСППЗУ, в котором тактовая частота внешнего сигнала ограничивается до граничного значения, при котором надежно обеспечивается считывание запоминающего устройства ЭСППЗУ.

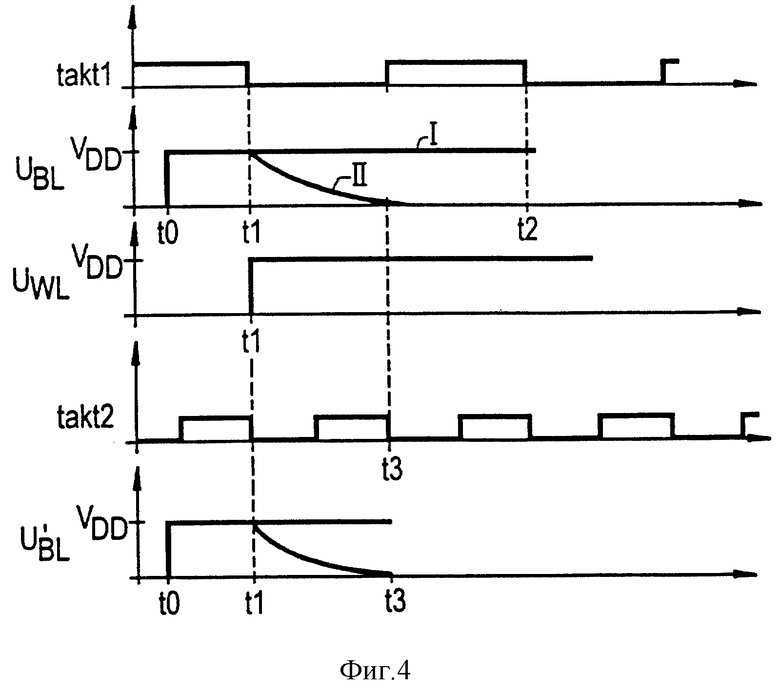

В таких программируемых постоянных запоминающих устройствах типа ЭСППЗУ запоминающая ячейка выполнена с двумя МОП-транзисторами и расположена в точке пересечения шины слов WL с разрядной шиной BL, как показано на фиг. 3. Один из транзисторов ST содержит изолированный электрод затвора FG, состоянием заряда которого может устанавливаться запускающее напряжение этого транзистора. Транзистор ST является собственно запоминающим транзистором. При стертой запоминающей ячейке с n-канальными транзисторами изолированный электрод затвора заряжен отрицательно так, что запускающее напряжение запоминающего транзистора ST сдвигается в направлении более высоких значений. В случае программированной запоминающей ячейки изолированный электрод затвора разряжен или даже заряжен положительно. Запускающее напряжение тогда соответствует запускающему напряжению обычного МОП-транзистора или является еще более низким. К электроду управляющего затвора SG запоминающего транзистора ST для считывания прикладывается напряжение считывания UL, находящееся в пределах между запускающими напряжениями запоминающего транзистора в состояниях программирования и стирания. Если транзистор стерт, то он заперт, если он программирован, то находится в проводящем состоянии. В случае p-канальных транзисторов указанные соотношения противоположны.

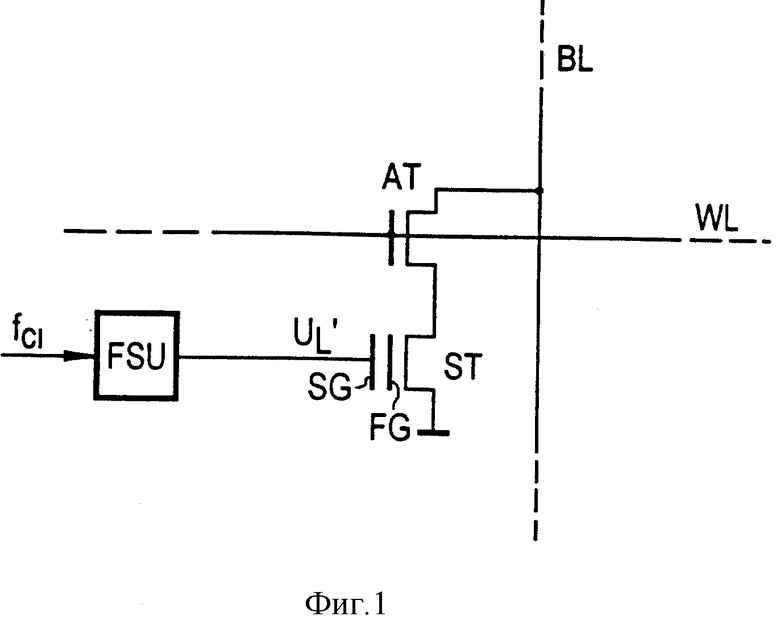

Последовательно с запоминающим транзистором ST включен транзистор выбора AT, электрод стока которого соединен с разрядной шиной BL, а электрод затвора соединен с шиной слов WL. За счет приложения напряжения, которое примерно соответствует напряжению питания VDD, к шине слов WL или, соответственно, к затвору транзистора выбора AT последний переходит в проводящее состояние и подключает вывод стока запоминающего транзистора ST к разрядной шине BL. Она заряжается перед процессом считывания примерно до потенциала напряжения питания VDD. Если ячейка стерта, то запоминающий транзистор ST заперт и разрядная шина BL остается на потенциале напряжения питания VDD, тогда считывается логическая "1". Если ячейка программирована, то запоминающий транзистор ST находится в проводящем состоянии и разрядная шина BL разряжается через него так, что спустя определенное время может детектироваться логический "0". Это представлено в верхней части фиг. 4. К моменту времени t0 разрядная шина BL заряжается до напряжения UBL со значением порядка VDD. Например, падающим фронтом тактового сигнала takt1 к моменту времени t1 напряжение UWL на шине слов WL переключается на значение порядка VDD. В случае стертой ячейки, которая обозначена I, напряжение UBL разрядной шины BL сохраняет значение VDD, в то время как в случае программированной ячейки, которая обозначена II, напряжение UBL разрядной шины уменьшается.

Если частота тактового сигнала takt1 является достаточно малой, следующим падающим фронтом к моменту времени t2 запускается процесс оценки. К этому моменту времени разрядная шина BL уже достаточно разрядилась, чтобы можно было однозначно детектировать программированное состояние.

Если, однако, время выборки должно быть уменьшено, то тактовая частота должна увеличиваться. На фиг. 4 представлена в качестве примера вдвое более высокая частота тактового сигнала takt2. Там после подключения напряжения питания VDD к моменту времени t1 к шине слов WL после некоторого периода к моменту времени t3 происходила бы оценка. К этому моменту времени, однако, разрядная шина BL в случае программированной ячейки еще полностью не разрядилась, следствием чего является опасность неправильного детектирования.

Задачей настоящего изобретения является таким образом создание программируемого постоянного запоминающего устройства типа ЭСППЗУ или типа ЭСППЗУ с быстрым стиранием (EEPROM= Flash), при котором при любом времени выборки возможно однозначное считывание.

Эта задача согласно изобретению решается за счет постоянного запоминающего устройства согласно пункту 1 формулы изобретения. Предпочтительные варианты осуществления изобретения представлены в зависимых пунктах формулы изобретения.

Соответствующее изобретению программируемое постоянное запоминающее устройство позволяет производить зависящий от применения выбор частоты тактового сигнала без учета схемно обусловленных ограничений относительно времен выборки при считывании из запоминающего устройства.

Изобретение поясняется ниже на примере выполнения, иллюстрируемом чертежами, на которых показано следующее:

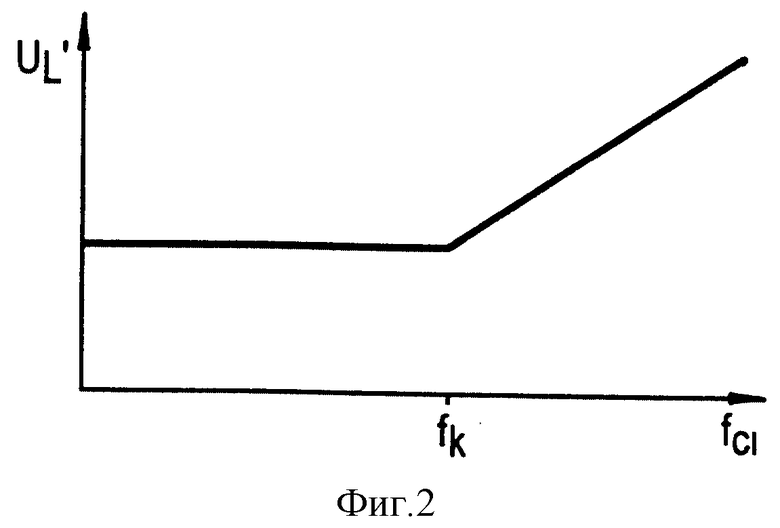

Фиг. 1 - запоминающая ячейка ЭСППЗУ (электрически стираемого программируемого ПЗУ) с соответствующим изобретению включением,

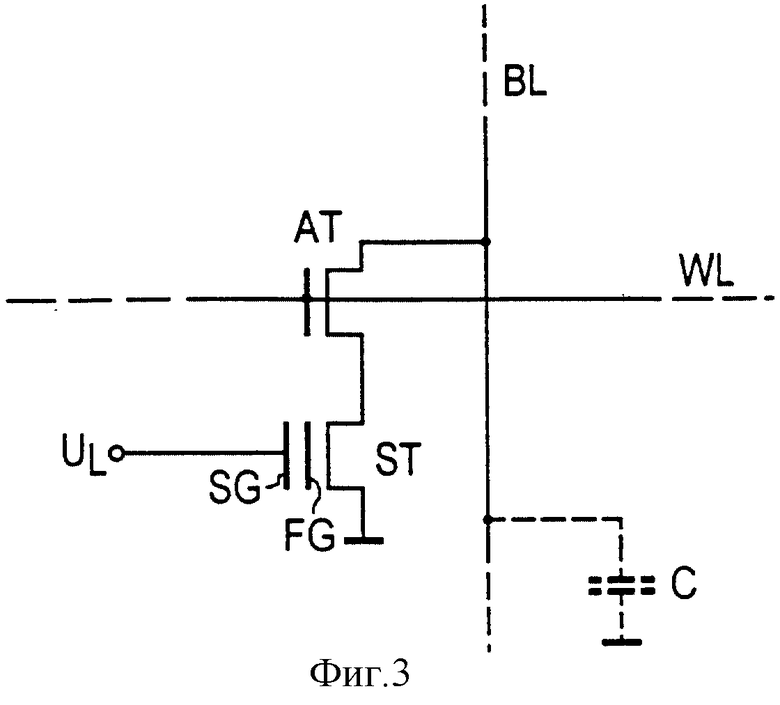

Фиг. 2 - возможный вид характеристики U'L - fC1,

Фиг. 3 - запоминающая ячейка ЭСППЗУ согласно уровню техники и

Фиг. 4 - временной ход некоторых напряжений при считывании ячейки.

На фиг. 1 показана для пояснения изобретения только одна запоминающая ячейка программируемого запоминающего устройства типа ЭСППЗУ. Все запоминающее устройство образовано множеством таких запоминающих ячеек, которые расположены в виде матрицы, образованной шинами слоев WL и разрядными шинами BL, и выполнены с возможностью адресации посредством схем, известных специалисту в данной области техники (на чертеже не представлены).

Изобретение может использоваться также и в запоминающих устройствах ЭСППЗУ с быстрым стиранием.

Для считывания содержания запоминающих ячеек соответствующую адресную разрядную линию BL заряжают до потенциала напряжения питания VDD и затем на соответствующую шину слов WL также подключают потенциал напряжения питания VDD, за счет чего транзистор выбора AT адресной запоминающей ячейки становится проводящим. На выводе управляющего затвора SG запоминающих транзисторов ST всегда на всех запоминающих ячейках приложено напряжение считывания U'L. Это напряжение считывания U'L зависит соответствующим изобретению образом от частоты fc1 тактового сигнала, которым запускают процессы при считывании из запоминающего устройства.

Фиг. 2 показывает возможный ход напряжения считывания U'L в качестве функции частоты fc1 тактового сигнала. Вплоть до определенной критической частоты fk напряжение считывания U'L остается постоянным, а затем оно линейно увеличивается. Возможны и другие виды характеристик, существенным является только, чтобы крутизна кривых была большей или равной нулю.

Ход напряжения считывания U'L зависит от передаточных характеристик средства (FSU), которое может быть реализовано, например, на преобразователе частоты в напряжение FSU, на выходе которого формируется напряжение считывания U'L. Выходной сигнал этого преобразователя частоты в напряжение FSU подают на выводы управляющих затворов SG запоминающих транзисторов ST соответствующего изобретению ЭСППЗУ.

При повышении напряжения считывания U'L запоминающий транзистор ST становится проводящим так, что адресованная разрядная шина BL может разряжаться быстрее. Это представлено в нижней части фиг. 4, где показан ход напряжения U'BL на адресной разрядной шине BL в случае программированной запоминающей ячейки. В данном случае при более высокой частоте тактового сигнала takt2 возможно однозначное детектирование программированного состояния.

Возможно, что адресная разрядная шина BL также в случае стертой запоминающей ячейки вследствие более высокой проводимости запоминающего транзистора ST несколько разряжается, что показано в нижней части фиг. 4, ходом напряжения U'BL на адресной разрядной шине BL. Этот разряд, однако, всегда будет весьма малым и не вызовет никаких проблем.

Изобретение относится к программируемым постоянным запоминающим устройствам типа электрически стираемого ПЗУ (ЭСППЗУ). Техническим результатом является создание ЭСППЗУ с быстрым стиранием, причем, используя данное ЭСППЗУ при любом времени выборки, возможно однозначное считывание из него данных. Устройство содержит запоминающий транзистор, транзистор выбора, разрядную шину, шину слов, средство (FSU), предназначенное для формирования напряжения считывания в зависимости от частоты тактового сигнала. 3 з.п.ф-лы, 4 ил.

| Постоянное запоминающее устройство | 1973 |

|

SU444246A1 |

| ВИЗИРНАЯ МАРКА | 1993 |

|

RU2035695C1 |

| US 5126969 А, 30.06.1992 | |||

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| US 4907202 А, 06.03.1990 | |||

| US 4612630 А, 16.09.1986. | |||

Авторы

Даты

2001-01-20—Публикация

1997-04-16—Подача