1

Изобретение касается автоматики и вычислительной техники и относится к запоминающим устройствам (ЗУ).

Известно запоминающее устройство, содержащее МОП-транзисторы с плавающим затвором, матрицу числовых шин и матрицу разрядных шин, подключенную через дополнительные МОП-транзисторы к шине питания. В таком устройстве наряду с запоминающим транзистором используется дополнительный ключевой транзистор. Это значительно увеличивает общее количество элементов ЗУ, особенно в ЗУ большой емкости, где собственно запоминающая матрица занимает основное место.

Цель изобретения - упрощение устройства.

Для этого в каждый запоминающий транзистор устройства введен дополнительный затвор, изолированный от плавающего затвора слоем диэлектрика, причем дополнительные затворы транзисторов одного числа соединены числовой шиной, стоки транзисторов одного разряда соединены с разрядной шиной, а истоки - с шиной нулевого потенциала.

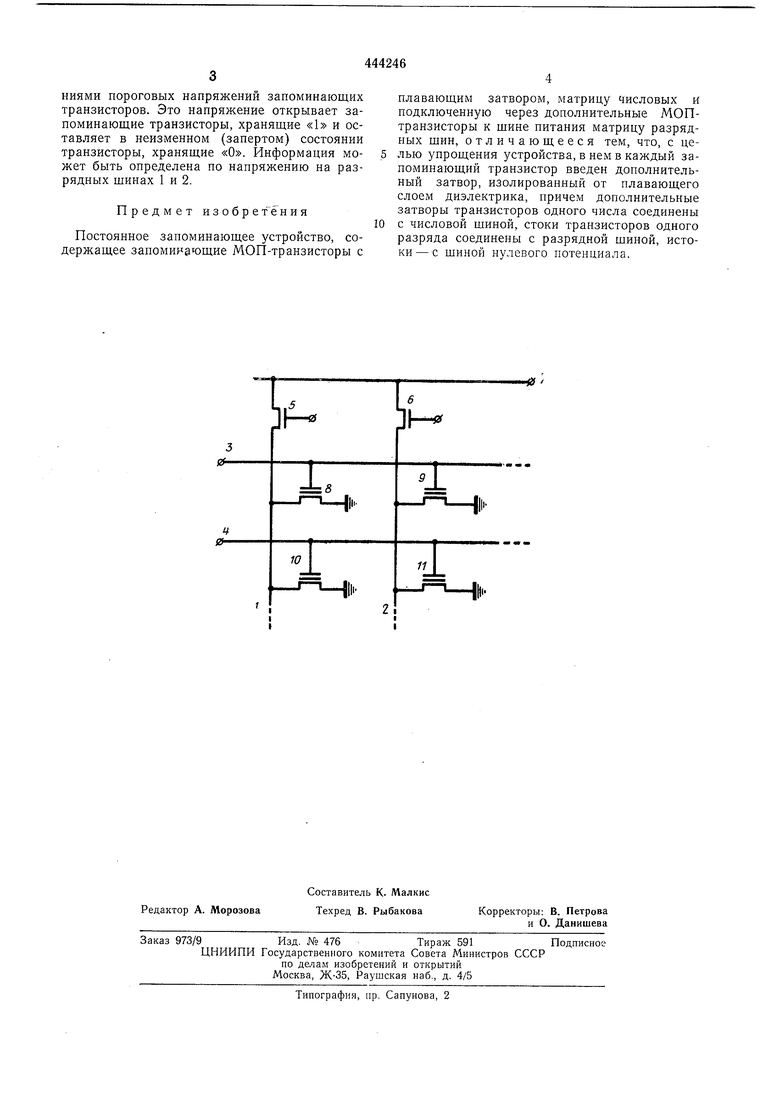

На чертеже изображена схема устройства.

Схема представляет собой матрицу, содержащую разрядные шины 1, 2 и числовые шины 3, 4. Шины 1 и 2 транзисторами 5 и 6 соединены с источником напряжения 7 (для р-канальных транзисторов имеет-Uran). В узлах

матрицы включены запоминающие транзисторы 8-11. Каждый запоминающий транзистор (в данном случае р-канальный) имеет по два затвора. Один из них, плавающий, выполнен из полпкристаллнческого кремния или молибдена и изолирован от подлох ки слоем Si02. Поверх плавающего затвора нанесен еще один слой SiO2, на котором расположен дополнительпый затвор.

Схема работает следующим образом.

При записи информации включаются транзисторы 5 и б тех разрядов, где должна быть записана «1. Эти транзисторы подают напрял ение - 6ш1т иа стоки запоминающих транзисторов, объединенных разрядной шиной 1. На одну из числовых шин нодается отрицательное напряжение Usun- Напрял ение бзап уменьшает величину пробивного напряжения транзисторов. Под действием напряжения

Ьпит в транзисторе 8 происходит пробой стокового диода и плавающий затвор в пем заряжается. В транзисторах, на управляющих затворах которых напряжение бзап отсутствует, величина напряжения Unm оказывается иедостаточной для пробоя стока. Накопленный заряд на плавающем затворе транзистора 8 соответствует записи в нем «1.

При считывании на числовую шину подается напряжение, величина которого является средней между наибольшим и наименьшим значениями пороговых напряжений запоминающих транзисторов. Это напряжение открывает запоминающие транзисторы, хранящие «1 и оставляет в неизменном (запертом) состоянии транзисторы, хранящие «О. Информация может быть определена по напряжению на разрядных шинах 1 и 2.

Предмет изобрет ёния

Постоянное запоминающее устройство, содержащее запоминающие МОП-транзисторы с

плавающим затвором, матрицу числовых и подключенную через дополнительные МОПтранзисторы к щине питания матрицу разрядных щин, отличающееся тем, что, с целью упрощения устройства, в нем в каждый запоминающий транзистор введен дополнительный затвор, изолированный от плавающего слоем диэлектрика, причем дополнительные затворы транзисторов одного числа соединены с числовой шиной, стоки транзисторов одного разряда соединены с разрядной шиной, истоки- с шиной нулевого потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| СХЕМА УПРАВЛЕНИЯ ДЛЯ ЭНЕРГОНЕЗАВИСИМОГО ПОЛУПРОВОДНИКОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1998 |

|

RU2221286C2 |

| Матричный накопитель для постоянного запоминающего устройства | 1977 |

|

SU734807A1 |

| УСТРОЙСТВО ПАМЯТИ И СПОСОБ ИЗГОТОВЛЕНИЯ | 2001 |

|

RU2247441C2 |

| Накопитель постоянного запоминающего устройства с электрической записью информции | 1973 |

|

SU466552A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444890A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444891A1 |

| Ячейка оперативной памяти | 2024 |

|

RU2826859C1 |

| ЭЛЕКТРИЧЕСКИ СТИРАЕМАЯ И ПРОГРАММИРУЕМАЯ ЭНЕРГОНЕЗАВИСИМАЯ НАКОПИТЕЛЬНАЯ ЯЧЕЙКА | 1996 |

|

RU2168242C2 |

X

т

0г0

I-

т

Авторы

Даты

1974-09-25—Публикация

1973-02-23—Подача