Изобретение относится к автоматике и вычислительной технике и может найти применение при построении систем управления технологическими процессами.

Известно модульное устройство для программного управления и контроля, содержащее блок памяти, счетчик адреса, регистр микроопераций, мультиплексоры адреса и логических условий, демультиплексор, два регистра логических условий, регистр номера, два коммутатора, два дешифратора, шифратор, генератор тактовых импульсов, триггеры пуска и управления, блок элементов ИЛИ, группу элементов ИЛИ, два элемента И и два элемента ИЛИ (а.с.1647519 СССР, G 05 B 19/18, опубл. 07.05.91, БИ N17).

Недостатком известного устройства является значительное число внешних входов и выходов, требуемых для организации взаимодействия с другими аналогичными устройствами при построении управляющих систем, вследствие необходимости обмена многоразрядными адресами передачи управления, представленными в параллельном коде.

Наиболее близким к предлагаемому устройству по технической сущности является устройство для программного управления, содержащее блок памяти микрокоманд, счетчики адреса и времени задержки, регистр микроопераций, коммутатор направления приема адреса, триггер режима, шифратор направления приема управления, дешифратор направления передачи управления, шину микроопераций, элемент запрета, четыре элемента ИЛИ и два элемента И (а.с. 1800445 СССР, G 05 B 19/18, опубл. 07.03.93, БИ N9).

Недостатком данного устройства является узкая область применения, обусловленная избыточным числом внешних входов и выходов, используемых для реализации взаимодействия (передачи управления) с другими аналогичными устройствами при функционировании устройства в составе системы управления.

Технической задачей изобретения является расширение области применения устройства за счет минимизации числа внешних входов и выходов, требуемых для организации взаимодействия с другими аналогичными устройствами в составе системы управления.

Техническая задача решается тем, что в устройство программного управления, содержащее блок памяти микрокоманд, счетчик адреса, регистр микроопераций, коммутатор направления приема адреса, триггер режима, шифратор направления приема управления, дешифратор направления передачи управления, счетчик времени задержки, шину микроопераций, с первого по четвертый элементы ИЛИ, первый и второй элементы И, причем выход первого элемента ИЛИ соединен с управляющим входом счетчика адреса, выход которого подключен к адресному входу блока памяти микрокоманд, выход признака формата которого подключен к K-входу триггера режима и к первому входу второго элемента ИЛИ, выход которого соединен с первыми входами первого и второго элементов И, прямой выход триггера режима подключен ко второму входу второго элемента ИЛИ, выход микроопераций блока памяти микрокоманд подключен к информационному входу регистра микроопераций, выход кода времени задержки блока памяти микрокоманд соединен с информационным входом счетчика времени задержки, информационный выход которого соединен с входами третьего элемента ИЛИ, выход которого подключен к управляющему входу счетчика времени задержки, выход переноса которого соединен с входом синхронизации и счетным входом счетчика адреса, информационный вход которого подключен к выходу коммутатора направления приема адреса, выход четвертого элемента ИЛИ соединен с J-входом триггера режима, а также с прямым и первым инверсным управляющими входами коммутатора направления приема адреса, первый вход синхронизации устройства соединен с входом синхронизации триггера режима и со вторым входом первого элемента И, выход которого подключен к входу синхронизации и счетному входу счетчика времени задержки, второй вход синхронизации устройства соединен со вторым входом второго элемента И, выход которого подключен к входу синхронизации регистра микроопераций, выход адреса/кода передачи управления блока памяти микрокоманд соединен с входами первого элемента ИЛИ, с входом дешифратора направления передачи управления, а также с первым информационным входом коммутатора направления приема адреса, входы/выходы инициализации устройства с первого по (n-1)-й (где n - количество идентичных устройств в составе системы управления) подключены к входам шифратора направления приема управления с первого по (n-1)-й соответственно, дополнительно введены блок тристабильных элементов, группа элементов И-НЕ, блок элементов запрета и триггер запуска, причем выход признака формата блока памяти микрокоманд соединен со вторым инверсным управляющим входом коммутатора направления приема адреса, с инверсным входом блока элементов запрета и с первыми входами элементов И-НЕ группы с первого по (n- 1)-й, вторые входы которых подключены к выходам дешифратора направления передачи управления с первого по (n-1)-й соответственно, а выходы соединены с входами/выходами инициализации устройства с первого по (n-1)-й соответственно, прямой выход триггера режима соединен с управляющим входом блока тристабильных элементов, информационный вход которого подключен к выходу регистра микроопераций, а выход соединен с шиной микроопераций, выход переноса счетчика времени задержки подключен к входу синхронизации триггера запуска, D-вход которого соединен с шиной логического нуля, вход запуска устройства подключен к входу установки триггера запуска, инверсный выход которого соединен с n-м входом шифратора направления приема управления, выход которого соединен с прямым входом блока элементов запрета, выход которого подключен к входам четвертого элемента ИЛИ и ко второму информационному входу коммутатора направления приема адреса.

Сущность изобретения заключается в следующем.

При функционировании устройства - прототипа в составе системы управления для обмена управляющими сигналами (сигналами передачи управления) с другим аналогичным устройством (модулем системы) используются две физические линии связи. Первая из указанных линий служит для выдачи сигнала передачи управления, вторая предназначается для приема сигнала передачи управления от другого устройства. Общее предельное число межмодульных линий связи в системе управления (сложность межмодульного интерфейса), таким образом, составляет (n-1)n.

Поскольку в системе управления, построенной на основе прототипа, возможно только последовательное функционирование различных устройств (параллельная работа устройств имеет место лишь в течение времени межмодульной передачи управления, когда функционирует устройство, передающее управление, и устройство, принимающее управление), одно и то же устройство mi не может одновременно принимать и вырабатывать сигналы межмодульной передачи управления. Таким образом, передача управляющих сигналов между любой парой устройств mi и mj в заданный момент времени может происходить либо в направлении от i-го устройства к j-му, либо от j-го устройства к i-му. Отсюда следует, что при реализации каждого акта передачи управления между устройствами mi и mj используется только одна из двух линий, связывающих эти устройства, т.е. имеет место избыточность в числе межмодульных линий связи.

При построении системы управления на основе предлагаемого устройства для обмена сигналами передачи управления между i-м и j-м устройствами (i, j=1, 2,...,n, i ≠ j) необходима единственная линия связи. При передаче управления от i-го устройства к j-му линия используется как выходная для i-го устройства и как входная для j-го. При передаче управления в обратном направлении линия является входной для i-го и выходной для j-го устройства. Таким образом, общее предельное число межмодульных линий связи в системе управления снижается в 2 раза и составляет

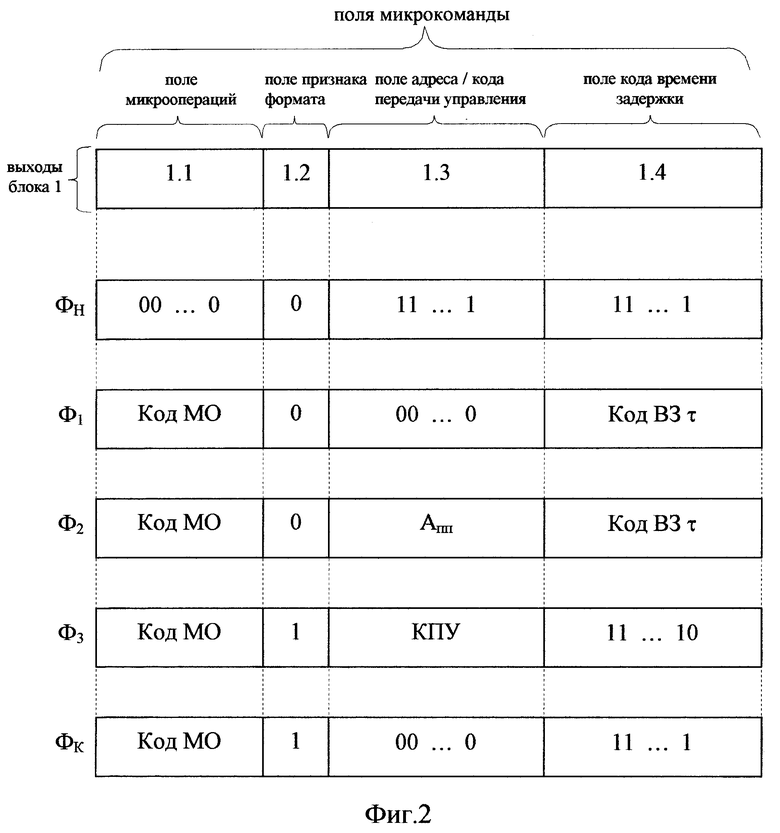

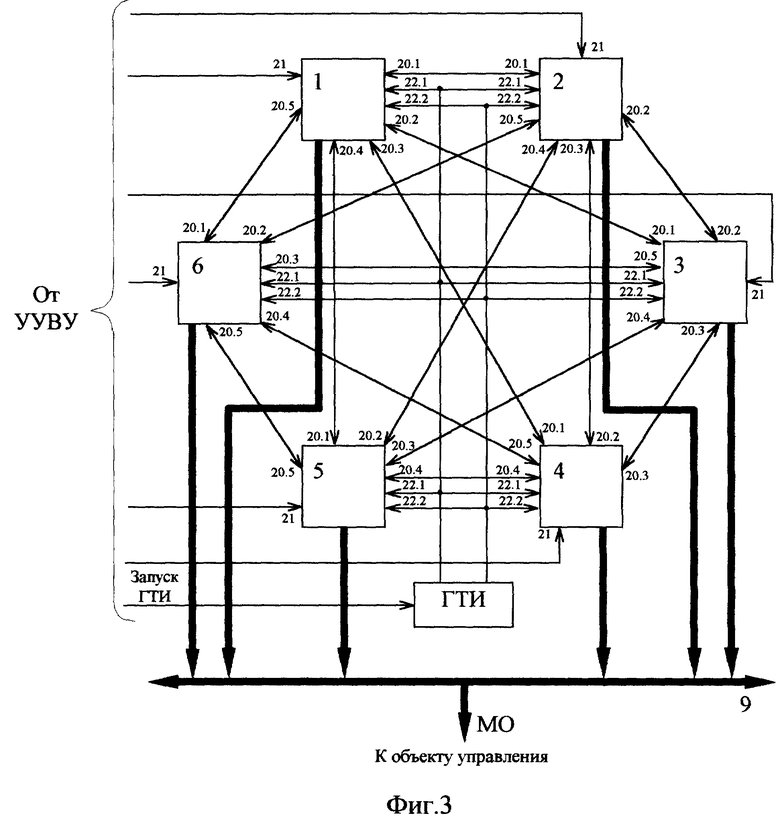

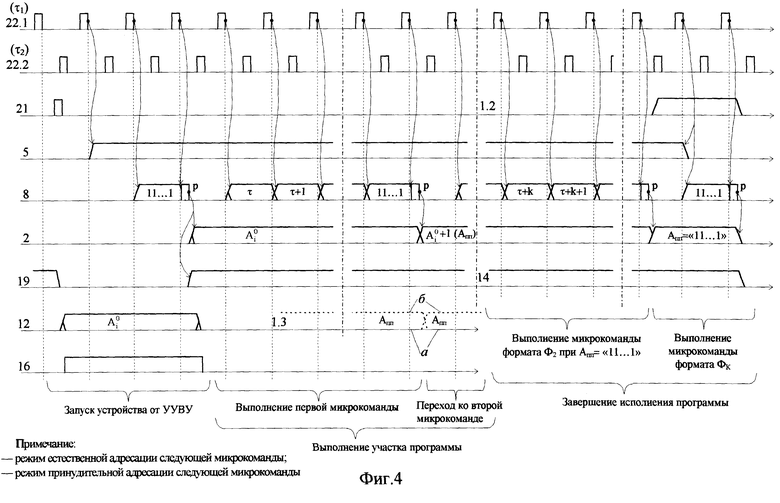

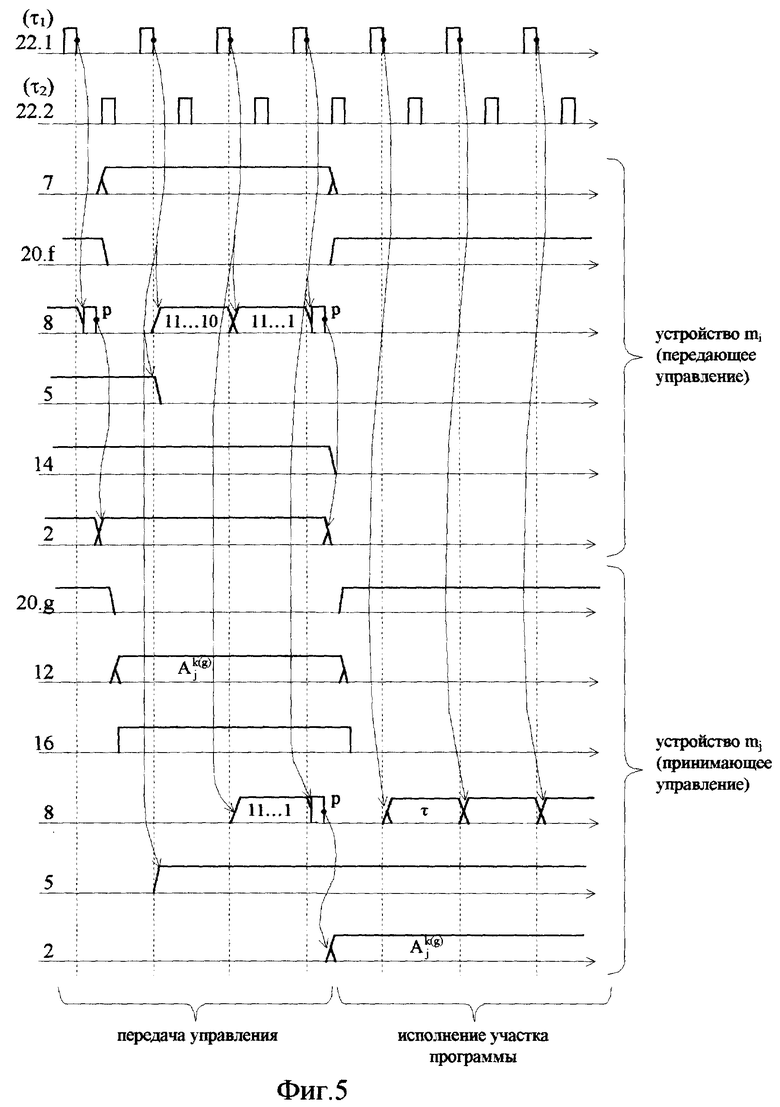

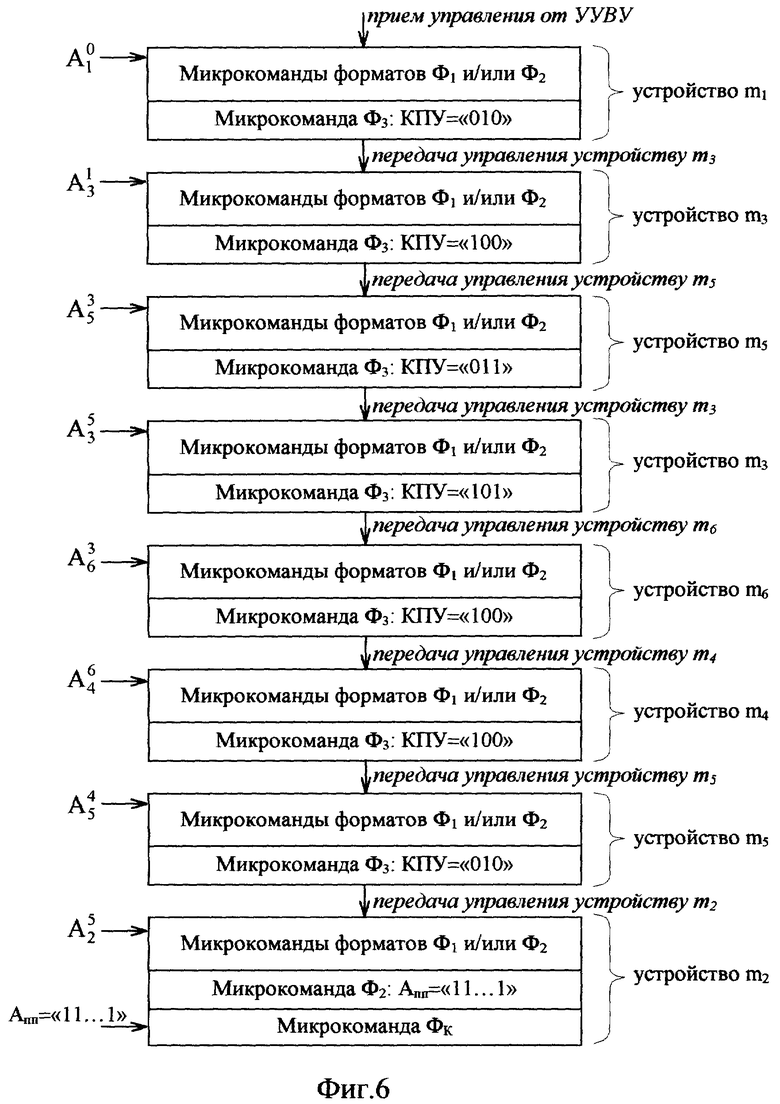

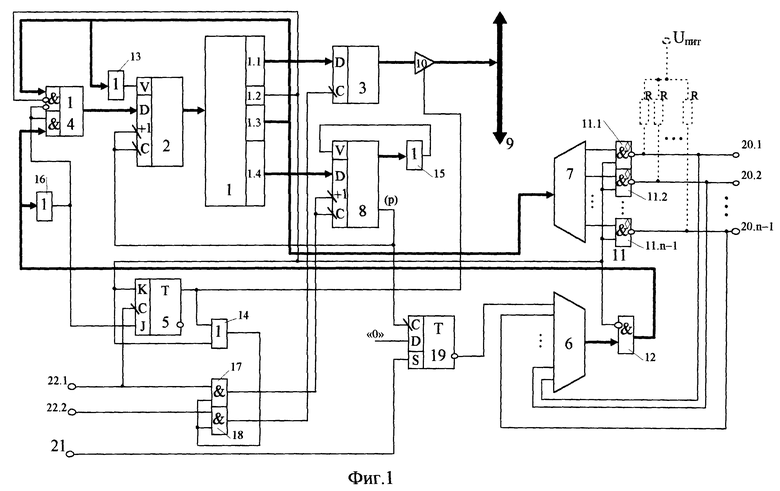

Сущность изобретения поясняется чертежами, где на фиг.1 изображена функциональная схема устройства программного управления; на фиг.2 представлены форматы микрокоманд, реализуемые устройством; на фиг.3 показана структурная схема системы управления, построенной на основе шести идентичных устройств; на фиг. 4 даны временные диаграммы работы устройства в режиме запуска, выполнения участка программы и завершения исполнения программы; на фиг.5 изображены временные диаграммы работы устройства в режиме межмодульной передачи/приема управления; на фиг.6 представлен пример, поясняющий процесс функционирования системы управления, изображенной на фиг.3, при реализации гипотетического алгоритма (программы) управления.

Устройство программного управления (фиг. 1) содержит блок памяти микрокоманд 1 с выходами 1.1 микроопераций, 1.2 признака формата, 1.3 адреса/кода передачи управления, 1.4 кода времени задержки, счетчик 2 адреса, регистр 3 микроопераций, коммутатор 4 направления приема адреса, триггер 5 режима, шифратор 6 направления приема управления, дешифратор 7 направления передачи управления, счетчик 8 времени задержки, шину 9 микроопераций, первый 13, второй 14, третий 15 и четвертый 16 элементы ИЛИ, первый 17 и второй 18 элементы И, причем выход элемента ИЛИ 13 соединен с управляющим входом счетчика 2 адреса, выход которого подключен к адресному входу блока 1 памяти микрокоманд, выход 1.2 признака формата которого подключен к K-входу триггера 5 режима и к первому входу элемента ИЛИ 14, выход которого соединен с первыми входами элементов И 17 и 18, прямой выход триггера 5 режима подключен ко второму входу элемента ИЛИ 14, выход 1.1 микроопераций блока 1 памяти микрокоманд подключен к информационному входу регистра 3 микроопераций, выход 1.4 кода времени задержки блока 1 памяти микрокоманд соединен с информационным входом счетчика 8 времени задержки, информационный выход которого соединен с входами элемента ИЛИ 15, выход которого подключен к управляющему входу счетчика 8 времени задержки, выход переноса которого соединен с входом синхронизации и счетным входом счетчика 2 адреса, информационный вход которого подключен к выходу коммутатора 4 направления приема адреса, выход элемента ИЛИ 16 соединен с J-входом триггера 5 режима, а также с прямым и первым инверсным управляющими входами коммутатора 4 направления приема адреса, первый вход 22.1 синхронизации устройства соединен с входом синхронизации триггера 5 режима и со вторым входом элемента И 17, выход которого подключен к входу синхронизации и счетному входу счетчика 8 времени задержки, второй вход 22.2 синхронизации устройства соединен со вторым входом элемента И 18, выход которого подключен к входу синхронизации регистра 3 микроопераций, выход 1.3 адреса/кода передачи управления блока 1 памяти микрокоманд соединен с входами элемента ИЛИ 13, с входом дешифратора 7 направления передачи управления, а также с первым информационным входом коммутатора 4 направления приема адреса, входы/выходы 20.1-20.n-1 инициализации устройства подключены к входам шифратора 6 направления приема управления с первого по (n-1)-й соответственно, а также дополнительно введенные блок 10 тристабильных элементов, группу 11 элементов И-НЕ (11.1-11/n-1), блок 12 элементов запрета и триггер 19 запуска, причем выход 1.2 признака формата блока 1 памяти микрокоманд соединен со вторым инверсным управляющим входом коммутатора 4 направления приема адреса, с инверсным входом блока 12 элементов запрета и с первыми входами элементов И-НЕ 11.1-11.n -1, вторые входы которых подключены к выходам дешифратора 7 направления передачи управления с первого по (n-1)-й соответственно, а выходы соединены с входами/выходами 20.1-20.n- 1 инициализации устройства соответственно, прямой выход триггера 5 режима соединен с управляющим входом блока 10 тристабильных элементов, информационный вход которого подключен к выходу регистра 3 микроопераций, а выход соединен с шиной 9 микроопераций, выход переноса счетчика 8 времени задержки подключен к входу синхронизации триггера 19 запуска, D-вход которого соединен с шиной логического нуля, вход 21 запуска устройства подключен к входу установки (S) триггера 19 запуска, инверсный выход которого соединен с n-м входом шифратора 6 направления приема управления, выход которого соединен с прямым входом блока 12 элементов запрета, выход которого подключен к входам элемента ИЛИ 16 и ко второму информационному входу коммутатора 4 направления приема адреса.

Назначение элементов устройства программного управления (фиг. 1) состоит в следующем.

Блок 1 памяти микрокоманд служит для постоянного хранения и выдачи микрокоманд, входящих в участки программ, закрепленные за текущим устройством. Очередная микрокоманда появляется на выходах блока 1 непосредственно после подачи на его адресный вход соответствующего адреса. В ячейке блока 1, имеющей адрес "00...0", размещена начальная микрокоманда формата Фн (фиг.2), соответствующая исходному состоянию устройства (указанная микрокоманда размещается в блоках 1 всех устройств системы управления). Если некоторое устройство реализует конечный участок программы управления, то в ячейке блока 1 этого устройства, имеющей адрес "11...1" (в последней ячейке блока 1), фиксируется конечная микрокоманда формата Фк (фиг.2), обеспечивающая приведение устройства в исходное состояние.

Счетчик 2 адреса предназначен для приема, хранения, модификации и выдачи адреса следующей микрокоманды. Счетчик 2 функционирует в одном из двух режимов в зависимости от сигнала на его управляющем входе (V). Если этот сигнал нулевой, то счетчик 2 работает в режиме счета и поступление заднего фронта очередного импульса на его счетный вход и вход синхронизации вызывает увеличение его содержимого на единицу. Если данный сигнал единичный, то счетчик 2 работает в режиме приема информации и появление заднего фронта импульса на его счетном входе и входе синхронизации обусловливает запись в него кода с информационного входа (D). (Вход синхронизации и счетный вход счетчика 2 соединены.)

Регистр 3 микроопераций используется для приема, временного хранения и выдачи кодов микроопераций.

Коммутатор 4 направления приема адреса обеспечивает подключение информационного входа счетчика 2 адреса либо к выходу 1.3 блока 1 памяти микрокоманд (если устройство выполняет участок программы), либо к выходу блока 12 элементов запрета (если устройство функционирует в режиме приема управления или запуска).

Триггер 5 режима служит для индикации текущего режима работы устройства. Единичное состояние триггера 5 соответствует рабочему режиму устройства, нулевое состояние определяет нахождение устройства в режиме ожидания запуска или передачи управления.

Шифратор 6 направления приема управления предназначен для формирования адреса приема управления при поступлении сигналов передачи управления от других устройств или сигнала запуска от устройства управления верхнего уровня (УУВУ).

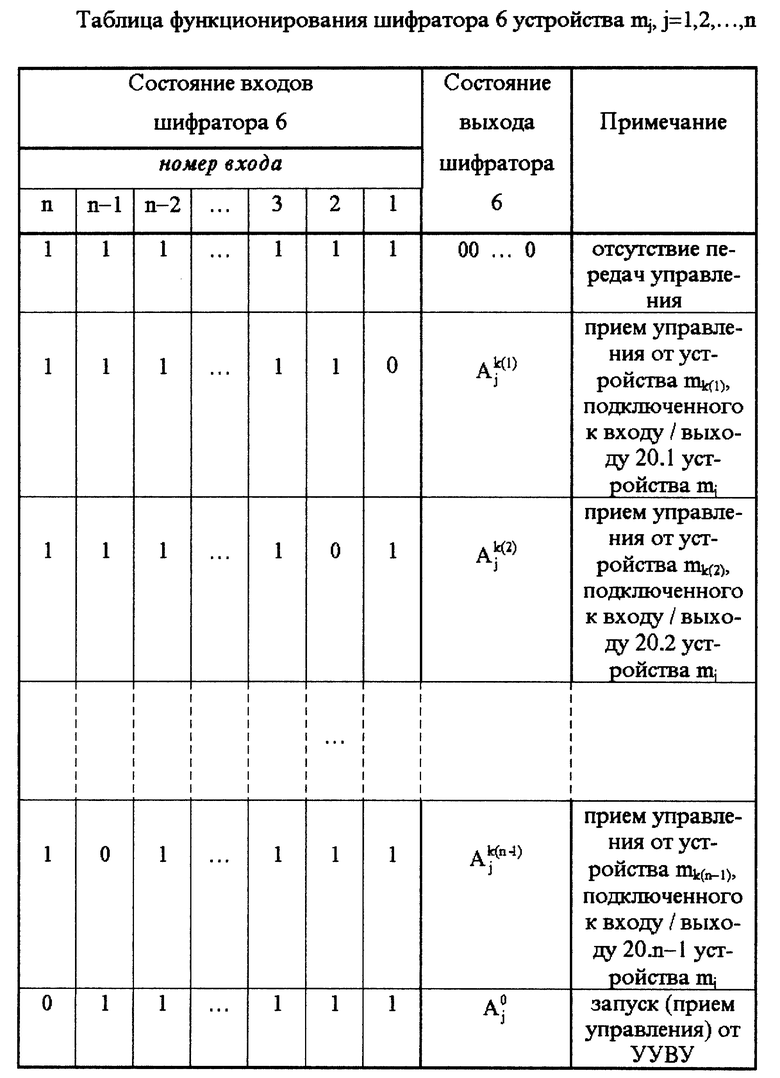

Настройка шифратора 6 и, соответственно, формирование адресов приема управления осуществляется в соответствии с таблицей (которая представлена в конце описания). Активным для шифратора 6 является нулевой (низкий) уровень сигнала. При отсутствии нулевых сигналов на входах шифратора 6 на его выходе присутствует нулевой код, соответствующий отсутствию передач управления. При наличии нулевого сигнала на одном из входов шифратора 6 на его выходе образуется ненулевой адрес приема управления, однозначно соответствующий устройству - инициатору передачи управления. (Указанный адрес аналогично прототипу однозначно определяется номером входа, или направлением, с которого поступает сигнал передачи управления.)

Дешифратор 7 направления передачи управления служит для выбора одного из n-1 возможных направлений передачи управления в соответствии с кодом на его входе и формирования единичного сигнала передачи управления на выходе, соответствующем выбранному направлению. Появление единичного сигнала на одном из выходов дешифратора 7 происходит непосредственно после подачи на его вход соответствующего кода передачи управления. При нулевом коде на входе дешифратора 7 на всех его выходах находятся сигналы логического нуля.

Счетчик 8 времени задержки предназначен для отсчета времени обработки (выдачи) микрокоманд. Указанное время (выраженное числом периодов следования импульсов синхронизации, формируемых внешним генератором тактовых импульсов (ГТИ, см. фиг. 3)) определяется разностью 2r+1- τ, где τ - код времени задержки, размещаемый в счетчике 8 (0< τ < 2r+1); r - разрядность счетчика 8. Максимальное время обработки микрокоманды задается кодом τ =00...01; обработка микрокоманды без задержки осуществляется при τ =11...11.

Счетчик 8 аналогично счетчику 2 адреса работает либо в режиме счета импульсов, либо в режиме приема информации. Переход в первый из указанных режимов происходит при единичном сигнале на управляющем входе (V) счетчика 8; во втором режиме счетчик 8 работает при нулевом сигнале на управляющем входе. (Вход синхронизации и счетный вход счетчика 8 соединены.)

Шина 9 микроопераций предназначена для передачи сигналов микроопераций с выходов блоков 10 различных устройств системы управления на входы объекта управления.

Блок 10 тристабильных элементов используется для отключения выхода регистра 3 от шины 9 микроопераций при переходе устройства в режим ожидания.

Группа 11 элементов И-НЕ (11.1-11.n-1) введена для формирования сигналов передачи управления другим устройствам системы управления. Элементы группы 11 имеют выходные каскады с "открытым" коллектором и поэтому выходы этих элементов подключаются к внешним сопротивлениям нагрузки R. Сопротивления R и соответствующие им связи показаны на фиг.1 пунктиром; через Uпит на фиг.1 обозначено напряжение источника питания устройства.

Введение элементов И-НЕ 11.1-11.n-1 с открытым коллектором позволяет использовать входы/выходы 20.1-20. n-1 устройства как для выдачи, так и для приема сигналов передачи управления. Если хотя бы на одном из входов элемента 11.f (f ∈ {1,2,..., n-1}) находится нулевой сигнал, то уровень сигнала на входе/выходе 20.f устройства определяется уровнем сигнала, поступающего на данный вход/выход от другого устройства. Таким образом обеспечивается возможность приема сигнала передачи управления по входу/выходу 20.f устройства. Если на входах элемента 11.f происходит совпадение единиц, то на выходе этого элемента устанавливается нулевой сигнал, который определяет уровень сигнала на входе/ выходе 20.f данного устройства и, следовательно, на входе/ выходе 20.g другого устройства, подключенном к входу/выходу 20.f данного устройства.

Блок 12 элементов запрета предназначен для запрещения прохождения информации с выхода шифратора 6 на входы элемента ИЛИ 16 и на второй информационный вход коммутатора 4 при функционировании текущего устройства в режиме передачи управления другому аналогичному устройству.

Элемент ИЛИ 13 предназначен для формирования сигнала - признака режима адресации следующей микрокоманды. При единичном сигнале на выходе элемента 13 реализуется режим принудительной адресации (счетчик 2 настроен на прием информации), при нулевом - режим естественной адресации (счетчик 2 работает в режиме счета).

Элемент ИЛИ 14 служит для объединения сигналов с выхода 1.2 блока 1 и прямого выхода триггера 5 режима.

Элемент ИЛИ 15 служит для формирования сигнала управления счетчиком 8 времени задержки.

Элемент ИЛИ 16 используется для формирования сигнала- признака приема управления.

Элементы И 17, 18 служат для запрещения передачи импульсов синхронизации с входов 22.1 и 22.2 устройства на счетный вход и вход синхронизации счетчика 8 времени задержки, а также на вход синхронизации регистра 3 микроопераций соответственно.

Триггер 19 запуска служит для фиксации сигнала (импульса) запуска системы управления от УУВУ на время инициализации устройства. Введение триггера 19 позволяет исключить требования к наименьшей длительности сигнала запуска системы (длительность данного сигнала должна быть достаточной для надежного переключения триггера 19; максимально допустимая длительность составляет два периода следования импульсов синхронизации).

Входы/выходы 20.1-20. n-1 инициализации устройства используются для выдачи сигналов передачи управления другим аналогичным устройствам и приема сигналов передачи управления от других устройств.

Вход 21 запуска устройства служит для приема сигнала (импульса) запуска системы управления от УУВУ.

Входы 22.1 и 22.2 синхронизации устройства используются для приема серий импульсов синхронизации τ1 и τ2 от внешнего генератора тактовых импульсов ГТИ (фиг.3).

Рассмотрим процесс работы предлагаемого устройства. Учитывая, что устройство предназначено для включения в состав системы управления, его работу будем рассматривать во взаимосвязи с другими аналогичными устройствами (модулями системы).

Первоначально счетчики 2 и 8, регистр 3, триггер 5 и триггер 19 устройства находятся в состоянии логического нуля (фиг. 1). (Цепи при ведения элементов устройства в исходное состояние на фиг. 1 не показаны.) Так как на выходе счетчика 2 присутствует нулевой код, на выходах блока 1 находится начальная микрокоманда формата Фн (фиг.2). Поскольку триггер 5 находится в нулевом состоянии, нулевой сигнал с его прямого выхода закрывает блок 10 тристабильных элементов и обеспечивает отключение выхода регистра 3 от шины 9 микроопераций. Этот же сигнал совместно с нулевым сигналом с выхода 1.2 блока 1 формирует нулевой сигнал на выходе элемента ИЛИ 14, закрывая тем самым элементы И 17, 18 и запрещая передачу импульсов синхронизации на их выходы. Так как счетчик 8 установлен в нулевое состояние, на выходе элемента ИЛИ 15 присутствует сигнал логического нуля. Этот сигнал, в свою очередь, воздействует на управляющий вход (V) счетчика 8 и обусловливает работу данного счетчика в режиме приема информации. Учитывая, что на выходе 1.3 блока 1 установлен единичный код (см. фиг.2), на выходе элемента ИЛИ 13 находится сигнал логической единицы. Данный сигнал воздействует на управляющий вход (V) счетчика 2 и настраивает этот счетчик на прием информации. Описанное исходное состояние характерно для каждого из устройств, образующих систему управления.

Поскольку на выходах 1.2 блоков 1 всех устройств системы управления находятся сигналы логического нуля, выходные транзисторы элементов группы 11 заперты и на входах/выходах 20.1-20. n-1 устройств присутствует высокий (единичный) уровень сигнала, обусловленный подключением заказанных входов/выходов к шине питания (Uпит) через внешние сопротивления нагрузки R (см. фиг. 1). Единичные сигналы с входов/выходов 20.1-20.n-1 поступают на входы шифратора 6 с первого по (n-1)-й соответственно и совместно с единичным сигналом, поступающим на n-й вход шифратора 6 с инверсного выхода триггера 19, формируют на выходе шифратора 6 нулевой код (см. таблицу, строка 1). Нулевое состояние выхода шифратора 6 обусловливает нулевое состояние выхода блока 12 элементов запрета.

Процесс функционирования устройства (и системы управления в целом) инициируется импульсом запуска системы, вырабатываемым устройством управления верхнего уровня. Синхронизация работы узлов различных устройств является централизованной и осуществляется единым генератором тактовых импульсов (ГТИ) системы управления (фиг. 3). Генератор вырабатывает две последовательности тактовых импульсов (импульсов синхронизации) τ1 и τ2, сдвинутые друг относительно друга на половину периода. Импульсы τ1 подаются на входы 22.1 устройств, а импульсы τ2 -на входы 22.2 устройств.

Импульс запуска системы управления подается на вход 21 одного из устройств, а именно, на вход 21 устройства mi, реализующего первую микрокоманду требуемой программы. Импульс запуска с входа 21 устройства mi поступает на вход установки (S) триггера 19 и устанавливает его в единичное состояние; на инверсном выходе триггера 19 появляется сигнал логического нуля. Нулевой сигнал с инверсного выхода триггера 19 подается на n-й вход шифратора 6 и совместно с единичными сигналами, находящимися на его остальных входах, обусловливает появление на выходе шифратора 6 ненулевого адреса Ai 0 приема управления от УУВУ (см. табл.), т.е. адреса первой микрокоманды реализуемой программы в блоке 1.

Адрес Ai 0 с выхода шифратора 6 проходит через открытый блок 12 и далее поступает на второй информационный вход коммутатора 4, а также на входы элемента ИЛИ 16. Так как адрес Ai 0 является ненулевым, на выходе элемента 16 появляется сигнал логической единицы - признак приема управления. Этот сигнал подается на J-вход триггера 5 и подготавливает данный триггер к переключению в единичное состояние. Одновременно этот же сигнал воздействует на прямой и первый инверсный управляющие входы коммутатора 4 и обеспечивает передачу адреса Ai 0 через коммутатор 4 на информационный вход счетчика 2.

Очередной импульс синхронизации τ1 c входа 22.1 устройства поступает на вход синхронизации триггера 5 и задним фронтом устанавливает его в единичное состояние. Единичный сигнал с прямого выхода триггера 5 поступает на управляющий вход блока 10 и обеспечивает подключение выхода регистра 3 к шине 9 микроопераций. Этот же сигнал проходит через элемент ИЛИ 14 на первые входы элементов И 17 и 18, открывает указанные элементы и разрешает тем самым прохождение импульсов синхронизации τ1 и τ2 на их выходы.

Очередной импульс τ2 с входа 22.2 устройства подается на второй вход элемента И 18, проходит на его выход и, поступая далее на вход синхронизации регистра 3, задним фронтом фиксирует в этом регистре нулевой код, установленный на выходе 1.1 блока 1.

Следующий импульс τ1 с входа 22.1 устройства поступает на вход синхронизации триггера 5 и подтверждает его единичное состояние. Этот же импульс проходит через открытый элемент И 17 на счетный вход и вход синхронизации счетчика 8. Так как счетчик 8 работает в режиме приема информации (на его управляющем входе находится нулевой сигнал), задний фронт импульса τ1 обеспечивает перезапись единичного кода с выхода 1.4 блока 1 в счетчик 8. Единичный код с информационного выхода указанного счетчика подается на входы элемента 15 и формирует на его выходе единичный сигнал - счетчик 8 переходит в режим счета.

Очередной импульс τ2 вновь вызывает перезапись нулевого кода с выхода 1.1 блока 1 в регистр 3.

Следующий импульс τ1 подтверждает единичное состояние триггера 5. Одновременно этот импульс проходит через элемент И 17 на счетный вход и вход синхронизации счетчика 8 и задним фронтом инициирует увеличение содержимого данного счетчика на единицу. Так как в счетчике 8 находится единичный код ("11. . . 1"), добавление к нему единицы приводит к переполнению счетчика 8. Счетчик 8 возвращается в нулевое состояние и вырабатывает на выходе переноса импульс переполнения p, по форме и длительности идентичный импульсам τ1 и τ2. На выходе элемента 15 снова образуется сигнал логического нуля и счетчик 8 возвращается в режим приема информации.

Импульс p с выхода переноса счетчика 8 поступает на счетный вход и вход синхронизации счетчика 2 и, так как последний функционирует в режиме приема информации, задним фронтом заносит в него адрес Ai 0, поступающий с выхода коммутатора 4. Адрес Ai 0 с выхода счетчика 2 подается на адресный вход блока 1 и обеспечивает считывание из блока 1 первой микрокоманды выполняемой программы. Одновременно импульс p подается на вход синхронизации триггера 19 запуска и задним фронтом возвращает его в исходное (нулевое) состояние. На инверсном выходе триггера 19 образуется сигнал логической единицы, соответственно, на выходе шифратора 6 восстанавливается нулевой код. На этом процесс запуска устройства mi (и системы управления в целом) завершается и устройство (система) приступает к исполнению программы управления.

Дальнейший ход работы устройства полностью определяется форматом считанной микрокоманды.

Временные диаграммы работы устройства в режиме запуска (приема управления) от УУВУ представлены на фиг.4 (слева).

Случай 1. Пусть очередная считанная из блока 1 микрокоманда имеет формат Ф1 или Ф2 (фиг.2). В этом случае на выходе 1.1 блока 1 образуется код микроопераций (МО), на выходе 1.3 формируется адресная информация, определяющая способ получения исполнительного адреса следующей микрокоманды, на выходе 1.4 появляется ненулевой код τ времени задержки (ВЗ), задающий время обработки считываемой микрокоманды, а на выходе 1.2 устанавливается нулевой сигнал - признак формата микрокоманды. Нулевой сигнал с выхода 1.2 блока 1 поступает на второй инверсный управляющий вход коммутатора 4 и совместно с нулевым сигналом с выхода элемента ИЛИ 16, поступающим на первый инверсный управляющий вход данного коммутатора, настраивает его на передачу информации с выхода 1.3 блока 1 на информационный вход счетчика 2. Кроме того, нулевой сигнал с выхода 1.2 блока 1 блокирует элементы И-НЕ группы 11, обусловливая наличие на их выходах сигнала логической единицы.

Очередной импульс синхронизации τ2 через открытый элемент И 18 проходит на вход синхронизации регистра 3 и задним фронтом фиксирует в данном регистре код МО, поступающий с выхода 1.1 блока 1. Далее код МО с выхода регистра 3 через открытый блок 10 передается на шину 9 микроопераций, откуда поступает на вход объекта управления.

Следующий импульс τ1 через открытый элемент И 17 проходит на счетный вход и вход синхронизации счетчика 8 и поскольку последний работает в режиме приема информации, задним фронтом фиксирует в нем код В3 (τ) с выхода 1.4 блока 1. Так как код τ является ненулевым, на выходе элемента ИЛИ 15 образуется единичный сигнал. Данный сигнал воздействует на управляющий вход счетчика 8 и переводит счетчик 8 в режим счета.

Очередной импульс τ2, проходя через элемент 18 на вход синхронизации регистра 3, вновь фиксирует в указанном регистре код МО.

Следующий импульс τ1 через элемент 17 подается на счетный вход и вход синхронизации счетчика 8 и увеличивает его содержимое на единицу. Если исходный код, записанный в счетчике 8, отличен от единичного, то переполнение счетчика 8 не происходит; соответственно, на выходе элемента 15 сохраняется сигнал логической единицы и счетчик 8 продолжает функционировать в режиме счета. Следующий импульс τ2 снова фиксирует код МО в регистре 3.

Описанным выше образом устройство продолжает функционировать до тех пор, пока в счетчике 8 не будет зафиксирован единичный код. В этом случае по заднему фронту очередного импульса τ1 счетчик 8 переходит в нулевое состояние и вырабатывает на выходе переноса импульс p. Нулевой код, образующийся на информационном выходе счетчика 8, формирует нулевой сигнал на выходе элемента 15 и тем самым обусловливает возврат счетчика 8 в режим приема информации. Импульс p с выхода переноса счетчика 8 подтверждает нулевое состояние триггера 19. Одновременно импульс p поступает на счетный вход и вход синхронизации счетчика 2 и фиксирует в нем исполнительный адрес следующей микрокоманды.

Формирование адреса следующей микрокоманды происходит одновременно с обработкой текущей микрокоманды. Данный адрес может быть получен одним из двух способов в зависимости от кода на выходе 1.3 блока 1 (т.е. от содержимого поля адреса/кода передачи управления текущей микрокоманды (фиг.2)).

1. Если на выходе 1.3 блока 1 находится нулевой код (текущая микрокоманда имеет формат Ф1), то имеет место естественная адресация следующей микрокоманды. Нулевой код с выхода 1.3 блока 1 поступает на входы элемента ИЛИ 13 и формирует на его выходе нулевой сигнал. Этот сигнал воздействует на управляющий вход (V) счетчика 2 и переводит счетчик 2 в режим счета. Импульс p с выхода переноса счетчика 8 поступает на счетный вход счетчика 2 и задним фронтом увеличивает его содержимое - адрес текущей микрокоманды - на единицу.

2. Если на выходе 1.3 блока 1 присутствует ненулевой код (текущая микрокоманда имеет формат Ф2), то имеет место принудительная адресация следующей микрокоманды. В этом случае код с выхода 1.3 блока 1, интерпретируемый как адрес принудительного перехода (Aпп), формирует единичный сигнал на выходе элемента 13 и тем самым переводит счетчик 2 в режим приема информации. Одновременно данный код (адрес Aпп) проходит через открытый коммутатор 4 на информационный вход счетчика 2. Импульс p с выхода переноса счетчика 8 подается на вход синхронизации счетчика 2 и фиксирует в нем адрес Aпп.

Исполнительный адрес следующей микрокоманды с выхода счетчика 2 поступает на адресный вход блока 1 и обеспечивает считывание следующей микрокоманды программы. Процесс обработки считываемой микрокоманды аналогичен описанному выше.

Временные диаграммы работы устройства в рассмотренном режиме показаны на фиг.4.

Случай 2. Если очередная считанная из блока 1 микрокоманда имеет формат Ф3 (фиг. 2), то устройство mi переходит в режим передачи управления другому аналогичному устройству системы управления. На выходе 1.1 блока 1 образуется код МО, на выходе 1.2 появляется единичный сигнал - признак формата микрокоманды, на выходе 1.4 формируется код "11...10", а на выходе 1.3 устанавливается код передачи управления (КПУ). Код передачи управления представляет собой двоичный код номера входа/выхода инициализации i-го устройства, к которому подключено устройство, принимающее управление, и, таким образом, аналогично прототипу может рассматриваться как код направления передачи управления.

Единичный сигнал с выхода 1.2 блока 1 поступает на инверсный вход блока 12 элементов запрета и запрещает прохождение информации с выхода шифратора 6 через этот блок; на выходе блока 12 устанавливается нулевой код. Этот же сигнал открывает элементы группы 11. Одновременно единичный сигнал с выхода 1.2 блока 1 подается на K-вход триггера 5, подтверждает единичный уровень сигнала на выходе элемента ИЛИ 14 и, поступая также на второй инверсный управляющий вход коммутатора 4, блокирует передачу информации с выхода 1.3 блока 1 на информационный вход счетчика 2. Поскольку на выходе блока 12 присутствует нулевой код, на выходе элемента ИЛИ 16 устанавливается сигнал логического нуля. Этот сигнал поступает на прямой управляющий вход коммутатора 4. Так как на прямом и втором инверсном управляющих входах коммутатора 4 находятся запрещающие (соответственно нулевой и единичный) сигналы, на его выходе устанавливается нулевой код - передача информации на информационный вход счетчика 2 заблокирована.

Одновременно код передачи управления с выхода 1.3 блока 1 подается на входы элемента ИЛИ 13 и, будучи отличным от нулевого, формирует на выходе этого элемента единичный сигнал. Данный сигнал переводит счетчик 2 в режим приема информации и тем самым подготавливает устройство mi, к последующему переключению в исходное состояние (на информационном входе счетчика 2 находится нулевой код).

В то же самое время код с выхода 1.3 блока 1 подается на вход дешифратора 7. В результате на одном из выходов дешифратора 7, а именно, на выходе, соответствующем входу/выходу инициализации i-го устройства, к которому подключено устройство mj, принимающее управление, формируется сигнал логической единицы. Допустим, что данным выходом является f-й выход дешифратора 7, f ∈ (1,2,...,n-1}. Единичный сигнал с f-го выхода дешифратора 7 поступает на второй вход f-го элемента И-НЕ (11.f) группы 11 и, так как на первом входе этого элемента находится единичный признак формата микрокоманды, формирует на его выходе нулевой сигнал. Этот сигнал передается на вход/выход 20.f i-го устройства и обеспечивает запуск устройства mj, принимающего управление. Сигнал с выхода элемента 11.f воздействует также на f-й вход шифратора 6, однако, поскольку передача информации с выхода шифратора 6 через блок 12 запрещена единичным сигналом на инверсном входе блока 12, рассматриваемый сигнал игнорируется устройством mi (не воспринимается как сигнал передачи управления от другого устройства). На выходе элемента 16 i-го устройства, соответственно, сохраняется нулевой уровень сигнала.

Очередной импульс τ2 с входа 22.2 устройства mi через открытый элемент И 18 проходит на вход синхронизации регистра 3 и фиксирует в нем код МО с выхода 1.1 блока 1. Указанный код через блок 10 передается на шину 9 и далее поступает на вход объекта управления.

Одновременно нулевой сигнал с входа/выхода 20.f устройства mi передается на вход/выход 20. g устройства mi (устройства, принимающего управление). (Устройство mj находится в исходном состоянии, соответственно, на выходе 1.2 блока 1 j-го устройства присутствует нулевой сигнал, поэтому все элементы группы 11 заблокированы и уровень сигнала на их выходах определяется сигналами, поступающими с входов/выходов 20.1-20.n-1 j-го устройства от других устройств. ) Далее этот сигнал с входа/выхода 20.g j-го устройства подается на g-й вход шифратора 6 и формирует на его выходе адрес приема управления Aj k(g) (см. табл., k(g)=i - номер устройства, передающего управление). Адрес Aj k(g) через открытый блок 12 элементов запрета поступает на второй информационный вход коммутатора 4, а также на входы элемента ИЛИ 16, устанавливая на выходе последнего единичный сигнал. Сигнал с выхода элемента 16 поступает на J-вход триггера 5 и тем самым подготавливает триггер 5 к переключению в единичное состояние. Этот же сигнал подается на прямой и первый инверсный управляющие входы коммутатора 4 и обеспечивает прохождение адреса Aj k(g) с его второго информационного входа на информационный вход счетчика 2.

Очередной импульс τ1 одновременно появляется на входах 22.1 i-го и j-го устройств и вызывает следующие действия.

1. Устройство mi (передающее управление). Импульс τ1 с входа 22.1 i-го устройства поступает на вход синхронизации триггера 5 и, так как на K-входе этого триггера находится единичный сигнал - признак формата микрокоманды, задним фронтом устанавливает его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 5 поступает на управляющий вход блока 10 и отключает выход регистра 3 от шины 9, запрещая тем самым передачу МО на объект управления i-му устройству. (Так как на первом входе элемента 14 находится единичный сигнал, переключение триггера 5 в нулевое состояние не вызывает изменение уровня сигнала на выходе элемента 14, соответственно, элементы И 17 и 18 остаются открытыми.)

Одновременно импульс τ1 через открытый элемент И 17 передается на счетный вход и вход синхронизации счетчика 8 и, учитывая, что последний настроен на прием информации, задним фронтом фиксирует в нем код "11...10" с выхода 1.4 блока 1. На выходе элемента 15 формируется единичный сигнал и счетчик 8 переходит в режим счета.

2. Устройство mj (принимающее управление). Импульс τ1 с входа 22.1 j-го устройства поступает на вход синхронизации триггера 5 и, так как на J-входе этого триггера находится единичный сигнал, переводит его в единичное состояние. Единичный сигнал с прямого выхода триггера 5 открывает блок 10 тристабильных элементов и обеспечивает подключение выхода регистра 3 к шине 9, разрешая тем самым выдачу сигналов МО на объект управления j-му устройству. Этот же сигнал через элемент ИЛИ 14 открывает элементы И 17 и 18 и обеспечивает последующее прохождение на их выходы импульсов синхронизации τ1 и τ2.

Следующий импульс τ2, проходя через открытые элементы И 18 i-го и j-го устройств, фиксирует код МО в регистре 3 i-го устройства и заносит нулевой код в регистр 3 j-го устройства.

Появление очередного импульса τ1 приводит к следующим действиям.

1. Устройство mi (передающее управление). Импульс τ1, поступая с входа 22.1 устройства на вход синхронизации триггера 5, подтверждает его нулевое состояние. Одновременно импульс τ1/ проходит через открытый элемент 17 на счетный вход и вход синхронизации счетчика 8 и, поскольку последний настроен на режим счета, увеличивает его содержимое на единицу. В результате в счетчике 8 фиксируется код "11...1". На выходе элемента 15 сохраняется единичный уровень сигнала и счетчик 8 продолжает работать в режиме счета.

2. Устройство mj (принимающее управление). Импульс τ1 поступает на вход синхронизации триггера 5 и подтверждает его единичное состояние. Одновременно указанный импульс проходит через элемент 17 на счетный вход и вход синхронизации счетчика 8 и, так как последний функционирует в режиме приема информации, записывает в него единичный код с выхода 1.4 блока 1. На выходе элемента 15 появляется сигнал логической единицы и счетчик 8 переходит в режим счета.

Следующий импульс τ2 вызывает те же действия, что и предшествующий импульс τ2.

Очередной импульс τ1 проходит через элементы И 17 на счетные входы счетчиков 8 i-го и j-го устройств и вызывает их одновременное переполнение. На информационных выходах счетчиков 8 появляются нулевые коды, а на выходах переноса одновременно формируются импульсы переполнения p.

Дальнейшая работа устройств mi и mj происходит следующим образом.

1. Устройство mi (передающее управление). Импульс p с выхода переноса счетчика 8 подается на счетный вход и вход синхронизации счетчика 2 и, поскольку последний находится в режиме приема информации, причем на его информационном входе присутствует нулевой код с выхода коммутатора 4, устанавливает счетчик 2 в нулевое состояние. Нулевой код с выхода счетчика 2 поступает на адресный вход блока 1 и обеспечивает считывание микрокоманды формата Фн (фиг.2) - устройство mi возвращается в исходное состояние. На выходе 1.2 блока 1 восстанавливается нулевой уровень сигнала. На выходе элемента 14 также устанавливается нулевой сигнал, который закрывает элементы И 17, 18.

2. Устройство mj (принимающее управление). Импульс p с выхода переноса счетчика 8 поступает на счетный вход и вход синхронизации счетчика 2 и фиксирует в нем адрес приема управления Aj k(g), поступающий через блок 12 и коммутатор 4 на его информационный вход. Адрес Aj k(g) с выхода счетчика 2 подается на адресный вход блока 1 и обусловливает появление на его выходах первой микрокоманды участка программы, выполняемого устройством mj.

На этом процесс передачи управления завершается: на выходе элемента И-НЕ 11.f i-го устройства восстанавливается единичный сигнал, на входе/выходе 20. g j-го устройства, соответственно, также формируется сигнал логической единицы, на выходе шифратора 6 j-го устройства появляется нулевой код, на выходе элемента ИЛИ 16 j-го устройства восстанавливается нулевой уровень сигнала. Временные диаграммы работы устройства в режиме передачи управления изображены на фиг.5.

Случай 3. Если считанная из блока 1 микрокоманда имеет формат Фк (фиг. 2), то устройство переходит в режим окончания выполнения программы. Микрокоманда Фк размещается в последней ячейке блока 1 (в ячейке, имеющей адрес "11. . . 1"), поэтому предшествующая ей (предпоследняя) микрокоманда должна иметь формат Ф2 (т. е. предусматривать принудительную адресацию следующей микрокоманды) и содержать в поле 1.3 единичный код (Aпп="11...1"). На выходе 1.1 блока 1 формируется код МО, на выходе 1.2 образуется единичный сигнал - признак формата микрокоманды, а на выходах 1.3 и 1.4 появляются соответственно нулевой и единичный коды.

Нулевой код с выхода 1.3 блока 1 поступает на входы элемента ИЛИ 13 и формирует на его выходе нулевой сигнал. Данный сигнал передается на управляющий вход счетчика 2 и переводит его в режим счета. Единичный сигнал с выхода 1.2 блока 1 поступает на K-вход триггера 5, а также подтверждает единичный уровень сигнала на выходе элемента 14. Кроме того, этот сигнал открывает элементы группы 11 и запрещает прохождение информации через блок 12, формируя на его выходе нулевой код. Нулевой код с выхода блока 12 формирует нулевой сигнал на выходе элемента ИЛИ 16.

Так как на выходе 1.3 блока 1 находится нулевой код, на всех выходах дешифратора 7 устанавливается нулевой уровень сигнала, что, в свою очередь, приводит к блокировке всех элементов группы 11. Таким образом, на входах/выходах 20.1-20.n-1 устройства сохраняется единичный уровень сигнала.

Очередной импульс τ2 через элемент И 18 проходит на вход синхронизации регистра 3 и фиксирует в нем заключительный код МО. Указанный код через открытый блок 10 передается на шину 9 и поступает на вход объекта управления.

Следующий импульс τ1 поступает на вход синхронизации триггера 5 и устанавливает его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 5 закрывает блок 10 и тем самым отключает выход регистра 3 от шины 9 микроопераций. Одновременно данный импульс через элемент 17 подается на вход синхронизации и счетный вход счетчика 8 и записывает в него единичный код с выхода 1.4 блока 1. На выходе элемента 15 формируется сигнал логической единицы и счетчик 8 переходит в режим счета.

Очередной импульс τ1 через элемент 17 проходит на счетный вход и вход синхронизации счетчика 8 и инициирует увеличение его содержимого на единицу. Поскольку в счетчике 8 зафиксирован единичный код, счетчик 8 переключается в нулевое состояние и вырабатывает на выходе переноса импульс переполнения p. Импульс p поступает на счетный вход и вход синхронизации счетчика 2 и, так как последний работает в режиме счета, увеличивает его содержимое на единицу. Однако, поскольку в счетчике 2 находится код (адрес Aпп) "11...1", прибавление к нему единицы вызывает переполнение и возврат счетчика 2 в нулевое состояние. Нулевой код с выхода счетчика 2 поступает на адресный вход блока 1 и обеспечивает появление на его выходах микрокоманды формата Фн (фиг. 2). На выходе элемента 14 восстанавливается нулевой уровень сигнала, который закрывает элементы И 17 и 18 и запрещает прохождение на их выходы следующих импульсов синхронизации τ1 и τ2. Таким образом, устройство (и система управления в целом) завершает исполнение программы и возвращается в исходное состояние.

Временные диаграммы работы устройства в режиме окончания выполнения программы показаны на фиг.4 (справа).

Пример, поясняющий функционирование системы управления, представленной на фиг. 3, при реализации гипотетического алгоритма (программы), показан на фиг.6.

Работа системы начинается с момента запуска устройства mi (предполагается, что устройство mi реализует начальный участок выполняемой программы управления). Первая микрокоманда, считываемая устройством mi, размещается в блоке 1 по адресу A1 0 (адрес A1 0 формируется шифратором 6). В процессе функционирования устройство mi считывает последовательность микрокоманд формата Ф1 и/или Ф2, завершающуюся микрокомандой передачи управления формата Ф3. В ходе обработки микрокоманды Ф3 устройство mi формирует код передачи управления и осуществляет передачу управления устройству m3. Исходя из способа подключения устройств, принятого в схеме на фиг.3, КПУ равен "010" (что обеспечивает выдачу сигнала передачи управления на вход/выход 20.2 устройства mi).

Сигнал передачи управления поступает на вход/выход 20.1 устройства m3 и обеспечивает запуск устройства m3 по адресу A3 1, формируемому шифратором 6 данного устройства. После запуска устройство m3 аналогично устройству m1 считывает последовательность микрокоманд формата Ф1 и/или Ф2 и осуществляет передачу управления следующему устройству m5. В этом случае КПУ равен "100" (сигнал передачи управления выдается на вход/выход 20.4 устройства m3). Дальнейшее выполнение программы происходит аналогично рассмотренному выше.

Заключительный участок программы исполняется устройством m2. Устройство m2 считывает последовательность микрокоманд формата Ф1 и/или Ф2, после чего выполняет микрокоманду Ф2, обеспечивающую принудительный переход по адресу Aпп="11...1". Далее устройство m2 считывает микрокоманду Фк по адресу "11... 1" и переходит в исходное состояние. Таким образом, система управления завершает выполнение программы.

Как следует из описания, предлагаемое устройство обладает всеми функциональными возможностями устройства - прототипа, позволяя формировать многомодульные системы управления, ориентированные на реализацию комплексных алгоритмов (программ) управления значительной сложности. В то же время при построении систем управления на основе предлагаемого устройства достигается двукратное сокращение числа линий связи, требуемых для организации межмодульного взаимодействия (передачи управления). Сокращение числа межмодульных линий связи дает возможность увеличения предельного числа устройств в составе системы управления, которое ограничивается допустимой сложностью межмодульного интерфейса и/или максимальным числом входов/выходов устройства (например, при реализации отдельных устройств в виде СБИС). Это, в свою очередь, позволяет расширить класс реализуемых системой алгоритмов управления, а следовательно, и область применения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ СИСТЕМЫ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2145434C1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1999 |

|

RU2168198C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем управления технологическими процессами. Технический результат заключается в расширении области применения устройства за счет минимизации числа внешних входов и выходов, требуемых для организации взаимодействия с другими аналогичными устройствами в составе системы управления. Технический результат достигается за счет использования двунаправленных линий (входов/выходов) передачи управления, а также за счет того, что устройство содержит блок памяти микрокоманд, счетчик адреса, регистр микроопераций, коммутатор направления приема адреса, триггер режима, шифратор направления приема управления, дешифратор направления передачи управления, счетчик времени задержки, шину микроопераций, четыре элемента ИЛИ, два элемента И, блок тристабильных элементов, группу элементов И-НЕ, блок элементов запрета и триггер запуска. Для взаимодействия каждой пары устройств в составе системы управления требуется одна физическая линия связи. 6 ил., 1 табл.

Устройство программного управления, содержащее блок памяти микрокоманд, счетчик адреса, регистр микроопераций, коммутатор направления приема адреса, триггер режима, шифратор направления приема управления, дешифратор направления передачи управления, счетчик времени задержки, шину микроопераций, с первого по четвертый элементы ИЛИ, первый и второй элементы И, причем выход первого элемента ИЛИ соединен с управляющим входом счетчика адреса, выход которого подключен к адресному входу блока памяти микрокоманд, выход признака формата которого подключен к К-входу триггера режима и к первому входу второго элемента ИЛИ, выход которого соединен с первыми входами первого и второго элементов И, прямой выход триггера режима подключен к второму входу второго элемента ИЛИ, выход микроопераций блока памяти микрокоманд - к информационному входу регистра микроопераций, выход кода времени задержки блока памяти микрокоманд соединен с информационным входом счетчика времени задержки, информационный выход которого соединен с входами третьего элемента ИЛИ, выход которого подключен к управляющему входу счетчика времени задержки, выход переноса которого соединен с входом синхронизации и счетным входом счетчика адреса, информационный вход которого подключен к выходу коммутатора направления приема адреса, выход четвертого элемента ИЛИ соединен с J-входом триггера режима, а также с прямым и первым инверсным управляющими входами коммутатора направления приема адреса, первый

вход синхронизации устройства соединен с входом синхронизации триггера режима и с вторым входом первого элемента И, выход которого подключен к входу синхронизации и счетному входу счетчика времени задержки, второй вход синхронизации устройства соединен с вторым входом второго элемента И, выход которого подключен к входу синхронизации регистра микроопераций, выход адреса/кода передачи управления блока памяти микрокоманд соединен с входами первого элемента ИЛИ, с входом дешифратора направления передачи управления, а также с первым информационным входом коммутатора направления приема адреса, входы/выходы инициализации устройства с первого по (n-1)-й (где n - число идентичных устройств в составе системы управления) подключены к входам шифратора направления приема управления с первого по (n-1)-й соответственно, отличающееся тем, что в него дополнительно введены блок тристабильных элементов, группа элементов И - НЕ, блок элементов запрета и триггер запуска, причем выход признака формата блока памяти микрокоманд соединен с вторым инверсным управляющим входом коммутатора направления приема адреса, с инверсным входом блока элементов запрета и с первыми входами элементов И - НЕ группы с первого по (n - 1)-й, вторые входы которых подключены к выходам дешифратора направления передачи управления с первого по (n - 1)-й соответственно, а выходы соединены с входами/выходами инициализации устройства с первого по (n - 1)-й соответственно, прямой выход триггера режима соединен с управляющим входом блока тристабильных элементов, информационный вход которого подключен к выходу регистра микроопераций, а выход соединен с шиной микроопераций, выход переноса счетчика времени задержки подключен к входу синхронизации триггера запуска, D-вход которого соединен с шиной логического нуля, вход запуска устройства подключен к входу установки триггера запуска, инверсный выход которого соединен с n-м входом шифратора направления приема управления, выход которого соединен с прямым входом блока элементов запрета, выход которого подключен к входам четвертого элемента ИЛИ и к второму информационному входу коммутатора направления приема адреса.

| Устройство для программного управления | 1991 |

|

SU1800445A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| СХЕМА ВОЗБУЖДЕНИЯ УСТРОЙСТВА ОТОБРАЖЕНИЯ, УСТРОЙСТВО ОТОБРАЖЕНИЯ И СПОСОБ ВОЗБУЖДЕНИЯ УСТРОЙСТВА ОТОБРАЖЕНИЯ | 2010 |

|

RU2491654C1 |

Авторы

Даты

2000-02-27—Публикация

1999-01-19—Подача