Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах различного назначения.

Известна вычислительная система, описанная в работе [1], содержащая микропроцессор (процессорный модуль), шину адреса (системную интерфейсную магистраль адреса), шину данных (системную интерфейсную магистраль данных), шину управления (системную интерфейсную магистраль управления), оперативное запоминающее устройство, постоянное запоминающее устройство и контроллер связи с внешними устройствами, объединенные соответствующими связями.

Известна вычислительная система по свидетельству РФ на полезную модель [2] . Эта вычислительная система содержит вычислительный модуль, содержащий внутренние системные магистрали адреса, данных и управления, а также центральный процессор, оперативное запоминающее устройство, постоянное запоминающее устройство и контроллер связи с внешними устройствами. Вычислительная система [2] дополнительно содержит элемент ИЛИ, коммутирующий элемент, внешний соединитель, при этом контроллер связи с внешними устройствами имеет вход сигнала "свой". В системе [2] оперативное запоминающее устройство и постоянное запоминающее устройство имеют выходы сигнала "свой", выход сигнала "свой" оперативного запоминающего устройства соединен с первым входом элемента ИЛИ, выход сигнала "свой" постоянного запоминающего устройства соединен с первым выводом коммутирующего элемента, второй вывод коммутирующего элемента соединен со вторым входом элемента ИЛИ, выход элемента ИЛИ соединен со входом сигнала "свой" контроллера связи с внешними устройствами, выводы коммутирующего элемента соединены с контактами внешнего соединителя.

Вычислительная система [2] позволяет монтировать незапрограммированное постоянное запоминающее устройство с последующим его программированием на основе программ во внешнем запоминающем устройстве и/или программ, загружаемых в оперативное запоминающее устройство, восстанавливать испорченные (ошибочно стертые) программы в постоянном запоминающем устройстве без его демонтажа из системы, отрабатывать и тестировать новые версии программного обеспечения без стирания старых версий в постоянном запоминающем устройстве.

Известна вычислительная система по свидетельству РФ на полезную модель [3] , являющаяся наиболее близкой к предлагаемой. Вычислительная система [3] содержит центральный процессор (процессорный модуль), системную интерфейсную магистраль адреса, системную интерфейсную магистраль данных, системную интерфейсную магистраль управления и n периферийных модулей, выполненных, в частности, в виде постоянного запоминающего устройства, оперативного запоминающего устройства и других устройств. Вычислительная система содержит также блок элементов Исключающее ИЛИ и вход выбора стартового адреса, при этом младшие разряды входа адреса постоянного запоминающего устройства соединены с внутренней системной магистралью адреса, старшие разряды входа адреса постоянного запоминающего устройства соединены с выходами блока элементов Исключающее ИЛИ, первые входы которого соединены с внутренней системной магистралью адреса, а вторые - со входом выбора стартового адреса. Входы адреса каждого из n периферийных модулей соединены посредством системной интерфейсной магистрали адреса с выходами адреса процессорного модуля, входы-выходы данных каждого из n периферийных модулей соединены посредством системной интерфейсной магистрали данных с входами-выходами данных процессорного модуля, входы-выходы управления каждого из n периферийных модулей соединены посредством системной интерфейсной магистрали управления с входами-выходами управления процессорного модуля.

Вычислительная система [3] позволяет использовать две различные независимые стартовые программы. Например, одна из этих программ может быть предназначена для проведения заводской регулировки и тестирования, а другая для осуществления запуска и обеспечения работы пользовательского программного обеспечения.

Недостатком вычислительной системы-прототипа является невозможность использования в вычислительной системе нескольких периферийных модулей, имеющих один и тот же базовый (свой) адрес.

Задачей изобретения является обеспечение возможности назначения своего адреса любому периферийному модулю, включаемому в вычислительную систему.

Сущность предлагаемого изобретения заключается в том, что в вычислительной системе, содержащей процессорный модуль, системную интерфейсную магистраль адреса, системную интерфейсную магистраль данных, системную интерфейсную магистраль управления и n периферийных модулей, каждый из n периферийных модулей дополнительно содержит блок управления, регистр, блок сравнения и дешифратор сигнала записи, при этом входы адреса каждого из n периферийных модулей соединены посредством системной интерфейсной магистрали адреса с выходами адреса процессорного модуля, входы-выходы данных каждого из n периферийных модулей соединены посредством системной интерфейсной магистрали данных с входами-выходами данных процессорного модуля, входы-выходы управления каждого из n периферийных модулей соединены посредством системной интерфейсной магистрали управления с входами-выходами управления процессорного модуля, вход инициализации первого периферийного модуля соединен с выходом инициализации процессорного модуля, вход инициализации каждого из последующих периферийных модулей соединен с выходом инициализации предыдущего периферийного модуля, выход инициализации n-го периферийного модуля соединен со входом инициализации процессорного модуля, в каждом из n периферийных модулей первый вход блока управления является входом инициализации данного периферийного модуля, первый выход блока управления является выходом инициализации данного периферийного модуля, второй выход блока управления соединен с входом разрешения работы регистра, выходы регистра соединены со вторыми входами блока сравнения, второй вход блока управления и вход сигнала записи регистра соединены с выходом дешифратора сигнала записи, входы данных регистра и входы-выходы данных функциональной части данного периферийного модуля соединены с системной интерфейсной магистралью данных, первые входы блока сравнения и входы адреса функциональной части данного периферийного модуля соединены с системной интерфейсной магистралью адреса, входы-выходы управления функциональной части данного периферийного модуля и вход дешифратора сигнала записи соединены с системной интерфейсной магистралью управления, вход разрешения работы функциональной части данного периферийного модуля соединен с выходом блока сравнения.

Функциональная часть каждого из n периферийных модулей может быть выполнена, в частности, в виде запоминающего устройства.

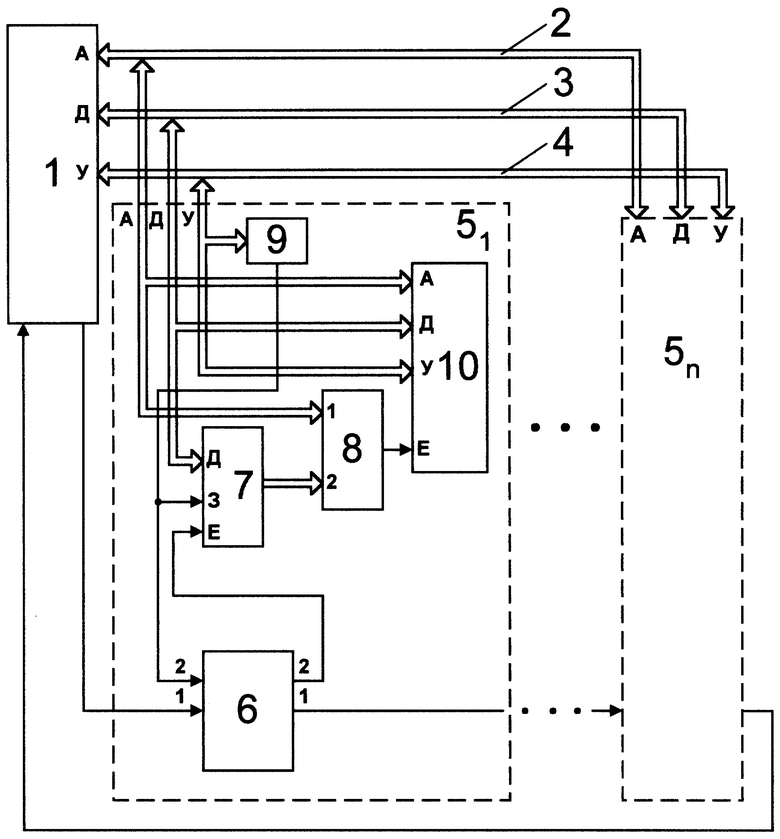

Сущность предлагаемого изобретения поясняется чертежом, на котором обозначены:

1 - процессорный модуль;

2 - системная интерфейсная магистраль адреса;

3 - системная интерфейсная магистраль данных;

4 - системная интерфейсная магистраль управления;

51 - первый периферийный модуль;

5n - n-й периферийный модуль;

6 - блок управления;

7 - регистр;

8 - блок сравнения;

9 - дешифратор сигнала записи;

10 - функциональная часть периферийного модуля.

Предлагаемая вычислительная система содержит процессорный модуль 1, системную интерфейсную магистраль адреса, системную интерфейсную магистраль 3 данных, системную интерфейсную магистраль 4 управления и n периферийных модулей 51...5n.

Входы адреса (А) каждого из n периферийных модулей 51...5n соединены посредством системной интерфейсной магистрали 2 адреса с выходами адреса (А) процессорного модуля 1, входы-выходы данных (Д) каждого из n периферийных модулей 51. . .5n соединены посредством системной интерфейсной магистрали 3 данных с входами-выходами данных (Д) процессорного модуля 1, входы-выходы управления (У) каждого из n периферийных модулей 51...5n соединены посредством системной интерфейсной магистрали 4 управления с входами-выходами управления (У) процессорного модуля 1.

Каждый из n периферийных модулей 51...5n содержит блок 6 управления, регистр 7, блок 8 сравнения и дешифратор 9 сигнала записи и функциональную часть 10.

Вход инициализации первого периферийного модуля 51 соединен с выходом инициализации процессорного модуля 1, вход инициализации каждого из последующих периферийных модулей соединен с выходом инициализации предыдущего периферийного модуля, выход инициализации n-го периферийного модуля 5n соединен со входом инициализации процессорного модуля 1.

В каждом из n периферийных модулей 51...5n первый вход блока 6 управления является входом инициализации данного периферийного модуля, первый выход блока 6 управления является выходом инициализации данного периферийного модуля, второй выход блока 6 управления соединен с входом разрешения работы (E) регистра 7, выходы регистра 7 соединены со вторыми входами блока 8 сравнения, второй вход блока 6 управления и вход сигнала (3) записи регистра 7 соединены с выходом дешифратора сигнала записи, входы данных регистра 7 и входы-выходы данных (Д) функциональной части 10 данного периферийного модуля соединены с системной интерфейсной магистралью 3 данных, первые входы блока 8 сравнения и входы адреса (А) функциональной части 10 данного периферийного модуля соединены с системной интерфейсной магистралью 2 адреса, входы-выходы управления (У) функциональной части 10 данного периферийного модуля и входы дешифратора 9 соединены с системной интерфейсной магистралью 4 управления, вход разрешения работы (E) функциональной части 10 данного периферийного модуля соединен с выходом блока 8 сравнения.

Функциональная часть 10 периферийных модулей 51...5n в зависимости от назначения модулей может представлять собой, например, оперативное запоминающее устройство, постоянное запоминающее устройство и другое подобное устройство.

Блок 6 управления может быть построен по известным правилам исходя из описанного алгоритма его работы. Построение остальных блоков, входящих в предлагаемую вычислительную систему, хорошо известно.

Вычислительная система работает следующим образом.

После включения питания или поступления команды "сброс" процессорный модуль 1 выдает на свой выход инициализации сигнал логической единицы, а все периферийные модули 51...5n выдают на свои выходы инициализации сигналы логического нуля (блок 6 управления каждого из n периферийных модулей 51...5n выдает на свой первый выход сигнал логического нуля). При этом непосредственно после сброса и при наличии сигнала логической единицы на входе инициализации периферийного модуля, то есть на первом входе блока 6 управления, блок 6 управления выдает на свой второй выход сигнал логической единицы, который поступает на вход разрешения работы (E) регистра 7. Процессорный модуль 1 производит операцию записи на системной интерфейсной магистрали 4. На выходе дешифратора 9 сигнала записи появляется сигнал логической единицы, который поступает на вход записи (З) регистра 7 и на второй вход блока 6 управления. При этом вне зависимости от адреса, выставленного на системной интерфейсной магистрали 2 адреса, производится запись данных, выставленных процессорным модулем 1 на системной интерфейсной магистрали 3 данных в регистр 7. После записи данных в регистр 7 блок 6 управления выдает на свой второй выход сигнал логического нуля, который поступает на вход разрешения работы регистра 7, что запрещает дальнейшую запись данных в регистр 7 при следующих операциях записи по системной интерфейсной магистрали. Также блок 6 управления выдает на свой первый выход сигнал логической единицы, который поступает на вход инициализации следующего периферийного модуля и при следующей операции записи аналогичным образом производится запись данных в регистр 7 следующего периферийного модуля. Данная процедура повторяется для каждого из n периферийных модулей 51...5n. После завершения записи данных в регистр 7 n-го периферийного модуля 5n на его выходе инициализации появляется сигнал логической единицы, который поступает на вход инициализации процессорного модуля 1. В случае, если после n-й операции записи по системной интерфейсной магистрали на вход инициализации процессорного модуля 1 сигнал логической единицы не поступает, что означает наличие неисправности в вычислительной системе, то процессорный модуль 1 осуществляет действия, предусмотренные в случае неисправности вычислительной системы (например, приостановку работы вычислительной системы, включение соответствующей индикации, запуск программы диагностики).

Данные, записанные в регистр 7 каждого из n периферийных модулей 51... 5n, являются базовым адресом данного периферийного модуля на системной интерфейсной магистрали (старшими разрядами адреса). При осуществлении последующих операций обмена по системной интерфейсной магистрали адрес, выставленный процессорным модулем 1 или другим периферийным модулем, поступает на первые входы блока 8 сравнения. На вторые входы блока 8 сравнения подаются данные, записанные в регистр 7. В случае совпадения адреса (старших разрядов адреса), выставленного на системной интерфейсной магистрали 2 адреса с данными, записанными в регистр 7, блок 8 сравнения выдает на свой выход сигнал логической единицы, который поступает на вход разрешения работы (E) функциональной части 10 периферийного модуля и осуществляется обмен данными по системной интерфейсной магистрали с функциональной частью 10 данного периферийного модуля (обмен данными между данным периферийным модулем и процессорным модулем 1 или обмен данными между данным периферийным модулем и другим периферийным модулем). В случае несовпадения адреса (старших разрядов адреса), выставленного на системной интерфейсной магистрали 2 адреса с данными, записанными в регистр 7, блок 8 сравнения выдает на свой выход сигнал логического нуля, который поступает на вход разрешения работы (E) функциональной части 10 периферийного модуля и данный периферийный модуль не участвует в обмене данными по системной интерфейсной магистрали.

После включения питания или осуществления сброса в регистре 7 каждого из n периферийных модулей 51...5n и до осуществления описанной процедуры записи данных в регистр 7 процессорным модулем 1 по системной магистрали в регистре 7 находится фиксированный базовый адрес периферийного модуля (записанный при изготовлении или предварительной настройке данного периферийного модуля).

Таким образом, предлагаемое изобретение обеспечивает возможность назначения своего адреса любому периферийному модулю, включаемому в вычислительную систему, и позволяет использовать периферийные модули в вычислительных системах, не содержащих линий инициализации.

Представленные чертежи и описание вычислительного модуля позволяют, используя существующую элементную базу, изготовить его промышленным способом и использовать в вычислительных устройствах различного назначения, что характеризует предлагаемое изобретение как промышленно применимое.

Источники информации.

1. Каган Б.М. Сташин В.В. Основы проектирования микропроцессорных устройств автоматики. - М.: Энергоатомиздат, 1987, - с. 11.

2. РФ, свидетельство N 13511 на полезную модель, МПК G 06 F 7/00, публикация 20.04.2000 г.

3. РФ, свидетельство N 13105 на полезную модель, МПК G 06 F 7/00, публикация 20.03.2000 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ИНДИКАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2001 |

|

RU2206872C2 |

| МНОГОФУНКЦИОНАЛЬНЫЙ БОРТОВОЙ ИНДИКАТОР | 2000 |

|

RU2162204C1 |

| ПАРАЛЛЕЛЬНЫЙ ПРОЦЕССОР С ПЕРЕПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1994 |

|

RU2110088C1 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 2008 |

|

RU2387000C1 |

| АДАПТИВНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2477882C2 |

| Способ передачи данных по шине, система связи для осуществления данного способа и устройство автоматической защиты для предотвращения аварийной ситуации на объекте управления | 2018 |

|

RU2705421C1 |

| НАВИГАЦИОННЫЙ КОМПЛЕКС ЛЕТАТЕЛЬНОГО АППАРАТА | 2000 |

|

RU2170409C1 |

| Устройство ввода-вывода | 2020 |

|

RU2753980C1 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах различного назначения. Техническим результатом является возможность назначения своего адреса любому периферийному модулю. Система содержит процессорный модуль, системные интерфейсные магистрали адреса, данных и управления, n периферийных модулей, каждый из которых содержит блок управления, регистр, блок сравнения и дешифратор сигнала записи. 1 з.п.ф-лы, 1 ил.

| Способ непрерывной обработки тканей при сообщении им водоупорности | 1927 |

|

SU13105A1 |

| Автоматические весы для наблюдения за сушкой дерева | 1928 |

|

SU13511A1 |

| КАГАН Б.М., СТАШИН В.В | |||

| Основы проектирования микропроцессорных устройств автоматики | |||

| - М.: Энергоатомиздат, 1987, с | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| US 4591977 A, 27.05.1986 | |||

| Устройство для сигнализации контроля объектов | 1981 |

|

SU966717A2 |

Авторы

Даты

2002-02-10—Публикация

2000-07-28—Подача