Изобретение относится к вычислительной технике и может быть использовано для построения высоконадежных отказоустойчивых бортовых комплексов в космической, авиационной, ядерной и в других отраслях, требующих высокой достоверности и надежности функционирования.

Известна микроЭВМ, содержащая микропроцессор, постоянное запоминающее устройство, оперативное запоминающее устройство, схему начального сброса, генератор синхросигналов, программируемый интервальный таймер, контроллер прерываний (Хвощ С.Т. и др. "Микропроцессоры и микроЭВМ в системах автоматического управления". Справочник, Ленинград, "Машиностроение", 1987, стр. 8).

Недостатком данной микроЭВМ является ее низкая надежность при работе в экстремальных условиях.

Известно отказоустойчивое устройство для обработки информации (SU 1758649 A1, опубл. 30.08.92, G 06 F 15/16), содержащее три резервируемых вычислительных канала, группу мажоритарных элементов, шесть схем сравнения, девять триггеров, три элемента НЕ, шестнадцать элементов И, три элемента задержки, элемент ИЛИ, девять элементов ИЛИ-НЕ, счетчик сбоев, три элемента И-НЕ.

Недостатком устройства являются большие затраты ресурсов для достижения высоких показателей надежности, низкая ресурсоемкость и достаточно ограниченное общее время функционирования.

Наиболее близкой к заявленной (прототип) является микропроцессорная система с контролем (SU 1242976 A1, опубл. 07.07.86, G 06 F 15/00), содержащая микропроцессор, блок оперативной памяти, блок памяти команд, регистр состояния, три буферных регистра, генератор тактовых импульсов, регистр хранения контрольного операнда, дешифратор кода адреса, блок сравнения, счетчик, дешифратор кода номера внутреннего регистра, триггер отказа, триггер контроля, блок индикации, два элемента ИЛИ и два элемента И.

Способ ее работы, заключающийся в том, что осуществляют первый цикл контроля работы системы, предназначенный для выявления отказавших элементов микропроцессора, в случае обнаружения отказа одного из элементов микропроцессора блокируют работу микропроцессора, в случае правильного функционирования элементов микропроцессора осуществляют второй цикл контроля работы системы, в случае обнаружения отказавших элементов системы блокируют работу микропроцессора, в случае правильного функционирования переходят к выполнению с помощью микропроцессора цикла вычислений, представляющего собой обмен информацией с периферийными устройствами и обработку информации, причем первый и второй циклы контроля работы системы осуществляют периодически перед каждым новым циклом вычислений.

Недостатком этой системы является низкая надежность функционирования в условиях разрушающего воздействия ионизирующего излучения и потоков ТЗЧ, имеющих место при эксплуатации в остро неблагоприятных условиях (например, космоса и других).

Программируемый интервальный таймер (TMR) представляет собой устройство, ведущее исчисление времени и прерывающее работу микропроцессора через заданные интервалы. Известен программируемый интервальный таймер, содержащий 16-разрядный буфер данных, 10-разрядный регистр состояний, два счетчика с программируемым коэффициентом пересчета, устройство управления и блок деления частоты (Хвощ С. Т. и др. "Микропроцессоры и микроЭВМ в системах автоматического управления". Справочник, Ленинград, "Машиностроение", 1987, стр. 230).

В микропроцессорах и в микроЭВМ источниками отказов являются все устройства, подключенные к общей шине, при этом наиболее интенсивными источниками отказов являются блоки постоянной и оперативной памяти, на которые приходится от 50 до 95% всех используемых в системе микросхем.

В основу изобретения поставлена задача создания способа и устройства, позволяющих повысить надежность работы отказоустойчивой бортовой микропроцессорной системы в условиях разрушающего воздействия ионизирующего излучения и потоков тяжелых заряженных частиц (ТЗЧ) за счет повышения надежности работы блока памяти команд, выполненного в виде ЭППЗУ. Другой задачей является создание устройства, позволяющего осуществлять автоматический аппаратный переход на резервную копию программы при обнаружении неправильного функционирования модуля памяти, в котором размещена основная программа.

Эти задачи решаются тем, что отказоустойчивая бортовая микропроцессорная система содержит микропроцессор, блок оперативной памяти, блок памяти команд, дешифратор кода адреса, счетчик, причем информационные и адресные входы/выходы микропроцессора, блока оперативной памяти и блока памяти команд соединены через шину адрес/данных и являются информационными и адресными входами/выходами системы, устройство "Служба сторожевого таймера", регистр, регистр защелки адреса, дешифратор старшего разряда адреса, а блок памяти команд выполнен в виде N модулей памяти команд, блок оперативной памяти выполнен в виде М модулей оперативной памяти, причем выход "CLK", выход "NMI", выход "RESIN" устройства "Служба сторожевого таймера" соединены соответственно с первым, вторым и третьим управляющими входами микропроцессора, первый и второй управляющие выходы которого соединены соответственно со счетным входом и входом "разрешение записи" счетчика, первый и второй выходы которого соединены с первым и вторым входами дешифратора кода адреса, с первого по N-й выходы которого соединены соответственно с первыми управляющими входами с первого по N-й модулей памяти команд, входы записи и чтения которых соединены соответственно с третьим и четвертым выходами микропроцессора, выход "адрес обращения" которого соединен с информационным входом регистра защелки адреса, выход которого соединен с адресными входами всех модулей памяти команд и всех модулей оперативной памяти, третий управляющий выход микропроцессора соединен со входами записи регистра и счетчика, первый выход регистра соединен с первым управляющим входом устройства "Служба сторожевого таймера", второй выход регистра соединен с первым входом дешифратора старшего разряда адреса, второй вход которого соединен с пятым управляющим выходом микропроцессора, шестой управляющий выход которого соединен с первыми управляющими входами всех модулей оперативной памяти, вторые управляющие входы которых соединены с выходом дешифратора старшего разряда адреса, седьмой и восьмой управляющие выходы микропроцессора соединены соответственно со вторым и третьим управляющими входами устройства "Служба сторожевого таймера", информационные входы регистра и счетчика соединены с информационными входами/выходами системы.

При этом устройство "Служба сторожевого таймера" содержит регистр состояния, счетчик синхронизации, генератор тактовых импульсов, элемент ИЛИ, схему начальной установки, элемент И-ИЛИ, схему сравнения, триггер, причем информационный вход регистра состояния является информационным входом устройства и предназначен для подключения к шине адрес/данные, n-разрядный выход регистра подключен к первому входу схемы сравнения, второй вход которой соединен с n-разрядным выходом счетчика синхронизации, счетный вход которого соединен с выходом генератора тактовых импульсов, который также является выходом "CLK" устройства, выход схемы начальной установки является выходом "HDWRES" устройства и соединен с первыми входами элемента ИЛИ и элемента И-ИЛИ и со входом обнуления триггера, выход триггера является выходом "NMI" устройства, выход элемента И-ИЛИ соединен со вторым входом элемента ИЛИ и является выходом "RESIN" устройства, i-й разряд (где i=1,2,...,n) счетчика синхронизации соединен с третьим входом элемента И-ИЛИ, четвертый вход которого соединен с третьим входом элемента ИЛИ и является первым управляющим входом устройства, второй вход которого является четвертым входом элемента ИЛИ, третий управляющий вход устройства соединен с управляющим входом регистра состояний и с пятым входом элемента ИЛИ, выход которого соединен с управляющим входом счетчика синхронизации, выход схемы сравнения соединен с установочным входом триггера.

Способ работы отказоустойчивой бортовой микропроцессорной системы заключается в том, что осуществляют первый цикл контроля работы системы, предназначенный для выявления отказавших элементов микропроцессора, в случае обнаружения отказа одного из элементов микропроцессора блокируют работу микропроцессора, в случае правильного функционирования элементов микропроцессора осуществляют второй цикл контроля работы системы, в случае обнаружения отказавших элементов системы блокируют работу микропроцессора, в случае правильного функционирования переходят к выполнению с помощью микропроцессора цикла вычислений, представляющего собой обмен информацией с периферийными устройствами и обработку информации, причем первый и второй циклы контроля работы системы осуществляют периодически перед каждым новым циклом вычислений, при втором цикле контроля работы системы задают временный период срабатывания устройства "Служба сторожевого таймера", разбивают адресное пространство блока памяти команд на N модулей памяти команд, разбивают адресное пространство блока оперативной памяти на М модулей, записывают в каждый модуль памяти команд стартовый код системы и рабочие программы, осуществляют инициализацию системы, после чего осуществляют цикл по выбору рабочего модуля памяти команд, при этом осуществляют контроль i-го модуля памяти команд (где i=1,2,...,N), если в результате контроля обнаруживают неправильное функционирование данного модуля памяти команд, то формируют сигнал "RESIN" с помощью устройства "Служба сторожевого таймера", данный сигнал подают на третий управляющий вход микропроцессора, формируют сигнал "RESOUT" и подают его на первый управляющий вход счетчика, изменяют состояние счетчика, с помощью дешифратора определяют адрес следующего рабочего модуля памяти команд, а затем повторяют цикл по выбору рабочего модуля памяти команд, причем данный цикл повторяют до обнаружения первого работоспособного модуля памяти команд, в случае отсутствия работоспособного модуля памяти команд блокируют работу микропроцессора, если же в результате контроля определяют работоспособность i-го модуля памяти команд, то адрес обращения микропроцессора записывают в регистр защелки адреса, после чего с помощью микропроцессора последовательно считывают из модуля памяти команд информацию, осуществляют контроль работы каждого модуля оперативной памяти, если в результате контроля модуля оперативной памяти обнаруживают изменения записанных в данный модуль оперативной памяти данных, то формируют с помощью дешифратора старшего адреса сигнал перехода на следующий модуль оперативной памяти, причем контроль осуществляется до обнаружения первого работоспособного модуля оперативной памяти и осуществляют контроль его работы, в случае отсутствия работоспособного модуля оперативной памяти блокируют работу микропроцессора, затем осуществляют один цикл вычислений, промежуточные значения вычислений и данные записывают в работоспособный модуль оперативной памяти.

В дальнейшем изобретение поясняется описанием примера его выполнения и прилагаемыми чертежами, на которых:

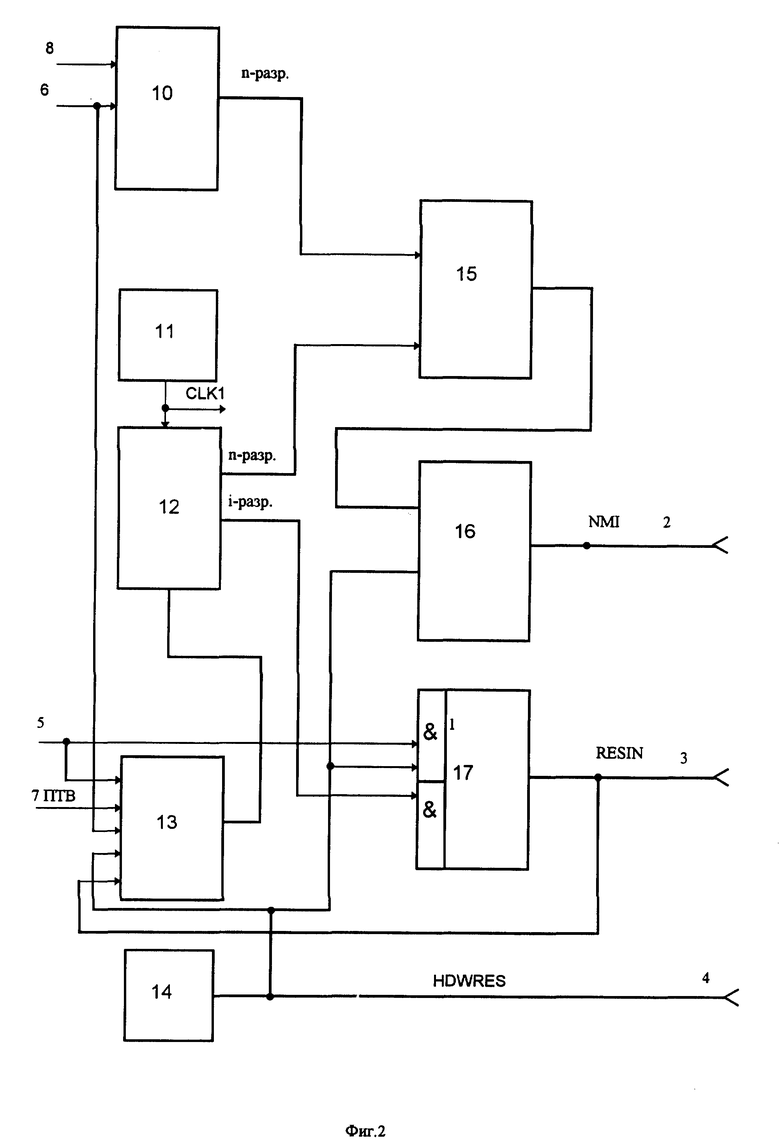

фиг.1 изображает функциональную схему отказоустойчивой бортовой вычислительной системы;

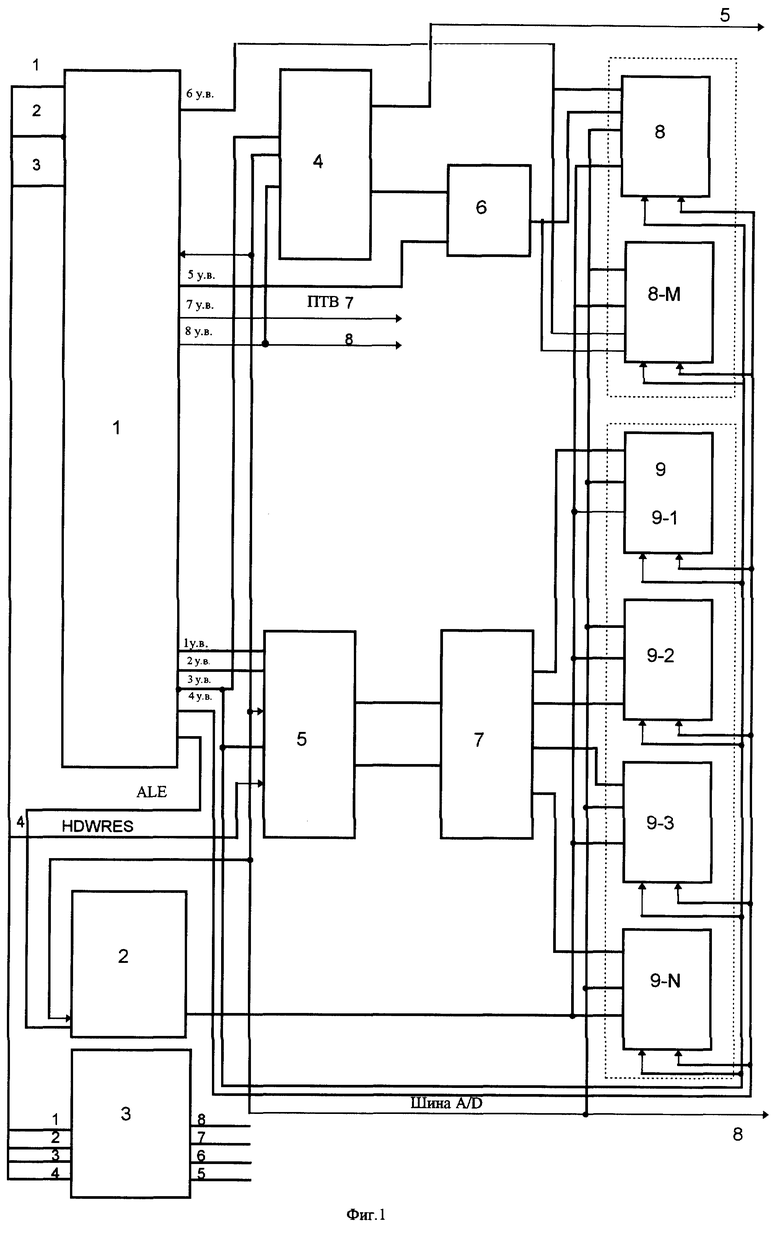

фиг.2 - функциональную схему устройства "Служба сторожевого таймера".

Отказоустойчивая бортовая вычислительная система (фиг.1) содержит: 1 - микропроцессор, 2 - регистр защелки адреса, 3 - устройство "Служба сторожевого таймера", 4 - регистр, 5 - счетчик, 6 - дешифратор старшего разряда адреса, 7 -дешифратор кода адреса, 8 - блок оперативной памяти, 9 - блок памяти команд, содержащий с первого по N модулей памяти команд. Модули 1-N памяти команд представляют собой равноправные, прошитые одинаковым кодом ЭППЗУ и служат для хранения стартового кода системы и рабочих программ. Блок оперативной памяти 8 используется для хранения промежуточных значений вычислений и данных. Этот блок выполнен на ОЗУ в виде М независимых модулей оперативной памяти. С помощью дешифратора 6 кода адреса по коду счетчика вырабатывается сигнал модуля памяти команд. Счетчик 5 используется для формирования адреса команд с учетом номера модуля памяти команд при отсутствии подтверждения о нормальном (нормативном) поведении программы. Системный регистр 10 служит для формирования сигнала программного сброса микропроцессора, а также для хранения признака выборки модуля блока оперативной памяти. С помощью дешифратора 6 формируется старший разряд адреса обращения блока оперативной памяти (пропускает его без изменения либо инвертирует его на противоположное значение).

Устройство "Служба сторожевого таймера" (фиг.2) содержит: 10 - регистр состояния, 11 - генератор тактовых импульсов, 12 - счетчик синхронизации, 13 - элемент ИЛИ, 14 - схему начальной установки, 15 - схему сравнения, 16 - триггер, 17 - элемент И-ИЛИ. Генератор тактовых импульсов 11 используется в качестве источника тактовых импульсов. Счетчик 12 синхронизации служит для подсчета времени, прошедшего от начала следующих событий: включения питания, подтверждения нормального (нормативного) поведения программы, программного обнуления, выдачи сигнала "RESIN", загрузки кода регистра состояний устройства "Сторожевой таймер". Регистр 10 состояния используется для хранения кода периода срабатывания устройства "Сторожевой таймер". Элемент сравнения 15 служит для сравнения кода периода, установленного в регистре состояния, и старших разрядов счетчика синхронизации. Триггер 16 используется для формирования сигнала "NMI". Элемент ИЛИ 13 и элемент И-ИЛИ 17 используются соответственно для сборки сигналов "RESIN" микропроцессора и сброса счетчика устройства. Схема 14 начальной установки представляет собой RC цепочку, формирующую сигнал обнуления при включении питания.

Применяемый в системе метод контроля длительности выполнения программ относится к программно-логическому типу. Контроль длительности выполнения программ основан на том, что для каждой программы заранее известна максимальная длительность выполнения (при нормальном или нормативном ее поведении) и всякое ее превышение означает, что программа зациклилась, остановилась или выполняется неправильно. Превышение длительности выполнения может быть связано с ошибками в программе, с искажением адресной информации в результате сбоев. Например, возможны случаи, когда выполняется одна программа, а потом в результате сбоя выполнение переходит по ошибке к другой программе. Контроль правильности выполнения программ осуществляется преимущественно программными средствами, которые позволяют обнаруживать ошибки в работе системы с задержкой, соизмеримой с временем выполнения программы (или подпрограммы).

Система работает следующим образом.

Отказоустойчивая бортовая микропроцессорная система содержит микропроцессор 1, блок 8 оперативной памяти, блок 9 памяти команд, дешифратор 7 кода адреса, счетчик 5, причем информационные и адресные входы/выходы микропроцессора, блока оперативной памяти и блока памяти команд соединены между собой через шину адрес/данных с информационными входами/выходами блока оперативной памяти и блока памяти команд и являются информационными и адресными входами/выходами системы, устройство 3 "Служба сторожевого таймера", регистр 4, регистр 2 защелки адреса, дешифратор 6 старшего разряда адреса, а блок памяти команд выполнен в виде N модулей памяти команд, блок оперативной памяти выполнен в виде М модулей оперативной памяти, причем выход "CLK", выход "NMI", выход "RESIN" устройства "Служба сторожевого таймера" соединены соответственно с первым, вторым и третьим управляющими входами микропроцессора, первый и второй управляющие выходы которого соединены соответственно со счетным входом и входом "разрешение записи" счетчика, первый и второй выходы которого соединены с первым и вторым входами дешифратора кода адреса, с первого по N-й выходы которого соединены соответственно с первыми управляющими входами с первого по N-й модулей памяти команд, входы записи и чтения которых соединены соответственно с третьим и четвертым выходами микропроцессора, выход "адрес обращения" которого соединен с информационным входом регистра защелки адреса, выход которого соединен с адресными входами всех модулей памяти команд и всех модулей оперативной памяти, третий управляющий выход микропроцессора соединен со входами записи регистра и счетчика, первый выход регистра соединен с первым управляющим входом устройства "Служба сторожевого таймера", информационный вход которого соединен с информационным входом/выходом системы, второй выход регистра соединен с первым входом дешифратора старшего разряда адреса, второй вход которого соединен с пятым управляющим выходом микропроцессора, шестой управляющий выход которого соединен с первыми управляющими входами всех модулей оперативной памяти, вторые управляющие входы которых соединены с выходом дешифратора старшего разряда адреса, седьмой и восьмой управляющие выходы микропроцессора соединены соответственно со вторым и третьим управляющими входами устройства "Служба сторожевого таймера", причем устройство "Служба сторожевого таймера", содержащее регистр 10 состояния и счетчик 12 синхронизации, генератор 11 тактовых импульсов, элемент 13 ИЛИ, схему 14 начальной установки, элемент 17 И-ИЛИ, схему 15 сравнения, триггер 16, причем информационный вход регистра состояния является информационным входом устройства и предназначен для подключения к шине адрес/данные, n-разрядный выход регистра подключен к первому входу схемы сравнения, второй вход которой соединен с n-разрядным выходом счетчика синхронизации, счетный вход которого соединен с выходом генератора тактовых импульсов, который также является выходом "CLK" устройства, выход схемы начальной установки является выходом "HDWRES" устройства и соединен с первыми входами элемента ИЛИ и элемента И-ИЛИ и со входом обнуления триггера, выход триггера является выходом "NMI" устройства, выход элемента И-ИЛИ соединен со вторым входом элемента ИЛИ и является выходом "RESIN" устройства, i-й разряд (где i=1,2,...,n) счетчика синхронизации соединен с третьим входом элемента И-ИЛИ, четвертый вход которого соединен с третьим входом элемента ИЛИ и является первым управляющим входом устройства, второй вход которого является четвертым входом элемента ИЛИ, третий управляющий вход устройства соединен с управляющим входом регистра состояний и с пятым входом элемента ИЛИ, выход которого соединен с управляющим входом счетчика синхронизации, выход схемы сравнения соединен с установочным входом триггера.

В устройстве "Служба сторожевого таймера" при включении питания на выходе схемы начальной установки 14 формируется сигнал на выходе "HDWRES" устройства, с помощью которого производится обнуление всех элементов устройства "Служба сторожевого таймера" и всех блоков системы. Сигнал с выхода схемы 14 устройства "Служба сторожевого таймера" формирует на выходе элемента 17, являющегося выходом "RESIN" устройства, сигнал "RESIN", который поступает на третий управляющий вход микропроцессора. Далее осуществляют первый цикл контроля работы системы, при котором микропроцессор осуществляет самоконтроль, предназначенный для выявления отказавших элементов микропроцессора. Самоконтроль микропроцессора осуществляется путем запуска тестовой контрольной программы, записанной в блоке памяти команд. Самоконтроль основан на тестах, обеспечивающих полный контроль всех элементов микропроцессора за короткое время (и является встроенным контролем). В случае обнаружения отказа одного из элементов микропроцессора работа микропроцессора блокируется, в случае правильного функционирования элементов микропроцессора осуществляют второй цикл контроля работы системы.

Необходимо заметить, что тестовый самоконтроль микропроцессора может проводиться в специально отведенные промежутки времени (регламентно) на основе решения тестовых задач.

На втором цикле контроля работы системы задается временный период срабатывания устройства "Служба сторожевого таймера" путем записи в регистр 10 состояния необходимого значения временного периода, при этом счетчик 12 синхронизации обнуляется. Сигнал сброса микропроцессора в этом случае будет сформирован через время, величина которого определяется суммой значения, записанного в регистр 10, и заранее заданным значением времени t, необходимым для обработки сигнала прерывания "NMI".

Адресное пространство блока памяти команд делят на N модулей памяти команд, в каждый из которых записываются копии стартового кода системы и рабочих программ. Стартовый код системы содержит собственную контрольную сумму и рабочие программы (программу углубленного тестирования ресурсов системы и функциональную программу, осуществляющую собственно управление).

На втором цикле контроля осуществляется цикл по выбору рабочего модуля памяти команд, при этом осуществляют контроль i-го модуля памяти команд (где i= 1,2,...,N). Этот цикл начинается с того, что на первом управляющем выходе микропроцессора формируется сигнал "RESOUT", который поступает на счетный вход счетчика 5, далее информация с выхода счетчика 5 поступает на входы дешифратора 7, с помощью которого производится выбор модуля памяти команд. Счетчик 5 и счетчик 12 устройства "Служба сторожевого таймера" имеют нулевые состояния. Происходит обращение микропроцессора к первому модулю памяти команд. Адрес обращения по сигналу ALE микропроцессора записывается в регистр 2 защелки адреса.

Контроль модуля памяти команд осуществляется следующим образом.

В случае, если подтверждение о нормальном (нормативном) поведении выполняемой программы поступило заблаговременно, то есть на седьмом управляющем выходе микропроцессора сформировался сигнал ПТВ за время t до предполагаемого времени срабатывания устройства "Служба сторожевого таймера", то сигналы на выходах "NMI" и "RESIN" устройства не формируются. Сигнал ПТВ с седьмого управляющего выхода микропроцессора поступает на четвертый вход элемента 13, выход которого поступает на управляющий вход счетчика синхроимпульсов 12. На счетный вход счетчика 12 синхронизации поступают сигналы с выхода генератора 11 тактовых импульсов (данный выход генератора 11 является выходом "CLK" устройства "Службы сторожевого таймера") устройства. Сторожевой таймер приводится в исходное состояние, то есть обнуляется. При этом обнуление всего устройства не производится.

В случае, если подтверждение о нормальном (нормативном) поведении выполняемой программы поступило за время, меньшее, чем t до предполагаемого времени срабатывания устройства "Службы сторожевого таймера", то при совпадении значения старших разрядов (n-разрядный выход) счетчика синхронизации 12 и содержимого регистра 10 состояния (n-разрядного выхода) с выхода схемы сравнения 15 выдается единичный сигнал, который поступает на установочный вход триггера 16, с выхода которого, являющегося также выходом "NMI" устройства "Служба сторожевого таймера", единичный сигнал "NMI" поступает на второй управляющий вход микропроцессора. Сигнал с выхода триггера 16 используется для подготовки обнуления системы и перехода на другой модуль памяти команд. При появлении сигнала о нормальном (нормативном) поведении программы счетчик 12 устройства "Служба сторожевого таймера" сбрасывается и работа выполняемой программы продолжается без перехода на другой модуль памяти команд.

В случае, если подтверждение не поступило за время, равное сумме периода устройства "Службы сторожевой таймер" и времени t, то при совпадении значения старших разрядов счетчика синхронизации 12 и содержимого регистра состояния 10 с выхода схемы сравнения 15 выдается единичный сигнал "NMI", поступающий на второй управляющий вход микропроцессора. Затем через время t после прерывания на третий управляющий вход микропроцессора с выхода элемента 17, являющегося также выходом "RESIN" устройства 3, выдается сигнал "RESIN", с помощью которого происходит обнуление микропроцессора, после чего с первого управляющего выхода микропроцессора выдается сигнал "RESOUT", с помощью которого происходит обнуление всей системы. Сигнал "RESOUT" микропроцессора поступает на счетный вход счетчика 5, с выхода которого информация поступает на входы дешифратора 7, с выходов которого единичный сигнал поступает на управляющий вход модуля блока памяти команд. Таким образом произойдет выбор исправного модуля памяти команд, подготовка цепей для инициализации микропроцессора и работы программ, находящихся в выбранном модуле памяти команд.

При выполнении программы, размещенной в модулях памяти команд, кроме аппаратного переключения между этими модулями при отсутствии подтверждения о нормальном (нормативном) поведении программы, имеется возможность программного перехода с одного модуля на любой другой в процессе работы. Для этого по информационному входу счетчика 5 записывается код модуля памяти команд, в котором размещена рабочая копия программы, и формируется сигнал обнуления системы. Кроме того, по информационному входу регистра 4 записывается признак переключения между модулями оперативной памяти 8, с помощью которого производится выбор работоспособного модуля оперативной памяти.

Если в результате контроля обнаруживают неправильное функционирование данного модуля памяти команд, то с выхода устройства "Службы сторожевого таймера" на третий управляющий вход микропроцессора 1 подается сигнал "RESIN", в результате чего с первого управляющего выхода микропроцессора выдается сигнал "RESOUT", который подается на счетный вход счетчика 5, состояние счетчика изменяется, информация с выхода счетчика 5 поступает на входы дешифратора 7, с одного из выходов которого единичный сигнал поступает на первый управляющий вход модуля блока команд 1, и таким образом определяется следующий работоспособный модуль памяти команд.

Цикл по выбору рабочего модуля повторяется до обнаружения первого работоспособного модуля памяти команд. Если в результате контроля определяют работоспособность i-го модуля памяти команд, то он используется в дальнейшем для осуществления одного цикла вычислений микропроцессора.

Цикл вычислений микропроцессора представляет собой обмен информацией с периферийными устройствами и обработку информации. При этом промежуточные значения вычислений и данные записывают в один из модулей оперативной памяти

Каждый цикл вычислений начинается с выполнения микропроцессором стартовой программы, с помощью которой подсчитывается контрольная сумма стартовой программы и сравнивается с эталонным значением, хранящимся в модулях памяти команд. Если подсчитанная сумма не совпадает с эталонной, то микропроцессор перестает сбрасывать счетчик, входящий в состав устройства "Службы сторожевого таймера", устройство "Службы сторожевого таймера" формирует сигнал "RESET" микропроцессора. Далее вычислительный процесс начинается со следующей копии стартового кода.

Если контрольная сумма совпала с эталоном, то управление передается в программу углубленного тестирования ресурсов, которая также подсчитывает контрольные суммы текущей активной области. Если программа углубленного тестирования ресурсов не обнаружила отказов, то управление передается функциональной программе. Микропроцессор выполняет функциональную программу и ожидает следующего синхронизирующего внешнего события. С момента окончания текущего цикла вычислений до следующего синхронизирующего внешнего события микропроцессор осуществляет фоновое тестирование путем подсчета контрольных сумм всех доступных областей модулей памяти команд с последующим сравнением их с эталоном.

Если в результате контроля модуля оперативной памяти обнаруживают изменения записанных в данный модуль оперативной памяти данных, то с помощью дешифратора старшего разряда адреса формируется сигнал перехода на другой модуль оперативной памяти.

Первый и второй циклы контроля работы системы осуществляют периодически перед каждым новым циклом вычислений.

Элементы системы могут быть реализованы на следующих микросхемах:

1. Микропроцессор (1) реализован на элементе фирмы "Intel Corp." MG80C186EB-13.

2. Регистр (2) защелки адреса, элементы 10, 12, 13, 15-17 устройства (3) "Служба сторожевого таймера", регистр (4), счетчик (5), дешифратор (6) старшего разряда адреса, дешифратор (7) могут быть реализованы либо на типовых отечественных логических микросхемах, например серии 1533, либо на типовых зарубежных логических микросхемах фирмы Actel A1020B.

3. Элемент (11) данного устройства реализован на генераторе СО-447-24 МГц.

4. Блок оперативной памяти (8) реализован на микросхемах фирмы "Micron" - MT5C1008DCJ.

5. Блок памяти команд (9) реализован на микросхемах фирмы "Hitachi" - 28C010.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

| СИСТЕМНЫЙ КОНТРОЛЛЕР | 1996 |

|

RU2110834C1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ БОРТОВОЙ ИНДИКАТОР | 2000 |

|

RU2162204C1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения высоконадежных отказоустойчивых бортовых комплексов в космической, авиационной, ядерной и других отраслях, требующих высокой достоверности и надежности функционирования. Технический результат изобретения заключается в повышении надежности функционирования в условиях разрушающего воздействия ионизирующего излучения и потоков ТЗЧ, имеющих место при эксплуатации в остронеблагоприятных условиях (например, космоса и других), и достигается тем, что отказоустойчивая бортовая микропроцессорная система содержит микропроцессор, блок оперативной памяти, блок памяти команд, дешифратор кода адреса, счетчик, устройство "Служба сторожевого таймера", регистр, регистр защелки адреса, дешифратор старшего разряда адреса, а блок памяти команд выполнен в виде N модулей памяти команд, блок оперативной памяти выполнен в виде M модулей оперативной памяти. 3 с.п.ф-лы, 2 ил.

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| Хвощ С.Т | |||

| и др | |||

| Микропроцессоры и микроЭВМ в системах автоматического управления | |||

| Справочник | |||

| - Л.: Машиностроение, 1987, с.8 | |||

| Устройство для контроля логическихблОКОВ | 1978 |

|

SU813430A1 |

Авторы

Даты

1999-06-10—Публикация

1998-08-18—Подача