Изобретение относится к области вычислительной техники и предназначено для создания высокоскоростных систем обработки больших потоков данных в реальном режиме времени.

Известен процессор на основе однородной вычислительной перепрограммируемой структуры, состоящий из блока приема информации, блока коммутации, блока диспетчеризации, блока программного управления и N устройств обработки данных.

Недостатками его являются ограничение быстродействия, вызванное резким усложнением коммутатора при росте числа устройств обработки данных, ограничение скорости обмена с внешними устройствами, вызванное наличием одного блока приема информации, невозможность параллельного выполнения нескольких программ.

Наиболее близким к описываемому процессору является компьютер, в котором арифметико-логический блок выполнен на однородной перепрограммируемой структуре и введены блок управления, блок настройки и блок формирования макрокоманд, выход которого соединен со вторым управляющим входом блока управления памятью, а вход - со вторым выходом регистра команд, второй вход которого соединен с первым выходом постоянного запоминающего устройства команд, а третий выход подключен к первому управляющему входу устройства ввода-вывода, второй информационный выход которого подключен к первому входу блока управления, а второй информационный вход соединен с первым выходом блока контроля, первый вход которого соединен с контрольным выходом блока управления памятью, а второй и третий выходы подключены соответственно к контрольному выходу блока настройки и первому выходу блока управления, второй вход которого соединен со вторым выходом блока контроля, третий вход блока управления соединен со счетчиком команд, а четвертый вход подключен к первому выходу блока настройки, второй выход блока управления соединен с постоянным запоминающим устройством программ, второй выход которого подключен к третьему управляющему входу блока управления памятью, третий выход блока управления соединен с первым входом постоянного запоминающего устройства команд, второй вход которого подключен ко второму выходу блока настройки, а второй выход соединен с первым управляющим входом арифметико-логического блока, управляющий выход которого соединен со счетчиком команд, а второй управляющий вход подключен к третьему выходу блока настройки, вход которого соединен с четвертым выходом блока управления.

Недостатками его являются ограничение быстродействия, ограничение скорости обмена с внешними устройствами, вызванное наличием одного устройства ввода-вывода, невозможность параллельного выполнения нескольких программ.

Целью изобретения является повышение быстродействия процессора за счет одновременного выполнения нескольких программ и повышения скорости обмена с внешней оперативной памятью и внешними устройствами.

Указанная цель достигается тем, что в известном компьютере, содержащем арифметико-логическое устройство на однородной вычислительной структуре, первый и второй регистры, блок управления, постоянное запоминающее устройство команд и оперативное запоминающее устройство, выход которого соединен с первым входом первого регистра, а первый вход - с выходом второго регистра, введены блок начальной загрузки, регистр-счетчик адреса и арифметико-логических устройств на однородной вычислительной структуре, которые вместе с первым арифметико-логическим устройством на однородной вычислительной структуре объединены в матрицу арифметико-логических устройств на однородной вычислительной структуре, причем каждое арифметико-логическое устройство на однородной вычислительной структуре матрицы арифметико-логических устройств на однородной вычислительной структуре связано входами и выходами с соседними арифметико-логическими устройствами на однородной вычислительной структуре или с соответствующими входами и выходами матрицы арифметико-логических устройств на однородной вычислительной структуре, при этом выход каждого разряда первого регистра через первый управляющий вход матрицы арифметико-логических устройств на однородной вычислительной структуре соединен с первым управляющим входом соответствующего арифметико-логического устройства на однородной вычислительной структуре, вторые управляющие входы которых через второй управляющий вход матрицы арифметико-логических устройств на однородной вычислительной структуре соединены с выходами соответствующих разрядов второго регистра, а первый из выходов матрицы арифметико-логических устройств на однородной вычислительной структуре соединен с первым входом блока управления, второй выход соединен с первым входом второго регистра, третий выход соединен с первым входом регистра-счетчика адреса, четвертый выход соединен со вторым входом оперативного запоминающего устройства, а пятый выход соединен со вторым входом блока управления, третий вход которого соединен с выходом блока начальной загрузки, первый выход связан со вторым входом второго регистра, второй выход связан со вторым входом первого регистра, третий выход связан с третьим входом оперативного запоминающего устройства, четвертый выход связан с первым входом постоянного запоминающего устройства команд, а пятый выход - со вторым входом регистра-счетчика адреса, выход которого связан с четвертым входом оперативного запоминающего устройства и со вторым входом постоянного запоминающего устройства команд, выход которого связан с первым входом первого регистра, третий вход которого связан с шестым выходом блока управления, с третьим входом второго регистра и с третьим входом регистра-счетчика адреса.

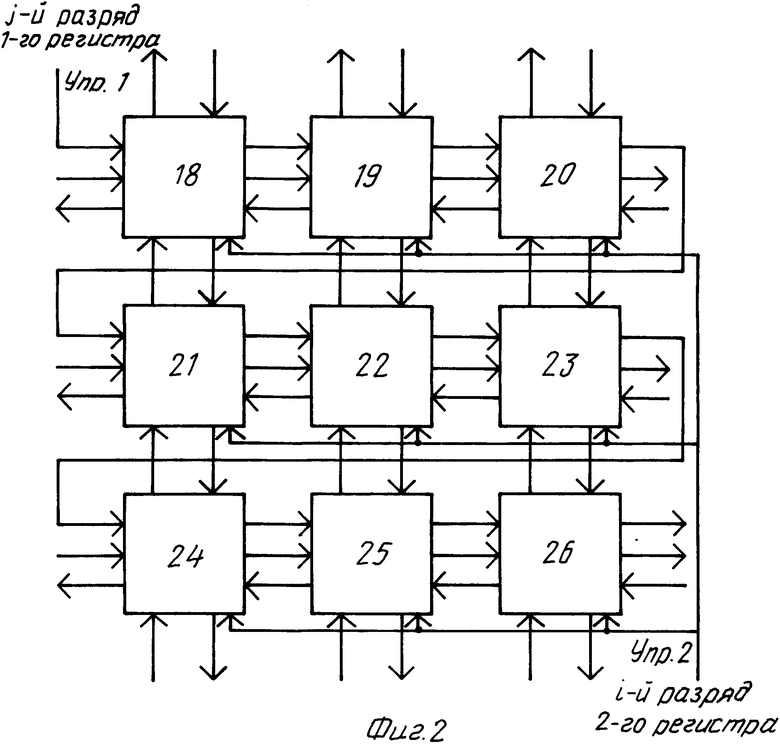

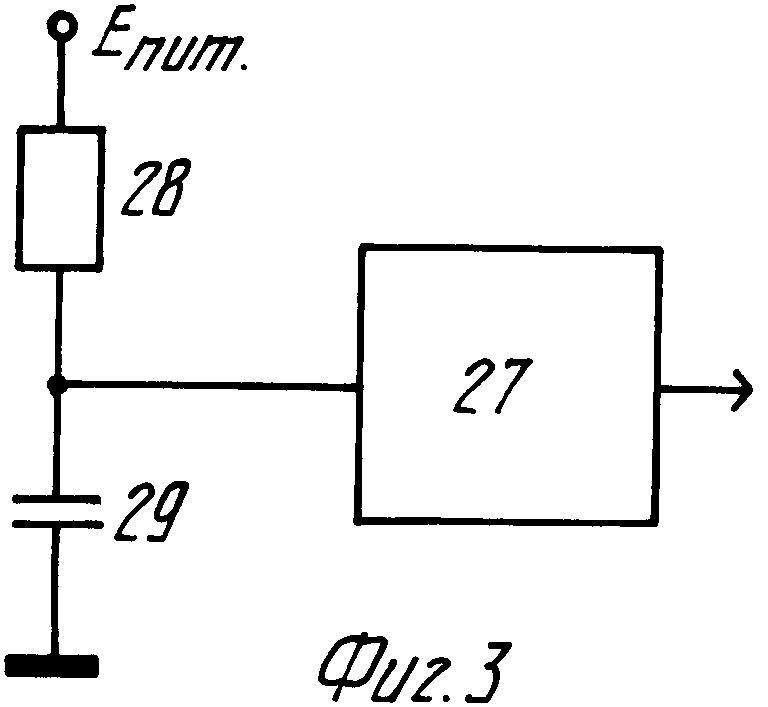

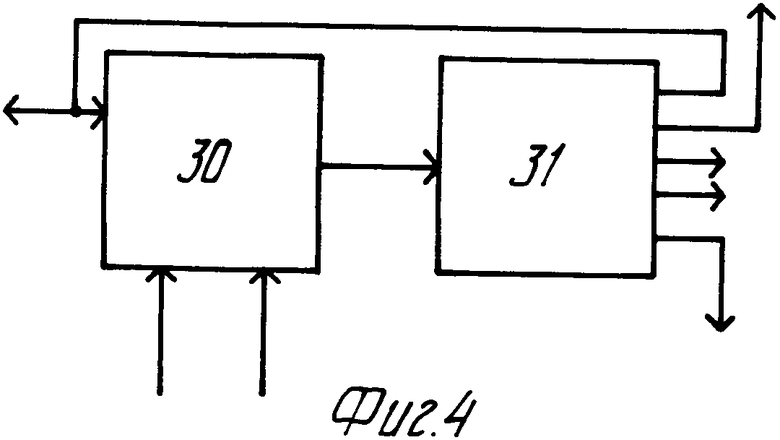

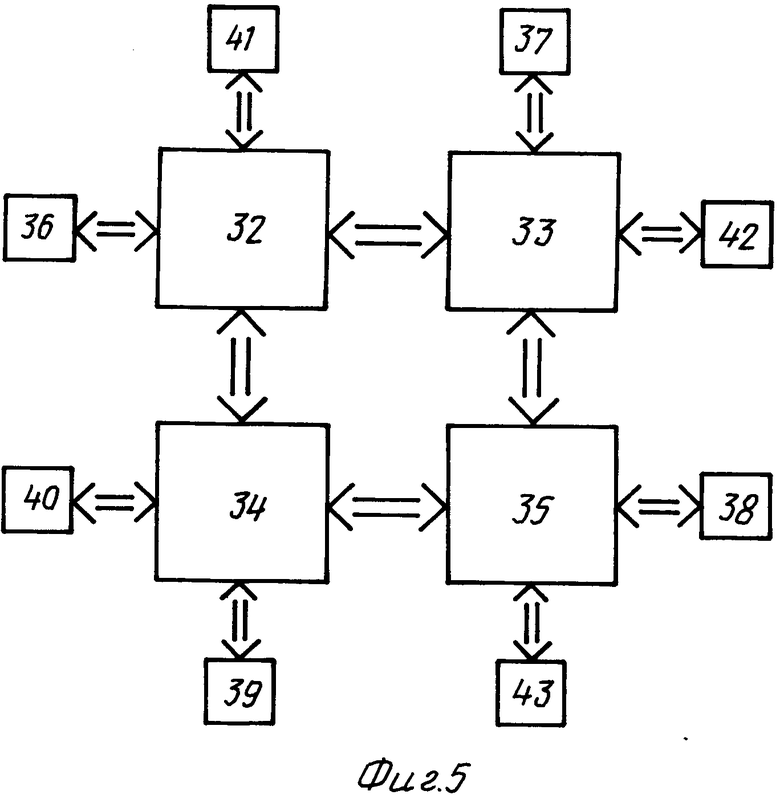

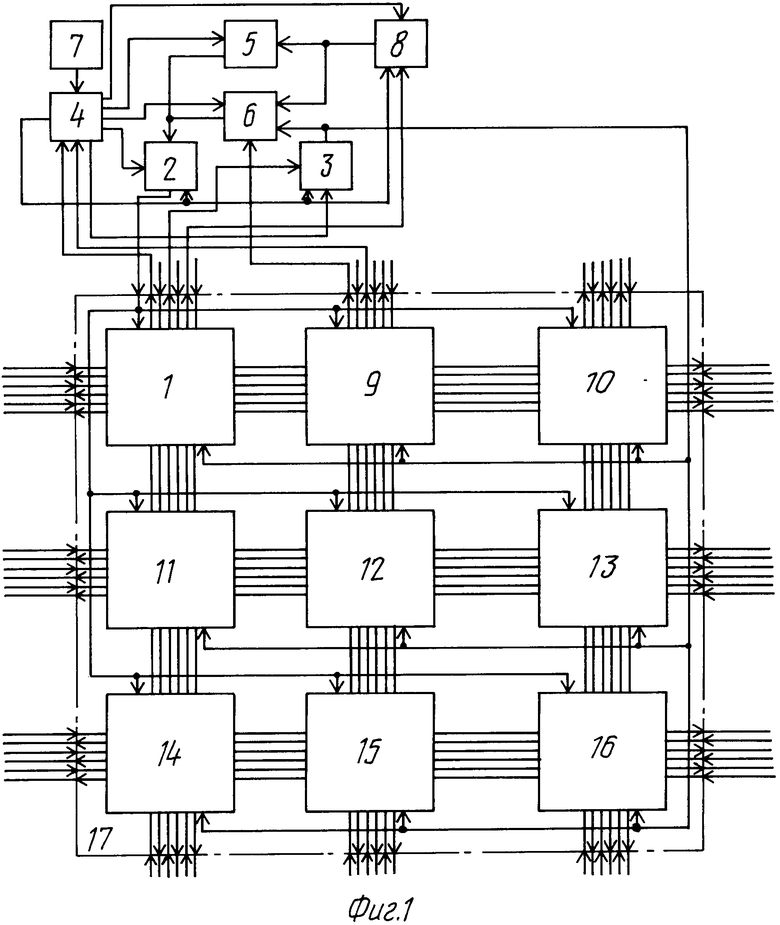

На фиг. 1 представлена структурная схема описываемого параллельного процесса с перепрограммируемой структурой на базе девяти арифметико-логических устройств на однородной вычислительной структуре; на фиг. 2 - структурная схема арифметико-логического устройства на однородной вычислительной структуре; на фиг. 3 - структурная схема блока начальной загрузки; на фиг. 4 - структурная схема блока управления; на фиг. 5 - структурная схема параллельного компьютера на основе параллельного процессора с перепрограммируемой структурой.

На фиг. 1-5 приняты следующие обозначения:

1 - арифметико-логическое устройство на однородной вычислительной структуре, 2, 3 - первый и второй регистры, 4 - блок управления, 5 - постоянное запоминающее устройство команд, 6 - оперативное запоминающее устройство, 7 - блок начальной загрузки, 8 - регистр-счетчик адреса, 9-16 - арифметико-логические устройства на однородной вычислительной структуре, 17 - матрица арифметико-логических устройств на однородной вычислительной структуре, 18-26 - ячейки однородной вычислительной структуры, 27 - одновибратор, 28 - резистор, 29 - конденсатор, 30 - счетчик, 31 - постоянное запоминающее устройство, 32, 33, 34, 35 - параллельные процессоры с перепрограммируемой структурой, 36, 37, 38, 39 - внешние оперативные запоминающие устройства, 40, 41, 42, 43 - внешние устройства.

На фиг. 1 представлена структурная схема описываемого параллельного процессора с перепрограммируемой структурой на базе девяти арифметико-логических устройств на однородной вычислительной структуре (N=8). Он содержит N+1 арифметико-логических устройств 1, 9-16, объединенных в матрицу 17, первый 2 и второй 3 регистры, блок 4 управления, постоянное запоминающее устройство команд 5, оперативное запоминающее устройство 6, блок 7 начального пуска, регистр-счетчик адреса 8. На фиг. 1 выходы матрицы арифметико-логических устройств 17 с первого по пятый соединены с соответствующими выходами первого и девятого арифметико-логических устройств на однородной вычислительной структуре. Но так как все выходные сигналы, выдаваемые из матрицы арифметико-логических устройств на однородной вычислительной структуре, вырабатываются программным путем, то соответствующая программа может быть записана в любое из арифметико-логических устройств на однородной вычислительной структуре 1, 9-16, имеющих связь с выходами матрицы арифметико-логических устройств на однородной вычислительной структуре 17, а выходы матрицы арифметико-логических устройств на однородной вычислительной структуре 17 с первого по пятый могут быть соединены с соответствующими выходами соответствующих арифметико-логических устройств. Входы и выходы матрицы арифметико-логических устройств на однородной вычислительной структуре 17 предназначены для выполнения следующих функций:

- первый управляющий вход является векторным, при этом выход каждого разряда первого регистра 2 через первый управляющий вход матрицы арифметико-логических устройств 17 соединен с первым управляющим входом соответствующего арифметико-логического устройства на однородной вычислительной структуре 18-26 и служит для ввода программы в арифметико-логические устройства 18-26;

- второй управляющий вход является векторным, при этом выход каждого разряда второго регистра 3 через второй управляющий вход матрицы арифметико-логических устройств 17 соединен со вторым управляющим входом соответствующего арифметико-логического устройства на однородной вычислительной структуре 18-26 и служит для включения режима ввода программы в арифметико-логические устройства;

- первый выход инициирует перезагрузку программы (программ) в матрице арифметико-логических устройств на однородной вычислительной структуре 17;

- второй выход выдает во второй регистр 3 информацию для записи в оперативное запоминающее устройство или маску, определяющую в какие арифметико-логические устройства на однородной вычислительной структуре будет вводиться программа;

- третий выход выдает начальный адрес записываемой или загружаемой программы;

- четвертый выход выдает в оперативное запоминающее устройство режим записи или чтения;

- пятый выход выдает сигнал инициализации работы блока управления.

На фиг. 2 представлена структурная схема арифметико-логического устройства на однородной вычислительной структуре 1, 9-16. Оно состоит из M ячеек однородной вычислительной структуры 18-26 (фиг. 2, M=9), например, может быть использована ячейка однородной вычислительной структуры. Каждая ячейка однородной вычислительной структуры 18-26 имеет по одному программному входу и выходу и по несколько информационных входов и выходов (на фиг. 2 их по четыре). Все программные входы-выходы ячеек одного арифметико-логического устройства на однородной вычислительной структуре 1, 9-16 последовательно соединены друг с другом и с одним из разрядов первого регистра 2. Программа записывается по одной команде в каждую ячейку однородной вычислительной структуры 18-26. Информационные входы-выходы каждой ячейки соединены с ближайшими соседями. В ячейке однородной вычислительной структуры 18-26 есть командный регистр (не показан), содержимое которого определяет, какую операцию выполняет ячейка однородной вычислительной структуры 18-26 и с какими соседними ячейками однородной вычислительной структуры 18-26 она программно связана.

Все ячейки жестко синхронизированы от общего генератора (не показан), то есть выполняют каждая свою команду одновременно. Данные в последовательном коде без задержки бит за битом передаются соседним ячейками или выдаются наружу для связи с внешними оперативными запоминающими устройствами 36-39 или внешними устройствами 40-43. Входы и выходы арифметико-логического устройства на однородной вычислительной структуре 18-26 предназначены для выполнения следующих функций:

- первый управляющий вход через первый управляющий вход матрицы арифметико-логических устройств на однородной вычислительной структуре 17 соединен с одним из разрядов первого регистра 2 и служит для ввода программы в арифметико-логические устройства 18-26;

- второй управляющий вход через второй управляющий вход матрицы арифметико-логических устройств на однородной вычислительной структуре 17 соединен с одним из разрядов второго регистра 3 и служит для включения режима ввода программы в арифметико-логические устройства на однородной вычислительной структуре 18-26;

- информационные входы и выходы служат для передачи информации в последовательном виде от одного процессора к другому.

На фиг. 3 представлена структурная схема блока начальной загрузки 7, который содержит одновибратор 27, срабатывающий при включении питания, резистор 28 и конденсатор 29. Выход блока начальной загрузки 7 предназначен для выдачи сигнала запуска блока управления при включении питания.

На фиг. 4 представлена структурная схема блока управления 4, который состоит из счетчика 30 и постоянного запоминающего устройства 31, содержащего запись временной диаграммы. Выходы блока управления 4 соединены с соответствующими разрядами постоянного запоминающего устройства 31. Счетчик 30 запускается по сигналу из блока начальной загрузки 7 или из матрицы арифметико-логических устройств на однородной вычислительной структуре 17. Последовательный перебор адресов обеспечивает считывание временной диаграммы и выдачу сигналов управления на соответствующие выходы.

Входы и выходы блока управления выполняют следующие функции:

- первый вход инициирует перезагрузку программы (программ) в матрице арифметико-логических устройств на однородной вычислительной структуре 17;

- второй вход предназначен для инициализации работы блока управления;

- третий вход предназначен для запуска блока управления при включении питания;

- первый выход разрешает прием во второй регистр 3;

- второй выход разрешает прием в первый регистр 2;

- третий выход выдает сигнал обращения к оперативному запоминающему устройству 6;

- четвертый выход выдает сигнал обращения к постоянному запоминающему устройству команд 5;

- пятый выход разрешает прием в регистр-счетчик адреса 8;

- шестой выход выдает сигнал начальной установки.

На фиг. 5 в качестве примера применения представлена структурная схема компьютера на основе параллельного процессора с перепрограммируемой структурой. Четыре параллельных процессора 32-35 соединены друг с другом внешними входами и выходами арифметико-логических устройств на однородной вычислительной структуре 1, 9-16, которым подключены также внешние устройства 40-43 и блоки внешних оперативных запоминающих устройств 36-39. Быстродействие такого компьютера может достигать триллиона операций в секунду.

Устройство работает следующим образом. Блок управления 4 по сигналу перезагрузки из блока начальной загрузки 7 или по сигналу с первого выхода матрицы арифметико-логических устройств на однородной вычислительной структуре 17 записывает начальный адрес выполняемой программы, выдаваемый по третьему выходу матрицы арифметико-логических устройств на однородной вычислительной структуре 17, в регистр-счетчик адреса 8. Одновременно во второй регистр 3 со второго выхода матрицы арифметико-логических устройств на однородной вычислительной структуре 17 записывается информация о том, в какие арифметико-логические устройства на однородной вычислительной структуре 1, 9-16 будет записываться программа. Второй управляющий вход каждого арифметико-логического устройства на однородной вычислительной структуре 1, 9-16 соединен с одним из разрядов второго регистра 3. Наличие "1" в этом разряде означает, что соответствующее арифметико-логическое устройство на однородной вычислительной структуре 1, 9-16 находится в режиме перезаписи программы, наличие "0" - в режиме выполнения программы. В процессе записи программы каждая из ячеек однородной вычислительной структуры 18-26 получает свою команду.

Далее значение регистра-счетчика адреса 8 увеличивается и дается сигнал на считывание из оперативного 6 или постоянного 5 запоминающих устройств в первый регистр данных 2, откуда программа поступает в арифметико-логические устройства на однородной вычислительной структуре 1,9-16. Блок управления 4 выдает сигнал окончания ввода программы, после чего регистр-счетчик адреса 8 и счетчик 30 блока управления сбрасываются в "0", одновременно сбрасывается в "0" и второй регистр 3, что означает запуск программ в тех арифметико-логических устройствах на однородной вычислительной структуре 1, 9-16, в которые она вводилась (в остальных арифметико-логических устройствах на однородной вычислительной структуре 1, 9-16 продолжается выполнение ранее введенных программ). Перед началом запуска выполняемая программа (их может быть несколько) должна быть записана в оперативное запоминающее устройство 6 или в постоянное запоминающее устройство команд 5. Причем программы для одного арифметико-логического устройства 1, 9-16 записываются в один разряд соответствующего количества слов оперативного запоминающего устройства 6 или постоянного запоминающего устройства команд 5. Это делается из арифметико-логического устройства на однородной вычислительной структуре 1, 9-16, имеющего связь со вторым регистром. На время выполнения программа переписывается и хранится в арифметико-логическом устройстве на однородной вычислительной структуре 1, 9-16. Первой программой, вводимой в арифметико-логические устройства на однородной вычислительной структуре 1, 19-16, является программа начальной загрузки, обеспечивающая связь параллельного процессора с перепрограммируемой структурой 32-35 с другими параллельными процессорами с перепрограммируемой 32-35 и внешними устройствами 40-43, в частности, с рабочим местом оператора, и хранящаяся в постоянном запоминающем устройстве команд 5. Далее смена и запуск программ происходит по запросам оператора, арифметико-логического устройства на однородной вычислительной структуре 1,9-16 или внешних устройств 40-43, или другого параллельного процессора с перепрограммируемой структурой 32-35).

Поставленная цель достигается тем, что на период выполнения программы на одном или нескольких арифметико-логических устройствах на однородной вычислительной структуре 1, 9-16 создается для данной программы, причем программа хранится непосредственно в арифметико-логических устройствах на однородной вычислительной структуре 1, 9-16, а также одновременной работой большого количества ячеек однородной вычислительной структуры 18-26.

Быстродействие параллельного процессора с перепрограммируемой структурой 32-35 может достигать сотен миллиардов операций в секунду. Программа может быть перезаписана полностью или частично из оперативного запоминающего устройства 6 или постоянного запоминающего устройства команд 5, что обеспечивает динамическую реконфигурацию вычислительной структуры в ходе выполнения программы и позволяет выполнять одновременно несколько программ. Увеличение скорости обмена с внешними оперативными запоминающими устройствами 36-39, другими параллельными процессорами с перепрограммируемой структурой 32-35 и внешними устройствами 36-39 достигается за счет большого количества входов-выходов арифметико-логических устройств на однородной вычислительной структуре 1, 9-16, входящих наружу, и тем, что на период выполнения программы в арифметико-логическом устройстве на однородной вычислительной структуре 1, 9-16, к которому подключено внешнее устройство 36-39, создается специализированная вычислительная конвейерная структура, оптимальная для операций обмена в данной программе.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИЗОБРАЖЕНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2093968C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ БОРТОВОЙ ИНДИКАТОР | 2000 |

|

RU2162204C1 |

| ПРОЦЕССОР ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2000 |

|

RU2180969C1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| СИСТЕМА ИНДИКАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2001 |

|

RU2206872C2 |

| Цифро-аналоговая система для регистрации и статистической обработки информации | 1979 |

|

SU858023A1 |

| НАВИГАЦИОННЫЙ КОМПЛЕКС ЛЕТАТЕЛЬНОГО АППАРАТА | 2000 |

|

RU2170409C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2179332C1 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

Изобретение относится к области вычислительной техники и предназначено для создания высокоскоростных систем обработки больших потоков данных в реальном режиме времени. Целью изобретения является повышение быстродействия процессора за счет одновременного выполнения нескольких программ и повышения скорости обмена с внешней оперативной памятью и внешними устройствами. Указанная цель достигается тем, что в известное устройство введены блок начальной загрузки, регистр-счетчик адреса и N арифметико-логических устройств на однородной вычислительной структуре, которые вместе с первым арифметико-логическим устройством на однородной вычислительной структуре объединены в матрицу арифметико-логических устройств на однородной вычислительной структуре, причем каждое арифметико-логическое устройство на однородной вычислительной структуре матрицы арифметико-логических устройств на однородной вычислительной структуре связано входами и выходами с соседними арифметико-логическими устройствами на однородной вычислительной структуре или с соответствующими входами и выходами матрицы арифметико-логических устройств на однородной вычислительной структуре. 5 ил.

Параллельный процессор, содержащий матрицу процессорных элементов, каждый из которых соединен соответствующими входами и выходами с соседними процессорными элементами матрицы, при этом одноименные входы и выходы крайних процессорных элементов матрицы образуют соответствующие входы и выходы матрицы, первый и второй буферные регистры, блок управления, счетчик адреса, постоянное и оперативное запоминающие устройства, первый и второй выходы блока управления соединены с входами управления постоянного и оперативного запоминающих устройств, адресные входы которых подключены к выходу счетчика адреса, вход управления которого соединен с третьим выходом блока управления, четвертый и пятый выходы которого подключены к входам разрешения приема первого и второго буферных регистров, входы начальной установки которых соединены с шестым выходом блока управления и входом начальной установки счетчика адреса, выход каждого разряда первого буферного регистра через первый управляющий вход матрицы соединен с первым управляющим входом соответствующего процессорного элемента матрицы, первый выход которой соединен с информационным входом второго буферного регистра, отличающийся тем, что он содержит блок начальной загрузки, а каждый процессорный элемент выполнен в виде матрицы однородных вычислительных ячеек, при этом выход блока начальной загрузки соединен с входом запуска блока управления, вход инициализации работы которого подключен к второму выходу матрицы процессорных элементов, через второй управляющий вход которой выходы разрядов второго буферного регистра соединены с вторыми управляющими входами соответствующих процессорных элементов матрицы, третий выход которой соединен с входом задания начального адреса счетчика адреса, четвертый выход матрицы процессорных элементов соединен с входом задания режима оперативного запоминающего устройства, информационный вход которого подключен к выходу второго буферного регистра, информационный вход первого буферного регистра соединен с выходами постоянного и оперативного запоминающих устройств.

| GB, патент, 1445714, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-04-27—Публикация

1994-07-06—Подача