Изобретение относится к вычислительной технике и может быть использовано для создания вычислительных систем, к которым предъявляются повышенные требования по надежности при длительной работе в неблагоприятных внешних условиях (внешние механические, электромагнитные и ионизирующие воздействия). В результате воздействия ионизирующих излучений или температуры наблюдаются деградация параметров микросхем средней и большой степени интеграции (СИС и БИС), приводящая к снижению быстродействия, что особенно характерно для микросхем, изготавливаемых по КМОП технологии.

В настоящее время КМОП БИС являются основой для создания вычислительных систем, служащих основой для бортовых систем управления объектами ракетно-космической техники. Снижение быстродействия микросхем из-за деградации параметров приводит к неработоспособности вычислительных систем и системы управления в целом.

В то же время работоспособность вычислительных систем может быть сохранена снижением тактовой частоты работы компонентов, поскольку отсутствуют катастрофические отказы микросхем.

Кроме того, в процессе эксплуатации систем дрейф параметров микросхем в ряде случаев может приводить к возрастанию их быстродействия. Построение известных систем на основе жестко фиксированной частоты задающих генераторов формирователей синхроимпульсов вычислительных устройств приводит в первом случае к преждевременному отказу систем управления из-за невозможности выполнить весь необходимый объем задач, а во втором - к недоиспользованию потенциально возможного быстродействия вычислителей. Все это приводит к неэффективному использованию имеющихся аппаратурных ресурсов вычислительных систем. Возникает задача сохранения работоспособности вычислительных систем при возникновении отказов комплектующих СИС и БИС как катастрофического, так и параметрического характера, а также обеспечения максимально полного использования имеющихся аппаратурных ресурсов. Для решения этой задачи в вычислительные системы необходимо ввести аппаратно-программные средства, обеспечивающие адаптацию системы к изменению параметров комплектующих элементов.

Известна трехканальная вычислительная система (АС №1156273, содержащая в каждом канале внешнее устройство и вычислительное устройство, информационный выход которого подключен к первому входу первого мажоритарного элемента и к первому входу первого элемента сравнения всех каналов. Второй вход первого элемента сравнения соединен с выходом первого мажоритарного элемента и со входом внешнего устройства, выход которого подключен к первому информационному входу второго мажоритарного элемента всех каналов, второй и третий информационные входы которого соединены соответственно со вторым и третьим информационными входами вторых мажоритарных элементов других каналов и с выходами внешних устройств соответственно. Выход второго мажоритарного элемента подключен к первому входу второго элемента сравнения и к первому входу вычислительного устройства. Второй вход второго элемента сравнения соединен с первым входом второго мажоритарного элемента, а выход - с выводом связи.

В каждом канале содержится также регистр номера канала, четыре блока анализа, группа элементов И, контрольный регистр и элемент ИЛИ, выход которого подключен ко входу прерывания вычислительного устройства. Первый вход контрольного регистра соединен с выходом последовательной передачи информации вычислительного устройства. Входы контрольного регистра соединены с выходами группы элементов И. Вторые выходы соединены со входами элемента ИЛИ. Кроме того, каждый канал содержит элемент НЕ, а каждый блок анализа выполнен в виде дешифратора, связанного входами с выходами элементов сравнения.

Это известное устройство благодаря установке мажоритарных элементов в выходных информационных шинах вычислителей обеспечивает нейтрализацию неисправности, возникающей в одном из каналов при правильной работе двух других каналов. Кроме того, благодаря введению схем сравнения, подключенных к связям внешних устройств, обеспечивается обнаружение неправильной работы одного из них по отличию его информации от двух других, что позволяет диагностировать отказы внешних устройств путем анализа состояний контрольного регистра вычислительным устройством. Эти свойства являются достаточно положительными. Особенно важным является нейтрализация неисправности в одном из каналов вычислительного устройства.

В то же время после возникновения неисправности в одном из каналов надежность дальнейшей работы системы резко снижается, так как возникновение неисправности в любом из двух оставшихся исправными вычислительных устройств приводит к полной неработоспособности системы. Это происходит потому, что интенсивность отказа в двух каналах в два раза больше, чем у одноканального вычислителя. Целесообразно максимально полно использовать имеющуюся избыточность в виде двух дополнительно введенных каналов для сохранения работоспособности системы после возникновения второй неисправности.

Задача сохранения работоспособности системы при возникновении двух неисправностей в системе частично решена в резервированном вычислительном устройстве (АС №1200292). В данном устройстве для повышения надежности между блоками памяти и процессора введен коммутатор, переключающий блоки по сигналам встроенных устройств оперативного контроля.

Общим недостатком известных вычислительных устройств является то, что как для работы схем мажоритации, так и для работы коммутатора, переключающего блоки в процессе работы, требуется синхронная и синфазная работа всех каналов устройства, что обеспечивается введением единого генератора синхроимпульсов. При такой реализации резервирования отказ этого генератора приводит к отказу устройства в целом, кроме того, наличие временного рассогласования одноименных сигналов разных каналов резервированного устройства требует снижение быстродействия с целью учета межканальных рассогласований, вызванных некоторыми отличиями задержек элементов разных каналов. Более того, в процессе работы в блоках вычислительного устройства под влиянием температуры и особенно из-за воздействия внешнего ионизирующего излучения, например, космического пространства происходит деградация параметров электрорадиоизделий (ЭРИ), учесть которую при проектировании невозможно.

С целью устранения отмеченных недостатков в части критичности отказа единого генератора синхроимпульсов, а также обеспечения максимально возможного быстродействия вычислительного устройства на каждом интервале времени работы в основном режиме предлагается адаптивная вычислительная система, содержащая Несколько (К) вычислительных модулей (ВМ) и несколько (М) модулей связи (МС) для обмена с периферийными подсистемами.

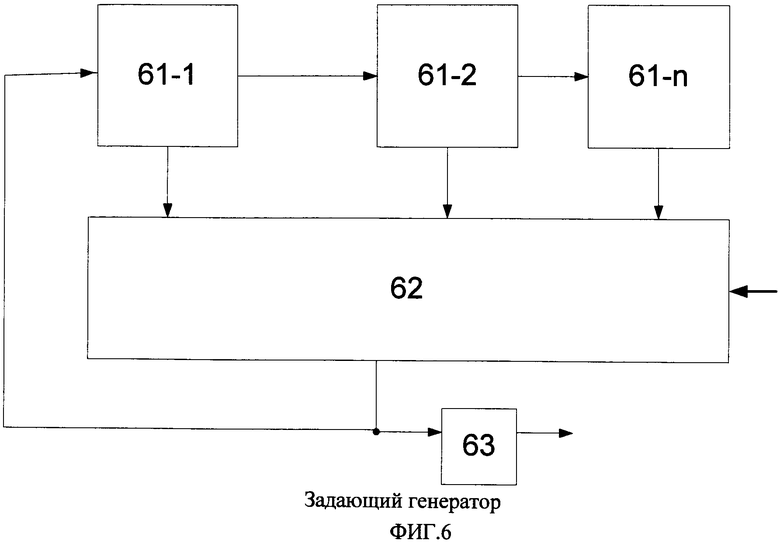

Для организации взаимодействия все модули подключены к трехканальной общесистемной магистрали (ОСМ), для управления которой, а также для контроля работы вычислительных модулей и модулей связи введен центральный - системный модуль (СМ), обозначенный цифрой 1. Системный модуль также подключен к общесистемной магистрали. В данной системе все модули работают независимо друг от друга, на собственных частотах синхроимпульсов.

На фиг.1 изображена структурная схема предлагаемой системы, где цифрами от 2-1 до 2-К обозначены вычислительные модули от ВМ №1 до ВМ № К соответственно, цифрами от 3-1 до 3-М обозначены модули обмена от МС №1 до МС № М соответственно. Цифрой 4 обозначен модуль общесистемного запоминающего устройства (СЗУ).

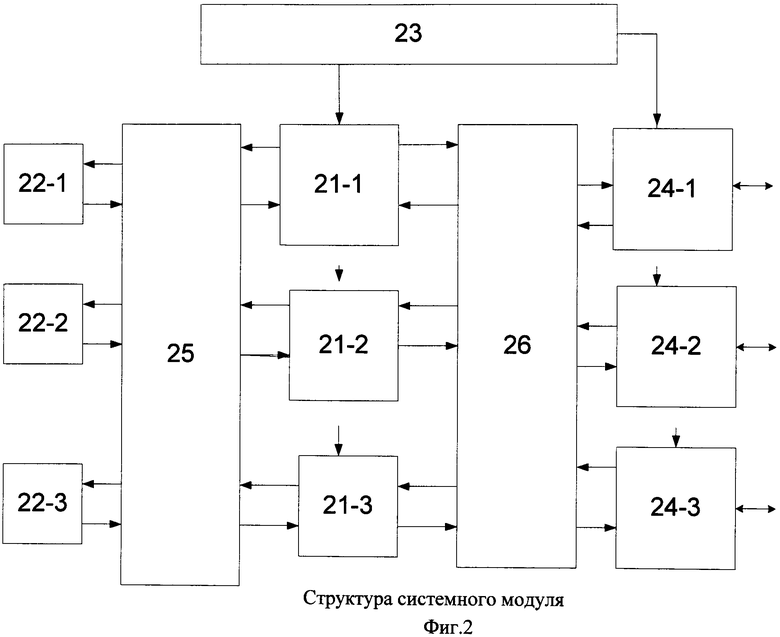

На фиг.2 изображена структурная схема системного модуля. Системный модуль содержит три идентичных процессора, обозначенные цифрами 21-1, 21-2 и 21-3, три запоминающих устройства (ЗУ), каждое из которых может содержать как оперативное запоминающее устройство (ОЗУ), так и постоянное запоминающее устройство (ПЗУ). ЗУ обозначены цифрами 22-1, 22-2 и 22-3. Кроме того, СМ содержит резервированный формирователь синхроимпульсов, обозначенный цифрой 23, три блока связи с магистралью (БСМ), обозначенные цифрами 24-1, 24-2 и 24-3, первый и второй блоки мажоритарных элементов, обозначенные цифрами 25 и 26 соответственно. Первая группа выходов резервированного формирователя синхроимпульсов подключена к синхронизирующим входам процессоров, а вторая группа выходов формирователя подключена к синхронизирующим входам блоков связи с магистралью, двунаправленные входы-выходы которых являются входами-выходами системного модуля.

Первый выход первого процессора подключен к первому входу первой группы входов первого блока мажоритарных элементов, у которого первый выход второй группы выходов подключен к входу первого запоминающего устройства, выход которого подключен к первому входу второй группы входов первого блока мажоритарных элементов, у которого первый выход первой группы выходов подключен к первому входу первого процессора, второй выход которого подключен к первому входу первой группы входов второго блока мажоритарных элементов, у которого первый выход второй группы выходов второго блока мажоритарных элементов подключен к входу первого блока связи с магистралью, выход которого подключен к первому входу второй группы входов второго блока мажоритарных элементов, у которого первый выход первой группы выходов подключен ко второму входу первого процессора, причем двунаправленный вход-выход первого блока связи с магистралью является первым двунаправленным входом-выходом системного модуля, у которого первый выход второго процессора подключен ко второму входу первой группы входов первого блока мажоритарных элементов, у которого второй выход второй группы выходов подключен к входу второго запоминающего устройства, выход которого подключен ко второму входу второй группы входов первого блока мажоритарных элементов, у которого второй выход первой группы выходов подключен к первому входу второго процессора, у которого второй выход подключен ко второму входу первой группы входов второго блока мажоритарных элементов, у которого второй выход второй группы выходов подключен ко входу второго блока связи с магистралью, выход которого подключен ко второму входу второй группы входов второго блока мажоритарных элементов, у которого второй выход первой группы выходов подключен к второму входу второго процессора, причем двунаправленный вход-выход второго блока связи с магистралью является вторым входом-выходом системного модуля, у которого первый выход третьего процессора подключен к третьему входу первой группы входов первого блока мажоритарных элементов, у которого третий выход второй группы выходов первого блока мажоритарных элементов подключен к входу третьего запоминающего устройства, выход которого подключен к третьему входу второй группы входов первого блока мажоритарных элементов, у которого третий выход первой группы выходов подключен к первому входу третьего процессора, второй выход которого подключен к третьему входу первой группы входов второго блока мажоритарных элементов, у которого третий выход второй группы выходов подключен ко входу третьего блока связи с магистралью, выход которого подключен к третьему входу второй группы входов второго блока мажоритарных элементов, у которого третий выход первой группы выходов подключен к второму входу третьего процессора, причем двунаправленный вход-выход третьего блока связи с магистралью является третьим входом-выходом системного модуля.

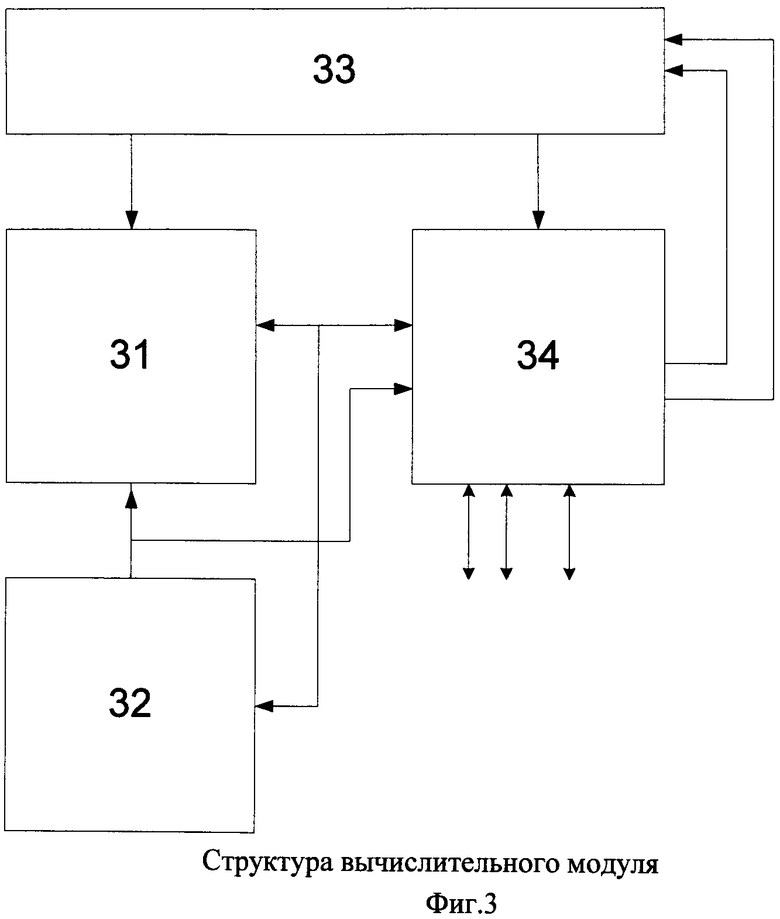

На фиг.3 изображена структурная схема вычислительного модуля, где цифрой 31 обозначен процессор, цифрой 32 - запоминающее устройство (ЗУ), цифрой 33 обозначен формирователь синхроимпульсов (ФСИ), цифрой 34 - устройство обмена по общесистемной магистрали (УОМ).

В вычислительном модуле выход процессора объединен с выходом УОМ и подключен к входу ЗУ, выход которого подключен ко входу процессора и входу УОМ, первый и второй управляющие выходы которого подключены к соответствующим входам формирователя синхроимпульсов, у которого первая группа выходов подключена к синхронизирующим входам УОМ, а вторая группа выходов подключена к синхронизирующим входам процессора, двунаправленные входы/выходы которого являются входами/выходами вычислительного модуля.

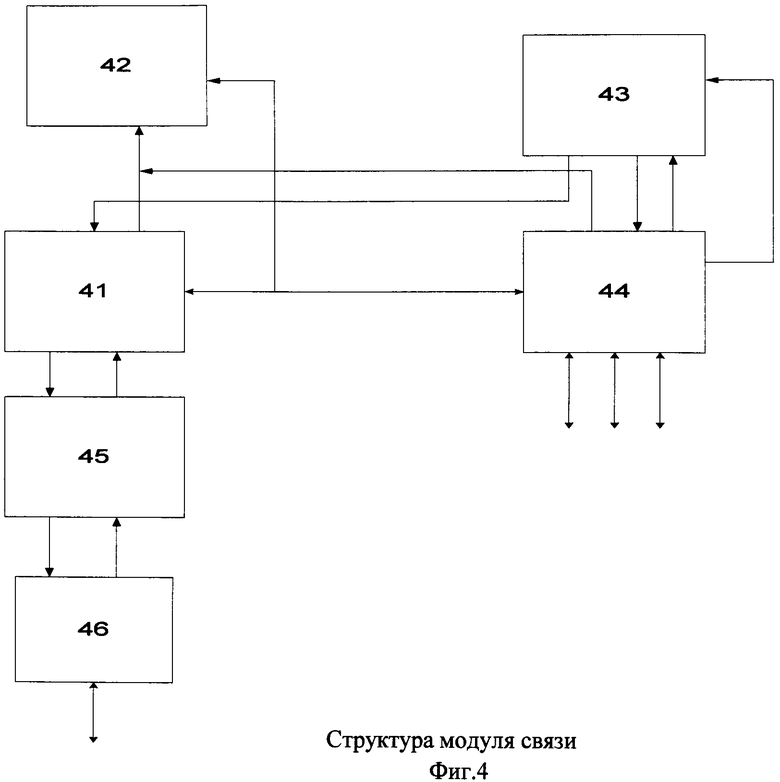

На фиг.4 изображена структурная схема модуля связи, где цифрой 41 обозначен процессор, цифрой 42 - запоминающее устройство (ЗУ), цифрой 43 обозначен формирователь синхроимпульсов (ФСИ), цифрой 44 - устройство обмена по общесистемной магистрали (УОМ), цифрой 45 обозначено кодирующе-декодирующее устройство (кодек), а цифрой 46 обозначено приемно-передающее устройство (ППУ) мультиплексного канала обмена.

В модуле связи выход процессора объединен с выходом УОМ и подключен ко входу ЗУ, выход которого подключен ко входу процессора и входу УОМ, первый и второй управляющие выходы которого подключены к соответствующим входам формирователя синхроимпульсов, у которого первая группа выходов подключена к синхронизирующим входам УОМ, а вторая группа выходов подключена к синхронизирующим входам процессора, двунаправленные входы/выходы которого являются магистральными входами/выходами модуля связи, при этом передающий выход процессора подключен ко входу кодека, выход которого подключен к принимающему входу процессора. При этом передающий выход кодека подключен к информационному входу ППУ, у которого информационный выход подключен к принимающему входу кодека, а мультиплексный вход/выход является соответствующим входом/выходом модуля связи, подключаемым к периферийным подсистемам.

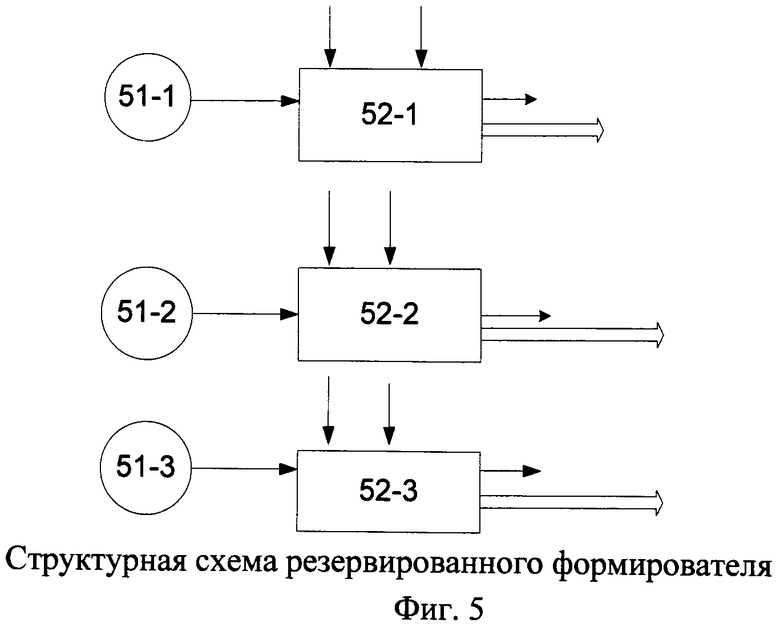

На фиг.5 изображена структурная схема резервированного формирователя синхроимпульсов.

Формирователь содержит три задающих генератора, обозначенных цифрами 51-1, 51-2 и 51-3, а также три узла формирования синхроимпульсов, обозначенных цифрами 52-1, 52-2, 52-3.

При этом выход каждого задающего генератора подключен к входу соответствующего узла формирования синхроимпульсов, группа выходов каждого из которых является выходами формирователя.

Фазирующий выход каждого из узлов формирования подключен к фазирующим входам двух других узлов формирования.

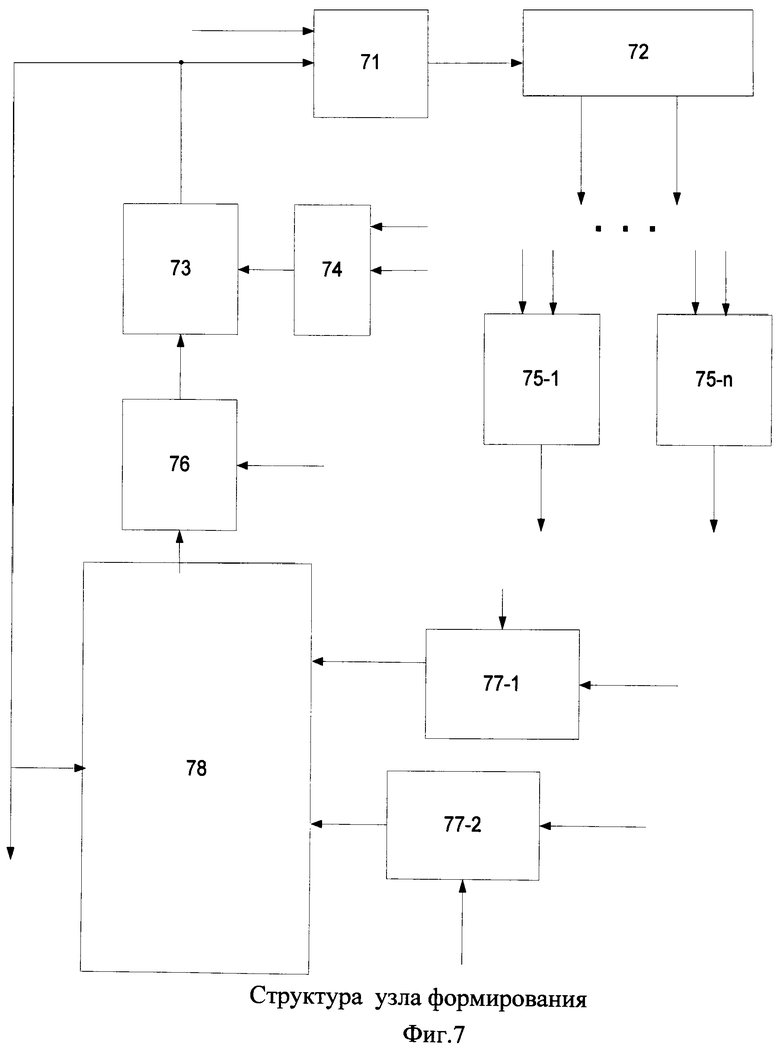

На фиг.6 изображена схема задающего генератора.

Генератор содержит n последовательно соединенных инверторов, обозначенных цифрами от 61-1 до 61-n соответственно.

При этом выходы всех инверторов подключены к входам мультиплексора, обозначенного цифрой 62, выход которого подключен к входу первого инвертора 61-1, входу буферного усилителя 63, выход которого является выходом генератора соответственно.

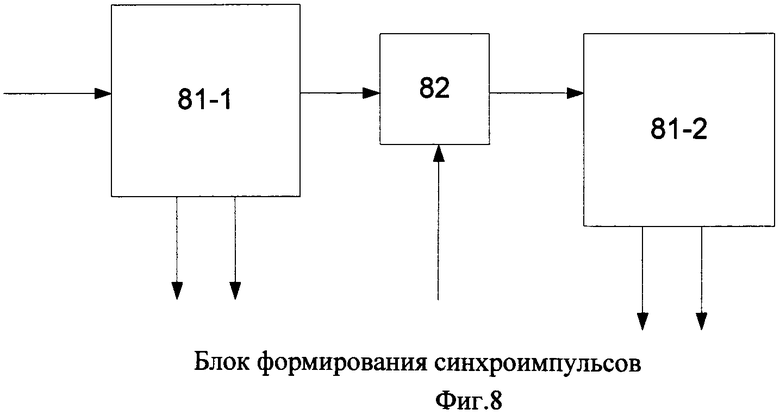

На фиг.7 изображена структура узла формирования резервированного формирователя синхроимпульсов.

Узел формирования содержит элемент И, обозначенный цифрой 71. Его выход подключен к сдвиговому регистру 72, цифрой 73 обозначен триггер останова, цифрой 74 обозначен дешифратор, n триггеров-формирователей обозначены цифрами от 75-1 до 75-n соответственно, триггер пуска обозначен цифрой 76, первый и второй триггеры привязки обозначены цифрами 77-1 и 77-2 соответственно. Мажоритарный элемент обозначен цифрой 78.

Первый вход элемента И является входом узла формирования, подключенного к задающему генератору. Выход элемента И подключен к входу сдвигового регистра, выходы четных и нечетных триггеров которого подключены соответственно к запускающим и сбрасывающим входам триггеров-формирователей. Информационные входы триггеров привязки являются фазирующими входами узла формирования, а синхронизирующие входы этих триггеров подключены к соответствующим выходам триггеров-формирователей. Выходы триггеров привязки подключены к первому и второму входам мажоритарного элемента, выход которого подключен к сигнальному входу триггера пуска, стробирующий вход которого подключен к выходу одного из триггеров формирователей. Выход триггера пуска подключен к сбрасывающему входу триггера останова, запускающий вход которого подключен к выходу дешифратора, входы которого подключены к выходам сдвигового регистра. При этом выход триггера останова подключен ко второму входу элемента И и третьему входу мажоритарного элемента и является выходом узла.

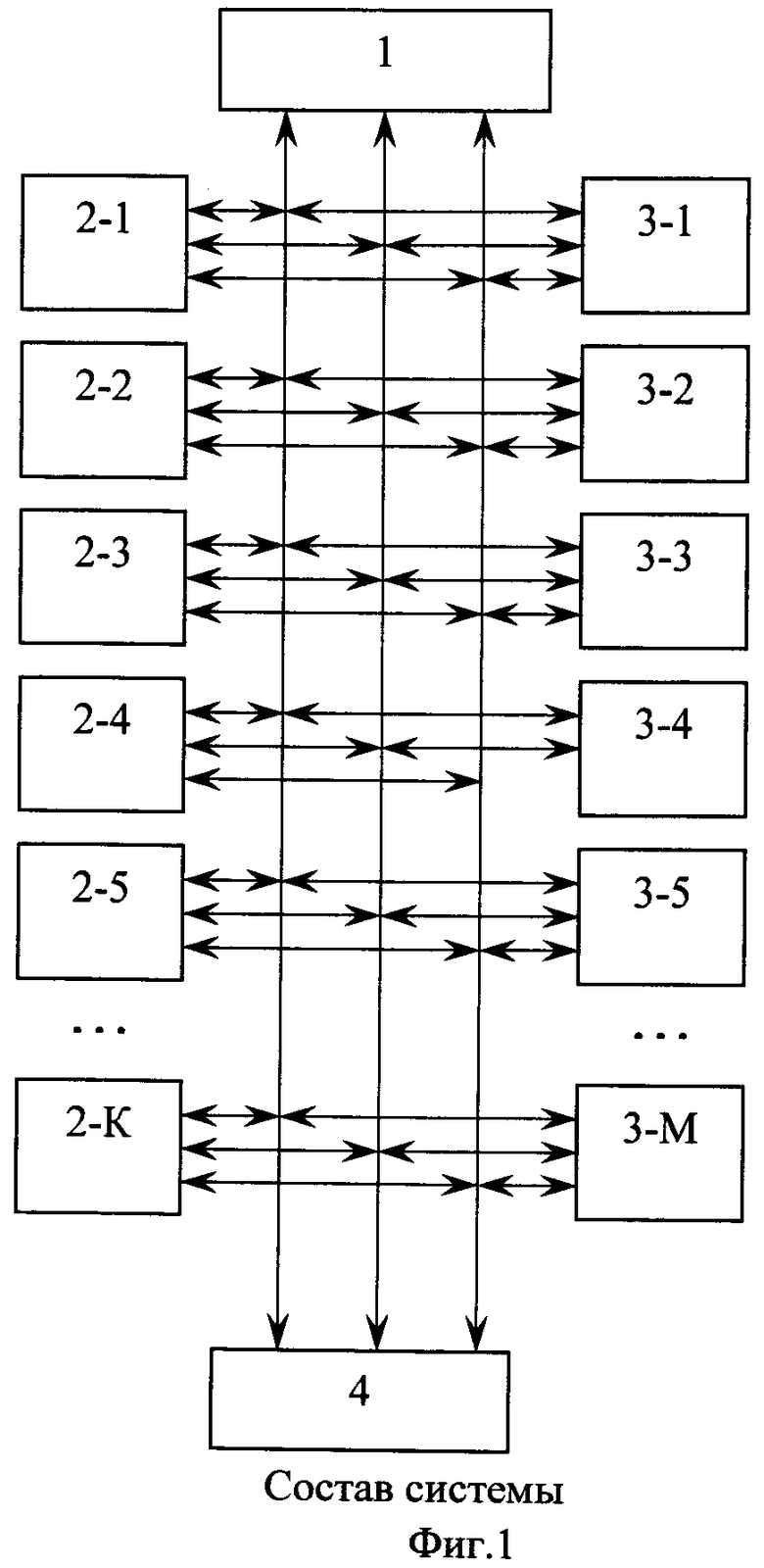

На фиг.8 изображена структура блока формирования синхроимпульсов вычислительного модуля и модуля связи. Блок формирования содержит первую и вторую секции сдвигового регистра, обозначенные цифрами 81-1 и 81-2 соответственно, а также элемент И, обозначенный цифрой 82. Вход первой секции сдвигового регистра является входом блока формирования, а выход подключен к первому входу элемента И, выход которого подключен к входу второй секции сдвигового регистра. При этом выходы первой и второй секций сдвигового регистра являются первой и второй группой выходов формирователя синхроимпульсов, второй управляющий вход которого является вторым входом элемента И.

Вычислительная система работает следующим образом.

После включения питания системный модуль инициирует вычислительные модули и модули связи посылкой по общесистемной магистрали командной информации, содержащей указатель адресов программ, подлежащих исполнению. Получив эту информацию, модули приступают к решению функциональных задач. Модули, по мере необходимости выставляя сигнал прерывания, обращаются к системному модулю с запросом разрешения межмодульного обмена. СМ по своей программе определяет приоритетность и очередность межмодульного обмена, после чего посылает в модуль, принимающий данные, команду на прием, а в модуль, выдающий данные, команду на передачу. Посылка последней команды, содержащей адресные указатели массивов передаваемых данных и количество слов в массиве, является командой начала обмена. Получив последнюю команду, модули начинают автономный обмен данными без участия СМ. После завершения обмена принимающий модуль посредством формирования сигнала прерывания информирует СМ об окончании обмена, формируя при этом в фиксированном адресе своего ОЗУ информацию о результатах обмена. В случае обнаружения ошибок при передаче данных, например, с помощью проверки контрольных сумм данных массива, СМ дает команду модулям на повторение обмена.

Для обеспечения нейтрализации отказов, возникающих в вычислительных модулях в процессе решения функциональных задач, СМ при начальной инициализации ВМ может назначить несколько (например, три) модулей на решение одной и той же задачи в режиме резервного счета. По окончании решения задачи каждый из модулей формирует в фиксированных адресах своего ОЗУ результирующий массив данных и просчитывает его контрольную сумму, которую записывает в фиксированный адрес памяти. Системный модуль после опроса контрольных сумм результатов расчета задачи разными ВМ сравнивает их и по результатам сравнения определяет возможный отказ в одном из модулей. При обнаружении ошибки в работе одного ВМ проводится процедура восстановления его работоспособности. Эта процедура заключается в следующем: СМ дает команду на передачу информации из памяти одного из исправных ВМ в память ВМ, у которого обнаружены отличия в результатах расчетов. В результате такой процедуры происходит восстановление правильной работы модуля, если отказ носил кратковременный характер (так называемый сбой). Если отказ в этом модуле повторяется в случае возникновения постоянной неисправности, то данный модуль бракуется и далее не назначается на решение функциональных задач, к решению которых подключаются только полностью исправные модули.

Такое построение системы позволяет гибко перераспределять имеющиеся вычислительные ресурсы между повышением производительности или надежности, назначая вычислительные модули или на параллельное решение разных функциональных задач, или переводя их в режим резервного счета одной и той же задачи. Для контроля исправности модулей как ВМ, так и МС они периодически переводится на решение задач тестовых проверок с заранее известным результатом.

По результатам этих проверок СМ посылкой по магистрали может изменять быстродействие функциональных модулей, перестраивая тактовую частоту их формирователей синхроимпульсов. Периодические проверки работоспособности модулей с перестройкой их быстродействия обеспечивает максимально возможную эффективность работы вычислительной системы и СУ в целом.

| название | год | авторы | номер документа |

|---|---|---|---|

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2444053C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| КОМПЛЕКС ОТЛАДКИ | 2010 |

|

RU2448363C1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

Изобретение относится к области вычислительной техники. Техническим результатом является повышение быстродействия вычислительного устройства на каждом интервале времени работы в основном режиме. Вычислительная система, содержащая несколько (К) вычислительных модулей и несколько (М) модулей связи с периферийными подсистемами, системное запоминающее устройство. Причем указанные модули подключены к трехканальной общесистемной магистрали, для управления которой введен трехканальный центральный (системный модуль). 6 з.п. ф-лы, 8 ил.

1. Вычислительная система, содержащая несколько (К) вычислительных модулей, несколько (М) модулей связи с периферийными подсистемами и модуль общесистемного запоминающего устройства,

отличающаяся тем, что в ее состав введен с подключенным к нему формирователем синхроимпульсов системный модуль, к которому через троированную общесистемную магистраль подключены остальные модули, а для связи с периферийными подсистемами вычислительная система имеет М мультиплексных модулей связи, причем формирователь синхроимпульсов содержит три идентичных задающих генератора, входы которых являются установочным входом формирователя, а выход каждого из которых подключен к входу своего узла фазирования, выходы которых являются выходами формирователя, а фазирующий выход каждого узла подключен к фазирующим входам двух других узлов.

2. Вычислительная система по п.1, отличающаяся тем, что системный модуль содержит три идентичных процессора, три системных запоминающих устройства, три блока связи с магистралью, два блока мажоритарных элементов, при этом первая группа выходов резервированного формирователя синхроимпульсов подключена к синхронизирующим входам процессоров, а вторая группа выходов формирователя подключена к синхронизирующим входам блоков связи с магистралью, двунаправленные входы-выходы которых являются входами-выходами системного модуля, причем первый выход первого процессора подключен к первому входу первой группы входов первого блока мажоритарных элементов, у которого первый выход второй группы выходов подключен к входу первого запоминающего устройства, выход которого подключен к первому входу второй группы входов первого блока мажоритарных элементов, у которого первый выход первой группы выходов подключен к первому входу первого процессора, второй выход которого подключен к первому входу первой группы входов второго блока мажоритарных элементов, у которого первый выход второй группы выходов подключен к входу первого блока связи с магистралью, выход которого подключен к первому входу второй группы входов второго блока мажоритарных элементов, у которого первый выход первой группы выходов подключен ко второму входу первого процессора, причем двунаправленный вход-выход первого блока связи с магистралью является первым двунаправленным входом-выходом системного модуля, у которого первый выход второго процессора подключен ко второму входу первой группы входов первого блока мажоритарных элементов, у которого второй выход второй группы выходов первого блока мажоритарных элементов подключен к входу второго запоминающего устройства, выход которого подключен ко второму входу второй группы входов первого блока мажоритарных элементов, у которого второй выход первой группы выходов подключен к первому входу второго процессора, у которого второй выход подключен ко второму входу первой группы входов второго блока мажоритарных элементов, у которого второй выход второй группы выходов подключен ко входу второго блока связи с магистралью, выход которого подключен ко второму входу второй группы входов второго блока мажоритарных элементов, у которого второй выход первой группы выходов подключен к второму входу второго процессора, причем двунаправленный вход-выход второго блока связи с магистралью является вторым входом-выходом системного модуля, у которого первый выход третьего процессора подключен к третьему входу первой группы входов первого блока мажоритарных элементов, у которого третий выход второй группы выходов первого блока мажоритарных элементов подключен к входу третьего запоминающего устройства, выход которого подключен к третьему входу второй группы входов первого блока мажоритарных элементов, у которого третий выход первой группы выходов подключен к первому входу третьего процессора, второй выход которого подключен к третьему входу первой группы входов второго блока мажоритарных элементов, у которого третий выход второй группы выходов подключен ко входу третьего блока связи с магистралью, выход которого подключен к третьему входу второй группы входов второго блока мажоритарных элементов, у которого третий выход первой группы выходов подключен к второму входу третьего процессора, причем двунаправленный вход-выход третьего блока связи с магистралью является третьим входом-выходом системного модуля.

3. Вычислительная система по п.1, отличающаяся тем, что вычислительный модуль содержит процессор, процессорное запоминающее устройство, вычислительный формирователь синхроимпульсов и устройство обмена по магистрали, при этом выход процессора объединен с выходом устройства обмена по магистрали и подключен к входу запоминающего устройства, выход которого подключен ко входу процессора и входу устройства обмена по магистрали, первый и второй управляющие выходы которого подключены к соответствующим входам формирователя синхроимпульсов, у которого первая группа выходов подключена к синхронизирующим входам устройства обмена по магистрали, а вторая группа выходов подключена к синхронизирующим входам процессора, двунаправленные входы-выходы которого являются входами-выходами вычислительного модуля, при этом формирователь синхроимпульсов содержит три задающих генератора, установочный вход которых является входом формирователя, выход каждого из которых подключен к своему узлу фазирования, группа выходов каждого из которых является выходами формирователя, а фазирующий выход каждого из узлов фазирования подключен к фазирующим входам двух других узлов.

4. Вычислительная система по п.1, отличающаяся тем, что модуль связи содержит процессор, свое запоминающее устройство и связной формирователь синхроимпульсов, кодек, приемопередающее устройство, свое устройство обмена по магистрали, при этом выход процессора объединен с выходом устройства обмена по магистрали и подключен ко входу запоминающего устройства, выход которого подключен ко входу процессора и входу устройства обмена по магистрали, первый и второй управляющие выходы которого подключены к соответствующим входам формирователя синхроимпульсов, у которого первая группа выходов подключена к синхронизирующим входам устройства обмена по магистрали, а вторая группа выходов подключена к синхронизирующим входам процессора, двунаправленные входы-выходы которого являются магистральными входами-выходами модуля связи, при этом передающий выход процессора подключен ко входу кодека, выход которого подключен к принимающему входу процессора, а передающий выход кодека подключен к информационному входу приемопередающего устройства, у которого информационный выход подключен к принимающему входу кодека, а мультиплексный вход-выход является соответствующим входом-выходом модуля связи, подключаемым к периферийным подсистемам.

5. Вычислительная система по п.1, отличающаяся тем, что задающий генератор содержит n последовательно соединенных инверторов, подключенных к входам мультиплексора, выход которого подключен к первому инвертору, буферному усилителю, выход которого является выходом генератора, и счетчику частоты, подключенного выходами к первым входам схемы сравненения, ко вторым входам которой подключены выходы регистра кода частоты, а инкрементный и декрементный выходы схемы сравнения подключены к одноименным входам счетчика кода частоты, подключенного выходами к управляющим входам мультиплексора, при этом вход счетчика кода частоты и вход регистра кода частоты являются установочным входом генератора.

6. Система по п.1, отличающаяся тем, что узел фазирования содержит элемент И, первый вход которого является входом узла, а выход подключен к сдвиговому регистру и счетчику, подключенного выходами к дешифратору, выход которого подключен к запускающему входу триггера останова, выход которого является фазирующим выходом узла и подключен ко второму входу элемента И и первому входу мажоритарного элемента, подключенного выходом к входу триггера пуска, выход которого подключен к сбрасывающему входу триггера останова, а ко второму и третьему входам мажоритарного элемента подключены выходы триггеров привязки, синхронизирующий вход которых объединен с первым входом элемента И, а входы являются фазирующими входами узла, при этом выходы четных и нечетных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам триггеров формирователей, выходы которых являются синхронизирующими выходами узла.

7. Вычислительная система по п.3, отличающаяся тем, что вычислительный формирователь синхроимпульсов содержит первую и вторую секции сдвигового регистра, а также элемент И, при этом вход первой секции сдвигового регистра является входом блока формирования, а выход подключен к первому входу элемента И, выход которого подключен к входу второй секции сдвигового регистра, при этом выходы первой и второй секций сдвигового регистра являются первой и второй группой выходов формирователя синхроимпульсов, второй управляющий вход которого является вторым входом элемента И.

| ХВОЩ С.Т | |||

| и др | |||

| МИКРОПРОЦЕССОРЫ И МИКРОЭВМ в системах автоматического управления | |||

| СПРАВОЧНИК | |||

| - Ленинград: Машиностроение, 1987 | |||

| Трехканальная резервированная вычислительная система | 1983 |

|

SU1156273A1 |

| RU 20084011 C1, 10.07.1997 | |||

| Многопроцессорная вычислительная система | 1987 |

|

SU1792540A3 |

| Резервированное вычислительное устройство | 1983 |

|

SU1200292A1 |

Авторы

Даты

2013-03-20—Публикация

2011-06-23—Подача