Изобретение относится к импульсной технике и может быть использовано в составе различных цифровых устройств, работающих в условиях воздействия электромагнитных помех и разрядов статического электричества.

Целью изобретения является расширение функциональных возможностей устройства путем введения режима вычитания.

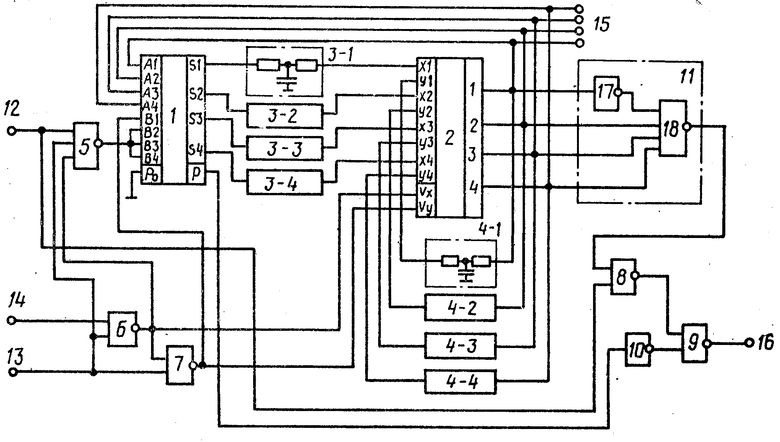

На чертеже приведена схема устройства для частного случая, когда n 4.

Устройство содержит четырехразрядный комбинационный сумматор 1, двухканальный четырехразрядный мультиплексор 2, RC-элементы задержки 3.1,3.4, 4.1, 4,4, элементы ИЛИ-НЕ 5-9, инвертор 10 и дешифратор 11. Первый вход элемента ИЛИ-НЕ 5 cоединен с шиной 12 управления, второй вход с шиной сброса 13, третий вход с выходом элемента ИЛИ-НЕ 6, с первым управляющим входом мультиплексора 2 и первым входом элемента ИЛИ-НЕ 7, второй вход которого соединен с шиной 13 сброса и вторым входом элемента ИЛИ-НЕ 6, первый вход которого соединен с входной шиной 14. Выход элемента ИЛИ-НЕ 7 cоединен с вторым управляющим входом мультиплексора 2 и входом младшего разряда первого слагаемого комбинационного сумматора 1, входы остальных разрядов первого слагаемого комбинационного сумматора 1 соединены с выходом элемента ИЛИ-НЕ 5. Входы разрядов второго слагаемого комбинационного сумматора 1 соединены с выходами соответствующих разрядов мультиплексора 2 и разрядными выходами 15 счетчика, выходы разрядов комбинационного сумматора 1 через RC-элементы задержки 3.1, 3.4 подключены к соответствующим входам первого канала мультиплексора 2, выходы разрядов которого через RC-элементы задержки 4.1,4.4 соединены с соответствующими входами второго канала мультиплексора 2. Входы дешифратора 11 подключены к соответствующим выходам разрядов мультиплексора 2, выход соединен с первым входом элемента ИЛИ-НЕ 8, второй вход которого соединен с шиной управления 12, выход с первым входом элемента ИЛИ-НЕ 9. Выход переноса комбинационного сумматора 1 через инвертор 10 соединен с вторым входом элемента ИЛИ-НЕ 9, выход которого соединен с выходной шиной 16. Постоянная времени RC-элементов задержки 3.1,3.4, 4.1,4.4 одинаковая и выбирается, исходя из требуемого уровня помехозащиты счетчика. Резисторы на выходах всех RC-элементов задержки не являются функционально необходимыми элементами схемы: они нужны, в частных случаях, например для защиты отдельных серий микросхемы с комплементарной МДП структурой (например серии 564) от так называемого тиристорного эффекта при больших значениях емкостей на входах этих микросхем. Дешифратор 11 служит для выделения состояния устройства, соответствующего числу "1", выполнен на одном инверторе 17 и элементе ИЛИ-НЕ 18. Может быть выполнен также на базе элементов И-НЕ (не четырех инверторах и одном элементе И-НЕ), или что несколько сложнее, на интегральной микросхеме дешифратора, при этом используется только один из выходов таких дешифраторов выход, соответствующий числу "1" (у последних двух дешифраторов выходной сигнал необходимо дополнительно инвертировать). Дешифратор 11 в принципе может быть настроен и для выделения других состояний устройства (кроме нулевого), т. е. для формирования выходного сигнала устройства в других его состояниях. В этих случаях при циклической работе устройства его коэффициент пересчета не меняется, только первый выходной сигнал устройства после начала счета появляется раньше, чем при настройке дешифратора на число "1", т.е. в первом цикле устройство как бы имеет другой, меньший, коэффициент пересчета. Однако такое свойство устройства позволяет использовать его в составе различных цифровых устройств, например в составе формирователей пачек импульсов, т.е. позволяет расширить сферу применения устройства. Построение предлагаемого устройства с количеством разрядов более четырех, т.е. больше, чем показано на фиг.1, осуществляется путем простого увеличения разрядов комбинационного сумматора 1, мультиплексора 2 и количества RC-элементов задержки 3.1,3.4, 4.1,4.4 и входов дешифратора 11.

Работает устройство для счета импульсов (см.фиг.1) следующим образом.

Перед работой устройство устанавливается в исходное нулевое состояние подачей импульсного сигнала положительной полярности по шине сброса 13 (здесь и далее в тексте уровни сигналов соответствуют счетчику, реализованному на базе микросхем серии 564). При этом в течение длительности импульса сброса на выходах элементов ИЛИ-НЕ 5-7 и, следовательно, первом и втором управляющих входах мультиплексора 2 поддерживается уровень логического нуля. При наличии уровня логического нуля на обоих управляющих входах мультиплексора 2 на его разрядных выходах присутствует независимо от уровней сигналов на разрядных входах уровень логического нуля. Поэтому конденсаторы RC-элементов задержки 4.1,4.4 начинают разряжаться (если до этого были заряжены) через малые выходные сопротивления разрядных выходов мультиплексора 2. Одновременно уровни логического нуля с разрядных выходов мультиплексора 2 поступают на входы разрядов второго слагаемого комбинационного сумматора 1. Но так как в течение длительности импульса сброса на всех разрядных входах и первого слагаемого комбинационного сумматора 1 присутствуют уровни логического нуля, то на выходах его разрядов в течение импульса сброса также поддерживается уровень логического нуля. Следовательно, конденсаторы RС-элементов задержки 3.1,3.4 также начинают разряжаться (если до этого были заряжены) через малые выходные сопротивления разрядных выходов комбинационного сумматора 1. Длительность импульса выбирается такой, что в течение длительности этого импульса конденсаторы RC-элементов задержки 3.1,3.4, 4.1,4.4 полностью разряжаются (до уровня напряжения логического нуля на выходах комбинационного сумматора 1 и мультиплексора 2). После окончания импульса сброса на выходе элемента ИЛИ-НЕ 6 восстанавливается уровень логической единицы, а на выходах элементов ИЛИ-НЕ 5, ИЛИ-НЕ 7 сохраняется уровень логического нуля. Следовательно, на первом управляющем входе мультиплексора 2 будет уровень логической единицы, на втором логического нуля. При такой комбинации сигналов на управляющих входах мультиплексора 2 на его разрядные выходы выдаются сигналы, имеющиеся на входах его первого канала, т.е. уровни сигналов с конденсаторов RC-элементов задержки 3.1,3.4. Так как в течение длительности импульса сброса эти конденсаторы разряжаются, то на выходах мультиплексора 2 уровни логического нуля сохраняются. Следовательно, на разрядных выходах комбинационного сумматора 1 также сохраняются уровни логического нуля, поскольку на всех входах первого и второго слагаемых комбинационного сумматора 1 в это время наблюдается уровень логического нуля, конденсаторы RC-элементов задержки 3.1,3.4 остаются разряженными. Таким образом, после импульса сброса конденсаторы всех RC-элементов задержки 3.1,3.4, 4.1,4.4 разряжены, а на всех разрядных выходах комбинационного сумматора 1 и мультиплексора 2 реверсивного счетчика присутствуют уровни логического нуля. Такое состояние устройства сохраняется до подачи счетного импульса по входной шине 14. Устройство при включении питания само устанавливается в описанное выше исходное состояние (благодаря разряженным конденсаторам RC-элементов задержки 3.1, 3.4, 4.1,4.4) и не нуждается в начальном сбросе.

Устройство в режиме сложения работает следующим образом.

Для работы устройства в режиме сложения по шине управления подается соответствующий сигнал уровень логической единицы, при этом описанное исходное состояние не нарушается. При поступлении по входной шине 14 первого счетного импульса (положительной полярности) на выходе элемента ИЛИ-НЕ 6 появляется уровень логического нуля, а на выходе элемента ИЛИ-НЕ 7 уровень логической единицы, так как на шине сброса 13 имеется уровень логического нуля. Следовательно, на первом и втором управляющих входах мультиплексора 2 в течение длительности первого счетного импульса поддерживаются соответственно уровни логического нуля и логической единицы. При такой комбинации сигналов на управляющих входах мультиплексора 2 на его разрядные выходы выдаются сигналы со входов второго канала, т.е. с выходов RC-элементов задержки 4.1,4.4. Поскольку конденсаторы этих RC-элементов задержки после импульса сброса поддерживаются разряженными, то в течение первого счетного импульса на всех разрядных выходах мультиплексора 2 поддерживается уровень логического нуля, т. е. двоичный код (0000) числа "0" (младший разряд кода здесь и далее в тексте справа). Этот код нулевого состояния счетчика одновременно поддерживает разряженное состояние конденсаторов RC-элементов 4.1,4.4 и подается на разрядные входы второго слагаемого комбинационного сумматора 1 для обеспечения операции суммирования с кодом первого счетного импульса, подаваемого на разрядные входы первого слагаемого комбинационного сумматора 1 (код счетного импульса, поступающего через элементы ИЛИ-НЕ 6, 7 на вход младшего разряда первого слагаемого комбинационного сумматора 1 равен 0001, поскольку на разрядных входах остальных разрядов второго слагаемого комбинационного сумматора 1 поддерживается уровень логического нуля с выхода элемента ИЛИ-НЕ 5). Таким образом, в течение первого счетного импульса код этого импульса и код предыдущего состояния (в данном случае нулевого состояния) устройства на входах слагаемых комбинационного сумматора 1 поддерживаются неизменными, на разрядных выходах комбинационного сумматора 1 присутствует код суммы (0001), следовательно, заряжается конденсатор RC-элемента задержки 3.1. Постоянная времени RС-элементов выбирается таким образом, чтобы конденсатор до среза счетного импульса успел зарядиться до уровня логической единицы (или разрядиться до уровня логического нуля, если был заряжен). Таким образом к концу первого счетного импульса код нового состояния устройства (0001) запоминается на конденсаторах RС-элементов задержки 3.1,3.4, а конденсаторы элементов задержки 4.1,4.4 в это время еще хранят код предыдущего исходного состояния (0000) устройства. После снятия первого счетного импульса на выходе элемента ИЛИ-НЕ 6 восстанавливается уровень логической единицы, а на выходе элемента ИЛИ-НЕ 7 уровень логического нуля, следовательно, на входах разрядов первого слагаемого комбинационного сумматора 1 также восстанавливается уровень логического нуля. На первом и втором управляющих входах мультиплексора 2 восстанавливаются исходные уровни соответственно логической единицы и логического нуля, а при такой комбинации сигналов на управляющих входах на его разрядные выходы выдается, как было указано выше, код числа, запомненный на конденсаторах RC-элементов задержки 3.1,3.4, в нашем случае это код числа "1" (0001). Этот код поступает на входы разрядов второго слагаемого комбинационного сумматора 1, а так как на всех входах первого слагаемого комбинационного сумматора 1 в это время присутствует уровень логического нуля, то на его разрядных выходах будет тот же код 0001, который будет поддерживать запомненный после первого счетного импульса на конденсаторах RC-элементов задержки 3.1,3.4 код числа "1" (0001). Одновременно, т.е. при появлении кода 0001 на разрядных выходах мультиплексора 2 после первого счетного импульса, начинается заряд конденсатора RC-элемента задержки 4.1. Постоянная времени RC-элементов задержки 4.1,4.4 выбирается таким образом, чтобы до поступления следующего счетного импульса конденсатор успел зарядиться до уровня логической единицы (или разрядиться до уровня логического нуля, если он был заряжен). Таким образом, в интервале между счетными импульсами код нового состояния устройства (в нашем случае код числа "1") запоминается и на конденсаторах RC-элементов задержки 4.1,4.4. Следовательно, между первым и вторым счетными импульсами счетчик находится в своем первом устойчивом состоянии: на конденсаторах RC-элементов задержки 3.1,3.4 и 4.1,4.4 хранится код (0001) состояния устройства, которое оно приняло после первого счетного импульса. При поступлении второго счетного импульса счетчик работает аналогично, в течение длительности счетного импульса код числа "1" (0001), хранящийся на конденсаторах RC-элементов задержки 4.1,4.4, через мультиплексор 2 подается на входы второго слагаемого комбинационного сумматора 1 для обеспечения суммирования кода состояния 0001 счетчика, соответствующего числу "1", с кодом счетного импульса (0001), подаваемого на входы первого слагаемого этого комбинационного сумматора. В результате на разрядных выходах комбинационного сумматора 1 в течение второго счетного импульса присутствует код числа "2" (0010), при этом разряжается конденсатор RC-элемента задержки 3.1, подключенного к выходу первого разряда комбинационного сумматора 1, и заряжается конденсатор RC-элемента задержки 3.2, подключенного к выходу второго разряда комбинационного сумматора 1. После окончания второго счетного импульса код числа "2" (0010), запомненный на конденсаторах RC-элементов задержки 3.1, 3.4, через мультиплексор 2 и комбинационный сумматор 1 поддерживает сам себя, и одновременно разряжается конденсатор RC-элемента задержки 4.1, подключенного к выходу первого разряда мультиплексора 2, и заряжается конденсатор RC-элемента задержки 4.2, подключенного к выходу второго разряда мультиплексора 2. Таким образом, после второго счетного импульса на конденсаторах RC-элементов задержки 3.1,3.4 и 4.1,4.4 хранится код 0010, соответствующий числу "2", устройство находится во втором своем устойчивом состоянии и сохраняет его до поступления следующего (третьего) счетного импульса. При поступлении третьего и последующих счетных импульсов устройство в рассматриваемом режиме сложения работает аналогично и последовательно принимает свои состояния, включая и состояние, соответствующее числу "15", двоичный код которого 1111. При поступлении шестнадцатого счетного импульса на выходе переноса (Р) комбинационного сумматора 1 появляется сигнал с уровнем логической единицы с длительностью, равной длительности счетного импульса, который через инвертор 10 и элемент ИЛИ-НЕ 9 выдается (поскольку при работе устройства в режиме суммирования на другом входе элемента ИЛИ-НЕ 9 поддерживается уровень логического нуля разрешение) на выходную шину 16 как импульс переполнения устройства. А после окончания шестнадцатого счетного импульса конденсаторы всех RC-элементов задержки оказываются разряженными, т.е. устройство возвращается в исходное нулевое состояние. Таким образом, устройство изменяет свое состояние по срезу каждого счетного импульса и только в том случае, если длительность счетного импульса, поступающего по входной шине 14, оказывается больше некоторого заданного значения, т.е. будет достаточной для перезаряда конденсаторов RC-элементов задержки 3.1,3.4 (от уровня логического нуля до уровня логической единицы или наоборот), в противном случае после окончания счетного импульса устройство сохраняет свое текущее состояние. Поскольку промежуточные состояния устройства хранятся на емкостях RC-элементов задержки, т.е. пассивных и инерционных элементах памяти конденсаторах, а устройство содержит только элементы комбинационной логики, т.е. не содержит в своем составе активных бистабильных функциональных элементов, оно устойчиво и к внутренним помехам, в том числе к помехам по шинам питания. Вход шины 13 сброса устройства обладает преимуществом перед управляющим входом шины 12 и счетным входом шины 14, при этом при подаче импульса сброса на разрядных выходах мультиплексора 2 код 0000 устанавливается сразу по фронту импульса сброса и сохраняется в течение этого импульса. Однако нулевое состояние по окончании импульса сброса устройство сохраняет только в том случае, если длительность этого импульса будет достаточной для перезаряда конденсаторов RC-элементов задержки 3.1,3.4. В противном случае после окончания импульса сброса (помехи) устройство восстанавливает свое состояние, которое оно имеет до поступления указанного импульса по шине 13 сброса.

Рассмотрим теперь работу устройства в режиме вычитания.

Для перевода устройства в режим вычитания по управляющей шине 12 подается уровень логического нуля, следовательно в этом режиме в работе устройства принимают участие элементы ИЛИ-НЕ 5, 8, которые в режиме суммирования блокированы постоянным сигналом с уровнем логической единицы, поданным по шине управления 12. Установка устройства в исходное нулевое состояние перед работой в режиме вычитания осуществляется так же, как перед работой в режиме суммирования. При этом функциональные узлы устройства работают аналогично. Свое нулевое состояние устройство сохраняет до подачи счетных импульсов. При поступлении по входной шине 14 первого счетного импульса на выходе элемента ИЛИ-НЕ 6 появляется уровень логического нуля, на выходах элементов ИЛИ-НЕ 5, ИЛИ-НЕ 7 уровень логической единицы, так как на шинах сброса 13 и управления 12 имеется уровень логического нуля. Следовательно, в течение счетного импульса на входах всех разрядов первого слагаемого комбинационного сумматора 1 поддерживается уровень логической единицы, т.е. код 1111 (двоичный код числа 15), а на первом и втором управляющих входах мультиплексора 2 соответственно уровень логического нуля и логической единицы. При такой комбинации сигналов на управляющих входах мультиплексора 2 на его разрядные выходы выдаются сигналы с входов второго канала, т.е. с выходов RC-элементов задержки 4.1,4.4, т. е. в данном случае на разрядных выходах мультиплексора в течение длительности счетного импульса поддерживается код 0000.

Этот код нулевого состояния устройства одновременно поддерживает разряженное состояние конденсаторов RC-элементов задержки 4.1,4.4 и подается на разрядные входы второго слагаемого комбинационного сумматора 1 для обеспечения операции суммирования с кодом счетного импульса 1111 (в данном случае первого счетного импульса), присутствующего в течение длительности счетного импульса на разрядных входах первого слагаемого комбинационного сумматора 1. В результате на разрядных выходах комбинационного сумматора 1 в течение первого счетного импульса присутствует код 1111, конденсаторы RC-элементов задержки 3.1,3.4 заряжаются до уровня логической единицы. Таким образом, к концу первого счетного импульса код нового состояния устройства (1111) запоминается на конденсаторах RC-элементов задержки 3.1,3.4, а конденсаторы RC-элементов задержки 4.1, 4.4 в это время еще хранят код предыдущего (нулевого) состояния (0000) устройства. После снятия первого счетного импульса на выходе элемента ИЛИ-НЕ 6 восстанавливается уровень логической единицы, на выходе элемента ИЛИ-НЕ 7 уровень логического нуля. Следовательно, на всех входах разрядов первого слагаемого комбинационного сумматора 1 восстанавливается уровень логического нуля, на управляющих входах мультиплексора 2 исходная комбинация сигналов. При этом на разрядные выходы мультиплексора 2 выдается код 1111, запомненный на конденсаторах RC-элементов задержки 3.1,3.4, который поступает на входы разрядов второго слагаемого комбинационного сумматора 1, и на выходах последнего поддерживается тот же код 1111, поскольку между счетными импульсами на входах разрядов первого слагаемого комбинационного сумматора 1 поддерживается уровень логического нуля, т. е. код 0000. Одновременно при появлении кода 1111 на выходах мультиплексора 2 начинается процесс заряда конденсаторов RC-элементов задержки 4.1,4.4, который завершается до поступления второго счетного импульса. Таким образом, после первого счетного импульса устройство в режиме вычитания принимает состояние 1111, соответствующее числу 15. При появлении второго счетного импульса в течение этого импульса код числа 15 (1111), запомненный и хранящийся на конденсаторах RC-элементов задержки 4.1,4.4, через мультиплексор 2 подается на входы разрядов второго слагаемого комбинационного сумматора 1 для обеспечения суммирования кода состояния 1111 счетчика с кодом второго счетного импульса 1111 (код всех счетных импульсов в режиме вычитания 1111), подаваемого на входы разрядов первого слагаемого комбинационного сумматора 1. В результате на разрядных выходах комбинационного сумматора 1 в течение второго счетного импульса присутствует код числа 14 (1110), а на выходе переноса уровень логической единицы (сигнал переноса). При этом разряжается конденсатор RC-элемента задержки 3.1, а сигнал переноса на выходную шину 16 не проходит, поскольку элемент ИЛИ-НЕ 9 блокирован по первому входу уровнем логической единицы с выхода элемента ИЛИ-НЕ 8, на обоих входах которого имеется уровень логического нуля. После окончания второго счетного импульса код 1110 числа 14, запомненный на конденсаторах RC-элементов задержки 3.1,3,4, через мультиплексор 2 и комбинационный сумматор 1 поддерживает сам себя. Одновременно разряжается конденсатор RC-элемента задержки 4.1. Следовательно, после второго счетного импульса устройство принимает второе устойчивое состояние, соответствующее числу 14, запоминает и хранит код этого текущего состояния (1110) на конденсаторах RC-элементов задержки 3.1,3.4, 4.1,4.4. При поступлении третьего, четвертого и последующих счетных импульсов устройство в рассматриваемом режиме работы, т.е. в режиме вычитания, работает аналогично и последовательно принимает состояния, соответствующие соответственно числам 13, 12 и т.д. (коды 1101, 1100 и т.д.), включая и пятнадцатый счетный импульс, по срезу которого устройство принимает состояние, соответствующее числу "1" (код 0001). При этом в течение каждого счетного импульса на выходе переноса комбинационного сумматора 1 появляется сигнал переноса, который на выходную шину 16 не проходит, поскольку на первом входе элемента ИЛИ-НЕ 9 cохраняется блокирующий сигнал уровень логической единицы. После окончания пятнадцатого счетного импульса, когда устройство принимает состояние, соответствующее числу "1" (код 0001), на выходе дешифратора 11 появляется уровень логической единицы, на выходе элемента ИЛИ-НЕ 8 уровень логического нуля, т. е. с первого входа элемента ИЛИ-НЕ 9 снимается блокирующий этот элемент сигнал. При поступлении шестнадцатого счетного импульса на выходах разрядов комбинационного сумматора 1 появляется (как результат суммирования кода предыдущего состояния 0001 устройства с кодом 1111 счетного импульса) код 0000, а на выходе переноса уровень логической единицы, т. е. сигнал переноса. При этом разряжаются конденсаторы RC-элементов задержки 3.1,3.4, а код 0001 на выходе мультиплексора 2 в течение длительности счетного импульса сохраняется, сохраняется и сигнал на выходе дешифратора 11, следовательно, сохраняется уровень логического нуля (разрешение) на первом входе элемента ИЛИ-НЕ 9, поэтому сигнал переноса комбинационного сумматора 1, проходя через инвертор 10 и элемент ИЛИ-НЕ 9, выдается на выходную шину 16 в качестве импульса переполнения устройства. После окончания шестнадцатого счетного импульса на выходы мультиплексора 2 выдается код 0000, запомненный в течение шестнадцатого счетного импульса на конденсаторах RC-элементов задержки 3.1,3.4, который поступает на входы разрядов второго слагаемого комбинационного сумматора 1, и с его выходов через RC-элементы задержки 3.1,3,4 сам себя поддерживает. Одновременно исчезает уровень логической единицы на выходе дешифратора 11. Разряжается конденсатор RC-элемента задержки 4.1. Таким образом в режиме вычитания после шестнадцатого счетного импульса конденсаторы всех RC-элементов задержки 3.1,3.4, 4.1,4.4 оказываются разряженными, т. е. устройство возвращается в свое исходное нулевое состояние, при этом импульс переполнения устройства формируется и выдается на выходную шину 16 в течение длительности шестнадцатого счетного импульса. Из изложенного следует, что в обоих режимах работы функциональные элементы устройства работают одинаково, за исключением элементов, формирующих импульс переполнения и код счетного импульса: в режиме сложения импульс переполнения устройства формируется перед переходом его из состояния, соответствующего числу "15", в состояние, соответствующее числу "16" ("0"), а кодом счетного импульса является двоичный код числа "1" (0001). В режиме вычитания импульс переполнения устройства формируется перед переходом его из состояния, соответствующего числу "1", в состояние, соответствующее числу "0", а кодом счетного импульса является двоичный код числа "15" (1111).

Устройство для счета импульсов может иметь количество разрядов больше, чем показано на фиг.1. Для этого достаточно по известным правилам нарастить до требуемой разрядности комбинационного сумматора 1, мультиплексора 2 и количество входов дешифратора 11 и RC-элементов задержки. По сравнению с известным устройством предлагаемое устройство расширяет функциональные возможности. Расширение функциональных возможностей устройства достигнуто введением в него режима вычитания и возможности формировать (с помощью дешифратора 11) выходной сигнал устройства в любом его состоянии, кроме нулевого, что способствует расширению сферы его применения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1987 |

|

SU1464893A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1988 |

|

SU1572383A1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1991 |

|

SU1817645A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1989 |

|

SU1785407A2 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1991 |

|

SU1826835A1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1990 |

|

SU1814487A1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1992 |

|

RU2022463C1 |

Изобретение относится к импульсной технике и может быть использовано в составе различных цифровых устройств в условиях помех. Цель изобретения расширение функциональных возможностей устройства путем введения режима вычитания. Устройство содержит сумматор 1, мультиплексор 2, RC-элементы задержки 3 1, 3 4, 4 1, 4 4, элементы ИЛИ-НЕ 5 9, инвертор 10 и дешифратор 11. На шину управления 12 подаются сигналы выбора направления счета. На шину 13 подается сигнал сброса при начальной установке состояния, а на шину 14 подаются входные счетные импульсы. Увеличение или уменьшение кода обеспечивается сумматором 1, а в промежутках между входными сигналами состояние сохраняется в конденсаторах элементов задержки. 1 ил.

УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ, содержащее входную и выходную шины, шину сброса, n-разрядный комбинационный сумматор, первые и вторые RС-элементы задержки, первый и второй элементы ИЛИ-НЕ и двухканальный n-разрядный мультиплексор, первый вход первого элемента ИЛИ-НЕ соединен с входной шиной, второй вход с шиной сброса и первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента ИЛИ-НЕ и первым управляющим входом двухканального n-разрядного мультиплексора, второй управляющий вход которого соединен с выходом второго элемента ИЛИ-НЕ и входом младшего разряда первого слагаемого n-разрядного комбинационного сумматора, входы остальных разрядов первого слагаемого n разрядного комбинационного сумматора объединены, входы разрядов второго слагаемого соединены с выходами соответствующих разрядов двухканального n разрядного мультиплексора, выходы разрядов через соответствующие первые RС-элементы задержки подключены к соответствующим входам первого канала двухканального n-разрядного мультиплексора, выходы разрядов которого через соответствующие вторые RС-элементы задержки соединены с соответствующими входами его второго канала, отличающееся тем, что, с целью расширения функциональных возможностей путем введения режима вычитания, в него введены третий, четвертый и пятый элементы ИЛИ-НЕ, инвертор, дешифратор и шина управления, причем первый вход третьего элемента ИЛИ-НЕ соединены с шиной управления, второй вход с шиной сброса, третий вход с выходом первого элемента ИЛИ-НЕ, выход с объединенными входами разрядов, кроме младшего, первого слагаемого n-разрядного комбинационного сумматора, выходы разрядов двухканального n-разрядного мультиплексора соединены с соответствующими входами дешифратора, выход которого соединен с первым входом четвертого элемента ИЛИ-НЕ, второй вход которого соединен с шиной управления, выход с первым входом пятого элемента ИЛИ-НЕ, выход переноса n-разрядного комбинационного сумматора через инвертор соединен с вторым входом пятого элемента ИЛИ-НЕ, выход которого соединен с выходной шиной.

| Счетчик импульсов | 1983 |

|

SU1187263A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-10-27—Публикация

1988-12-28—Подача