Область техники, к которой относится изобретение

Настоящее изобретение относится к вычислительной технике и может использоваться для сложения двоичных чисел в произвольной системе счисления.

Уровень техники

Известны комбинационные параллельные сумматоры с модулем сложения, равным целой степени двойки, состоящее из одноразрядных сумматоров, связанных общей цепью последовательного или параллельного переноса [1, 2]. Недостаток таких сумматоров заключается в фиксированном значении модуля сложения 2n (n - число разрядов сумматора), что ограничивает возможности их применения в устройствах автоматики.

Из известных аналогов наиболее близким по технической сущности к настоящему изобретению является двоично-десятичный сумматор с модулем сложения, равным 10 [3], состоящий из первого сумматора, подключенного входами к шинам слагаемых, и второго сумматора, у которого входы первого слагаемого соединены с выходами первого сумматора, а выходы - с выходной шиной устройства. Между выходом первого сумматора и входами второго слагаемого второго сумматора подключен комбинационный блок, который в случае превышения числом на выходе первого сумматора значения 9 (1001 в двоичной системе) подает на второй вход второго сумматора двоичное дополнение 9. В результате из числа, образованного первым сумматором, вычитается число 6, а число на выходной шине устройства равно сумме слагаемых по модулю сложения 10. Однако в устройстве-прототипе модуль сложения также фиксирован и не может регулироваться электронным путем, что ограничивает его функциональные возможности.

Сущность изобретения

Целью настоящего изобретения является обеспечение возможности электронного управления модулем сложения.

Указанная цель достигается путем сложения во втором сумматоре результата, полученного при сложении слагаемых в первом сумматоре, с двоичным дополнением заданного модуля сложения в том случае, когда указанный результат оказывается больше или равен заданному модулю сложения.

Для этого в устройство, содержащее подключенный к шинам слагаемых первый сумматор и второй сумматор, у которого входы первого слагаемого соединены с выходами первого сумматора, а выходы - с выходной шиной суммы, введены элемент ИЛИ, блок управляемых инверторов и компаратор. При этом первая группа входов компаратора присоединена к выходам первого сумматора, а его вторая группа входов - к входной шине управления модулем сложения и группе информационных входов блока управляемых инверторов. Выходы блока управляемых инверторов подключены к входам второго слагаемого второго сумматора, а входы элемента ИЛИ соединены соответственно с выходом переноса первого сумматора и с выходом компаратора. Выход элемента ИЛИ, соединенный с входом управления блока управляемых инверторов и входом переноса второго сумматора, служит выходом переноса устройства.

Блок управляемых инверторов может быть выполнен в виде группы элементов ИЛИ-НЕ, у которых первые входы служат соответствующими информационными входами блока управляемых инверторов, а объединенные вторые входы через инвертор соединены с входом управления блока управляемых инверторов.

Разрядность входящих в устройство первого и второго сумматоров, компаратора и блока инверторов выбирается одинаковой.

Если при суммировании слагаемых в первом сумматоре результат оказывается меньше заданного модуля сложения, то второй сумматор не корректирует результата сложения. В случае, когда результат сложения на первом сумматоре оказывается не менее заданного модуля сложения, элемент ИЛИ вырабатывает и передает логическую единицу на вход переноса второго сумматора и управляющий вход блока управляемых инверторов, который формирует на своих выходах поразрядную инверсию модуля сложения. В итоге результат сложения первого сумматора корректируется вторым сумматором путем вычитания из него модуля сложения и формирования сигнала переноса на выходе элемента ИЛИ.

Изменяя двоичное число на шине управления модулем сложения, можно задавать модуль сложения, что выгодно отличает устройство согласно настоящему изобретению от прототипа и других известных аналогов.

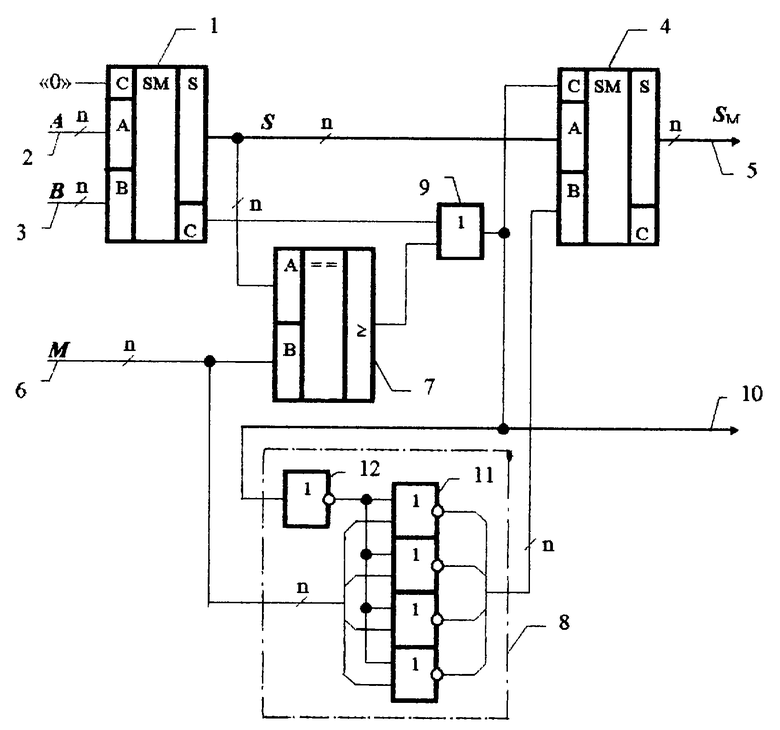

На чертеже показана электрическая функциональная схема сумматора с переменным модулем сложения согласно настоящему изобретению.

Сведения, подтверждающие возможность осуществления изобретения

Показанная на чертеже функциональная схема сумматора с переменным модулем сложения состоит из первого n-разрядного сумматора 1, который своими входами первого и второго слагаемых подключен к n-разрядным шинам 2 и 3 слагаемых А и В соответственно, и второго n-разрядного сумматора 4, соединенного входом первого слагаемого с n-разрядным выходом первого сумматора 1, а выходом - с n-разрядной шиной 5 суммы. Имеется также n-разрядная шина 6 управления модулем М сложения устройства, к которой подключены один n-разрядный вход компаратора 7 и n-разрядный информационный вход блока 8 управляемых инверторов. Другой n-разрядный вход компаратора 7 соединен с выходом первого сумматора 1, а его выход подключен к одному входу элемента ИЛИ 9, другой вход которого присоединен к выходу переноса С первого сумматора 1, а выход - одновременно к входу переноса С второго сумматора 4 и к управляющему входу блока 8 управляемых инверторов. В свою очередь n-разрядный выход блока 8 управляемых инверторов соединен с n-разрядным входом второго слагаемого второго сумматора 4. Выход 10 элемента ИЛИ 9 служит выходом переноса устройства.

Блок 8 управляемых инверторов в описываемом варианте осуществления устройства включает группу из n элементов ИЛИ-НЕ 11, выходы которого являются n-разрядным выходом блока 8 управляемых инверторов, а первые входы - его n-разрядным информационным входом. Вторые входы всех элементов 11 ИЛИ-НЕ через инвертор 12 соединены с управляющим входом блока 8 управляемых инверторов.

Разрядность устройства может быть произвольной, для определенности положим n=4.

Устройство работает в следующем порядке.

На входы 2 и 3 слагаемых поступают четырехразрядные двоичные числа слагаемых А и В, а на вход 6 управления модулем сложения - четырехразрядное двоичное число М, равное заданному модулю сложения. Пусть М=10 (1010 в двоичной системе).

В случае, когда сумма слагаемых S на выходе первого сумматора 1 оказывается меньше 10, компаратор 7 вырабатывает на своем выходе логический 0. Так как сигнала переноса в первом сумматоре 1 не возникает, то на выходе элемента ИЛИ 9 присутствует уровень логического 0. На выходах блока 8 управляемых инверторов также образуются нули, т.е. его выходное число равно 0000. Таким образом, на вход первого слагаемого второго сумматора 4 поступает число S, на его вход второго слагаемого - 0, на его вход переноса - 0. Поэтому число SМ на выходной шине 5 суммы равно числу S, т.е. полученный первым сумматором 1 результат не корректируется и перенос на выходе элемента 9 ИЛИ не возникает. Например, при А=4 и В=3 сумма SM=S=7 (0111 в двоичной системе).

В том случае, когда S≥10, например, при А=4 и В=9 их сумма S равна 13 (1101 в двоичной системе), компаратор 7 вырабатывает на своем выходе уровень логической 1, который через элемент 9 ИЛИ поступает на вход переноса второго сумматора 4 и на управляющий вход блока 8 управляемых инверторов. Число на выходе блока 8 управляемых инверторов будет при этом поразрядной инверсией числа М, т.е. будет равным 5 (0101 в двоичной системе). При сложении чисел S= 1101,  и переноса С=1 во втором сумматоре 4 их сумма окажется равной 0011, т.е. 3 в десятичной системе счисления. Так как на выходе 10 имеется логическая 1 сигнала переноса, то общее выходное число устройства в двоично-десятичной системе равно 13. По существу в этом случае второй сумматор 4, складывая значение S с двоичным дополнением отрицательного числа М, осуществляет вычитание М из S.

и переноса С=1 во втором сумматоре 4 их сумма окажется равной 0011, т.е. 3 в десятичной системе счисления. Так как на выходе 10 имеется логическая 1 сигнала переноса, то общее выходное число устройства в двоично-десятичной системе равно 13. По существу в этом случае второй сумматор 4, складывая значение S с двоичным дополнением отрицательного числа М, осуществляет вычитание М из S.

Совершенно аналогично устройство работает при другом значении модуля М.

Устройство в соответствии с настоящим изобретением может использоваться в качестве цифрового контроллера, управляющего селекцией рабочей фазы в устройствах на основе многофазных опорных генераторов [4, 5].

Литература

1. Зельдин Е. А. Цифровые интегральные схемы в информационно-измерительной аппаратуре. - Л.: Энергоатомиздат, Ленингр. отд-ние, 1986, с. 128, рис.9-8.

2. Алексенко А.Г., Шагурин И.И. Микросхемотехника. - М.: Радио и связь, 1990, с. 272, рис.7.1.

3. Угрюмов Е. П. Проектирование элементов и узлов ЭВМ. - М.: Высшая школа, 1987, стр. 195, рис.11.13.

4. Управляемый напряжением генератор импульсов. Патент РФ 2103816, бюл. 1998 3.

5. Устройство фазовой синхронизации. Патент РФ 2119717, бюл. 1998 27.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР С РАЗДЕЛЬНОЙ ЦИФРОВОЙ РЕГУЛИРОВКОЙ ЧАСТОТЫ И ФАЗЫ ИМПУЛЬСОВ | 2000 |

|

RU2168268C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2000 |

|

RU2173934C1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ С ПЕРЕМЕННЫМ МОДУЛЕМ СЧЕТА | 2000 |

|

RU2179784C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2000 |

|

RU2167493C1 |

| Преобразователь двоичного кода в десятичный | 1979 |

|

SU868747A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР-ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2021 |

|

RU2764876C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР-ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2021 |

|

RU2763988C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Устройство сложения (вычитания) N чисел с настраиваемым модулем | 2016 |

|

RU2637988C1 |

Изобретение предназначено для сложения двоичных чисел с возможностью электронной перестройки модуля сложения и может использоваться в управляемых генераторах импульсов с селекцией опорной фазы. Для получения переменного модуля сложения устройство, содержащее пару обычных сумматоров (1, 4), один из которых складывает слагаемые, а другой корректирует при необходимости результат сложения, дополнено элементом ИЛИ (9), блоком (11) управляемых инверторов и компаратором (7). В устройстве предусмотрена также шина (6) управления модулем, на которую подается двоичное число, равное заданному модулю сложения. Компаратор (7) сравнивает образованную основным сумматором (1) сумму с модулем сложения и в случае, когда указанная сумма равна или больше модуля, вырабатывает сигнал, обеспечивающий вычитание из нее корректирующим сумматором (4) значения модуля и выработку сигнала переноса. Технический результат: расширение функциональных возможностей за счет электронного управления модулем сложения. 1 ил.

Сумматор с переменным модулем сложения, содержащий подключенный к шинам слагаемых первый сумматор и второй сумматор, у которого входы первого слагаемого соединены с выходами первого сумматора, а выходы - с выходной шиной суммы, отличающийся тем, что в него введены элемент ИЛИ, блок управляемых инверторов и компаратор, присоединенный первой группой входов к выходам первого сумматора, а второй группой входов - к входной шине управления модулем сложения и группе информационных входов блока управляемых инверторов, у которого выходы подключены к входам второго слагаемого второго сумматора, при этом входы элемента ИЛИ соединены соответственно с выходом переноса первого сумматора и с выходом компаратора, а его выход - с входом управления блока управляемых инверторов и входом переноса второго сумматора.

| УГРЮМОВ Е.П | |||

| Проектирование элементов и узлов ЭВМ | |||

| - М.: Высшая школа, 1987, с | |||

| Регулятор давления для автоматических тормозов с сжатым воздухом | 1921 |

|

SU195A1 |

| СУММАТОР ПО МОДУЛЮ P | 1992 |

|

RU2032934C1 |

| Устройство для сложения чисел по модулю | 1981 |

|

SU981994A1 |

| US 4187549, 05.08.1980 | |||

| ОВЧИННИКОВ В.В | |||

| и др | |||

| Проектирование быстродействующих микроэлектронных цифровых устройств | |||

| - М.: Советское радио, 1975 , с | |||

| Вагонетка для движения по одной колее в обоих направлениях | 1920 |

|

SU179A1 |

Авторы

Даты

2002-06-10—Публикация

2000-03-24—Подача