Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передач с временным уплотнением.

Известно устройство для цикловой синхронизации [1], содержащее опознаватель циклового синхросигнала, анализатор совпадения синхросигнала, вход устройства, блок выделения тактовой частоты, распределитель импульсов, выход устройства, триггер, первый, второй и третий элементы И, элемент ИЛИ, регистр.

Данное устройство сокращает время вхождения в цикловой синхронизм за счет дополнительного регистра. Но уменьшение времени вхождения в цикловой синхронизм недостаточно при длине цикла в несколько раз больше длины регистра и высоком уровне помех.

Наиболее близким по технической сущности к заявляемому изобретению является выбранная в качестве прототипа система цикловой синхронизации [2], содержащая опознаватель циклового синхросигнала, состоящий из регистра сдвига и схемы совпадения, анализатор совпадения синхросигнала, решающее устройство, блок выделения тактовой частоты, генераторное оборудование (генератор импульсов).

Недостатком данного устройства является невысокая помехоустойчивость при высоком уровне помех, что приводит к большим потерям информации.

Целью изобретения является повышение помехоустойчивости.

Указанная цель достигается тем, что в устройство для цикловой синхронизации, содержащее регистр сдвига, вход которого является входом устройства, схему совпадения, выход которой соединен с анализатором совпадения синхросигнала, анализатор совпадения синхросигнала, вход "T" которого соединен с выходом "T" генератора импульсов, а выход является выходом устройства, решающее устройство, выход которого является вторым выходом устройства, блок выделения тактовой частоты, вход которого соединен со входом устройства, а выход соединен со входом генератора импульсов, генератор импульсов, согласно изобретению введены вторая и третья схемы совпадения, соединенные соответственно со вторым и третьим анализаторами совпадения синхросигнала, второй и третий анализаторы совпадения синхросигнала, входы "T" которых соединены с выходом "T" генератора импульсов, первый, второй и третий элементы НЕ, входы которых соединены соответственно со вторым, первым и третьим анализаторами совпадения синхросигнала, первый элемент И, входы которого соединены с первым анализатором совпадения синхросигнала, вторым, третьим элементами НЕ, а выход и соединен со входом "+1" генератора импульсов, второй элемент И, входы которого соединены с третьим анализатором совпадения синхросигнала, первым, вторым элементами НЕ, а выход соединен со входом второго элемента ИЛИ, первый элемент ИЛИ, входы которого соединены с анализаторами совпадения синхросигнала, а выход с решающим устройством и элементом ИЛИ-НЕ, второй элемент ИЛИ, входы которого соединены с элементом ИЛИ-НЕ и вторым элементом И, а выход соединен со входом "-1" генератора импульсов, элемент ИЛИ-НЕ, входы которого соединены с первым элементом ИЛИ и решающим устройством, а выход со вторым элементом ИЛИ.

В цифровых системах передач с временным уплотнением при высоком уровне помех наиболее часто ошибки происходят в демодуляторе: логической "0" представляется логической "1" и наоборот. При этом в демультиплексорах происходит ошибка в ходе обработки стаффингования - либо при наличии стаффинга ложно определяется, что его нет, либо при его отсутствии ложно определяется, что он есть. В результате, в цифровом потоке нижнего уровня иерархии либо добавляется несуществующий информационный бит, либо убирается существующий. Следовательно, импульс цикловой синхронизации смещается влево или вправо на один бит. Обычное устройство для цикловой синхронизации, в данном случае, выходит из синхронизма, затем заново осуществляет поиск синхросигнала и вход в синхронизм, в результате чего теряется много информационных сигналов. Предлагаемое устройство для цикловой синхронизации в данной ситуации не выходит из синхронизма и, следовательно, не теряет при этом информацию.

Новизна технического решения заключается в наличии в заявляемом устройстве новых схемных элементов: второй и третьей схемы совпадения, второго и третьего анализатора совпадения синхросигнала, первого, второго и третьего элемента НЕ, первого и второго элемента И, первого и второго элемента ИЛИ, элемента ИЛИ-НЕ.

Таким образом изобретение соответствует критерию "новизна".

Анализ известных технических решений в исследуемой и смежной областях позволяет сделать вывод, что введенные функциональные узлы известны. Однако введение их в устройство для цикловой синхронизации с указанными связями придает этому устройству новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют поддерживать синхронизм при ошибках демодуляротора и последующем неправильном стаффинговании и, следовательно, нормальную работу устройства для цикловой синхронизации при высоком уровне помех.

Таким образом, изобретение соответствует критерию "Изобретательский уровень", так как оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано в цифровых системах передач с временным уплотнением.

Таким образом, изобретение соответствует критерию "Промышленная применимость".

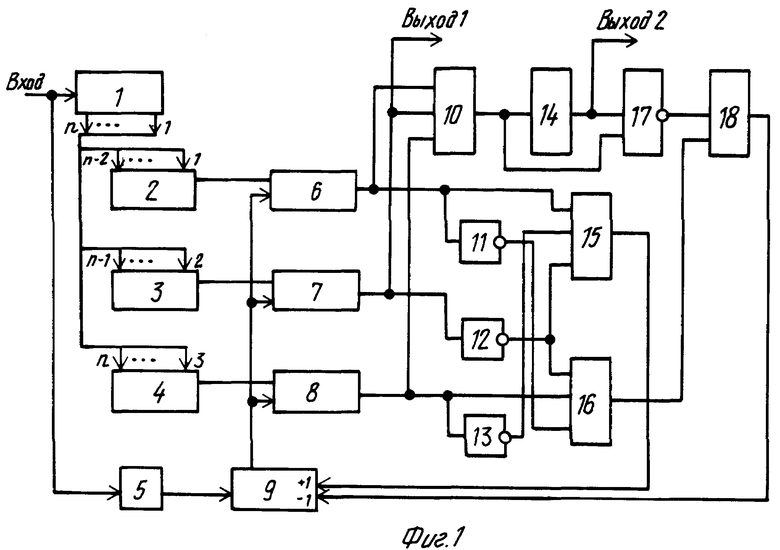

На фиг. 1 изображена структурная электрическая схема устройства для цикловой синхронизации, на фиг. 2 изображена структурная электрическая схема генератора импульсов.

Устройство (фиг. 1) содержит регистр сдвига РС 1, схемы совпадения СС2 2, СС1 3, СС3 4, блок выделения тактовой частоты ВТЧ 5, анализаторы совпадения синхросигнала А2 6, А1 7, А3 8, генератор импульсов ГИ 9, элемент ИЛИ 10, элементы НЕ 11, 12, 13, решающее устройство РУ 14, элементы И 15, 16, элемент ИЛИ-НЕ 17, элемент ИЛИ 18, причем вход регистра сдвига РС 1 соединен со входом устройства, выход регистра сдвига соединен со входом схемы совпадения СС2 2 - с разряда 1 по n-2, со входом СС1 3 - с разряда 2 по n-1, со входом СС3 4 - с разряда 3 по n, выходы схем совпадения соединены соответственно с анализаторами совпадения синхросигнала А2 6, А1 7, А3 8, выход анализатора А2 6 соединен с элементами И 15, ИЛИ 10 и НЕ 11, выход анализатора А1 7 соединен с элементами НЕ 12, ИЛИ 10 и первым выходом устройства, выход анализатора А3 8 соединен с элементами И 16, ИЛИ 10 и НЕ 13, выход элемента НЕ 11 соединен с элементом И 16, выход элемента НЕ 12 соединен с элементами И 15 и И 15, выход элемента НЕ 13 соединен с элементом И 15, выход элемента И 15 соединен со входом "+1" генератора импульсов ГИ 9, выход элемента И 16 соединен с элементом ИЛИ 18, выход элемента ИЛИ 10 соединен с элементом ИЛИ-НЕ 17 и решающим устройством РУ 14, выход решающего устройства РУ 14 соединен со вторым выходом устройства и входом элемента ИЛИ-НЕ 17, выход элемента ИЛИ-НЕ 17 соединен с элементом ИЛИ 18, выход элемента ИЛИ 18 соединен со входом "-1" генератора импульсов ГИ 9, вход блока выделения тактовой частоты ВТЧ 5 соединен со входом устройства, выход соединен со входом "ТЧ" генератора импульсов ГИ 9, выход генератора импульсов ГИ 9 "т" соединен со входами "т" анализаторов А2 6, А1 7, А3 8.

Генератор импульсов (фиг. 2) содержит счетчик Сч 19, дешифратор Дш1 20, дешифратор Дш2 21, дешифратор Дш3 22, элементы И 23, 24, 25, элемент ИЛИ 26, элементы НЕ 27, 28, причем выходы разрядов счетчика Сч 19 соединены со входами дешифраторов Дш1 20, Дш2 21 и Дш3 22, выход дешифратора Дш1 20 соединен со входом элемента И 23, выход дешифратора Дш2 21 соединен со входом элемента И 24, выход дешифратора Дш3 22 соединен со входом элемента И 25, вход генератора импульсов "+1" соединен со входоами элемента НЕ 28 и И 25, вход генератора импульсов "-1" соединен со входами элемента НЕ 27 и И 23, выходы элементов НЕ 27 и НЕ 28 соединены со входами элемента И 24, выходы элементов И 23, 24, 25 соединены со входами элемента ИЛИ 26, выход элемента ИЛИ 26 соединен со входом "Сбр" счетчика Сч 19.

Устройство работает следующим образом.

В режиме поиска синхросигнала схемы совпадения СС2 2, СС1 3 и СС3 4, не обнаруживая синхрокомбинации, выдают логические "0". Соответственно анализаторы совпадения А2 6, А1 7 и А3 8 выдают "0". Элемент ИЛИ 10 вырабатывает на выходе "0", который поступает на элемент ИЛИ-НЕ 17 и решающее устройство РУ 14, которое не находится в состоянии синхронизма. В результате, элемент ИЛИ-НЕ 17 выдает на выходе логическую "1", которая, проходя через элементы ИЛИ 18, поступает на вход "-1" генератора импульсов ГИ 9, вызывая его задержку на один период тактовой частоты. Этот процесс будет повторятьтся до тех пор, пока одна из схем совпадения не обнаружит синхрокомбинацию, которая совпадает с импульсами от ГИ 9.

Очевидно, что обнаружение синхрокомбинации произойдет в схеме совпадения СС3 4, которая соединена с регистром сдвига с разряда 3 по n, и, следовательно, осуществляет проверку сигнала раньше чем СС2 2 и СС1 3.

В результате, при обнаружении синхрокомбинации, анализатор А3 8 выдаст на выход логическую "1", которая поступит на элемент ИЛИ 10, затем на РУ 14 и элемент ИЛИ-НЕ 17. Решающее устройство РУ 14 начнет подсчет количества циклов, в течение которых фиксируется синхронизм, т.е. решение о входе в синхронизм принимается на основании анализа не одного, а нескольких циклов. Элемент И 16 выдаст на выходе "1", так как на выходе анализатора А3 8 логическая "1", а на выходах А1 6 и А2 7 логической "0". Следовательно, на элемент ИЛИ 18 и далее на вход "-1" ГИ 9 поступит логическая "1", которая приведет к задержке ГИ 9 еще на один такт. Эта задержка приведет к тому, что на следующем такте синхронизация будет зафиксирована анализатором А1 7, так как схема совпадения СС1 3 соединена с регистром сдвига с разряда 2 по n-1. Устройство вошло в нормальный режим синхронизации.

В ходе этого режима на выходах элементов И 15, И 16, ИЛИ-НЕ 17, ИЛИ 18 - логические "0". Следовательно, если синхрокомбинация была правильно найдена, то при каждом цикле на выходах перечисленных элементов будут "0" и генератор импульсов ГИ 9 будет работать без задержек.

При наличии помех синхронизация может быть нарушена так, как это описано выше - за счет добавления или удаления информационных битов при неправильном стаффинговании. При этом синхрокомбинация сдвигается влево или вправо на один бит. В результате, когда генератор импульсов выдаст очередной сигнал на анализаторы А2 6, А1 7 и А3 8, синхрокомбинация будет обнаружена не анализатором А1 7, а анализатором А2 6 - если произошел сдвиг вправо, или анализатором А3 8 - если произошел сдвиг влево.

Если произошел сдвиг вправо, то логическая "1" с анализатора А2 6 и соответственно логический "0" с анализаторов А1 7 и А3 8 дадут логическую "1" на выходе элемента ИЛИ 15, которая, поступив на вход "+1" ГИ 9, увеличит на один такт количество тактов генератора до выдачи очередного импульса на анализаторы А1 7, А2 6 и А3 8. В результате данной коррекции очередной импульс генератора ГИ 9 опять совпадает с обнаружением синхрокомбинации схемой совпадения СС1 3 и, таким образом, будет восстановлена нормальная работа устройства без потери синхронизма.

Если произошел сдвиг влево, то логическая "1" с анализатором А3 8 и соответственно логический "0" с анализаторов А2 6 и А1 7 дадут логическую "1" на выходе элемента ИЛИ 16, которая, поступив на вход "-1" ГИ 9, задержит на один такт количество тактов генератора до выдачи очередного импульса на анализаторы А1 7, А2 6 и А3 8. В результате, также, очередной импульс генератора ГИ 9 совпадает с обнаружением синхрокомбинации схемой совпадения СС1 3 и будет продолжена нормальная работа устройства.

Генератор импульсов ГИ 9 работает следующим образом.

Дешифратор Дш2 21 настроен на длину цикла N и когда счетчик Сч 19 досчитает до конца цикла, дешифратор Дш2 21 выдаст на своем выходе сигнал для сброса счетчика. Когда устройство уже находится в состоянии синхронизма, на входах "+1" и "-1" генератора импульсов - "0", в результате элементы НЕ 27, 28 и И 24, 23, 25 работают таким образом, что на вход сброса счетчика Сч 19 поступает сигнал сброса от дешифратора Дш2 21.

При поиске синхросигнала на вход "-1" генератора импульсов подается "1", которая через элементы НЕ 27, 28 и И 23, 24, 25 разрешает сброс счетчика дешифратором Дш1 20, настроенном на длину N-1. Таким образом, расстояние между импульсами от ГИ 9 и синхрокомбинацией уменьшается на один такт, до тех пор, пока устройство не обнаружит синхрокомбинацию и сигнал "1" будет снят со входа "-1" генератора импульсов.

При подаче на вход "+1" генератора импульсов "1", когда необходимо увеличить на единицу количество тактов генератора до выдачи очередного импульса на анализаторы совпадения синхросигнала А2 6, А1 7 и А3 8, элементы НЕ 27, 28 и И 23, 24, 25 разрешают сброс счетчика дешифратором Дш3 22, настроенном на длину N+1. Таким образом, расстояние между импульсами от ГИ 9 и синхрокомбинацией увеличивается на один такт, в результате чего устройство обнаружит синхрокомбинацию и сигнал "1" будет снят со входа "+1" генератора импульсов.

Устройство для цикловой синхронизации по сравнению с прототипом дает повышение помехоустойчивости цифровых систем передач с временным уплотнением, так как обеспечивает надежную работу устройства для цикловой синхронизации, без потери синхронизма, при наиболее часто встречающихся помехах.

Источники информации

1. Патент РФ N 2019046, кл. H 04 L 7/08.

2. Гитлиц М.В., Лев А.Ю. Теоретические основы многоканальной связи. М.: Радио и связь, 1985, с. 159 - 166, рис. 84.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2237374C1 |

| УСТРОЙСТВО ДЛЯ ГРУППОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2248677C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2256295C1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С МОНОКАНАЛОМ | 1991 |

|

RU2032213C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1999 |

|

RU2173027C2 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2224378C1 |

Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровой систем передач с временным уплотнением. Технический результат - повышение помехоустойчивости. За счет введения второй и третьей схем совпадения, второго и третьего анализаторов совпадения синхросигнала, первого, второго и третьего элементов НЕ, первого и второго элементов И, первого и второго элементов ИЛИ, элемента ИЛИ-НЕ в устройстве обеспечивается поддержка синхронизма при ошибках демодулятора и последующем неправильном стаффинговании и, следовательно, нормальную работу устройства при высоком уровне помех. 2 ил.

Устройство для цикловой синхронизации, содержащее регистр сдвига, вход которого является входом устройства, схему совпадения, выход которой соединен с анализатором совпадения синхросигнала, анализатор совпадения синхросигнала, вход "Т" которого соединен с выходом "Т" генератора импульсов, а выход является выходом устройства, решающее устройство, выход которого является вторым выходом устройства, блок выделения тактовой частоты, вход которого соединен с входом устройства, а выход соединен с входом генератора импульсов, генератор импульсов, отличающееся тем, что введены вторая и третья схемы совпадения, соединенные соответственно с вторым и третьем анализаторами совпадения синхросигнала, второй и третий анализаторы совпадения синхросигнала, входы "Т" которых соединены с выходом "Т" генератора импульсов, первый, второй и третий элементы НЕ, входы которых соединены соответственно с вторым, первым и третьим анализаторами совпадения синхросигнала, первый элемент И, входы которого соединены с первым анализатором совпадения синхросигнала, вторым, третьим элементами НЕ, а выход соединен с входом "+1" генератора импульсов, второй элемент И, входы которого соединены с третьим анализатором совпадения синхросигнала, первым, вторым элементами НЕ, а выход соединен с входом второго элемента ИЛИ, первый элемент ИЛИ, входы которого соединены с анализаторами совпадения синхросигнала, а выход с решающим устройством и элементом ИЛИ-НЕ, второй элемент ИЛИ, входы которого соединены с элементом ИЛИ-НЕ и вторым элементом И, а выход соединен с входом "-1" генератора импульсов, элемент ИЛИ-НЕ, входы которого соединены с первым элементом ИЛИ и решающим устройством, а выход - с вторым элементом ИЛИ.

| Гитлиц М.В., Лев А.Ю | |||

| Теоретические основы многоканальной связи | |||

| - М.: Радио и связь, 1985, с.159 - 166, рис.8.4 | |||

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1992 |

|

RU2019046C1 |

| Устройство цикловой синхронизации | 1977 |

|

SU661836A1 |

| US 4517681 A, 14.05.85. | |||

Авторы

Даты

1999-08-27—Публикация

1998-06-11—Подача