Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передачи информации с временным уплотнением.

Известно устройство для цикловой синхронизации [1], содержащее оперативное запоминающее устройство, устройство настройки и диагностики, устройство хранения критериев входа в синхронизм, устройство хранения критериев выхода из синхронизма, дешифратор синхрокомбинации, фазирующее устройство, генераторное оборудование, входы и выходы устройства.

Данное устройство позволяет осуществить синхронизацию одним устройством большого ряда цифровых передач информации.

Однако указанное устройство имеет следующий недостаток. Реализация в нем последовательного поиска синхронизации увеличивает время вхождения в синхронизм.

Основное время при поиске синхронизации определяется временем нахождения первой синхрокомбинации.

Наиболее близким по технической сущности к заявленному изобретению является выбранное в качестве прототипа устройство для цикловой синхронизации [2], содержащее дешифратор, генераторное оборудование, фазирующее устройство, оперативное запоминающее устройство, распределитель, триггер, инверторы, регистр запоминания, кроме того, устройство содержит элементы ИЛИ, И и задающее устройство.

Указанное устройство реализует параллельный поиск синхронизма при распределенной синхрокомбинации.

Недостатком данного устройства является невозможность одним и тем же устройством осуществить синхронизацию различных передач информации с асинхронным объединением цифровых потоков при распределенной синхрокомбинации и реализацией параллельного поиска синхронизма.

Целью изобретения является расширение функциональных возможностей за счет обеспечения одним устройством синхронизации группы передач информации с асинхронным объединением цифровых потоков при рассредоточенной синхрокомбинации группового сигнала и реализацией параллельного поиска синхронизма.

Указанная цель достигается тем, что в устройство для цикловой синхронизации, содержащее первое оперативное запоминающее устройство (ОЗУ), регистр запоминания (РЗ), дешифратор, генераторное оборудование (ГО), фазирующее устройство (ФУ), распределитель, триггер, первый и второй инверторы, причем тактовый вход устройства для цикловой синхронизации (ЦС) соединен с соответствующими входами распределителя и ГО, адресные выходы 1, ..., m и 1, ..., n которого являются соответствующими адресными выходами устройства для ЦС, адресные выходы 1, ..., m ГО также соединены с соответствующими адресными входами первого ОЗУ, входы/выходы 1, ..., N которого соединены с соответствующими входами/выходами РЗ, информационный вход которого является информационным входом устройства для ЦС, а выходы соединены с соответствующими входами дешифратора, выход которого соединен с соответствующими входами ГО и ФУ, выход нулевого состояния которого соединен с соответствующим входом ГО, а выход наличия синхронизации является выходом наличия синхронизации устройства для ЦС, выход генератора импульсов ГО соединен с соответствующим входом распределителя, первый и третий выходы которого соединены соответственно с тактовым входом и входом установки в ноль триггера, а второй выход - с тактовым входом РЗ, вход чтения/записи которого соединен с выходом первого инвертора, информационный вход триггера соединен с шиной питания, выходы первого и второго инверторов соединены соответственно с входами чтения и записи первого ОЗУ, согласно изобретению введены второе и третье ОЗУ, устройство настройки и диагностики (УНД), с третьего по пятый инверторы, с первого по пятый элементы И, первый и второй элементы ИЛИ, причем адресные входы 1, ..., m второго ОЗУ соединены с соответствующими выходами ГО, адресные выходы 1, ..., n которого соединены с соответствующими входами третьего ОЗУ, входы выбора первого, второго и третьего ОЗУ соединены с соответствующими выходами УНД, выходы 3.0, ..., З.М и PO, ..., PN которого соединены с соответствующими входами дешифратора, входы чтения второго и третьего ОЗУ соединены между собой и с выходом четвертого инвертора, входы записи второго и третьего ОЗУ соединены между собой и с выходом пятого инвертора, входы/выходы позиции конца цикла и позиции синхрокомбинации в цикле второго ОЗУ соединены с соответствующими входами/выходами УНД, вход/выход позиции конца сверхцикла которого соединен с соответствующим входом/выходом третьего ОЗУ, вход/выход позиции конца цикла второго ОЗУ соединен также с соответствующими входом ГО и выходом устройства для ЦС, вход/выход позиции синхрокомбинации в цикле второго ОЗУ соединен также с первым входом пятого элемента И, вход/выход позиции конца сверхцикла третьего ОЗУ соединен с соответствующими выходом устройства для ЦС, входом ГО и вторым входом пятого элемента И, третий вход которого соединен с третьим выходом распределителя, четвертый выход которого соединен со вторым входом четвертого элемента И, вход выбора режима устройства для ЦС соединен с соответствующими входами УНД и ГО, входом третьего инвертора и первыми входами второго и четвертого элементов И, выход чтения УНД соединен с входом четвертого инвертора и вторым входом первого элемента И, первый вход которого и первый вход третьего элемента И соединен с выходом третьего инвертора, выход записи УНД соединен с входом пятого инвертора и вторым входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, вторым своим входом соединенного с выходом четвертого элемента И, а выходом - с входом второго инвертора, выход триггера соединен со вторым входом второго элемента И, выход которого соединен со вторым входом первого элемента ИЛИ, первым своим входом соединенного с выходом первого элемента И, а выходом - с входом первого инвертора, выходы тактов настройки и установки в ноль УНД соединены с соответствующими входами ГО, выход пятого элемента И соединен с входом конца синхрокомбинации ФУ, входы нового адреса, установки в нулевое состояние, записи, чтения, настройки ОЗУ или регистров, выбора настраиваемого ОЗУ, информационные входы/выходы настройки устройства для ЦС соединены с соответствующими входами УНД.

Новизна технического решения заключается в применении в заявленном устройстве новых схемных элементов: второго и третьего оперативных запоминающих устройств, устройства настройки и диагностики, с третьего по пятый инверторов, с первого по пятый элементов И, первого и второго элементов ИЛИ.

Таким образом, изобретение соответствует критерию "новизна".

Анализ известных технических решений в исследуемой и смежных областях позволяет сделать вывод о том, что введенные функциональные узлы известны. Однако введение их в устройство для цикловой синхронизации с указанными связями придает этому устройству новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют без значительного увеличения аппаратных затрат расширить его функциональные возможности, обеспечивая одним устройством синхронизацию группы цифровых передач информации при рассредоточенной синхрокомбинации и реализацией параллельного поиска синхронизма.

Таким образом, изобретение соответствует критерию "изобретательский уровень", т.к. оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано в цифровых системах передачи с асинхронным объединением цифровых потоков.

Таким образом, изобретение соответствует критерию "промышленная применимость".

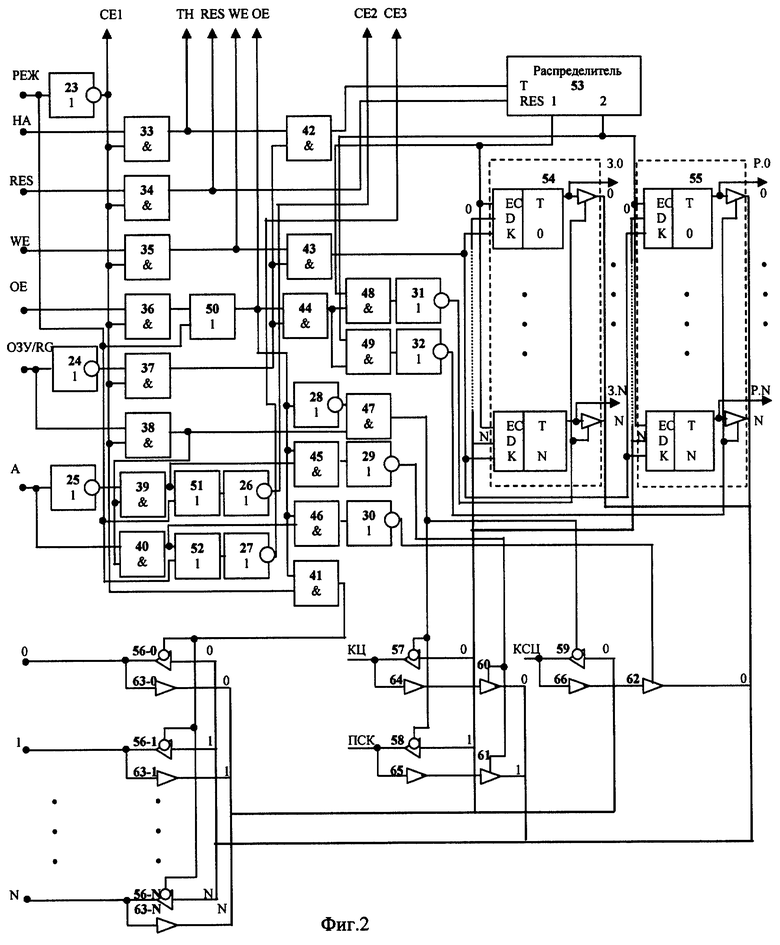

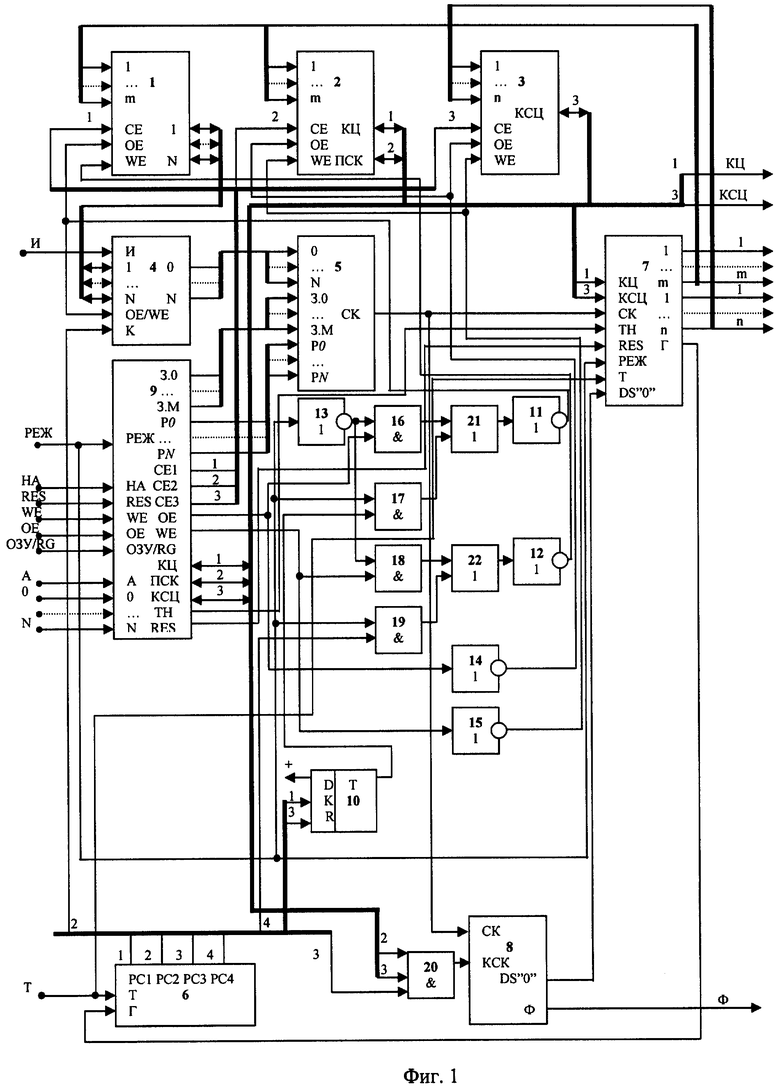

На фиг.1 представлена структурная электрическая схема устройства для цикловой синхронизации, на фиг.2 - электрическая схема устройства настройки и диагностики.

Устройство для цикловой синхронизации (фиг.1) содержит первое оперативное запоминающее устройство (ОЗУ) 1, второе ОЗУ 2, третье ОЗУ 3, регистр запоминания (РЗ) 4, дешифратор 5, распределитель 6, генераторное оборудование (ГО) 7, фазирующее устройство (ФУ) 8,устройство настройки и диагностики (УНД) 9, триггер 10, с первого по пятый инверторы 11, 12, 13, 14, 15, с первого по пятый элементы И 16, 17, 18, 19, 20, первый и второй элементы ИЛИ 21, 22, причем тактовый вход (вход Т) устройства для цикловой синхронизации (ЦС) соединен с соответствующими входами распределителя 6 и ГО 7, адресные выходы 1, ..., m и 1, ..., n которого являются соответствующими адресными выходами устройства для ЦС, адресные выходы 1, ..., m ГО 7 также соединены с соответствующими адресными входами первого ОЗУ 1, входы/выходы 1, ..., N которого соединены с соответствующими входами/выходами РЗ 4, информационный вход (вход И) которого является информационным входом устройства для ЦС, а выходы (выходы 0, ..., N) соединены с соответствующими входами дешифратора 5, выход (выход СК) которого соединен с соответствующими входами ГО 7 и ФУ 8, выход нулевого состояния (выход DS"0") которого соединен с соответствующим входом ГО 7, а выход наличия синхронизации (выход Ф) является выходом наличия синхронизации устройства для ЦС, выход (выход Г) генератора импульсов ГО 7 соединен с соответствующим входом распределителя 6, первый выход (выход РС1) и третий выход (выход РС3) которого соединены соответственно с тактовым входом (вход К) и входом установки в ноль (вход R) триггера 10, а второй выход (выход РС2) - с тактовым входом (вход К) РЗ 4, вход чтения/записи (вход OE/WE) которого соединен с выходом первого инвертора 11, информационный вход (вход D) триггера 10 соединен с шиной питания, выходы первого 11 и второго 12 инверторов соединены соответственно с входами чтения (вход ОЕ) и записи (вход WE) первого ОЗУ 1, адресные входы 1, ..., m второго ОЗУ 2 соединены с соответствующими выходами ГО 7, адресные выходы 1, ..., n которого соединены с соответствующими входами третьего ОЗУ 3, входы выбора (входы СЕ) первого 1, второго 2 и третьего 3 ОЗУ соединены с соответствующими выходами УНД 9, выходы 3.0, ..., З.М и PO, ..., PN которого соединены с соответствующими входами дешифратора 5, входы чтения (входы ОЕ) второго 2 и третьего ОЗУ 3 соединены между собой и с выходом четвертого инвертора 14, входы записи (входы WE) второго 2 и третьего 3 ОЗУ соединены между собой и с выходом пятого инвертора 15, входы/выходы позиции конца цикла (вход/выход КЦ) и позиции синхрокомбинации в цикле (вход/выход ПСК) второго ОЗУ 2 соединены с соответствующими входами/выходами УНД 9, вход/выход позиции конца сверхцикла (вход/выход КСЦ) которого соединен с соответствующим входом/выходом третьего ОЗУ 3, вход/выход позиции конца цикла второго ОЗУ 2 соединен также с соответствующими входом ГО 7 и выходом устройства для ЦС, вход/выход позиции синхрокомбинации в цикле второго ОЗУ 2 соединен также с первым входом пятого элемента И 20, вход/выход позиции конца сверхцикла третьего ОЗУ 3 соединен с соответствующими выходом устройства для ЦС, входом ГО 7 и вторым входом пятого элемента И 20, третий вход которого соединен с выходом РС3 распределителя 6, четвертый выход (выход РС4) которого соединен с вторым входом четвертого элемента И 19, вход выбора режима (вход РЕЖ) устройства для ЦС соединен с соответствующими входами УНД 9 и ГО 7, входом третьего инвертора 13 и первыми входами второго 17 и четвертого 19 элементов И, выход чтения (выход ОЕ) УНД 9 соединен с входом четвертого инвертора 14 и вторым входом первого элемента И 16, первый вход которого и первый вход третьего элемента И 18 соединен с выходом третьего инвертора 13, выход записи (выход WE) УНД 9 соединен с входом пятого инвертора 15 и вторым входом третьего элемента И 18, выход которого соединен с первым входом второго элемента ИЛИ 22, вторым своим входом соединенного с выходом четвертого элемента И 19, а выходом - с входом второго инвертора 12, выход триггера 10 соединен с вторым входом второго элемента И 17, выход которого соединен с вторым входом первого элемента ИЛИ 21, первым своим входом соединенного с выходом первого элемента И 16, а выходом - с входом первого инвертора 11, выходы тактов настройки (выход ТН) и установки в ноль (выход RES) УНД 9 соединены с соответствующими входами ГО 7, выход пятого элемента И 20 соединен с входом конца синхрокомбинации (вход КСК) ФУ 8, входы нового адреса (вход НА), установки в нулевое состояние (вход RES), записи (вход WE), чтения (вход ОЕ), настройки ОЗУ или регистров (вход ОЗУ/RG), выбора настраиваемого ОЗУ (вход А), информационные входы/выходы настройки (входы/выходы 0, ..., N) устройства для ЦС соединены с соответствующими входами УНД 9.

Устройство настройки и диагностики (УНД), представленное на фиг.2, содержит с 23-го по 32-й инверторы, с 33-го по 49-й элементы И, с 50-го по 52-й элементы ИЛИ, распределитель 53, запоминающие устройства 54 и 55, управляемые вентили 56-0, ..., 56-N и с 57-го по 62-й, неуправляемые вентили 63-0, ..., 63-N и с 64-го по 66-й, причем вход РЕЖ УНД 9 соединен с вторыми входами элементов ИЛИ 50, 51, 52 и входом инвертора 23, выход которого соединен с выходом выбора первого ОЗУ (выход СЕ1) УНД 9, со вторыми входами элементов И 33, ..., 38, 41, причем первый вход элемента ИЛИ 50 соединен с выходом элемента И 36, а выходом - с выходом чтения (выход ОЕ) УНД 9, с входом инвертора 28 и с первыми входами элементов И 41, 44, 45, 46, вход НА УНД 9 соединен с первым входом элемента И 33, выход которого является выходом тактов настройки (выход ТН) УНД 9, а также соединен с первым входом элемента И 42, соединенного своим выходом с тактовым входом (вход Т) распределителя 53, вход RES УНД 9 соединен с первым входом элемента И 34, выход которого является выходом установки в ноль (выход RES) УНД 9, а также соединен с входом установки в ноль (вход RES) распределителя 53, вход WE УНД 9 соединен с первым входом элемента И 35, выход которого является выходом записи (выход WE) УНД 9, а также соединен с первым входом элемента И 43, выход которого соединен с тактовыми входами (входы К) триггеров запоминающих устройств 54 и 55, вход ОЕ УНД 9 соединен с первым входом элемента И 36, вход ОЗУ/RG УНД 9 соединен с входом инвертора 24 и первым входом элемента И 38, выход которого соединен со вторыми входами элементов И 39, 40, 47, первый вход элемента И 47 соединен с выходом инвертора 28, а выход - с управляющими входами управляемых вентилей с 57-го по 59-й, выход инвертора 24 соединен с первым входом элемента И 37, выход которого соединен со вторыми входами элементов И 42, 43, 44, вход А УВД 9 соединен с входом инвертора 25 и первым входом элемента И 40, своим выходом соединенного со вторым входом элемента И 46 и первым входом элемента ИЛИ 52, выходом соединенного с входом инвертора 27, выход которого является выходом выбора ОЗУ 3 (выход СЕЗ) УНД 9, информационные входы/выходы (входы/выходы 0, ..., N) настройки УНД 9 соединены с выходами управляемых вентилей 56-0, ..., 56-N и входами неуправляемых вентилей 63-0, ..., 63-N, выходы которых соединены с соответствующими информационными входами (входы Д) триггеров запоминающих устройств 54, 55 и входами управляемых вентилей 57, 58, 59, выход инвертора 25 соединен с первым входом элемента И 39, своим выходом соединенного со вторым входом элемента И 45 и первым входом элемента ИЛИ 51, выходом соединенного с входом инвертора 26, выход которого является выходом выбора ОЗУ 2 (выход СЕ2), выход элемента И 44 соединен со вторьми входами элементов И 48, 49, выходы которых соединены соответственно с входами инверторов 31,32, а выходы последних соединены соответственно с управляющими входами управляемых вентилей запоминающих устройств 54, 55, выход элемента И 41 соединен с управляющими входами управляемых вентилей 56-0, ..., 56-N, выход элемента И 45 соединен с входом инвертора 29, подключенного своим выходом к управляющим входам управляемых вентилей 60,61, выход элемента И 46 соединен с входом инвертора 30, подключенного своим выходом к управляющему входу управляемого вентиля 62, выход 1 распределителя 53 соединен с первым входом элемента И 48 и входами разрешения (входы ЕС) триггеров запоминающего устройства 54, выход 2 распределителя 53 соединен с первым входом элемента И 49 и входами разрешения (входы ЕС) триггеров запоминающего устройства 55, одноименные выходы управляемых вентилей запоминающих устройств 54, 55 и управляемых вентилей 60, 61, 62 соединены между собой и входами управляемых вентилей 56-0, ..., 56-N, вход/выход КЦ УНД 9 соединен с выходом управляемого вентиля 57 и входом неуправляемого вентиля 64, выход которого подключен к входу управляемого вентиля 60, вход/выход ПСК УНД 9 соединен с выходом управляемого вентиля 58 и входом неуправляемого вентиля 65, выход которого подключен к входу управляемого вентиля 61, вход/выход КСЦ УНД 9 соединен с выходом управляемого вентиля 59 и входом неуправляемого вентиля 66, выход которого подключен к входу управляемого вентиля 62, выходы соответствующих триггеров запоминающего устройства 54 соединены с выходами значения синхрокомбинации (выходы З.0, ..., З.N) УНД 9, выходы соответствующих триггеров запоминающего устройства 55 соединены с разрешающими выходами (выходы Р.0, ..., P.N) УНД 9.

Устройство для цикловой синхронизации работает следующим образом. Устройство для цикловой синхронизации (ЦС) имеет два режима работы. Первый - режим настройки и диагностики, второй - режим работы. В первом режиме на входы устройства настройки и диагностики (УНД) 9 поступают сигналы с контроллера, работающего совместно с персональной электронной вычислительной машиной (ПЭВМ). Режим настройки и диагностики разрешается сигналом Лог."0", который поступает на вход выбора режима (вход РЕЖ) ЦС и далее на соответствующий вход УНД 9.

При этом в УНД 9 сигналом с выхода инвертора 23 разрешается работа элементов И 33, ..., 38, 41. Также сигналом с выхода инвертора 23, поступившем через выход СЕ1 УНД 9 на соответствующий вход первого ОЗУ 1, запрещается его работа. Выходы 1, ..., N первого ОЗУ 1 устанавливаются в третье состояние. Настройка второго 2 и третьего 3 ОЗУ разрешается сигналом Лог."1", поступающим с входа ОЗУ/RG устройства для ЦС через соответствующий вход УНД 9 на первый вход элемента И 38, а сигналом Лог."0", поступающим через инвертор 24 на первый вход элемента И 37, разрешается настройка запоминающих устройств 54 и 55. При настройке второго и третьего ОЗУ 2,3 устройства для ЦС, а также запоминающих устройств 54,55 УНД 9 управляемые вентили 56-0, ..., 56-N, 60, 61, 62 УНД 9, а также управляемые вентили запоминающих устройств 54, 55 УНД 9 закрыты сигналами, поступающими на их управляющие входы, а управляемые вентили 57, 58, 59 открыты. При этом выходы закрытых управляемых вентилей находятся в третьем состоянии. При настройке сигнал Лог."0" с входа ОЕ устройства для ЦС поступает на соответствующий вход УНД 9 и далее через элемент И 36, элемент ИЛИ 50 и выход ОЕ УНД 9 - на вход инвертора 14 устройства для ЦС. Сигналом Лог."1", поступающим с выхода инвертора 14 на входы ОЕ второго и третьего ОЗУ 2, 3, последние устанавливаются в режим записи.

Настройка второго ОЗУ 2 разрешается сигналом Лог."0", поступающим с входа А устройства для ЦС через соответствующий вход УНД 9, инвертор 25, элемент И 39, элемент ИЛИ 51, инвертор 26 и выход СЕ2 УНД 9 на вход СЕ второго ОЗУ 2.

Настройка третьего ОЗУ 3 разрешается сигналом Лог."1", поступающим с входа А устройства для ЦС через соответствующий вход УНД 9, элемент И 40, элемент ИЛИ 52, инвертор 27 и выход СЕЗ УНД 9 на вход СЕ третьего ОЗУ 3.

Перед настройкой второго 2 или третьего 3 ОЗУ устройства для ЦС и запоминающих устройств 54,55 УНД 9 с входа RES устройства для ЦС на соответствующий вход УНД 9 и далее на вход элемента И 34 УНД 9 поступает импульсный сигнал положительной полярности. Сигнал с выхода элемента И 34 поступает на вход RES распределителя 53, устанавливая его в нулевое состояние. Также сигнал с выхода элемента И 34 поступает на выход RES УНД 9 и далее на вход RES ГО 7, устанавливая счетчики цикла и сверхцикла последнего в нулевое состояние.

При настройке второго и третьего ОЗУ 2, 3 данные настройки со входов/выходов 0,1 устройства для ЦС через соответствующие входы/выходы 0,1 УНД 9 поступают соответственно на входы неуправляемых вентилей 63-0, 63-1. С выхода неуправляемого вентиля 63-0 данные настройки поступают на вход открытых управляемых вентилей 57 и 59. С выхода неуправляемого вентиля 63-1 данные настройки поступают на вход открытого управляемого вентиля 58. С выходов управляемых вентилей 57, 58 данные настройки через входы/выходы КЦ и ПСК УНД 9 поступают на соответствующие входы/выходы второго ОЗУ 2. С выхода управляемого вентиля 59 данные настройки через вход/выход КСЦ УНД 9 поступают на соответствующий вход/выход третьего ОЗУ3.

После этого по сигналу Лог."1" записи, поступившему с входа WE устройства для ЦС через соответствующий вход УНД 9, элемент И 35, выход WE УНД 9, инвертор 15 устройства для ЦС на входы WE второго 2 и третьего 3 ОЗУ, в настраиваемом ОЗУ по нулевому адресу записываются данные настройки.

Затем по сигналу Лог."1", поступившему с входа НА устройства для ЦС через соответствующий вход УНД 9, элемент И 33 и выход ТН УНД 9 на вход ТН ГО 7, счетчики цикла и сверхцикла последнего изменяют свое состояние на единицу. Далее запись данных по новому адресу в настраиваемых ОЗУ осуществляется так же, как было описано ранее.

После настройки ОЗУ, для определения ее правильности, сигналом установки в нулевое состояние, поступившем на вход RES ГО 7, как было описано ранее, счетчики цикла и сверхцикла последнего устанавливаются в нулевое состояние. Затем на вход чтения ОЕ устройства для ЦС и далее на соответствующий вход УНД 9 поступает сигнал Лог."1". При этом сигнал, поступивший с выхода элемента И 41 на управляющие входы управляемых вентилей 56-0, ..., 56-N, открывает последние. Также открываются управляемые вентили 60 и 61 сигналом, поступающим на их управляющие входы с выхода инвертора 29 при проверке правильности настройки второго ОЗУ 2, или открывается управляемый вентиль 62 сигналом, поступающим на его управляющий вход с выхода инвертора 30 при проверке правильности настройки третьего ОЗУ 3. Управляемые вентили 57, 58, 59 закрываются сигналом, поступающим на их управляющие входы с выхода элемента И 47. Управляемые вентили запоминающих устройств 54, 55 остаются закрытыми. Сигнал чтения также с выхода элемента ИЛИ 50 УНД 9 поступает на его выход ОЕ и далее через инвертор 14 устройства для ЦС - на входы ОЕ второго и третьего ОЗУ 2, 3. При этом сигналы с входов/выходов КЦ и ПСК второго ОЗУ 2 и входа/выхода КСЦ третьего ОЗУ 3 поступают на соответствующие входы/выходы УНД 9.

При проверке правильности настройки второго ОЗУ 2 сигналы с входов/выходов КЦ и ПСК УНД 9 соответственно через неуправляемые вентили 64, 65, управляемые вентили 60, 61, и управляемые вентили 56-0, 56-1 поступают на входы/выходы 0,1 УНД 9 и далее через соответствующие входы/выходы устройства для ЦС - в контроллер ПЭВМ для их сравнения с исходными сигналами. Далее по сигналу НА, как было описано ранее, осуществляется смена адресов ОЗУ 2 и считывание его данных. Результат определения правильности настройки ОЗУ 2 отображается на дисплее ПЭВМ.

При проверке правильности настройки третьего ОЗУ 3 сигналы с входа/выхода КСЦ УНД 9 через неуправляемый вентиль 66, управляемые вентили 62 и 56-0 поступают на вход/выход 0 УНД 9, и далее работа осуществляется так же, как было описано при проверке правильности настройки второго ОЗУ 2.

Настройка запоминающих устройств 54, 55 УНД 9 разрешается сигналом Лог."0", поступающим, как было указано ранее, на вход ОЗУ/RG устройства для ЦС. При этом разрешается работа элементов И 42, 43, 44. Работа управляемых вентилей запоминающих устройств 54, 55 запрещена сигналами, поступающими соответственно с выходов инверторов 31 и 32. Распределитель 53 находится в нулевом состоянии, разрешая сигналом с выхода 1 работу триггеров запоминающего устройства 54. Как было описано ранее, работа управляемых вентилей запрещена. Данные настройки с входов 0, ..., N устройства для ЦС поступают через соответствующие входы УНД 9 и через неуправляемые вентили 63-0, ..., 63-N на информационные входы триггеров запоминающего устройства 54. Далее по сигналу записи, поступившему с входа WE УНД 9 через элементы И 35, 43 на тактовые входы триггеров запоминающего устройства 54, в последних запоминаются данные настройки. Далее по сигналу, поступившему с входа НА УНД 9 через элементы И 33, 42 на тактовый вход распределителя 53, последний изменяет свое состояние, запрещая запись данных настройки в триггеры запоминающего устройства 54 и разрешая запись данных настройки в триггеры запоминающего устройства 55. Запись осуществляется так же, как в запоминающем устройстве 54.

Для проверки правильности настройки запоминающих устройств 54, 55 сигналом с входа RES УНД 9, поступившем через элемент И 34 на вход RES распределителя 53, последний устанавливается в нулевое состояние, разрешая сигналом с выхода 1 работу элемента И 48. Далее по сигналу чтения ОЕ, поступившему на вход ОЕ УНД 9, открываются управляемые вентили запоминающего устройства 54 и управляемые вентили 56-0, ..., 56-N, а управляемые вентили запоминающего устройства 55 и управляемые вентили 57, 58, 59, 60, 61 закрыты. Данные с выходов управляемых вентилей запоминающего устройства 54 поступают на соответствующие входы управляемых вентилей 56-0, ..., 56-N. Далее работа осуществляется так же, как было описано ранее. После чего по сигналу, поступившему на вход НА УНД 9, распределитель 53 меняет свое состояние, разрешая проверку правильности настройки запоминающего устройства 55. Далее работа осуществляется аналогично описанному ранее.

В режиме настройки и диагностики (проверка правильности настройки) на тактовый вход счетчиков цикла и сверхцикла ГО 7 поступают сигналы с выхода ТН УНД 9, а в режиме работы - с выхода Т устройства для ЦС.

Перевод устройства для ЦС в режим работы осуществляется сигналом Лог."1", поступающим на его вход РЕЖ. При этом сигналом Лог."0", поступающим с выходов СЕ1, СЕ2, СЕЗ УНД 9 на СЕ входы первого, второго и третьего ОЗУ 1,2,3, разрешается работа последних, а сигналами Лог."1" и Лог."0", поступающими соответственно с выходов ОЕ и WE УНД 9 через инверторы 14 и 15 на входы ОЕ и WE второго 2 и третьего 3 ОЗУ, последние устанавливаются в режим чтения.

По тактовым сигналам, поступающим с входа Т устройства для ЦС на вход Т ГО 7, счетчик цикла последнего осуществляет подсчет позиции в цикле, а счетчик сверхцикла - количество циклов в цифровой передаче. Количество позиций в цикле задается сигналом, поступающим с выхода КЦ второго ОЗУ 2 на соответствующий вход ГО 7, при поступлении которого счетчик цикла ГО 7 положительным фронтом тактового сигнала устанавливается в нулевое состояние (синхронный сброс). Сигнал КЦ также разрешает работу счетчика сверхцикла, и при поступлении следующего тактового сигнала счетчик сверхцикла изменяет свое состояние. Количество циклов в сверхцикле задается сигналом, поступающим с выхода КСЦ третьего ОЗУ 3 на соответствующий вход ГО 7. При поступлении этого сигнала, а также сигнала с входа КЦ ГО 7, счетчик сверхцикла осуществляет синхронную установку в нулевое состояние. Сигналы с выходов 1, ..., m разрядов счетчика цикла ГО 7 поступают на соответствующие входы разрядов первого 1 и второго 2 ОЗУ, а сигналы с выходов 1, ..., n разрядов счетчика сверхцикла ГО 7 - на входы разрядов третьего ОЗУ 3. Тактовые сигналы, кроме того, поступают на тактовый вход Т распределителя 6, на другой вход Г которого поступают сигналы с выхода генератора импульсов ГО 7. Частота генератора импульсов подобрана таким образом, чтобы за период тактового сигнала, поступившего на тактовый вход распределителя 6, в последнем сформировалась распределенная последовательность сигналов РС1, РС2, РСЗ, РС4. Информационные сигналы с входа И устройства для ЦС поступают на соответствующий вход регистра запоминания (РЗ) 4. Сигналом, поступившем с выхода РС1 распределителя 6 на тактовый вход К триггера 10, последний устанавливается в единичное состояние, т.к. информационный вход Д этого триггера соединен с шиной питания. Сигнал с выхода триггера 10 через открытый сигналом РЕЖ элемент И 17, элемент И 21 и инвертор 11, поступивший на вход ОЕ первого ОЗУ 1 и на вход OE/WE РЗ 4 устанавливает первое ОЗУ 1 в режим чтения, а РЗ 4 - записи. Считанные сигналы, записанные в первом ОЗУ 1 по соответствующему адресу во время предыдущего цикла работы, поступающие с выходов 1, ..., N первого ОЗУ 1 на соответствующие входы РЗ 4, по сигналу с выхода РС2 распределителя 6 запоминаются соответственно в разрядах 1, ..., N последнего, а в нулевом разряде запоминается текущий информационный сигнал, поступающий с информационного входа И устройства для ЦС. Сигналом, поступившим с входа РСЗ распределителя 6 на вход установки в ноль триггера 10, последний устанавливается в нулевое состояние. При этом первое ОЗУ 1 устанавливается в режим записи, а РЗ 4 - в режим чтения. По сигналу, поступившему с выхода РС4 распределителя 6 через открытый сигналом РЕЖ элемент И 19, элемент ИЛИ 22 и инвертор 12 на вход WE первого ОЗУ 1, в последнем запоминаются сигналы, поступившие с разрядов 0, ..., N-1 РЗ 4 соответственно через его 1, ..., N выходы на входы 1, ..., N первого ОЗУ 1. Таким образом, работу первого ОЗУ 1 во взаимодействии с работой РЗ 4 можно представить как работу М сдвигающих регистров, где М равно количеству позиций в цикле, а разрядность каждого регистра равна числу N, где N - количество циклов в сверхцикле.

РЗ 4 имеет двунаправленную группу входов/выходов и однонаправленную группу выходов. Двунаправленные входы/выходы соединяются с входами/выходами первого ОЗУ 1, а однонаправленные выходы - с соответствующими входами дешифратора 5. С выходов разрядов РЗ 4 текущий информационный сигнал и сигналы, считанные из первого ОЗУ 1, поступают на входы 0, ..., N дешифратора 5. На входы З0, ..., ЗМ дешифратора 5 поступают с соответствующих выходов УНД 9 сигналы значения синхрокомбинации. Так как на нулевой позиции цикла могут быть символы как синхрокомбинации, так и служебные символы, а также в связи с отличающимся количеством циклов в сверхцикле для различных видов цифровых передач на входы P0, ..., PN дешифратора 5 с соответствующих выходов УНД 9 поступают сигналы, разрешающие работу разрядов, на которых находятся символы синхрокомбинации. Сигналы с выхода СК дешифратора 5 поступают на соответствующие входы ГО 7 и ФУ 8. До появления на выходе дешифратора 5 сигнала положительного отклика ФУ 8 находится в нулевом состоянии, разрешая сигналом нулевого состояния Лог."1", поступающим с выхода DS"0" ФУ 8 на соответствующий вход ГО 7, установку в первое состояние счетчика цикла и установку в максимальное состояние счетчика сверхцикла, и первым сигналом положительного отклика на выходе дешифратора 5 передним фронтом следующего тактового импульса счетчик цикла устанавливается в первое состояние, а счетчик сверхцикла - в максимальное состояние. Первым сигналом положительного отклика реверсивный счетчик ФУ 8 переводится из нулевого в первое состояние, запрещая сигналом Лог."0" на выходе DS"0" дальнейшую установку счетчиков ГО 7 при сигнале положительного отклика на выходе дешифратора 5. Теперь, при совпадении по времени сигналов положительного отклика и сигнала позиции синхрокомбинации в цикле и сигнала конца сверхцикла, поступивших на первый и второй входы элемента И 20, сигналом с выхода РС3 распределителя 6, поступившем на третий вход элемента И 20, выходным сигналом последнего в реверсивном счетчике ФУ 8 добавляется единица, а при несовпадении - отнимается. Сигнал позиции синхрокомбинации в цикле формируется на выходе ПСК первого ОЗУ 1 при нулевом значении сигналов на его адресных входах.

Когда разность количества положительных и отрицательных откликов достигнет значения входа в синхронизм, устройство для ЦС переходит в режим синхронизма, о чем свидетельствует сигнал Лог."1" на выходе Ф устройства для ЦС. В этом режиме устройство для ЦС находится до тех пор, пока разность количества отрицательных и положительных откликов не достигнет значения критерия выхода из синхронизма. При этом ФУ 8 устанавливается в нулевое состояние, и синхронизатор переходит в режим поиска синхронизма, как было описано ранее.

Для технической реализации устройства для цикловой синхронизации использованы статические запоминающие устройства (ОЗУ) импортного производства типа 7С199 (фирма CYPRESS SEMICONDICTOR) и программируемая пользователем логическая интегральная схема типа ХС 3195 (фирма XILINX).

Предлагаемое изобретение позволяет расширить функциональные возможности за счет обеспечения одним устройством синхронизации класса передач информации с рассредоточенной синхрокомбинацией и реализацией параллельного поиска синхронизма.

Источники информации

1. Патент РФ № 2187210, H 04 L 7/08.

2. Патент РФ № 2190304, Н 04 L 7/08, H 04 J 3/06.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2237374C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2286020C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2224378C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302084C2 |

| УСТРОЙСТВО ДЛЯ ГРУППОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2248677C1 |

| УСТРОЙСТВО ДЛЯ ДЕМУЛЬТИПЛЕКСИРОВАНИЯ | 2005 |

|

RU2296431C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| УСТРОЙСТВО ДЕСКРЕМБЛИРОВАНИЯ | 2006 |

|

RU2310991C2 |

Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передачи информации с временным уплотнением. Технический результат - расширение функциональных возможностей за счет обеспечения одним устройством синхронизации класса передач информации при рассредоточенной синхрокомбинации группового сигнала и реализацией параллельного поиска синхронизма. Устройство для цикловой синхронизации содержит первое, второе и третье оперативные запоминающие устройства, регистр запоминания, дешифратор, распределитель, генераторное оборудование, фазирующее устройство, триггер, первый и второй инверторы, устройство настройки и диагностики, первый, второй и третий инверторы, первый, второй, третий, четвертый и пятый элементы И, первый и второй элементы ИЛИ. 2 ил.

Устройство для цикловой синхронизации, содержащее первое оперативное запоминающее устройство (ОЗУ), регистр запоминания (РЗ), дешифратор, генераторное оборудование (ГО), фазирующее устройство (ФУ), распределитель, триггер, первый и второй инверторы, причем тактовый вход устройства для цикловой синхронизации (ЦС) соединен с соответствующими входами распределителя и ГО, адресные выходы 1, ..., m и 1,..., n которого являются соответствующими адресными выходами устройства для ЦС, адресные выходы 1, ..., m ГО также соединены с соответствующими адресными входами первого ОЗУ, входы/выходы 1, ..., N которого соединены с соответствующими входами/выходами РЗ, информационный вход которого является информационным входом устройства для ЦС, а выходы соединены с соответствующими входами дешифратора, выход которого соединен с соответствующими входами ГО и ФУ, выход нулевого состояния которого соединен с соответствующим входом ГО, а выход наличия синхронизации является выходом наличия синхронизации устройства для ЦС, выход генератора импульсов ГО соединен с соответствующим входом распределителя, первый и третий выходы которого соединены соответственно с тактовым входом и входом установки в ноль триггера, а второй выход - с тактовым входом РЗ, вход чтения/записи которого соединен с выходом первого инвертора, информационный вход триггера соединен с шиной питания, выходы первого и второго инверторов соединены соответственно с входами чтения и записи первого ОЗУ, отличающееся тем, что введены второе и третье ОЗУ, устройство настройки и диагностики (УНД), с третьего по пятый инверторы, с первого по пятый элементы И, первый и второй элементы ИЛИ, причем адресные входы 1, ..., m второго ОЗУ соединены с соответствующими выходами ГО, адресные выходы 1, ..., n которого соединены с соответствующими входами третьего ОЗУ, входы выбора первого, второго и третьего ОЗУ соединены с соответствующими выходами УНД, выходы 3.0, ..., З.М и РО, ..., PN которого соединены с соответствующими входами дешифратора, входы чтения второго и третьего ОЗУ соединены между собой и с выходом четвертого инвертора, входы записи второго и третьего ОЗУ соединены между собой и с выходом пятого инвертора, входы/выходы позиции конца цикла и позиции синхрокомбинации в цикле второго ОЗУ соединены с соответствующими входами/выходами УНД, вход/выход позиции конца сверхцикла которого соединен с соответствующим входом/выходом третьего ОЗУ, вход/выход позиции конца цикла второго ОЗУ соединен также с соответствующими входом ГО и выходом устройства для ЦС, вход/выход позиции синхрокомбинации в цикле второго ОЗУ соединен также с первым входом пятого элемента И, вход/выход позиции конца сверхцикла третьего ОЗУ соединен с соответствующими выходом устройства для ЦС, входом ГО и вторым входом пятого элемента И, третий вход которого соединен с третьим выходом распределителя, четвертый выход которого соединен с вторым входом четвертого элемента И, вход выбора режима устройства для ЦС соединен с соответствующими входами УНД и ГО, входом третьего инвертора и первыми входами второго и четвертого элементов И, выход чтения УНД соединен с входом четвертого инвертора и вторым входом первого элемента И, первый вход которого и первый вход третьего элемента И соединен с выходом третьего инвертора, выход записи УНД соединен с входом пятого инвертора и вторым входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, вторым своим входом соединенного с выходом четвертого элемента И, а выходом - с входом второго инвертора, выход триггера соединен с вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, первым своим входом соединенного с выходом первого элемента И, а выходом - с входом первого инвертора, выходы тактов настройки и установки в ноль УНД соединены с соответствующими входами ГО, выход пятого элемента И соединен с входом конца синхрокомбинации ФУ, входы нового адреса, установки в нулевое состояние, записи, чтения, настройки ОЗУ или регистров, выбора настраиваемого ОЗУ, информационные входы/выходы настройки устройства для ЦС соединены с соответствующими входами УНД.

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1998 |

|

RU2136111C1 |

| Устройство синхронизации цифрового сигнала | 1989 |

|

SU1720161A1 |

| US 4517681, А, 14.05.1985 | |||

| US 4763324, А, 09.08.1988 | |||

| US 4727558, А, 23.02.1988. | |||

Авторы

Даты

2005-07-10—Публикация

2004-01-19—Подача