Настоящее изобретение относится в целом к компьютерным системам, а в частности относится к цифровым подсистемам, которые управляют передачей данных от одной синхронной шины данных к другой синхронной шине данных, причем две шины данных взаимно асинхронны.

Описание существующего уровня техники

Большинство новейших компьютерных систем имеют множество различных шин данных, работающих с разными скоростями передачи данных. В некоторых системах возможно привязать различные скорости передачи данных к одному общему тактовому сигналу, чтобы различные шины данных работали синхронно друг с другом. Однако, во многих системах различные шины данных работают асинхронно по отношению друг к другу. То есть шины управляются различными тактовыми сигналами, причем частоты и фазы различных тактовых сигналов не имеют фиксированных связей. Таким образом, данные в исходной шине могут изменяться в случайные моменты времени по отношению к управляющим сигналам в шине назначения, в которую эти данные передаются. Поскольку необходимо удовлетворять минимальным временам на установку и хранение в цифровых устройствах, таких как регистры, или других устройствах для хранения, следует синхронизировать передачи данных между двумя шинами. Это выполняется схемами синхронизации. Например, исходная шина может вырабатывать сигнал строба данных для указания того, что данные на исходной шине готовы для передачи. Сигнал строба данных в общем случае не может быть использован для прямого управления шиной назначения. Напротив, сигнал строба данных сначала регистрируется в схему управления, связанную с шиной назначения, путем тактирования того сигнала строба данных, который управляет шиной назначения. Зарегистрированный сигнал строба данных затем используется для управления устройствами хранения данных (например, регистрами или триггерами) на шине назначения. Путем синхронизации сигнала строба данных (или другого управляющего сигнала) с шиной назначения, можно быть уверенным, что данные из исходной шины стабильны по отношению к шине назначения и, следовательно, могут передаваться.

Хотя синхронизация сигнала строба данных гарантирует, что передачи данных между двумя взаимно асинхронными шинами проводятся без потери данных, существуют издержки по времени, связанные с синхронизацией. В частности, для достижения синхронизации может потребоваться два тактовых периода шины назначения. Для случайных передач данных издержками на синхронизацию можно легко пренебречь; однако, когда многочисленными передачами (например, пакетными передачами) передаются большие объемы данных, кумулятивные издержки могут значительно уменьшить общую производительность компьютерной системы. Таким образом, существует необходимость в уменьшении издержек на синхронизацию для передачи пакетов данных между двумя взаимно асинхронными шинами.

Раскрытие изобретения

Одним аспектом настоящего изобретения является схема интерфейса между первой и второй шинами, которые работают асинхронно по отношению друг к другу. Первая шина снабжает данными схему интерфейса синхронно с тактовым сигналом первой шины, а вторая шина принимает данные от схемы интерфейса синхронно с тактовым сигналом второй шины. Устройство включает в себя буфер ввода/вывода, содержащий по меньшей мере первую и вторую буферные ячейки, в которых данные из первой шины записываются синхронно с тактовым сигналом первой шины. По меньшей мере первый и второй индикаторы достоверности данных связаны соответственно с первой и второй буферными ячейками. Первый индикатор достоверности данных установлен синхронно с тактовым сигналом первой шины, когда данные хранятся в первой буферной ячейке. Второй индикатор достоверности данных установлен синхронно с тактовым сигналом второй шины, когда данные хранятся во второй буферной ячейке. Селектор индикаторов достоверности данных выбирает один из первого и второго индикаторов достоверности данных в качестве индикатора достоверности выходных данных. Конечный автомат шины работает синхронно с тактовым сигналом второй шины для передачи данных от буфера ввода/вывода на вторую шину. Конечный автомат шины выбирает одну из первой и второй буферных ячеек в качестве источника данных для передачи на вторую шину. Конечный автомат шины управляет селектором индикаторов достоверности данных для выбора соответствующего одного из первого и второго индикаторов достоверности данных в качестве индикатора достоверности выходных данных. Конечный автомат шины наблюдает за индикатором достоверности выходных данных, чтобы определить, когда данные из первой шины хранятся в выбранной первой или второй буферной ячейке. Первая схема синхронизации принимает первый индикатор достоверности данных и синхронизирует его с тактовым сигналом второй шины, чтобы сделать первый синхронизированный индикатор достоверности данных входным для селектора индикаторов достоверности данных. Вторая схема синхронизации принимает второй индикатор достоверности данных и синхронизирует его с тактовым сигналом второй шины, чтобы сделать второй синхронизированный индикатор достоверности данных входным для селектора индикаторов достоверности данных.

Другим аспектом настоящего изобретения является устройство для передачи данных между первой и второй шинами, которые работают асинхронно по отношению друг к другу. Устройство содержит блок хранения данных, который содержит множество ячеек хранения данных, которые хранят данные. Конечный автомат интерфейса первой шины подключен к первой шине данных. Конечный автомат интерфейса первой шины передает данные от первой шины данных в выбранную одну из множества ячеек хранения данных. Конечный автомат интерфейса второй шины подключен ко второй шине данных. Конечный автомат интерфейса второй шины передает данные от выбранной одной из множества ячеек хранения данных на вторую шину данных. Имеется буфер наличия данных, который имеет соответствующий индикатор для каждой из множества ячеек хранения данных. Один из индикаторов устанавливается в ответ на передачу данных конечным автоматом первой шины в выбранную одну из множества ячеек хранения и очищается в ответ на передачу данных конечным автоматом второй шины из выбранной одной из множества ячеек хранения данных на вторую шину данных. Конечный автомат интерфейса второй шины передает данные из выбранной одной из множества ячеек хранения данных, только когда установлен выбранный индикатор. Набор соответствующих схем задержки подключен между буфером наличия данных и конечным автоматом интерфейса второй шины для задержки индикаторов так, что конечный автомат интерфейса второй шины не может передавать данные из выбранной одной из множества ячеек хранения данных, пока не пройдет по меньшей мере заранее заданное время после того, как конечный автомат интерфейса первой шины передал данные в выбранную ячейку хранения данных.

Еще одним аспектом настоящего изобретения является устройство для передачи данных между первой шиной данных и второй шиной данных. Первая и вторая шины данных работают асинхронно по отношению друг к другу. Устройство содержит буфер, который включает в себя первую и вторую ячейки хранения данных, которые хранят данные. Конечный автомат интерфейса первой шины подключен к первой шине данных и буферу для управления передачами данных от первой шины данных в выбранную одну из первой и второй ячеек хранения данных в соответствии с тактовым сигналом первой шины. Конечный автомат интерфейса второй шины подключен ко второй шине данных и к буферу для управления передачами данных от буфера во вторую шину данных в соответствии с тактовым сигналом второй шины, работающим асинхронно по отношению к тактовому сигналу первой шины. Первый и второй флаговые буферы имеют соответствующие первый и второй флаговые выходы, соединенные с обоими конечными автоматами интерфейсов первой и второй шин. Выход первого флагового буфера устанавливается синхронно по отношению к тактовому сигналу первой шины, когда данные передаются в первую ячейку хранения данных от первой шины данных, и очищается синхронно по отношению к тактовому сигналу второй шины, когда данные передаются из первой ячейки хранения данных на вторую шину данных. Выход второго флагового буфера устанавливается синхронно по отношению к тактовому сигналу первой шины, когда данные передаются во вторую ячейку хранения данных от первой шины данных, и очищается синхронно по отношению к тактовому сигналу второй шины, когда данные передаются из второй ячейки хранения данных на вторую шину данных. Первый синхронизатор включен между первым флаговым буфером и конечным автоматом интерфейса второй шины. Второй синхронизатор включен между вторым флаговым буфером и конечным автоматом интерфейса второй шины. Первый синхронизатор синхронизирует первый флаговый выход с тактовым сигналом второй шины так, что первый флаговый выход задерживается по меньшей мере на заранее заданное время перед тем, как первый флаговый выход может быть принят конечным автоматом интерфейса второй шины после того, как первый флаговый выход изменен. Второй синхронизатор синхронизирует второй флаговый выход с тактовым сигналом второй шины так, что второй флаговый выход задерживается по меньшей мере на заранее заданное время перед тем, как второй флаговый выход может быть принят конечным автоматом интерфейса второй шины после того, как второй флаговый выход изменен.

Краткое описание чертежей

Настоящее изобретение будет описано ниже со ссылками на приложенные чертежи, на которых:

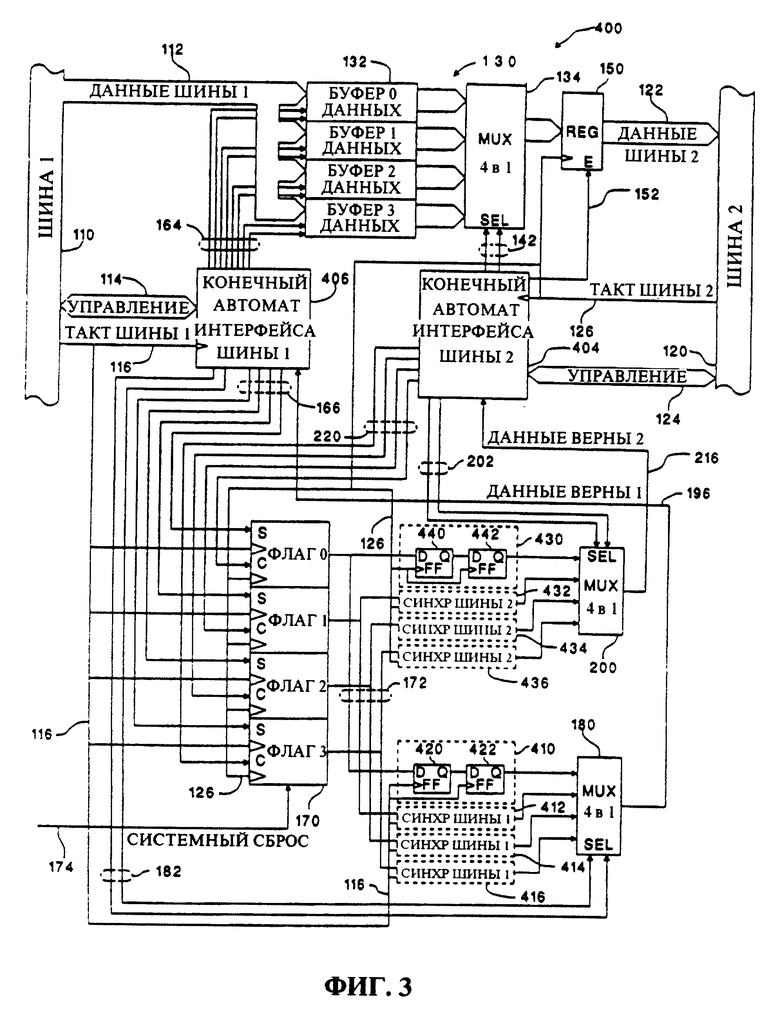

Фиг. 1 иллюстрирует примерный интерфейс между двумя асинхронными шинами.

Фиг. 2 показывает предпочтительное выполнение флагового буфера достоверности данных для использования в интерфейсе по фиг. 1.

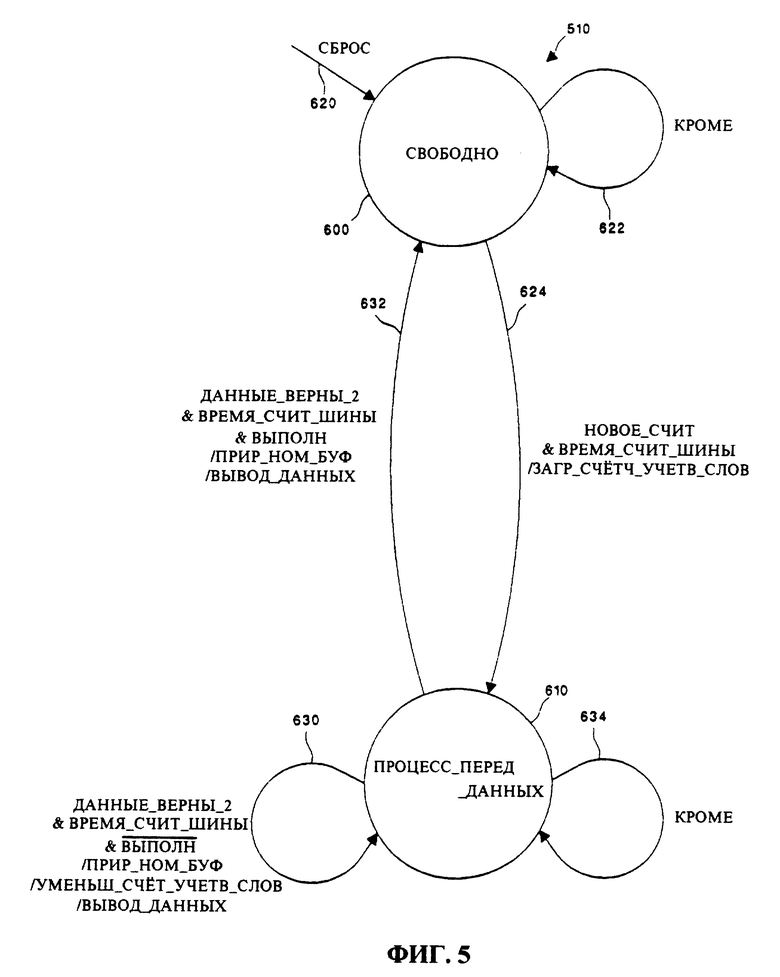

Фиг. 3 иллюстрирует примерный интерфейс между двумя асинхронными шинами по фиг. 1, причем интерфейс включает улучшенную схему синхронизации по настоящему изобретению.

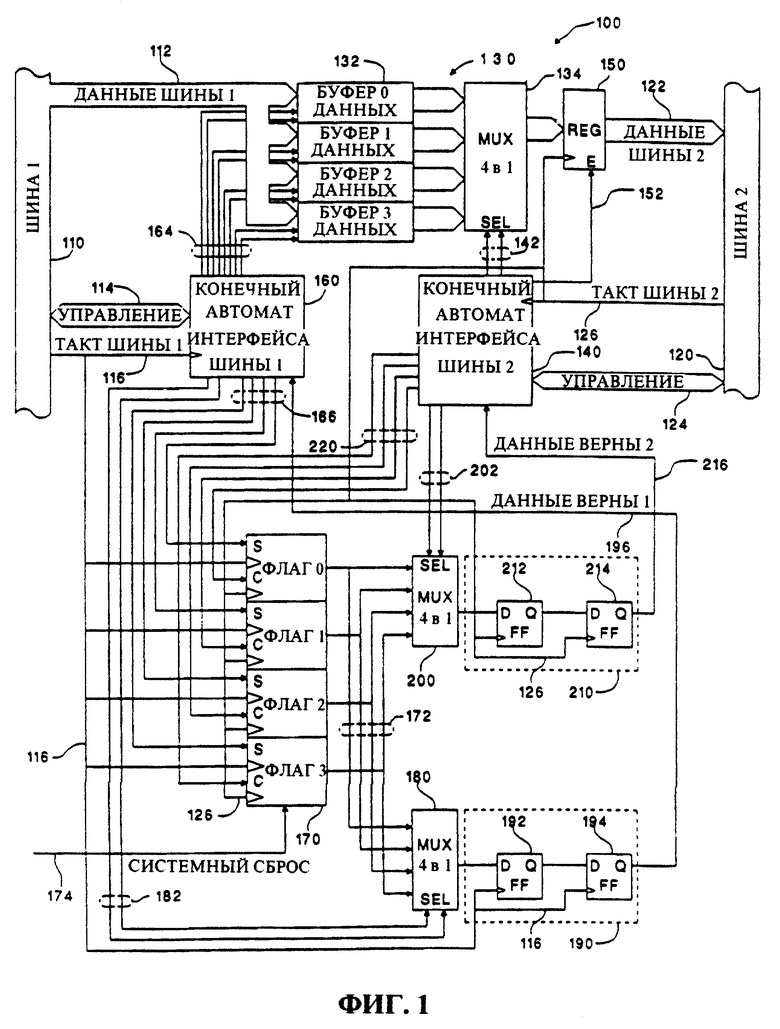

Фиг. 4 иллюстрирует примерную диаграмму состояний для существенной части конечного автомата интерфейса шины 2 по фиг. 1.

Фиг. 5 иллюстрирует примерную диаграмму состояний для существенной части конечного автомата интерфейса шины 2 по фиг. 3.

Подробное описание предпочтительного выполнения

Фиг. 1 иллюстрирует примерный интерфейс 100 между взаимно асинхронными шинами в соответствии с известными системами. Как показано на фиг. 1, интерфейс подключен к первой шине (ШИНА 1) 110. В описанном здесь выполнении первая шина 110 предпочтительно является шиной МПК (межсоединение периферийных компонент), которая работает в соответствии со стандартом, установленным для шин МПК для использования в основанных на микропроцессорах компьютерах, таких как компьютеры, основанные на семье микропроцессоров INTEL® (например, INTEL 80486, INTEL Pentium, Intel P6 и т.п.). Как правило, первая шина 110 является 32-разрядной шиной данных со множеством линий данных (показаны как ДАННЫЕ ШИНЫ 1, поз. 112), которые передают данные по первой шине 110, множество адресных линий (не показаны), которые обеспечивают адрес источника или адрес места назначения для данных, передаваемых по первой шине 110, и множество управляющих линий (показаны как УПРАВЛЕНИЕ, поз. 114), которые передают управляющие сигналы, которые управляют передачей данных по первой шине 110. Первая шина 110 включает в себя также тактовую линию 116 первой шины (ТАКТ ШИНЫ 1) с тактовым сигналом на ней, который синхронизирует сигналы адреса, данных и управления на первой шине 110. Например, тактовый сигнал в линии 116 ТАКТ ШИНЫ 1 преимущественно работает на частоте 33 МГц. Работа первой шины 110 хорошо известна специалистам и не будет здесь описываться подробно. Первая шина 110 также подключена к другим компонентам (не показаны) в компьютерной системе, таким как, например, контроллер периферии, который может быть источником данных для первой шины 110.

Интерфейс также подключен ко второй шине 120, которая в описываемом ниже выполнении предпочтительно является шиной высокоскоростного процессора, как, например, шина Р6. В предпочтительном выполнении вторая шина 120 является 64- разрядной шиной, предназначенной для связи с микропроцессором INTEL Р6, и работает асинхронно по отношению к первой шине 110. Например, вторая шина 120 может преимущественно работать на частоте 50 МГц, 60 МГц или на другой частоте в соответствии с тактовой частотой микропроцессора Р6, соединенного со второй шиной 120. Несмотря на описанное здесь в отношении второй шины 120, могут использоваться и другие процессорные шины, которые работают асинхронно по отношению к первой шине 110. Конкретные характеристики второй шины 120 не имеют значения для настоящего изобретения за исключением того, что передачи данных по второй шине 120 происходят асинхронно по отношению к передачам данных по первой шине 110. Вторая шина 120 также включает в себя множество линий 122 данных, множество адресных линий (не показаны), множество управляющих линий 124 и тактовую линию 125 ТАКТ ШИНЫ 2.

Из-за асинхронного соотношения между первой шиной 110 и второй шиной 120 интерфейс 100 далее включает в себя буфер 130 данных, который принимает данные от первой шины 110 по линиям 112 данных и под управлением управляющих сигналов первой шины на линии 114 и тактового сигнала в линии 116 ТАКТ ШИНЫ 1. Буфер 130 данных буферизует данные и снабжает буферизованными данными вторую шину 120 под управлением управляющих сигналов на управляющих линиях 124 от второй шины 120 и синхронно с тактовым сигналом в линии 126 ТАКТ ШИНЫ 2.

Буфер 130 данных содержит множество ячеек 132 хранения. В выполнении по фиг. 1 показаны только 4 ячейки 132 хранения, обозначенные как БУФЕР 0 ДАННЫХ, БУФЕР 1 ДАННЫХ, БУФЕР 2 ДАННЫХ и БУФЕР 3 ДАННЫХ. Из последующего описания должно быть понятно, что для обеспечения дополнительного хранения данных между двумя шинами могут быть включены дополнительные ячейки. Например, в одном особенно предпочтительном выполнении включено восемь ячеек хранения. Изобретение может быть легко понято, когда показано четыре ячейки хранения. Каждая из ячеек 132 хранения хранит 64 сигнала данных. Входы ячеек 132 хранения совместно подключены к линиям 112 ДАННЫЕ ШИНЫ 1. Выходы ячеек 132 хранения представляют собой входы для 64-разрядного мультиплексора 134 (MUX) 4 в 1. Опять-таки, когда имеются дополнительные ячейки хранения (например, восемь), мультиплексор 134 расширяется, чтобы обеспечить соответственно дополнительные наборы входов (например, в таком выполнении мультиплексор 134 будет мультиплексором 8 в 1). Мультиплексор 134 управляется конечным автоматом 140 интерфейса шины 2 через пару линий 142 выбора. В частности, конечный автомат интерфейса поддерживает выходной указатель, который указывает на следующую более высокую по номеру ячейку хранения после ячейки хранения, из которой были переданы предыдущие данные на вторую шину 120. Должно быть понятно, что выходной указатель является выходным указателем по модулю 4, который считает 0, 1, 2, 3, 0, так что выходной указатель показывает на ячейку хранения БУФЕР 0 ДАННЫХ, следующую за ячейкой хранения БУФЕР 3 ДАННЫХ.

В ответ на значение выходного указателя на линиях 142 выбора мультиплексор 134 выбирает данные из одной из четырех ячеек 132 хранения как из источника выходных данных для связи со второй шиной 120, предполагая, что данные в выбранной ячейке хранения достоверны, что будет обсуждено ниже. Выбранные данные регистрируются 64-разрядным регистром 150, который тактируется сигналом ТАКТ ШИНЫ 2 на линии 126 так, что данные синхронизируются со второй шиной 120. Регистр 150 далее управляется сигналом на входе разрешения по линии 152 разрешения. Когда линия 152 разрешения неактивна, выходы данных регистра 150 неактивны независимо от данных, зарегистрированных в регистре 150. Когда линия 152 разрешения активна, регистр 150 выдает зарегистрированные данные на вторую шину 120 через множество линий 122 ДАННЫЕ ШИНЫ 2. Линия 152 разрешения управляется конечным автоматом 140 интерфейса шины 2, чтобы дать разрешение регистру 150 только тогда, когда выбран интерфейс 100 для передачи данных на вторую шину 120.

Данные из первой шины 110 запоминаются в буфере 130 данных под управлением конечного автомата 160 интерфейса шины 1. Конечный автомат 160 интерфейса шины 1 принимает управляющие сигналы и сигнал ТАКТ ШИНЫ 1 от первой шины 110 через управляющие линии 114 и линию 116 ТАКТ ШИНЫ 1. Конечный автомат 160 интерфейса шины 1 реагирует на управляющий сигнал готовности данных, передаваемый управляющими линиями 114 для выработки строба выбранных данных в ячейки 132 хранения данных через одну из восьми линий 164 строба данных. (В предпочтительном выполнении предусмотрены две линии строба данных для каждой ячейки 132 хранения данных, чтобы стробировать 32 разряда данных из первой шины 110 в соответствующие верхнюю и нижнюю части каждой ячейки 132 хранения данных. ) Линии 164 строба данных работают как тактовые для ячеек 132 хранения данных, так что данные на линиях 112 ДАННЫЕ ШИНЫ 1 запоминаются в выбранной одной из ячеек 132 хранения данных, соответствующей одной активной линии из линий 164 строба данных. Конечный автомат 160 интерфейса шины 1 работает обычным образом для управления буфером 130 данных как циклическим буфером FIFO обратного магазинного типа (first in/first out - первый вошел/первый вышел). Таким образом, конечный автомат 160 интерфейса шины 1 поддерживает входной указатель на текущей ячейке из входных ячеек 132, которая является следующей доступной пустой ячейкой хранения в буфере 130 данных. Когда данные записаны в выбранную ячейку 132 хранения, входной указатель увеличивается до следующего ближайшего большего числа. Входной указатель является указателем по модулю 4 (в предпочтительном выполнении с четырьмя ячейками хранения), так что, когда входной указатель увеличивается от значения 3, оно меняется на 0. Поэтому буфер 130 данных может считаться "циклическим" буфером с ячейкой хранения БУФЕР 0 ДАННЫХ, следующей за ячейкой хранения БУФЕР 3 ДАННЫХ.

Конечный автомат 160 интерфейса шины 1 выдает множество сигналов установки флагов на набор линий 166, которые предусмотрены как входы для соответствующих установочных входов (S) флагового буфера 170, который содержит множество (например, четыре) флаговых буферных ячейки достоверности данных. Как описано подробнее ниже в связи с фиг. 2, сигналы установки флагов синхронизируются сигналом ТАКТ ШИНЫ 1 в сигнальных линиях 166, которые предусмотрены как соответствующие первые тактовые входы для каждой из ячеек хранения флагов во флаговом буфере 170. Флаговый буфер 170 хранит четыре флага достоверных данных (ФЛАГ0, ФЛАГ1, ФЛАГ2 и ФЛАГ3), причем один флаг достоверных данных соответствует каждой из буферных ячеек 132 (БУФЕР 0 ДАННЫХ ... БУФЕР 3 ДАННЫХ) в буфере 130 данных. Неактивный флаг достоверности данных показывает, что соответствующая буферная ячейка 132 пуста и что данные могут запоминаться в буферной ячейке 132. Активный флаг достоверности данных показывает, что соответствующая буферная ячейка 132 имеет хранящиеся в ней достоверные данные, и что другие данные не могут запоминаться в этой буферной ячейке. Активный флаг достоверности данных также показывает конечному автомату интерфейса шины 2 (обсуждается ниже), что данные в соответствующей буферной ячейке готовы к передаче на вторую шину 120. Флаг достоверности данных устанавливается, когда данные запоминаются в соответствующей буферной ячейке данных. Флаг достоверности данных очищается, когда данные передаются из соответствующей буферной ячейки данных на вторую шину 120.

Флаги достоверных данных во флаговом буфере 170 подаются через набор линий 172 флагов достоверных данных в качестве входов первого флагового мультиплексора 180 (MUX) 4 в 1. Первый флаговый мультиплексор 180 управляется парой линий 182 выбора шины 1 от конечного автомата 160 интерфейса шины 1. Конечный автомат 160 интерфейса шины 1 управляет парой линий 182 выбора шины 1 для кодирования текущего значения входного указателя. Таким образом, первый флаговый мультиплексор 180 выбирает флаг достоверности данных, соответствующий ячейке хранения данных, на которую в текущий момент указывает входной указатель, так что выход мультиплексора 180 является флагом достоверности данных, который показывает, достоверны ли уже данные в текущей входной ячейке. То есть выбранный флаг достоверности данных показывает, что либо данные, хранившиеся до этого в выбранной ячейке буфера данных, уже переданы на вторую шину 120 (флаг достоверности данных будет "недостоверно"), либо что данные, хранившиеся до этого в выбранной ячейке буфера данных, не переданы еще на вторую шину 120 (флаг достоверности данных будет "достоверно").

Флаги достоверности данных во флаговом буфере 170 пригодны для переустановки в известное состояние (например, все флаги достоверности данных неактивны) через сигнал СИСТЕМНЫЙ СБРОС на линии 174. Сигнал СИСТЕМНЫЙ СБРОС является обычным сигналом перезагрузки, который вырабатывается, когда включается питание компьютерной системы, когда компьютерная система перезагружается пользователем и т.д.

Выход первого флагового мультиплексора 180 подан в качестве входа данных на синхронизатор 190 достоверных данных шины 1, содержащий первый триггер (FF) 192 синхронизатора шины 1. Выход данных первого триггера 192 синхронизатора шины 1 подан в качестве входа данных на второй триггер 194 синхронизатора шины 1. Два триггера 192, 194 синхронизатора шины 1 тактируются сигналом ТАКТ ШИНЫ 1 на тактовой линии 116. Выход данных второго триггера 194 синхронизатора шины 1 подан в качестве входа на конечный автомат 160 интерфейса шины 1 через линию 196 данных ДАННЫЕ ВЕРНЫ 1. Таким образом, выбранный флаг достоверности подан как обратная связь на конечный автомат интерфейса шины 1 для указания того, доступна ли ячейка хранения данных, выбранная в текущий момент входным указателем, для запоминания новых данных, либо того, что новые данные не могут быть приняты. Должно быть понятно, что могут быть использованы и другие типы синхронизаторов данных.

Флаги достоверных данных во флаговом буфере 170 поданы через набор линий 172 флагов достоверных данных в качестве входов на второй флаговый мультиплексор 200 (MUX) 4 в 1. Второй флаговый мультиплексор 200 управляется парой линий 202 выбора шины 2 от конечного автомата 140 интерфейса шины 2. Линии 202 выбора шины 2 управляются для соответствия линиям 142 выходного указателя, которые выбирают ячейку 132 хранения данных в буфере 130 данных как источник данных для вывода на вторую шину 120. Таким образом, выход второго флагового мультиплексора 200 показывает, имеет ли выбранная в настоящий момент ячейка хранения данных достоверные данные, или данные в этой ячейке уже были переданы и более не являются достоверными.

Выход второго флагового мультиплексора 200 подан в качестве входа данных на синхронизатор 210 достоверных данных шины 2, содержащий первый триггер (FF) 212 синхронизатора шины 2. Выход данных первого триггера 212 синхронизатора шины 2 подан в качестве входа данных на второй триггер 214 синхронизатора шины 2. Два триггера 212, 214 синхронизатора шины 2 тактируются сигналом ТАКТ ШИНЫ 2 на тактовой линии 126. Выход данных второго триггера 214 синхронизатора шины 2 подан в качестве входа на конечный автомат 140 интерфейса шины 2 через линию 216 данных ДАННЫЕ ВЕРНЫ 2. Таким образом, конечный автомат 140 интерфейса шины 2 снабжен обратной связью, относящейся к достоверности данных в той ячейке хранения данных, на которую в текущий момент указывает выходной указатель.

Буферные ячейки достоверности данных (т.е. ФЛАГ0, ФЛАГ1, ФЛАГ2 и ФЛАГ3) во флаговом буфере 170 выборочно очищаются сигналами четырех линий 220 очистки флагов, которые вырабатываются конечным автоматом 140 интерфейса шины 2. Каждая из линий 220 очистки флагов подана в качестве соответствующего флагового очищающего входа (С) на одну из буферных ячеек достоверности данных синхронно с сигналом ТАКТ ШИНЫ 2 на сигнальной линии 126. Соответствующая линия очистки флага активируется, когда данные из соответствующей ячейки хранения в буфере 130 данных передаются на вторую шину 120. Например, когда конечный автомат 140 интерфейса шины 2 выбирает данные в ячейке БУФЕР 2 ДАННЫХ хранения в буфере 130 данных в качестве выходных данных на вторую шину 120, конечный автомат 140 интерфейса шины 2 активирует соответствующую одну из линий 220 очистки флага, поданную в качестве очищающего (С) входа на буферную ячейку достоверности данных. Буферная ячейка ФЛАГ2 достоверности данных очищается синхронно с сигналом ТАКТ ШИНЫ 2 на сигнальной линии 126.

Фиг. 2 показывает предпочтительное выполнение одной из ячеек 170 хранения достоверности данных по фиг. 1. В частности, фиг. 2 показывает ячейку 170А хранения достоверности данных ФЛАГ0. Остальные три ячейки хранения достоверности данных для ФЛАГ1, ФЛАГ2 и ФЛАГ3 предпочтительно идентичны ячейке хранения достоверности данных ФЛАГ0. Как показано, ячейка 170 хранения достоверности данных содержит первый переключающий триггер 300 и второй переключающий триггер 302.

Первый переключающий триггер 300 имеет тактовый вход 310, который принимает сигнал ТАКТ ШИНЫ 1 по сигнальной линии 116. Первый переключающий триггер 300 имеет вход 312 разрешения на переключение (ТЕ), который принимает выход от первого элемента 314 И с двумя входами. Первый элемент 314 И имеет первый, возбуждаемый высоким уровнем сигнала, вход, который принимает сигнал УСТ_ДОСТ_0 (установки достоверности) по сигнальной линии 166А (одна из набора флаговых линий 166 достоверности данных по фиг. 1) от конечного автомата 160 интерфейса шины 1. Первый элемент 314 И имеет второй, возбуждаемый низким уровнем сигнала, вход, который принимает флаг ФЛАГ0 достоверности данных в качестве обратной связи по сигнальной линии 172А (которая является одной из сигнальных линий 172 по фиг. 1). Первый переключающий триггер 300 имеет выходной сигнал 316 Q, который меняет состояние (т.е. от низкого логического уровня к высокому логическому уровню, или от высокого логического уровня к низкому логическому уровню) при переходе от низкого уровня к высокому для сигнала ТАКТ ШИНЫ 1 в предпочтительном выполнении. Выходной сигнал Q первого переключающего триггера 300 изменяется только тогда, когда сигнал УСТ_ДОСТ_0 в сигнальной линии 166А активен одновременно с тем, что флаг ФЛАГ0 достоверности данных неактивен. Когда сигнал УСТ_ДОСТ_0 активен, а флаг ФЛАГ0 достоверности данных неактивен, выходной сигнал элемента 314 И активен и выходной сигнал Q первого переключающего триггера 300 будет изменяться от его высокого состояния до его низкого состояния или от его низкого состояния до его высокого состояния один раз для каждого перехода от низкого уровня к высокому для сигнала ТАКТ ШИНЫ 1. Если сигнал УСТ_ДОСТ_0 неактивен или флаг ФЛАГ0 достоверности данных активен, выходной сигнал Q первого переключающего триггера 300 не будет изменяться независимо от изменений сигнала ТАКТ ШИНЫ 1.

Второй переключающий триггер 302 имеет тактовый вход 330, который принимает сигнал ТАКТ ШИНЫ 2 по сигнальной линии 126. Второй переключающий триггер 302 имеет вход 332 разрешения на переключение (ТЕ), который принимает выход от второго элемента 334 И с двумя входами. Второй элемент 334 И имеет первый, возбуждаемый высоким уровнем сигнала, вход, который принимает сигнал ОЧ_ДОСТ_0 (очистка достоверности) по сигнальной линии 220А (одна из флаговых линий 220 очистки достоверности данных по фиг. 1) от конечного автомата 140 интерфейса шины 2. Второй элемент 334 И имеет второй, возбуждаемый высоким уровнем сигнала, вход, который принимает флаг ФЛАГ0 достоверности данных как обратную связь по сигнальной линии 172А. Второй переключающий триггер 302 имеет выходной сигнал 336 Q, который меняет состояние (т.е. от низкого логического уровня к высокому логическому уровню, или от высокого логического уровня к низкому логическому уровню) при переходе от низкого уровня к высокому для сигнала ТАКТ ШИНЫ 2 в предпочтительном выполнении. Выходной сигнал Q первого переключающего триггера 302 изменяется только тогда, когда сигнал ОЧ_ ДОСТ_ 0 в сигнальной линии 220А активен одновременно с тем, что флаг ФЛАГ0 достоверности данных активен. Когда сигнал ОЧ_ДОСТ_0 активен и флаг ФЛАГ0 достоверности данных активен, выходной сигнал элемента 334 И активен, и выходной сигнал Q второго переключающего триггера 302 будет изменяться от его высокого состояния до его низкого состояния или от его низкого состояния до его высокого состояния один раз при каждом переходе от низкого уровня к высокому для сигнала ТАКТ ШИНЫ 2. Если либо сигнал ОЧ_ДОСТ_ 0 неактивен, либо флаг ФЛАГ0 достоверности данных неактивен, выходной сигнал Q второго переключающего триггера 300 не будет изменяться независимо от изменений сигнала ТАКТ ШИНЫ 2.

Первый переключающий триггер 300 имеет вход 340 сброса (RST) и второй переключающий триггер 302 имеет вход 342 сброса (RST). Входы 340, 342 RST принимают сигнал СИСТЕМНЫЙ СБРОС по сигнальной линии 174. Когда сигнал СИСТЕМНЫЙ СБРОС активен, два переключающих триггера 300, 302 сбрасываются, так что соответствующие выходные сигналы Q очищаются до их неактивных низких состояний.

Выходные сигналы Q первого и второго переключающих триггеров 300, 302 поданы как соответствующие первый и второй входы для элемента 350 Исключающее ИЛИ. Выход элемента 350 Исключающее ИЛИ выдает флаг ФЛАГ0 достоверности данных на линию 172А, который, таким образом, является выходом ячейки хранения достоверности данных. Флаг ФЛАГ0 достоверности данных на линии 172А является также обратной связью на два переключающих триггера 300, 302 через соответствующие элементы 314, 334 И, как рассмотрено выше. Элемент 350 Исключающее ИЛИ работает в ответ на два входа для обеспечения активного флага ФЛАГ0 достоверности данных на линии 172А, когда оба выходных сигнала Q отличаются друг от друга (т.е. один выходной сигнал Q имеет высокий активный уровень, а другой выходной сигнал Q имеет низкий активный уровень), и для обеспечения неактивного флага ФЛАГ0 достоверности данных на линии 172А, когда оба выходных сигнала Q имеют одинаковый логический уровень (т.е. когда оба выходных сигнала Q имеют высокий активный уровень, или когда оба выходных сигнала Q имеют низкий активный уровень). Как рассмотрено выше, когда выход элемента 350 Исключающее ИЛИ имеет высокий активный уровень, показывающий, что выходной сигнал Q второго переключающего триггера 302 отличается от выходного сигнала Q первого переключающего триггера 300, потенциально открыт только второй элемент 334 И, так что если активна сигнальная линия 220А ОЧ_ДОСТ_0, то разрешается работа второго переключающего триггера 302. Второй переключающий триггер 302 переключается в следующий переход от низкого уровня к высокому для сигнала ТАКТ ШИНЫ 2 на сигнальной линии 126. Это заставляет выходной сигнал Q второго переключающего триггера 302 становиться одинаковым с выходным сигналом Q первого переключающего триггера 300, так что выход элемента 350 Исключающее ИЛИ становится неактивным. Неактивное состояние выхода элемента 350 Исключающее ИЛИ показывает, что флаг ФЛАГ0 достоверности данных очищен (то есть, что данные недостоверны). Кроме того, второму переключающему триггеру 302 запрещается переключаться, а первому переключающему триггеру 300 разрешается переключаться, если сигнальная линия 166А УСТ_ ДОСТ_ 0 активируется конечным автоматом 160 интерфейса шины 1. Поэтому можно видеть, что флаг ФЛАГ0 достоверности данных устанавливается синхронно по отношению к сигналу ТАКТ ШИНЫ 1 и очищается синхронно по отношению к сигналу ТАКТ ШИНЫ 2.

Дополнительная информация, касающаяся ячеек хранения данных, основанных на вышеописанных переключающих триггерах, может быть найдена, например, в патенте США 5083049, который выдан заявителю по настоящей заявке и который включен сюда посредством ссылки. Специалисту ясно, что в настоящем изобретении могут быть использованы и альтернативные ячейки хранения данных.

Возвращаясь к фиг. 1, можно видеть, что задачами синхронизатора 190 достоверных данных шины 1 и синхронизатора 210 достоверных данных шины 2 является обеспечение того, чтобы изменения флагов достоверных данных подавались на конечный автомат 160 интерфейса шины 1 и на конечный автомат 140 интерфейса шины 2 синхронно с соответствующими тактовыми сигналами, которые управляют обоими конечными автоматами. В частности, как рассмотрено выше, флаги достоверных данных устанавливаются синхронно с сигналом ТАКТ ШИНЫ 1 и очищаются синхронно с сигналом ТАКТ ШИНЫ 2. Таким образом, флаг достоверных данных будет изменяться от своего неактивного состояния в свое активное состояние синхронно с сигналом ТАКТ ШИНЫ 1 и будет изменяться от своего активного состояния в свое неактивное синхронно с сигналом ТАКТ ШИНЫ 2. Поскольку сигнал ТАКТ ШИНЫ 1 несинхронен сигналу ТАКТ ШИНЫ 2, конечный автомат 160 интерфейса шины 1 принимает переход от высокого уровня к низкому для флагов достоверных данных асинхронно по отношению к своим внутренним переходам. Таким образом, существуют возможности, чтобы переходы происходили тогда, когда конечный автомат интерфейса шины 1 потребует, чтобы состояние флагов достоверных данных было стабильно и не изменялось. Синхронизатор 190 шины 1 синхронизирует переходы от высокого уровня к низкому для флагов достоверных данных с сигналом ТАКТ ШИНЫ 1 и, таким образом, с внутренними переходами конечного автомата 160 интерфейса шины 1. Аналогично, синхронизатор 210 шины 2 синхронизирует переходы от высокого уровня к низкому для флагов достоверных данных с сигналом ТАКТ ШИНЫ 2 и, таким образом, с внутренними переходами конечного автомата 140 интерфейса шины 2. Особенно важно, что переходы от высокого уровня к низкому для флагов достоверных данных синхронизированы с сигналом ТАКТ ШИНЫ 2, поскольку соответствующий флаг достоверных данных устанавливается как данные, записываемые в выбранную в текущий момент входную ячейку. Если выбранная в текущий момент входная ячейка также является выбранной в текущий момент выходной ячейкой (т.е. конечный автомат 140 интерфейса шины 2 выдал все хранившиеся до того данные), то конечный автомат 140 интерфейса шины 2 немедленно почувствует, что флаг достоверных данных стал активным, и выдаст данные на вторую шину 120. Однако это потенциально вызывает метастабильность внутри конечного автомата 140 интерфейса шины 2 и условия гонки фронтов, особенно если переходы флага достоверных данных из его неактивного состояния в его активное состояние происходят перед тем, как данные записываются в соответствующую ячейку хранения данных и распространяются через мультиплексор 134 и через регистр 150. Синхронизатор шины 2 гарантирует, что данные стабильны, перед тем, как конечный автомат 140 интерфейса шины 2 выдает данные на вторую шину 120.

Интерфейс 100 между шинами 1 и 2 хорошо работает для предназначенной цели; однако интерфейс 100 имеет задержку синхронизации, вызванную синхронизатором 190 шины 1 и синхронизатором 210 шины 2, которая уменьшает общую скорость передачи данных в интерфейсе 100, особенно когда данные передаются на интерфейс или от него в пакетном режиме. Проблема может быть понята при рассмотрении работы конечного автомата 140 интерфейса шины 2, когда все четыре буферных ячейки (БУФЕР 0 ДАННЫХ...БУФЕР 3 ДАННЫХ) данных в буфере 130 данных заполнены и установлены соответствующие флаги (ФЛАГ0...ФЛАГ3) достоверных данных. После того, как конечный автомат 140 интерфейса шины 2 передает данные из первой буферной ячейки данных (например, БУФЕР 0 ДАННЫХ), конечный автомат 140 интерфейса шины 2 выбирает следующую буферную ячейку (например, БУФЕР 1 ДАННЫХ) через мультиплексор 134, а также выбирает следующий флаг достоверных данных (например, ФЛАГ1) через линии 202 выбора ко второму флаговому мультиплексору 200. Хотя данные во второй буферной ячейке (БУФЕР 1 ДАННЫХ) могут быть стабильны на протяжении большого числа циклов синхронизации, конечный автомат 140 интерфейса шины 2 все же должен ждать флага достоверных данных для синхронизации синхронизатором 210 шины 2 перед тем, как он может выдать данные на вторую шину 120. Таким образом, вводятся два ненужных цикла сигнала ТАКТ ШИНЫ 2 для синхронизации флага достоверных данных.

Такая же ненужная задержка появляется, когда конечный автомат интерфейса шины 1 увеличивает входной указатель на следующую ячейку. Хотя следующая ячейка хранения данных может быть пустой в течение большого числа циклов синхронизации, но когда конечный автомат интерфейса шины 1 изменяет линии 182 выбора к первому флаговому мультиплексору 180, конечный автомат интерфейса шины 1 должен два цикла синхронизации ждать выбранного флага для синхронизации через синхронизатор 190 шины 1 перед тем, как он может определить, что флаг достоверных данных очищен и что поэтому ячейка хранения данных доступна.

Заявитель обнаружил, что ненужная задержка может быть исключена путем синхронизации флагов достоверных данных перед тем, как подавать флаги достоверных данных на флаговый мультиплексор 200 шины 2. Усовершенствованный интерфейс показан на фиг. 3, где одинаковые позиции означают одинаковые элементы, как описано выше по отношению к фиг. 1. Конечный автомат 140 интерфейса шины 2 изменен и показан на фиг. 3 как конечный автомат 404 интерфейса шины 2. Аналогично, конечный автомат 160 интерфейса шины 1 изменен и показан на фиг. 3 как конечный автомат 406 интерфейса шины 1.

Как показано на фиг. 3, единственный синхронизатор 190 шины 1 на выходе первого флагового мультиплексора 180 по фиг. 1 заменен четырьмя синхронизаторами 410, 412, 414 и 416 шины 1. Каждый синхронизатор 410, 412, 414 и 416 шины 1 имеет соответствующий вход, подключенный к выходу соответствующей одной из четырех буферных ячеек 170 флагов достоверных данных, и имеет соответствующий выход, подключенный к одному из четырех входов первого флагового мультиплексора 180. Как далее изображено для первого синхронизатора 410 шины 1, каждый из синхронизаторов содержит пару триггеров (FF) 420, 422, соединенных тандемом и тактируемых сигналом ТАКТ ШИНЫ 1 на сигнальной линии 116.

Аналогично, единственный синхронизатор 210 шины 2 заменен четырьмя синхронизаторами 430, 432, 434 и 436 шины 2. Каждый синхронизатор 430, 432, 434 и 436 шины 2 имеет соответствующий вход, подключенный к выходу соответствующей одной из четырех буферных ячеек 170 флагов достоверных данных, и имеет соответствующий выход, подключенный к одному из четырех входов второго флагового мультиплексора 200. Как далее изображено для первого синхронизатоpa 430 шины 2, каждый из синхронизаторов содержит пару триггеров (FF) 440, 442, соединенных тандемом и тактируемых сигналом ТАКТ ШИНЫ 2 на сигнальной линии 126.

Видно, что усовершенствованный интерфейс 400 выполняет задачу интерфейса 100 по фиг. 1 путем обеспечения того, что флаги достоверных данных должным образом синхронизируются конечным автоматом 406 интерфейса шины 1 и конечным автоматом 404 интерфейса шины 2. Например, если конечный автомат 404 интерфейса шины 2 выдал все данные в буфер 130 данных и ожидает следующих данных для запоминания в ячейке 132 хранения, входной указатель и выходной указатель будут указывать на одну и ту же ячейку 132 хранения. Когда конечный автомат интерфейса шины 1 устанавливает флаг достоверных данных (например, ФЛАГ0), выходной сигнал флагового буфера 107А ФЛАГ0 (фиг. 2) перейдет в свое активное состояние и распространится через первый синхронизатор 430 шины 2 и станет синхронизирован конечным автоматом 404 интерфейса шины 2 перед тем, как он будет подан в качестве активного входного сигнала на конечный автомат 404 интерфейса шины 2. Таким образом, активный выходной сигнал флагового буфера 170А ФЛАГ0 будет непременно синхронизирован с тактовым сигналом шины 2 и, таким образом, синхронизируется конечным автоматом 404 интерфейса шины 2. Активный выходной сигнал флагового буфера 170А ФЛАГ0 будет задержан для обеспечения потребного времени для того, чтобы дать возможность стабилизироваться данным, которые только что были записаны в ячейку 132 БУФЕР 0 ДАННЫХ хранения данных. С другой стороны, если конечный автомат интерфейса шины 2 выдает пакет данных из буфера 130 данных, причем следующая буферная ячейка 132, подлежащая выбору, имеет данные, хранившиеся в ней несколько циклов синхронизации, то флаг достоверных данных (например, ФЛАГ1) будет распространяться уже через соответствующий синхронизатор шины 2 (например, второй синхронизатор 432 шины 2) и будет активным на выходе второго флагового мультиплексора 200. Таким образом, когда конечный автомат интерфейса шины 2 изменяет линии 202 выбора для выбора выходного сигнала буфера ФЛАГ1 флагов достоверности данных, активное состояние флага будет немедленно подано на конечный автомат 404 интерфейса шины 2 без любой другой задержки.

Для помощи в дальнейшем понимании преимуществ усовершенствованного интерфейса по фиг. 3, фиг. 4 показывает примерную диаграмму 500 состояния существенной части конечного автомата 140 интерфейса шины 2 по фиг. 1, а фиг. 5 показывает примерную диаграмму 510 состояния существенной части конечного автомата 404 интерфейса шины 2 по фиг. 3. Каждый конечный автомат 140, 404 включает в себя дополнительные функции, не показанные на фиг. 4 и 5, которые не являются существенными для настоящего изобретения и которые не будут описаны ниже. На фиг. 4 и 5 существенные внутренние состояния конечного автомата представлены обычным образом как круги, имеющие внутри название состояния. Линии, соединяющие круги, представляют переходы состояний из одного состояния к другому состоянию или из состояния обратно в состояние, что происходит синхронно с сигналом 126 ТАКТ ШИНЫ 2 по фиг. 1 и 2.

Условия, предшествующие переходу состояния, определяются как параметры, расположенные рядом с каждым переходом состояния со знаком амперсанда ("&"), представляющим требование И, означающее, что все условия, связанные амперсандами, должны быть удовлетворены, чтобы вызвать появление перехода состояния. Линия над условием показывает, что условие должно быть неактивно. Цифра "1" рядом с переходом состояния показывает, что переход из одного состояния в другое будет происходить безусловно при наступлении следующего цикла сигнала ТАКТ ШИНЫ 2. Слово "КРОМЕ" рядом с переходом показывает, что переход состояния является переходом по умолчанию, который происходит, если не удовлетворены условия для других переходов из данного состояния. Если конечный автомат 140 интерфейса шины 2 выполняет существенную операцию при появлении конкретного перехода, то каждая операция определяется в конце параметра косой чертой ("/"), за которой следует название операции.

Как показано на фиг. 4, диаграмма 500 состояния включает в себя состояние 520 СВОБОДНО, состояние 522 МАСКА1, состояние 524 МАСКА2 и состояние 526 ПРОЦЕСС_ПЕРЕД_ДАННЫХ (процесс передачи данных). Диаграмма 500 состояния показывает развитие передачи множества учетверенных слов данных из буфера 132 данных на вторую шину 120. Состояние 520 СВОБОДНО является "нормальным" состоянием конечного автомата 140 интерфейса шины 2, который запускается, когда компьютерная система сбрасывается, как показано переходом 530 состояния СБРОС. Как будет рассмотрено ниже, конечный автомат 140 интерфейса шины 2 возвращается в состояние 520 СВОБОДНО, когда передача данных завершается.

Конечный автомат 140 интерфейса шины 2 остается в состоянии 520 СВОБОДНО до тех пор, пока не будет инициирован новый цикл считывания другими частями конечного автомата 140 интерфейса шины 2, который наблюдает за управляющими сигналами на второй шине 120 и за другими условиями, чтобы определить, когда инициируется новый цикл считывания. Работа конечного автомата 140 интерфейса шины 2, остающегося в состоянии СВОБОДНО, пока не инициирован новый цикл считывания, представлена переходом 532 состояния КРОМЕ, где эта часть конечного автомата 140 интерфейса шины 2 наблюдает за остальными частями конечного автомата 140 интерфейса шины 2 и определяет, когда инициируется новый цикл считывания. В частности, конечный автомат 140 интерфейса шины 2 остается в состоянии 520 СВОБОДНО, пока неактивен внутренний сигнал НОВОЕ_СЧИТ (новое считывания).

Когда новый цикл считывания запущен конечным автоматом 140 интерфейса шины 2 (сигнал НОВОЕ_СЧИТ активен) и конечный автомат 140 интерфейса шины 2 определил, что вторая шина 120 выделена для интерфейса 100 шин (активен сигнал, обозначенный как ВРЕМЯ_СЧИТ_ШИНЫ - время считывания шины), конечный автомат 140 интерфейса шины 2 производит переход 540 состояния в состояние 522 МАСКА1. Как показано далее частью "/ЗАГР_СЧЕТЧ_УЧЕТВ_СЛОВ" (загрузка счетчика учетверенных слов) параметра перехода состояния, конечный автомат интерфейса шины 2 загрузит счет учетверенных слов во внутренний счетчик учетверенных слов (не показан), когда происходит переход 540 состояния. Счет учетверенных слов показывает число переходов, которые должны произойти для передачи данного пакета данных из первой шины 110 во вторую шину 120.

Состояние 522 МАСКА1 и состояние 524 МАСКА2 являются состояниями задержки для обеспечения того, чтобы выбранный флаг достоверности данных имел достаточное время для распространения от флагового мультиплексора 200 шины 2 через синхронизатор 210 шины 2 перед тем, как конечный автомат 140 интерфейса шины 2 проверяет состояние выбранного флага достоверности данных. Таким образом, переход 542 из состояния 522 МАСКА1 в состояние 524 МАСКА2 показан как проходящий безусловно (как представлено соседним с ним параметром "1"). Аналогично, переход 544 из состояния 524 МАСКА2 в состояние 526 ПРОЦЕСС_ПЕРЕД_ДАННЫХ (процесс передачи данных) происходит безусловно.

В состоянии 526 ПРОЦЕСС_ПЕРЕД_ДАННЫХ конечный автомат 140 интерфейса шины 2 проверяет состояние флага ДАННЫЕ _ВЕРНЫ_2, и, если он неактивен, конечный автомат интерфейса шины 2 остается в состоянии 526 ПРОЦЕСС_ПЕРЕД_ДАННЫХ, как показано переходом 550 КРОМЕ. Напротив, если флаг ДАННЫЕ_ВЕРНЫ_2 и сигнал ВРЕМЯ_ СЧ_ШИНЫ активны, конечный автомат 140 интерфейса шины 2 будет переходить либо в состояние 520 СВОБОДНО, либо в состояние 522 МАСКА 1 через переход 552 или переход 554, соответственно, и выдаст данные в одну ячейку, выбранную в текущий момент из буферных ячеек 132. Это показано параметром /ВЫВОД_ ДАННЫХ на обоих переходах 552 и 554. Должно быть понятно, что кроме выдачи данных конечный автомат интерфейса шины 2 будет активировать сигнал ОЧИСТКА_ВЕРНА в соответствующий один из флаговых буферов 170.

Выбор перехода 552 или перехода 554 зависит от условия параметра ВЫПОЛН (выполнено). Параметр ВЫПОЛН представляет условие выходного сигнала СЧЕТ_ УЧЕТВ_ СЛОВ счетчика учетверенных слов. Если сигнал СЧЕТ_УЧЕТВ_СЛОВ равен нулю, параметр ВЫПОЛН будет активным. Если сигнал СЧЕТ_УЧЕТВ_СЛОВ имеет отличное от нуля значение, то параметр ВЫПОЛН неактивен (то есть, будет активным параметр  ). Если ВЫПОЛН активен, то конечный автомат 140 интерфейса шины 2 произведет переход 552 обратно в состояние 520 СВОБОДНО и увеличит указатель на текущую выходную буферную ячейку, как показано параметром /ПРИР_ НОМ_ БУФ (приращение номера буфера) для указания на следующую ячейку 32 памяти в качестве следующего выходного буфера. Напротив, если ВЫПОЛН неактивен (то есть, активен

). Если ВЫПОЛН активен, то конечный автомат 140 интерфейса шины 2 произведет переход 552 обратно в состояние 520 СВОБОДНО и увеличит указатель на текущую выходную буферную ячейку, как показано параметром /ПРИР_ НОМ_ БУФ (приращение номера буфера) для указания на следующую ячейку 32 памяти в качестве следующего выходного буфера. Напротив, если ВЫПОЛН неактивен (то есть, активен  то конечный автомат 140 интерфейса шины 2 произведет переход к состоянию 522 МАСКА 1, увеличит указатель на текущую выходную буферную ячейку и уменьшит счетчик учетверенных слов, как показано параметром /УМЕНЬШ_ СЧЕТЧ_УЧЕТВ_СЛОВ. Как рассмотрено выше в связи с фиг. 1, необходимо провести цикл обратно через состояние 522 МАСКА 1 и состояние 524 (МАСКА2) с целью обеспечения времени для того, чтобы предварительно выбранный флаг достоверности данных распространялся из синхронизатора шины 2 и заменялся вновь выбранным флагом достоверности данных перед тем, как сигнал ДАННЫЕ_ ВЕРНЫ_2 оценивается конечным автоматом 140 интерфейса шины 2. Эта задержка будет вводиться независимо от того, насколько длинные данные во вновь выбранной выходной буферной ячейке были запомнены в выбранной буферной ячейке 132 и насколько долго соответствующий флаг достоверности данных был активным.

то конечный автомат 140 интерфейса шины 2 произведет переход к состоянию 522 МАСКА 1, увеличит указатель на текущую выходную буферную ячейку и уменьшит счетчик учетверенных слов, как показано параметром /УМЕНЬШ_ СЧЕТЧ_УЧЕТВ_СЛОВ. Как рассмотрено выше в связи с фиг. 1, необходимо провести цикл обратно через состояние 522 МАСКА 1 и состояние 524 (МАСКА2) с целью обеспечения времени для того, чтобы предварительно выбранный флаг достоверности данных распространялся из синхронизатора шины 2 и заменялся вновь выбранным флагом достоверности данных перед тем, как сигнал ДАННЫЕ_ ВЕРНЫ_2 оценивается конечным автоматом 140 интерфейса шины 2. Эта задержка будет вводиться независимо от того, насколько длинные данные во вновь выбранной выходной буферной ячейке были запомнены в выбранной буферной ячейке 132 и насколько долго соответствующий флаг достоверности данных был активным.

В противоположность диаграмме 500 состояний по фиг. 4, диаграмма 510 по фиг. 5 требует меньшего количества состояний и работает более эффективно благодаря размещению многочисленных синхронизаторов 430, 432, 434 и 436 шины 2 между выходами флагового буфера 170 и входами флагового мультиплексора 200 шины 2, как показано на фиг. 3, вместо того, чтобы иметь единственный синхронизатор 210 шины 2, показанный после мультиплексора 200, как представлено на фиг. 1. В частности, диаграмма 510 состояний по фиг. 5 включает в себя только состояние 600 СВОБОДНО и состояние 610 ПРОЦЕСС_ПЕРЕД_ДАННЫХ. Состояние СВОБОДНО вводится переходом 620 СБРОС, как рассмотрено выше. Конечный автомат 404 интерфейса шины 2 по фиг. 3 останется в состоянии 600 СВОБОДНО, как показано переходом 622 КРОМЕ, пока не наступят определенные условия, как показано параметрами, соседними с переходом 624, для состояния 610 ПРОЦЕСС_ ПЕРЕД_ ДАННЫХ. В частности, конечный автомат 404 интерфейса шины 2 останется в состоянии СВОБОДНО, пока не будет инициирован параметр НОВОЕ_СЧИТ и условие ВРЕМЯ_СЧ_ШИНЫ не станет активно, и в это время он перейдет через переход 624 состояния в состояние 610 ПРОЦЕСС_ПЕРЕД_ДАНЫХ и загрузит счетчик учетверенных слов числом учетверенных слов для передачи, как представлено параметром /ЗАГР_СЧЕТЧ_УЧЕТВ_СЛОВ.

В состоянии 610 ПРОЦЕСС_ПЕРЕД_ДАННЫХ конечный автомат 404 интерфейса шины 2 наблюдает за состоянием сигнала ДАННЫЕ_ВЕРНЫ_2. Если сигнал ДАННЫЕ_ВЕРНЫ_ 2 активен и ВРЕМЯ_СЧ_ШИНЫ остается активным, конечный автомат 404 интерфейса шины произведет один из двух переходов 630 и 632 в соответствии с условием ВЫПОЛН. Если условие ВЫПОЛН неактивно, то конечный автомат 404 интерфейса шины 2 останется в состоянии 610 ПРОЦЕСС_ПЕРЕД_ДАННЫХ, как показано переходом 630 состояния, и будет выдавать содержимое выбранной в текущий момент одной из буферных ячеек 132 данных, как показано параметром /ВЫВОД_ДАННЫХ. Конечный автомат 404 интерфейса шины 2 увеличит номер текущего буфера (/ПРИР_ НОМ_ БУФ) и уменьшит счетчик учетверенных слов (/УМЕНЬШ_СЧЕТ_УЧЕТВ_ СЛОВ). Если условие ВЫПОЛН активно, то конечный автомат 404 интерфейса шины 2 затем перейдет обратно в состояние 600 СВОБОДНО через переход 632 состояния, выдавая последнее учетверенное слово (/ВЫВОД_ДАННЫХ) и увеличивая номер буфера (/ПРИР_НОМ_БУФ). Если сигнал ДАННЫЕ_ВЕРНЫ_2 неактивен или если еще не наступило условие ВРЕМЯ_СЧИТ_ШИНЫ (например, вторая шина 120 в текущий момент недоступна), то конечный автомат 404 интерфейса шины 2 останется в состоянии 610 ПРОЦЕСС_ПЕРЕД_ДАННЫХ, как показано переходом 634 КРОМЕ.

Как показано диаграммой 510 состояний, конечный автомат 404 интерфейса шины 2 в соответствии с фиг. 3 и 5 не имеет задержки по времени, неотъемлемой для конечного автомата 140 интерфейса шины 2 по фиг. 1 и 4. В частности, можно видеть, что как только конечный автомат 404 интерфейса шины 2 увеличивает номер буфера при переходе 630, он остается в состоянии 610 ПРОЦЕСС_ ПЕРЕД_ ДАННЫХ и немедленно проверяет сигнал ДАННЫЕ_ВЕРНЫ_2 для определения того, могут ли данные быть переданы из вновь выбранной буферной ячейки 132 данных. Это может произойти, поскольку соответствующий флаг достоверности данных (ФЛАГ0, ФЛАГ1, ФЛАГ2 и ФЛАГ3) будет распространяться через соответствующий синхронизатор 430, 432, 434 или 436 шины 2 и будет доступен на входе флагового мультиплексора 200, как только выбирается следующий вход мультиплексора 200. Таким образом, предполагая, что вторая шина 120 остается выделенной для конечного автомата 404 интерфейса шины 2, и предполагая, что первая шина 120 заполнена буферными ячейками 132 данных, данные могут быть выданы затем из буферных ячеек 132 в каждом последующем такте вместо того, чтобы производить задержку на два такта между каждым выходом.

Хотя вышеописанное дано в связи с конкретными выполнениями настоящего изобретения, должно быть понятно, что описания выполнений иллюстрируют изобретение и не предназначены для его ограничения. Различные изменения и применения могут быть видны специалистам без отхода от истинного духа и объема изобретения, как оно определено в приложенной формуле изобретения.

Изобретение относится к компьютерным системам, а в частности к цифровым подсистемам, которые управляют передачей данных от одной синхронной шины данных к другой синхронной шине данных. Техническим результатом является повышение производительности компьютерной системы. Схема интерфейса между первой и второй шинами включает в себя конечный автомат интерфейса первой шины, который управляет передачами данных от первой шины данных в буфер данных, конечный автомат интерфейса второй шины, который управляет передачами данных от буфера данных на вторую шину данных. Соответствующий флаг достоверных данных для каждой ячейки хранения устанавливается конечным автоматом интерфейса первой шины, когда данные запоминаются в ячейке хранения из первой шины данных, и очищается конечным автоматом интерфейса второй шины, когда данные передаются из ячейки хранения во вторую шину данных. Для уменьшения времени, требуемого для вывода последовательных данных из множества ячеек хранения данных в буфере данных, каждый флаг достоверности данных синхронизируется независимо. 3 с. и 2 з.п. ф-лы, 5 ил.

Приоритет по пунктам:

07.06.1995 - пп.1, 2, 5;

02.08.1995 - пп.3, 4.

| US 5274763 А, 28.12.1993 | |||

| Устройство для обмена данными | 1991 |

|

SU1807496A1 |

| US 5535341 А, 09.07.1996 | |||

| Устройство обмена данными | 1989 |

|

SU1615731A2 |

Авторы

Даты

2001-12-10—Публикация

1996-06-06—Подача