Изобретение относится к компьютерным системам, в частности к способу выполнения операций считывания из памяти в симметричных мультипроцессорных компьютерных системах.

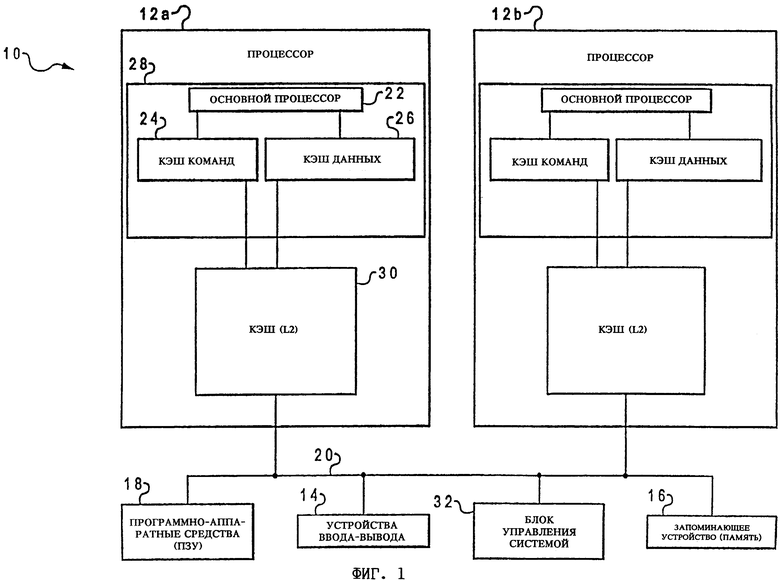

Базовая структура обычной мультипроцессорной компьютерной системы 10 показана на фиг.1. Эта компьютерная система 10 имеет несколько процессоров, из которых на схеме показаны только два процессора 12а и 12b, каждый из которых соединен с различными периферийными устройствами, включая устройства 14 ввода-вывода (I/O от англ. "input/output") (такие, как видеодисплей/монитор, клавиатура, графический указатель (мышь) и постоянное запоминающее устройство (жесткий диск)), запоминающее устройство (ЗУ) 16 (в частности, запоминающее устройство с произвольной выборкой или ЗУПВ), которое используется процессорами как источник машинных команд и служит системной памятью, и программно-аппаратные средства 18, которые содержат так называемые "зашитые" программы и основное назначение которых заключается в нахождении и загрузке операционной системы с одного из периферийных устройств (обычно с постоянного запоминающего устройства) при включении питания компьютера. Процессоры 12а и 12b могут быть связаны с периферийными устройствами различными путями, включая использование общей схемы межсоединений или шины 20 либо каналов прямого доступа к памяти (не показаны). Компьютерная система 10 может иметь много дополнительных компонентов, которые на чертеже не показаны, таких, например, как последовательные и параллельные порты связи, например, с модемами или принтерами. Для специалистов в данной области техники очевидно, что в данной структуре, блок-схема которой показана на фиг.1, возможно использование и других компонентов, например адаптера дисплея, который может использоваться для управления видеомонитором, контроллера памяти, который может использоваться для доступа, или обращения, к ЗУ 16, и т.д. Кроме того, и сам компьютер может иметь более двух процессоров.

В симметричном мультипроцессорном (СМП) компьютере все процессоры обычно являются идентичными, т.е. все они используют общую систему или подсистему команд и протоколов, обеспечивающих их функционирование, и обычно имеют одинаковую архитектуру. Архитектура типичного процессора показана на фиг.1. Этот процессор содержит основной процессор 22, имеющий множество регистров и исполнительных блоков, которые в определенном порядке отрабатывают машинные команды, управляя компьютером. В качестве примера такого процессора можно назвать процессор PowerPCТМ, выпускаемый корпорацией IBM. Процессор может также иметь один или несколько кэшей, таких как кэш 24 команд и кэш 26 данных, которые выполнены на основе быстродействующих запоминающих устройств. Кэш обычно используется для временного хранения информации, к которой периодически может обращаться процессор, с целью ускорения процесса обработки за счет исключения длительных операций загрузки информации из ЗУ 16. Такие кэши называют "встроенными", когда они выполнены совместно с основным процессором 28 в виде единой интегральной схемы. Каждый кэш функционально связан с соответствующим контроллером (не показан), который управляет передачей данных и команд между основным процессором и кэш-памятью.

Процессор может иметь дополнительные кэши, например кэш 30, который называется кэшем второго уровня (L2), поскольку он поддерживает работу встроенных кэшей 24 и 26 первого уровня. Иными словами, кэш 30 работает как промежуточное звено между ЗУ 16 и встроенными кэшами и может хранить при большем времени доступа большее в сравнении со встроенными кэшами количество информации (команды и данные). В качестве кэша 30 можно, например, использовать интегральную схему с объемом памяти 256 или 512 килобайт, при этом процессором может служить процессор IBM серии PowerPCТМ 604, имеющий встроенные кэши с общим объемом памяти 64 килобайта. Кэш 30 соединен с шиной 20, а вся загружаемая из ЗУ 16 в основной процессор 22 информация должна проходить через этот кэш 30. На фиг.1 показана двухуровневая иерархия кэшей, хотя фактически можно использовать и многоуровневую иерархию с несколькими уровнями (L3, L4 и т.д.) последовательно соединенных друг с другом кэшей.

В СМП-компьютере важно иметь связную систему памяти, т.е. обеспечить запись в каждую отдельную ячейку памяти в определенной последовательности для всех его процессоров. В кэш-связной системе во все процессоры будет поступать информация о том, что записи в определенную ячейку памяти будут происходить в указанном порядке. Существует много известных специалистам протоколов и соответствующих методов достижения связности кэшей. Суть всех этих методов сохранения связности заключается в необходимости выполнения требования, заключающегося в том, чтобы протокол разрешал только одному процессору в любой данный момент времени записывать информацию в данную ячейку памяти (в блок кэш). В этом случае при попытке любого процессора записать информацию в определенную ячейку памяти он должен предварительно информировать об этом все другие процессоры и получить от них разрешение на запись. Все другие процессоры системы должны быть предварительно проинформированы о записи информации первым процессором. Кроме того, при наличии блока информации в L1-кэше данного процессора этот блок будет также присутствовать в L2- и L3-кэшах этого же процессора. Такое свойство процессоров, называемое включением, хорошо известно специалистам.

С целью обеспечить связность кэшей в системе процессоры соединяются друг с другом общей разводкой (в частности, шиной 20). Процессоры передают по такой общей схеме внутренних межсоединений сообщения о своих намерениях занять для чтения или записи соответствующие ячейки памяти. Когда такая информация попадает в общую схему соединений, все другие процессоры отслеживают ее и решают, позволяет ли состояние их кэшей выполнить данную операцию и, если да, то при каких условиях. Имеется несколько совершаемых с использованием шины транзакций, которые требуют отслеживания и последующих действий с целью проверки, не нарушили ли они связность памяти. Результаты отслеживания собираются и анализируются системной логикой, которая обычно расположена в блоке 32 управления системой. Операция отслеживания запускается после подтверждения обоснованности запроса на ее выполнение, который создается на основе оценки определенных сигналов шины. Такое подтверждение необходимо в связи с тем, что в системе с кэшами самая последняя достоверная копия информации из данного блока памяти может быть передана из системного ЗУ 16 в один или несколько кэшей системы. Когда процессор, например процессор 12а, пытается получить доступ к ячейке памяти, не находящейся внутри его иерархии кэшей, истинная версия блока, который содержит действительную (текущую) информацию ячейки памяти, может находиться либо в системном ЗУ 16, либо в одном или нескольких кэшах другого процессора, например процессора 12b. Если истинная версия находится в одном или нескольких кэшах системы, ее необходимо получить из кэша, а не из системного ЗУ.

В качестве примера ниже рассмотрена работа процессора 12а, который пытается считать информацию из ячейки памяти. Сначала этот процессор опрашивает свой собственный L1-кэш (24 или 26). При отсутствии искомого блока информации в L1-кэше запрос направляется в L2-кэш (30). Если искомый блок отсутствует и в L2-кэше, то запрос направляется в кэш более низкого уровня, например в кэш третьего уровня (L3). Если блок отсутствует и в этом кэше, запрос на выполнение соответствующей операции направляется в общую схему внутренних соединений (на шину 20). Как только запрос попадает в общую схему соединений, все другие кэши более низкого уровня отслеживают его и определяют, содержат ли они искомый блок информации. Если данный процессор имеет блок, содержащий запрашиваемую информацию, в его L1-кэше и эта информация в нем изменена, то в соответствии с принципом включения и другие L2-кэши и кэши более низкого уровня также будут содержать копии этого блока информации (однако их копии могут быть устаревшими, поскольку копия в кэше процессора была изменена). Следовательно, когда кэш более низкого уровня (например, L3) данного процессора отслеживает операцию считывания, он определяет, что запрашиваемый блок информации присутствует в нем и в измененном виде - в кэше более высокого уровня. В этом случае L3-кэш выдает в общую схему внутренних соединений сообщение, информирующее процессор о том, что он должен повторить соответствующую операцию позже, поскольку истинное значение ячейки памяти находится в L1-кэше на вершине иерархии памяти и должно быть найдено для того, чтобы оно стало доступным для обслуживания по запросу на считывание от первого процессора.

После повторного запроса от первого процессора L3-кэш инициирует процесс выборки (поиска) измененной информации из L1-кэша и делает ее доступной для себя или для основной памяти либо для обоих этих устройств вместе в зависимости от конкретных деталей реализации, которые в настоящем изобретении не рассматриваются. Для выборки блока из кэша более высокого уровня L3-кэш посылает сообщения по системе связи между кэшами к кэш более высокого уровня с запросом на выборку блока. Эти сообщения распространяются вверх по иерархической структуре до тех пор, пока они не достигнут L1-кэша и не заставят искомый блок информации переместиться вниз по иерархической структуре до кэша, имеющего самый низкий уровень в иерархии (L3-кэш или основная память), и оказаться доступным для обслуживания запроса от первого, инициирующего этот запрос процессора.

Инициирующий запрос процессор в итоге посылает запрос на считывание в общую схему внутренних соединений. В этот момент, однако, измененная информация уже была найдена и получена из L1-кэша процессора, и поэтому запрос на считывание от инициирующего запрос процессора будет выполнен.

Работа системы в таком режиме обычно называется "отслеживающим толчком". Запрос на считывание отслеживается в общей схеме внутренних соединений, что заставляет процессор передать ("толкнуть") искомый блок информации вниз иерархической структуры памяти, где этот запрос на считывание, поступивший от инициирующего его процессора, будет выполнен ("удовлетворен").

Когда процессору требуется считать или записать определенный блок информации, он должен для сохранения связности кэшей передать соответствующее сообщение другим процессорам системы. Для этого с каждым блоком на каждом уровне иерархии кэшей ассоциируется протокол связности кэшей, при этом определенный индикатор состояния характеризует текущее "состояние" блока информации. Информация о состоянии используется для определенной оптимизации протокола связности, которая уменьшает трафик сообщений в общей схеме внутренних соединений и в схеме внутренних соединений между кэшами. Примером такого механизма является работа системы, когда выполняющий считывание процессор получает сообщение, показывающее, требуется ли считывание повторить позже или нет. Если операция считывания не требует повторения, то сообщение также обычно включает информацию, позволяющую процессору определить, имеет ли другой процессор еще одну действующую копию блока (это достигается за счет того, что другие кэши самого низкого уровня для любого не повторяемого ими считывания характеризуют имеющуюся в них информацию как "совместную" или "не совместную"). В этом случае процессор может определить, имеет ли другой процессор системы копию блока или нет. Если ни один другой процессор системы не имеет действующую копию блока, то считывающий процессор маркирует состояние этого блока как "исключительное". При такой маркировке блока как исключительный процессор может записать этот блок позже без предварительной связи с другими процессорами системы, поскольку ни один из них не имеет в своей памяти копии требуемого блока. Тем самым создается возможность для процессора считывать или записывать соответствующие ячейки без предварительного сообщения о своих намерениях на схему внутренних соединений, но сделать это он может только в том случае, когда протокол связности гарантирует, что ни один другой процессор не "интересуется" искомым блоком информации.

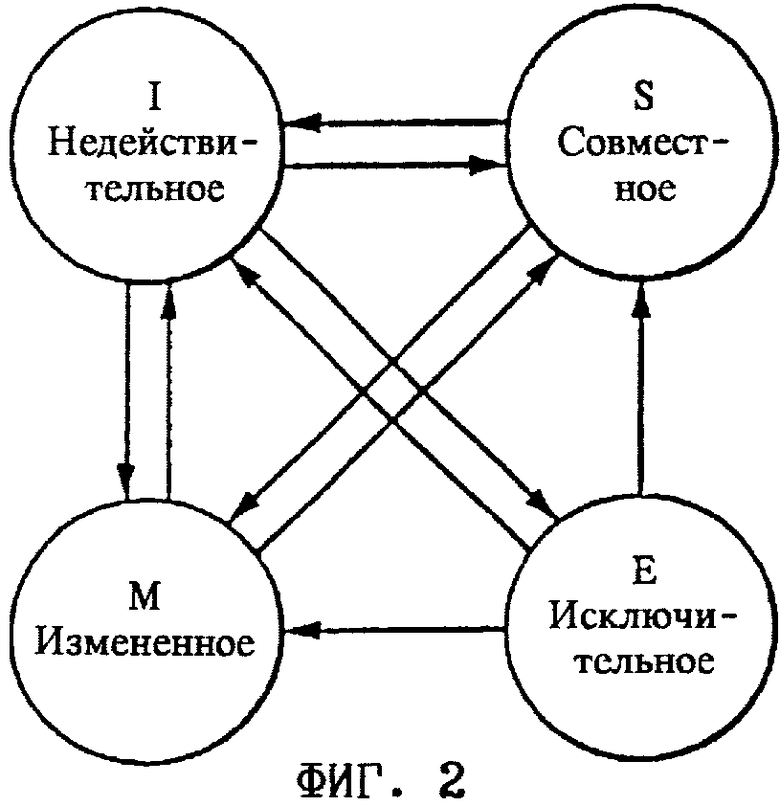

Вышеупомянутый способ обеспечения связности кэшей реализован в особом, показанном на фиг.2 протоколе, называемом протоколом MESI (от англ. modified (измененное), exclusive (исключительное), shared (совместное), invalid (недействительное)). В соответствии с этим протоколом блок информации может находиться в кэше в одном из четырех состояний: М (измененное), Е (исключительное), S (совместное), I (недействительное). По протоколу MESI каждый элемент (единица информации) в кэше (например, 32-байтовый сектор) имеет два дополнительных бита, которые показывают одно из четырех возможных состояний этого элемента. В зависимости от первоначального состояния элемента и типа доступа, определяемого запрашивающим процессором, состояние может быть изменено и для элемента в кэше запрашивающего процессора всегда устанавливается определенное конкретное состояние. Например, когда сектор находится в состоянии "измененное", действительный адресованный сектор находится только в том кэше, в котором имеется измененный сектор, при этом измененное значение не может быть записано обратно в системную память. Когда сектор находится в состоянии "исключительное", он находится только в отмеченном секторе в согласованном с системной памятью виде. Если сектор находится в состоянии "совместное", он действителен в этом кэше и по крайней мере еще в одном кэше, а все совместные секторы согласованы с системной памятью. И, наконец, когда сектор находится в состоянии "недействительное", то это означает, что в этом кэше нет адресованного сектора. Как показано на фиг.2, если сектор находится в одном из трех состояний: "измененное", "совместное", "недействительное", то он в зависимости от конкретной транзакции на шине может переходить из одного состояния в другое. Из состояния "исключительное" сектор может перейти в любое другое состояние, но в состояние "исключительное" он может перейти только из состояния "недействительное".

Дальнейшее улучшение процесса доступа к блокам информации, которые находятся в кэше, может быть достигнуто путем использования вышеупомянутого протокола связности кэшей. Такое улучшение, называемое "вмешательством", позволяет кэшу, управляющему блоком памяти, состояние которого маркировано как "измененное", доставлять данные или команды маркированного таким образом блока в другой кэш, запрашивающий информацию (для операции считывания), напрямую или, другими словами, без записи данных или команд в системную память с последующим их считыванием обратно из этой памяти по запросу процессора. Вмешательство может осуществляться только тем кэшем, который содержит информацию в блоке с состоянием "измененное". В таком состоянии имеется только один блок в кэше, в котором содержится действительная копия информации, что позволяет просто передать информацию по шине 20 без предварительной ее записи в системную память. Процедура вмешательства, таким образом, ускоряет процесс считывания за счет исключения длительных операций записи и считывания данных из системной памяти (что фактически включают три операции с шиной и две операции с памятью). Такая процедура не только повышает быстродействие памяти, но также увеличивает полезную пропускную способность шины.

Известные протоколы не пригодны для вмешательства, когда данные или команды находятся в неизмененном состоянии (т.е. в состоянии "исключительное" или "совместное"). Одно из возможных решений этой проблемы заключается в обработке находящегося в совместном состоянии блока в кэше таким образом, как будто он находится в измененном состоянии, что позволит доставить эту информацию по назначению из содержащего ее кэша, при этом, однако, вся эта информация будет также переписана в системную память, что не является необходимым и может привести к дальнейшим потерям времени. Было бы желательно, следовательно, пересмотреть существующий способ сохранения связности кэшей, обеспечив при этом возможность эффективного вмешательства неизмененных данных или команд. Желательно также, чтобы такой способ можно было реализовать при упрощенном вмешательстве значимой информации независимо от вида ее неизмененного состояния (т. е. для состояния "исключительное" либо "совместное" или для любого другого неизмененного состояния).

В этой связи одной из задач настоящего изобретения является разработка усовершенствованного способа выполнения операций считывания в многопроцессорной компьютерной системе, который позволил бы улучшить характеристики процесса при ответе на вмешательство за счет того, что искомая информация может быть найдена в неизмененном состоянии в кэше другого процессора.

В соответствии с первым вариантом изобретения предлагается способ повышения быстродействия памяти при выполнении операции считывания, инициируемой запрашивающим процессором в многопроцессорной компьютерной системе, включающей множество процессоров, каждый из которых имеет соответствующий кэш, причем этот способ включает следующие стадии: загрузку значимой информации из адреса запоминающего устройства по крайней мере в первый и второй кэш, маркирование первого и второго кэшей как кэшей, которые содержат совместные, неизмененные копии значимой информации, выдачу сообщения запрашивающим процессором, в котором указано, что запрашивающий процессор намерен считать значимую информацию из адреса запоминающего устройства, и передачу ответа от одного из первого и второго кэшей, указывающего, что данный кэш может служить источником значимой информации.

В соответствии со вторым вариантом изобретения предлагается способ повышения быстродействия памяти при выполнении операции считывания, инициируемой запрашивающим процессором в многопроцессорной компьютерной системе, включающей множество процессоров, каждый из которых имеет связанный с ним кэш, причем этот способ включает следующие стадии: загрузку значимой информации из адреса запоминающего устройства в множество кэшей, идентификацию данного кэша из множества кэшей, в котором содержится неизмененная копия значимой информации, которая совсем недавно была считана, маркирование данного кэша как содержащего совсем недавно считанную неизмененную копию значимой информации, маркирование множества кэшей, за исключением данного кэша, как содержащих совместные неизмененные копии значимой информации, выдачу сообщения запрашивающим процессором, указывающего, что запрашивающий процессор намерен считать значимую информацию из адреса запоминающего устройства, и передачу ответа из данного первого кэша, указывающего, что данный кэш может служить источником значимой информации.

Ниже описан вариант осуществления изобретения со ссылками на прилагаемые к описанию чертежи, на которых показано:

на фиг.1 - блок-схема известной многопроцессорной компьютерной системы,

на фиг. 2 - диаграмма состояний, иллюстрирующая известный протокол связности кэшей (протокол MESI), и

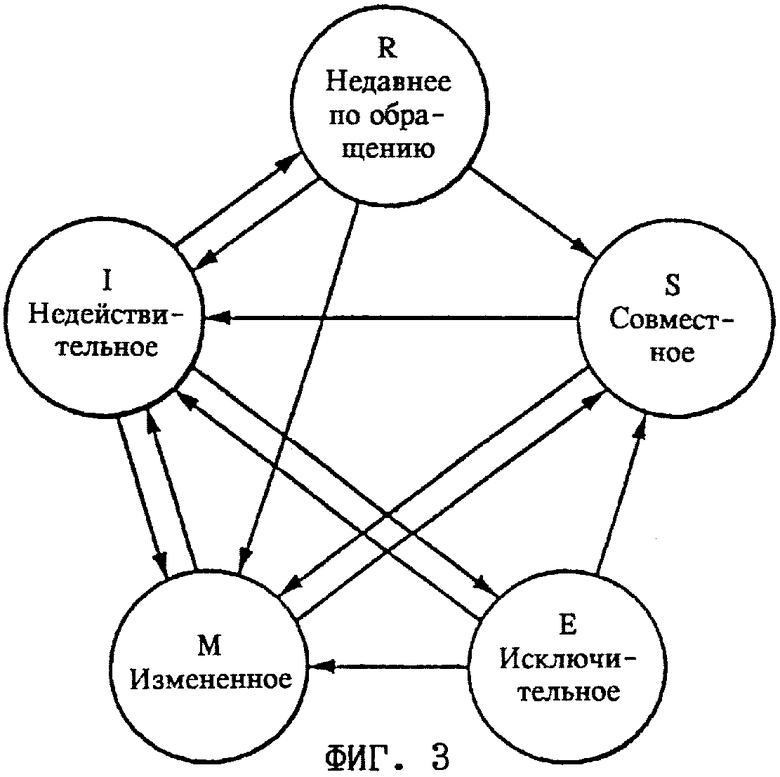

на фиг. 3 - диаграмма состояний, иллюстрирующая новый предлагаемый в изобретении протокол связности кэшей.

В настоящем изобретении предлагается способ выполнения команд чтения в многопроцессорной системе, в частности в системе, показанной на фиг.1, который также может быть использован в компьютерной системе, отличающейся от обычной и содержащей другие не показанные на фиг.1 аппаратные средства или имеющей другую архитектуру соединений между существующими компонентами. Поэтому для специалистов в данной области представляется очевидным, что настоящее изобретение в принципе не ограничивается обычной системой, показанной на этом чертеже.

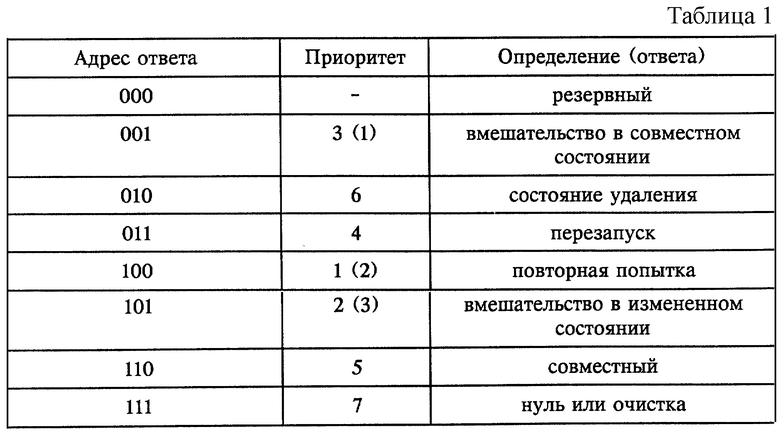

В настоящем изобретении устанавливается протокол, в соответствии с которым ответы связности в процессор, запрашивающий выполнение операции считывания, передаются устройствами, отслеживающими состояние всех имеющихся кэшей, которые в мультипроцессорной компьютерной системе соединены с другими процессорами. Такие ответы формируются в соответствии с таблицей 1.

Сигналы в предлагаемой системе имеют форму 3-разрядного отслеживающего ответа, значение (адрес ответа) и определение которого приведены в таблице 1. Эти сигналы закодированы и показывают после соединения с адресом полученный при отслеживании результат. В таблице 1 имеются ответы, аналогичные ответам в известных системах, с определениями "совместное", "вмешательство в измененном состоянии", "нуль или очистка" и "повторная попытка". В таблице 1 имеются также три новых ответа: "вмешательство в совместном состоянии", "состояние удаления" и "перезапуск". Ответ "состояние удаления", используемый только для считывания, служит для того, чтобы показать, что считывание будет успешным, и ответ связности с состоянием "совместное" или "исключительное" будет получен позже с использованием данных другого сигнала. Ответ "перезапуск" используется в тех случаях, когда ответ связности не может быть получен сразу, и запрос должен быть направлен в нижние уровни иерархии памяти. Ответ "перезапуск" отличается от ответа "повторная попытка" тем, что он требует повторной выдачи сообщения, которое должно иметь тот же идентификатор, т.е. должно быть согласовано с предыдущим отправленным ранее сообщением.

Ответ "вмешательство в совместном состоянии" означает, что кэш служит источником информации и имеет копию данных или команды, которые еще должны быть изменены, и этим такой ответ отличается от известного ответа "вмешательство в измененном состоянии". Ответ ""вмешательство в совместном состоянии" может, таким образом, использоваться с любым состоянием, показывающим наличие неизмененной информации, включая "совместное" или "исключительное" состояние, а также новое состояние (состояние R, обозначающего последнее считывание (от англ. Recently read)), о котором сказано ниже. Этот ответ предлагает запрашивающему процессору обратиться для считывания данных или команд к шине (общей схеме внутренних соединений), которая распознает его по идентификатору запроса и сигнализирует о том, что искомая информация находится в кэше, а не в системной памяти. Термин "шина" используется в самом общем смысле, и в системе может быть несколько "шин", таких как "отслеживающая" шина для задержанных ответов и сообщений, и одна или несколько других информационных шин, соединенных друг с другом в точке пересечения (узле).

Ответ маркируется (тегируется) 8-разрядным маркирующим значением на отдельной предназначенной для этого шине тегов данных, которая отслеживает информационную шину циклически. Маркирующее значение на такой шине тегов данных показывает, что данные на информационной шине принадлежат сообщению с тем же маркировочным значением, что и сообщение, посланное на адресную шину. В системе используется дополнительный сигнал "данные принадлежат кэш, а не системной памяти" (DCache (от англ. data cache)), который появляется во время вмешательства и показывает, что эти данные содержатся в кэше, а не в системной памяти. Системная память или кэш могут теоретически начать посылать данные до того, как ответ на вмешательство будет рассмотрен запрашивающим устройством, и поэтому появление сигнала "DCache" говорит о передаче последних данных, а при его отсутствии запрашивающее устройство должно ожидать ответа для того, чтобы увидеть, произошло ли вмешательство или нет, и если произошло, то не использовать старые данные и ожидать данные, маркированные сигналом "DCache" (и отмеченные тем же тегом данных). Кроме того, такой новый ответ информирует системную память о необходимости прекращения запроса на чтение, поскольку он может быть удовлетворен вмешательством другого кэша. Поскольку быстродействие кэша может значительно превышать быстродействие системной памяти, характеристики считывания при таком протоколе могут быть существенно улучшены.

Искомую информацию можно связать с каждым ответом для того, чтобы позволить системной логике определить, какой из ответов имеет более высокий приоритет, и найти единственный ответ запрашивающему информацию процессору, как показано в таблице 1. Если, например, один или несколько кэшей отвечают "вмешательство в совместном состоянии" (приоритет 3), а один или несколько кэшей отвечают "повторная попытка " (приоритет 1), то последний ответ, который имеет более высокий приоритет, будет передан системной логикой запрашивающему информацию процессору. Системная логика может находиться в различных компонентах системы, например в блоке управления системой или даже в контроллере памяти. Первичные значения приоритета, показанные в таблице 1 слева, говорят о том, что самый высокий приоритет, как и в известных системах, имеет ответ "повторная попытка". Однако можно предложить и альтернативную схему приоритетов, включив в нее содержащийся в протоколе ответ "вмешательство в совместном состоянии". В этом случае, для которого приоритеты в таблице 1 указаны числами в скобках, ответ "вмешательство в совместном состоянии" имеет наибольший приоритет, а за ним в порядке убывания приоритетов следуют ответы "повторная попытка" и "вмешательство в измененном состоянии". Все остальные ответы имеют такие же приоритеты, как в первом варианте. В альтернативном варианте ответ "вмешательство в совместном состоянии" всегда будет иметь более высокий приоритет, чем другие ответы, что можно считать вполне допустимым по многим причинам. Прежде всего, если на шине кэшей содержится информация (данные или команда) в состоянии "совместное", то ни один другой кэш не может содержать информацию, соответствующую тому же адресу, но находящуюся в состоянии "измененное", и в этом случае ни один другой кэш не может выдать ответ "вмешательство в измененном состоянии". Аналогичным образом, если любой другой кэш осуществляет повторную попытку, то любой последующий ответ от нее, полученный в результате этой попытки, в большинстве случаев будет "совместное", что позволяет снова поставить на первое место ответ "вмешательство в совместном состоянии".

В настоящем изобретении могут найти применение различные способы решения вопроса, какой из кэшей является так называемым "владельцем" неизмененной информации и, следовательно, может служить ее источником. Если компьютерная система использует известный протокол MESI, показанный на фиг.2, и кэш содержит информацию в состоянии "исключительное", то этот кэш является единственным, который содержит годную (действительную) копию информации. Очевидно, что этот кэш является владельцем информации и может выдать ответ "вмешательство в совместном состоянии". Если, однако, кэш содержит информацию в состоянии "совместное", то тогда эта информация в таком же состоянии содержится по крайней мере еще в одном кэше. Поэтому сразу не ясно, какой кэш может служить источником информации. Существует несколько возможностей для определения того, какой из всех кэшей следует считать источником искомой информации. Например, несколько кэшей могут ответить "вмешательство в совместном состоянии", и в этом случае системная логика (например, блок управления системой) может выбрать тот кэш, который будет источником искомой информации. При этом система может возвратить ответ "повторная попытка" всем кэшам, за исключением того, который является потенциальным владельцем, и возвратить ответ "вмешательство в совместном состоянии" только выбранному владельцу. Владельца можно выбрать произвольно либо с использованием фиксированной или циклической схемы приоритетов.

Другой способ определения владельца среди многих кэшей, содержащих информацию в состоянии "совместное", заключается в создании механизма определения того кэша, который последним из всех кэшей считал с шины кэшей искомую информацию. Этот кэш затем автоматически рассматривается в качестве владельца этой шины до тех пор, пока другой кэш не обратиться на шину для считывания или запрос на чтение не будет сброшен. Такой способ может быть реализован на основе нового протокола связности кэшей, показанного на диаграмме состояний, изображенной на фиг.3. Этот протокол аналогичен известному протоколу MESI, показанному на фиг. 2, т. е. он содержит те же 4 состояния ("измененное", "исключительное", "совместное", "недействительное"), к которым добавлено новое состояние R ("недавнее" (от англ. recently)), которое используется для определения состояния кэша, который считывал информацию и который иначе будет считаться находящимся в состоянии "совместное". Другими словами, когда два или несколько кэшей содержат действительную копию команды или информации, то все они будут находиться в состоянии "совместное", за исключением того кэша, который последним обращался к этой команде или данным, и такой кэш будет находиться в состоянии "недавнее". Поскольку в данном случае в протоколе имеется 5 возможных состояний, для определения того, в каком конкретно состоянии находится каждый кэш, каждый содержащийся в кэшах элемент должен дополнительно иметь 3-битовое поле (вместо 2-битового поля в известной системе).

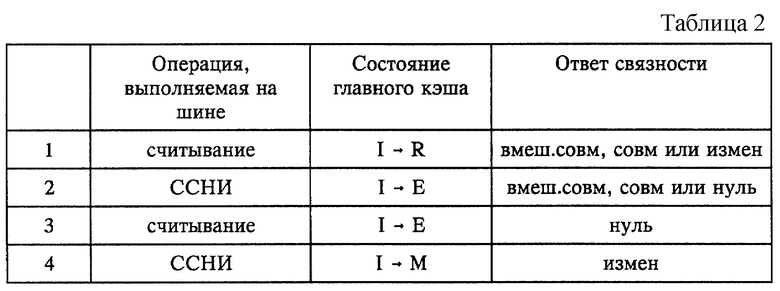

Этот новый протокол называется протоколом R-MESI. Как и в известном протоколе, четыре указанных в нем состояния M-E-S-I могут меняться в соответствии с первоначальным состоянием элемента и типом обращения запрашивающего информацию процессора. Способ изменения этих четырех состояний в принципе не отличается от известного (для протокола MESI), за исключением следующего. В таблице 2 показаны изменения состояний главного кэша для операций считывания при наличии "неудачи" (т.е. при безрезультатном обращении в кэш).

Состояние "недавнее" вводится при выполняемой на шине операции "неудача чтения" (первый ряд таблицы 2) при ответе связности "измененное" (измен), "совместное" (совм) или "вмешательство в совместном состоянии" (вмеш.совм); при ответе "измененное" в операции "неудача чтения" кэш с измененным состоянием посылает команду или данные и в системную память и тем самым перестает находиться в состоянии "измененное". При отсутствии ответа связности (нуль) в операции "неудача чтения" (третий ряд таблицы 2) вводится, как и в известном протоколе MESI, состояние "исключительное". При операции "неудача ССНИ" (где аббревиатура ССНИ означает "считывание с намерением изменить") вводится состояние "исключительное" при ответе связности "вмеш.совм", "совм" или нуль (второй ряд таблицы 2), а состояние "измененное" вводится при ответе связности "измен" (четвертый ряд таблицы 2). Операции ССНИ применяются только в отношении данных или команд, которые еще только готовятся к выполнению, поскольку готовые к выполнению команды обычно не изменяются.

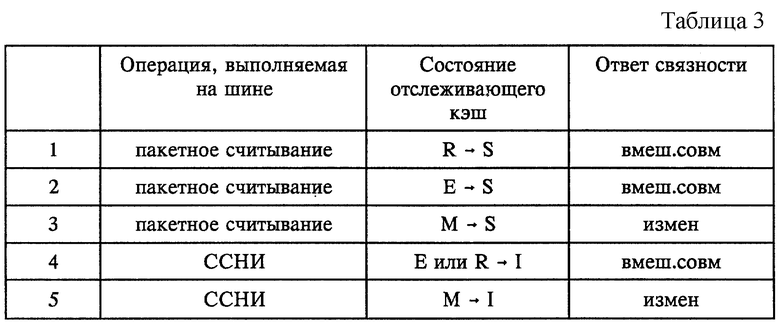

В таблице 3 показан пример того, каким образом транзакции на шине влияют на кэш, работающий в режиме отслеживания при выполнении операций считывания (т.е. при результативном обращении в кэш для чтения).

Для начальных состояний "исключительное" и "недавнее" (первый, второй и четвертый ряды таблицы 3) кэш передает ответ связности "вмешательство в совместном состоянии", означающий, что он будет посылать свою копию команды или данных напрямую в запрашивающий процессор путем вмешательства, минуя системную память. В любом случае при передаче команды таким путем следующим состоянием становится состояние "совместное" (первый и второй ряды таблицы 3) при выполнении операции "результативное считывание" или состояние "недействительное" (четвертый ряд таблицы 3) при выполнении операции "результативное ССНИ". В тех случаях, когда начальным состоянием является "измененное" (третий и пятый ряды таблицы 3), что, как уже указывалось выше, невозможно для программных команд, которые обычно не изменяются, ответом связности будет ответ "измененное", результатом чего является дальнейшее вмешательство. При выполнении на шине операции "ССНИ" значимая информация только передается от одного кэша к другому, а при операции "считывание" информация посылается и в кэш, и в системную память.

Как уже было отмечено выше, для состояний и операций, не показанных в таблицах 2 и 3, переходы от одного состояния к другому и ответы связности определяются в соответствии с протоколом, отличающимся от известного протокола MESI одной особенностью, заключающейся в том, что элемент в кэше может иметь состояние R, при котором можно выполнить операцию записи, и этот элемент будет переходить в состояние "измененное" аналогично тому, как он переходит в состояние "измененное" из состояния "совместное" во время выполнения операции записи. В отношении протокола R-MESI следует отметить следующее: элемент в кэше никогда не может перейти из состояния "недействительное" в состояние "совместное" (вместо этого произойдет переход к состоянию "недавнее"), элемент никогда не может перейти из состояния "исключительное" к состоянию "недавнее" (вместо этого произойдет переход к состоянию "совместное"), элемент никогда не может перейти из состояния "недавнее" к состоянию "исключительное" (точно так же, как из состояния "совместное" он не может перейти к состоянию "исключительное") и элемент никогда не может перейти из состояния "измененное" к состоянию "недавнее" (он будет переходить к состоянию "совместное", при этом элемент в кэше запрашивающего процессора будет переходить в состояние "недавнее").

При таком новом протоколе R-MESI владельцем требуемого блока информации становится кэш, который последним считывает содержащиеся в этом блоке команды или данные, что дополнительно увеличивает преимущества предлагаемого способа, предусматривающего сохранение наиболее новой по использованию информации и тем самым уменьшение вероятности ее перемещения, если используется механизм замещения наиболее давней по использованию информации в кэшах (алгоритм LRU). Состояние R кэша можно также успешно использовать и в других целях, например в интеллектуальном контроллере ввода-вывода (I/O), управляющем прерываниями системы процессор/кэш, которая последней считывает информацию из ячейки кэша о состоянии ввода-вывода, поскольку эта система процессор/кэш обычно имеет сохраняемую в кэше программу драйвера ввода-вывода и, следовательно, может запускать выполнение этой программы быстрее, чем другой процессор, для которого необходимо вызвать такую программу в его кэш.

За счет предоставления совместным командам и данным (т.е. командам или данным, которые достоверно содержатся более чем в одном кэше) возможности вмешательства быстродействие памяти значительно повышается. По одной из оценок использование протокола R-MESI по сравнению с известным протоколом MESI увеличивает быстродействие памяти по существующим стандартным тестам с 5300 Т/минС до 7500 Т/минС (транзакций класса С в минуту). За счет этого настоящее изобретение позволяет разгрузить контроллер памяти и снизить требования к числу каналов обращения к памяти, соответственно к пропускной способности памяти.

Хотя выше изобретение описано на примере конкретных вариантов его выполнения, они не ограничивают объем изобретения. Для специалистов в данной области техники очевидна не только возможность внесения в описанные варианты различных изменений, но и возможность создания на его основе других альтернативных вариантов. Однако все такие изменения и альтернативные варианты не должны нарушать основной идеи изобретения и не должны выходить за объем изобретения, определяемый приведенной ниже формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЬЮТЕРНАЯ СИСТЕМА И СПОСОБ ПЕРЕДАЧИ ДАННЫХ В КОМПЬЮТЕРНОЙ СИСТЕМЕ | 1999 |

|

RU2220444C2 |

| СИСТЕМА И СПОСОБ ЭФФЕКТИВНОГО ИСПОЛЬЗОВАНИЯ КЭШ-ПАМЯТИ В РАСПРЕДЕЛЕННОЙ ФАЙЛОВОЙ СИСТЕМЕ | 1994 |

|

RU2170454C2 |

| ВЫСОКОСКОРОСТНОЕ УПРАВЛЕНИЕ БЛОКИРОВКАМИ ДЛЯ МГНОВЕННОГО КОПИРОВАНИЯ В СИСТЕМАХ ХРАНЕНИЯ ДАННЫХ С СОВМЕСТНЫМ ИСПОЛЬЗОВАНИЕМ ПАМЯТИ N УЗЛАМИ | 2003 |

|

RU2297662C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ПРЯМОГО ДОСТУПА (DASD) ЕМКОСТЬЮ БОЛЬШЕ 528 МЕГАБАЙТ И СПОСОБ ЕГО ВОПЛОЩЕНИЯ ДЛЯ ПЕРСОНАЛЬНЫХ КОМПЬЮТЕРОВ | 1994 |

|

RU2155369C2 |

| ПРЕОБРАЗОВАНИЕ ИНИЦИИРУЕМОГО СООБЩЕНИЯМИ ПРЕРЫВАНИЯ В УВЕДОМЛЕНИЕ О ГЕНЕРИРОВАННОМ АДАПТЕРОМ ВВОДА-ВЫВОДА СОБЫТИИ | 2010 |

|

RU2546561C2 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ ЗАПРОСОВ НА ДОСТУП К ШИНЕ | 1990 |

|

RU2067314C1 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2111532C1 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2110839C1 |

| РАСШИРЕНИЕ СОГЛАСУЮЩЕГО ПРОТОКОЛА ДЛЯ ИНДИКАЦИИ СОСТОЯНИЯ ТРАНЗАКЦИИ | 2015 |

|

RU2665306C2 |

| КОНФИГУРАЦИЯ АРХИТЕКТУРНОГО РЕЖИМА В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ | 2015 |

|

RU2664413C2 |

Изобретение относится к компьютерным системам, в частности к способу выполнения операций считывания из памяти в симметричных мультипроцессорных компьютерных системах. Техническим результатом изобретения является разработка усовершенствованного способа выполнения операций считывания в мультипроцессорной компьютерной системе. Предложено после загрузки информации из системной памяти по крайней мере в два кэша последние маркировать как содержащие совместные неизмененные копии информации, и, когда запрашивающий процессор посылает сообщение, показывающее, что он хочет считать информацию, один определенный кэш выдает ответ, указывающий на то, что он является источником информации. Этот ответ передается кэшу, извлекающему сообщения из схемы внутренних соединений, которая соединена с запрашивающим процессором. Ответ обнаруживается системной логикой и направляется из нее в запрашивающий процессор. Кэш затем выдает информацию в схему внутренних соединений, которая соединена с запрашивающим процессором. Системная память обнаруживает сообщение и в норме служит источником информации, при этом, однако, ответ информирует запоминающее устройство системы также о том, что вместо него источником информации служит кэш. Поскольку запаздывание в сверхоперативной памяти можно сделать меньшим запаздывания в системной памяти, то использование такого нового протокола позволяет существенно улучшить эффективность считывания. 4 с. и 30 з.п.ф-лы, 3 ил., 3 табл.

| AL-SADOUN Н | |||

| В | |||

| ЕТ AL | |||

| CACHE COHERENCY IN MULTIPLE BUS SYSTEM" INTERNATIONAL JOURNAL OF ELECTRONICS | |||

| Vol | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| JP 8328957 A2, 13.12.1996 | |||

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1992 |

|

RU2060538C1 |

Авторы

Даты

2002-06-20—Публикация

1998-04-03—Подача