Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для перевода чисел из кода системы остаточных классов (СОК) в код полиадической системы счисления (ПСС).

Известно устройство (аналог) [1, с. 190, рис. 4, 3], содержащее n входных регистров (n - число оснований в СОК), мультиплексоры, элемент задержки на ]log2n[ тактов, (n-1) блоков суммирования вычетов, две схемы сравнения с константами, n постоянных запоминающих устройства, (4n-6) -разрядный регистр, регистр младшей цифры полиадического кода, (n-1) счетчиков и логическую схему. Недостаток устройства - низкое быстродействие преобразования чисел из кода СОК в код ПCC.

Известно также устройство (аналог) [2, с. 23, рис.2, 4], содержащее  сумматоров и

сумматоров и  узлов перекодировки. Недостаток устройства - низкое быстродействие преобразования чисел из кода СОК в код ПСС.

узлов перекодировки. Недостаток устройства - низкое быстродействие преобразования чисел из кода СОК в код ПСС.

Наиболее близким по технической сущности (прототипом к предлагаемому изобретению) является устройство (авт. св. СССР 1817246, МКИ Н 03 М 7/18, Б. И. 19, 1993 г.), содержащее 2 триггера, элемент И, 2 счетчика, 2 дешифратора, n входных регистров, группу элементов И, n шифраторов, дополнительный регистр, (n-1) сумматоров по модулям и ключ.

Недостаток прототипа - низкое быстродействие, так как для преобразования чисел из кода СОК в код ПСС в нем требуется время, равное τΣ•n, которое ограничено длительностью одного такта работы прототипа - τΣ.

Задача, на решение которой направлено заявляемое устройство, состоит в повышении производительности перспективных образцов вычислительной техники.

Технический результат выражается в повышении быстродействия преобразования чисел из кода СОК в код ПСС.

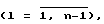

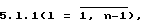

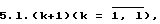

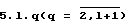

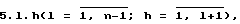

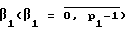

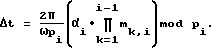

Технический результат достигается тем, что в устройство, содержащее n входных регистров (n - число оснований в СОК), информационные входы которых являются входами устройства, а тактовые входы соединены с тактовым входом устройства, введены генератор гармонического сигнала, (n-1) групп управляемых фазовращателей, содержащих по (l+1) (l - номер группы управляемых фазовращателей,  ) управляемых фазовращателей в каждой группе, и (n-1) измерителей фазы гармонического сигнала, причем в l-й группе управляемых фазовращателей первый вход первого управляемого фазовращателя группы соединен с выходом генератора гармонического сигнала, выход k-го

) управляемых фазовращателей в каждой группе, и (n-1) измерителей фазы гармонического сигнала, причем в l-й группе управляемых фазовращателей первый вход первого управляемого фазовращателя группы соединен с выходом генератора гармонического сигнала, выход k-го  управляемого фазовращателя группы - с первым входом (k+1)-гo управляемого фазовращателя группы, выход (l+1)-го управляемого фазовращателя группы - с первым входом l-го

управляемого фазовращателя группы - с первым входом (k+1)-гo управляемого фазовращателя группы, выход (l+1)-го управляемого фазовращателя группы - с первым входом l-го  измерителя фазы гармонического сигнала, ко второму входу которого подключен выход генератора гармонического сигнала, при этом выход первого входного регистра является первым выходом устройства, выход l-го измерителя фазы гармонического сигнала является (l+1)-м выходом устройства, второй вход первого управляемого (фазовращателя в l-й группе управляемых фазовращателей соединен с выходом (l+1)-го входного регистра, второй вход q-го

измерителя фазы гармонического сигнала, ко второму входу которого подключен выход генератора гармонического сигнала, при этом выход первого входного регистра является первым выходом устройства, выход l-го измерителя фазы гармонического сигнала является (l+1)-м выходом устройства, второй вход первого управляемого (фазовращателя в l-й группе управляемых фазовращателей соединен с выходом (l+1)-го входного регистра, второй вход q-го  управляемого фазовращателя l-й группы управляемых фазовращателей соединен с (q-1)-м выходом устройства.

управляемого фазовращателя l-й группы управляемых фазовращателей соединен с (q-1)-м выходом устройства.

В основу функционирования предлагаемого устройства положены следующие принципы.

В СОК число А представляется остатками (α1, α2...αn) от деления его на основания p1, p2. . . pn. В полиадической системе счисления то же число А представляется как

A = β1+β2p1+β3p1p2+...+βnp1p2...p(n-1), (1)

то есть для нахождения числа в ПСС необходимо знание коэффициентов  полиадического представления этого числа.

полиадического представления этого числа.

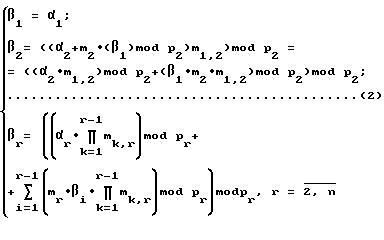

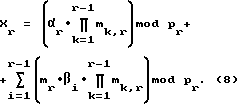

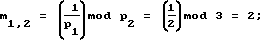

Перевод числа А из СОК в ПСС осуществляется по следующим формулам [2, с. 21-22]

где

Таким образом, для вычисления значения r-го разряда  полиадического представления числа А необходима сложить r чисел по модулю рr в соответствии с формулой (2).

полиадического представления числа А необходима сложить r чисел по модулю рr в соответствии с формулой (2).

Сущность изобретения заключается в кодировании значений остатков (α1, α2...αn) числа А фазой гармонического сигнала, управлении фазовым набегом этого сигнала в соответствии с алгоритмом преобразования чисел из кода СОК в код ПСС и определении результата преобразования путем измерения значения суммарного набега фазы.

Известно, что:

cos(x)=cos(x+π2k)=cos((x)mоd 2π), (3)

где k=1, 2, 3.

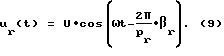

Если гармонический сигнал с амплитудой U и частотой ω

u(t)=U cos(ωt) (4)

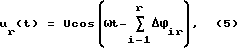

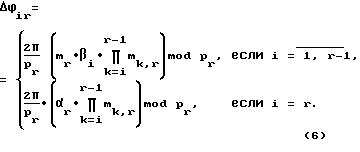

проходит через r последовательно соединенных фазовращателей, то на выходе последнего (r-го) фазовращателя гармонический сигнал будет описываться выpажением

где Δϕir- сдвиг фазы в i-м фазовращателе,

Пусть

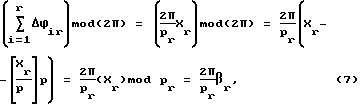

Тогда с учетом (3), (5) и (6) получим

где

Таким образом (5) с учетом (2), (7) и (8) можно представить в виде

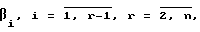

Следовательно, после прохождения гармонического сигнала через r фазовращателей, сдвиги фазы в которых установлены в соответствии с (6), фаза гармонического сигнала (9) на выходе r-го фазовращателя будет прямо пропорциональна значению r-го разряда  полиадического представления числа A (2).

полиадического представления числа A (2).

Для определения βr необходимо измерить величину сдвига фазы гармонического сигнала ur(t) (9) относительно u(t) (4). Измеритель фазы гармонического сигнала можно построить на основе оптимального измерителя параметра сигнала известной формы [3, с, 488, рис. 12,1].

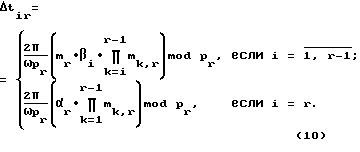

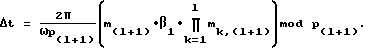

Управляемые фазовращатели могут быть реализованы на основе различных схемных решений. Например, в СВЧ диапазоне [4, с.102] такой фазовращатель наиболее просто реализовать на основе линий задержки (ЛЗ) на время

Действительно, если на входе ЛЗ на время Δtir действует гармонический сигнал

u(t)=Ucos(ωt),

то на выходе ЛЗ с учетом (6) и (10) будет сигнал

uл3(t) = Ucos(ω(t-Δtir)) = Ucos(ωt-Δϕir). (11)

Следовательно, подключая соответствующую ЛЗ в зависимости от значения унитарного кода αr или  можно получить значение фазового сдвига в i-м фазовращателе, прямо пропорциональное (6).

можно получить значение фазового сдвига в i-м фазовращателе, прямо пропорциональное (6).

Как отмечалось выше, время преобразования чисел из СОК в ПСС в прототипе составляет TПр= n•τΣ. Длительность одного такта τΣ работы прототипа примерно равна длительности выполнения операции сложения в двоичном сумматоре.

Как показано в [5, с. 138],

τΣ = 4•τлэ, (12)

где τлэ- время переключения полупроводникового логического элемента. С учетом изложенного

TПр = 4•n•τлэ. (13)

Время τлэ≈10-10 с является практическим пределом для полупроводниковых логических элементов, которое достигается только при жидкостном охлаждении до криогенных температур [6].

Поэтому, минимальное время преобразования чисел из СОК в ПСС в прототипе на основании (13) составляет

ТПрmin≈4•n•10-10 с. (14)

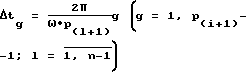

Время преобразования чисел из СОК в ПСС в предлагаемом устройстве (ТПУ) на основании вышеизложенного определяется временем формирования числа в старшем разряде ПСС и равно сумме времени задержки гармонического сигнала в n управляемых фазовращателях (n•τфв), времени коммутации линий задержки в n управляемых фазовращателях (n•τк) и времени измерения значения сдвига фазы в (n-1) измерителях фазы гармонического сигнала ((n-1)τизм). Тогда

TПУ = n•τФВ+n•τК+(n-1)τизм. (15)

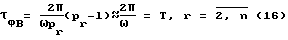

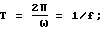

Максимальное время задержки в управляемом фазовращателе на ЛЗ с учетом (10) равно

где  f - несущая частота гармонического сигнала, Гц.

f - несущая частота гармонического сигнала, Гц.

Время коммутации линий задержки в управляемых фазовращателях τК при реализации коммутаторов, например, на СВЧ диодах, будет не более 10-11 с, то есть τК≈10-11c.

Если измеритель фазы гармонического сигнала построен на основе оптимального измерителя параметра сигнала известной формы [3, с.488, рис. 12.1], то, как следует из его структурной схемы, τизм равно сумме времени интегрирования ТИ в интеграторах измерителя фазы и времени принятия решения о значении фазы в решающем устройстве τру.

Измерение значения фазы гармонического сигнала (9) относительно сигнала (4) в измерителе фазы гармонического сигнала происходит путем сравнения фазы сигнала (9) с фазами рr,  опорных сигналов, формируемых из сигнала (4). Фазы опорных сигналов должны быть равны:

опорных сигналов, формируемых из сигнала (4). Фазы опорных сигналов должны быть равны:

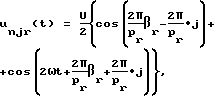

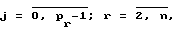

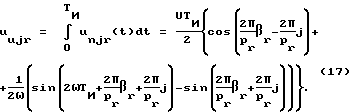

Алгоритм такого сравнения [3] заключается в перемножении гармонического сигнала (9), снимаемого с выхода r-го  управляемого фазовращателя, с опорными сигналами, интегрировании результата перемножения и принятии решения о значении сдвига фазы сигнала (9) относительно сигнала (4) путем определения в решающем устройстве канала, на выходе интегратора которого результат будет максимальным. Результат перемножения гармонического сигнала (9) c j-м опорным сигналом можно записать в виде

управляемого фазовращателя, с опорными сигналами, интегрировании результата перемножения и принятии решения о значении сдвига фазы сигнала (9) относительно сигнала (4) путем определения в решающем устройстве канала, на выходе интегратора которого результат будет максимальным. Результат перемножения гармонического сигнала (9) c j-м опорным сигналом можно записать в виде

(при выводе формулы unj(t) полагалось, что амплитуда опорного сигнала равна единице.)

где  фаза j-го опорного сигнала.

фаза j-го опорного сигнала.

После интегрирования unjr(t) в интеграторе, получим

Так как ω≫1, то из (17) видно, что уже при ТИ≥(2...3)•Т

причем uujr будет максимальным для j = βr. С учетом изложенного, при расчете времени преобразования чисел из СОК в ПСС возьмем значение

ТИ=3Т. (18)

И, наконец, время принятия решения τру соизмеримо со временем переключения полупроводниковых логических элементов τру = τлэ, которое в расчетах возьмем равным:

τру = τлэ = 10-10c. (19)

Таким образом, с учетом (15), (16), (18) и (19)

TПУ = n•T+n•τК+(n-1)(3T+τЛЭ). (20)

Уже сейчас на практике реализованы вплоть до 100... 150 ГГц типовые радиотехнические элементы (в том числе и в интегральном исполнении) [4], из которых состоят управляемые фазовращатели и измеритель фазы гармонического сигнала. Следовательно при f=100 ГГц = 1011 Гц.

ТПУ=n•10-11+n•10-11+(n-1)(3•10-11+10-10)=(1,5n-1,3)•10-10 с. (21)

Из (21) и (14) следует, что в рамках сформулированных допущений о составе сравниваемых устройств, предлагаемое устройство предпочтительнее прототипа, так как ТПУ<ТПР.

На фиг. 1 представлена структурная схема устройства для преобразования чисел из кода системы остаточных классов в полиадический код, где l.l-l.n - входы устройства (n - число оснований в СОК), 2.l-2.n - входные регистры, 3 - тактовый вход устройства, 4 - генератор гармонического сигнала, 5.l.r - управляемый фазовращатель  6.l - измеритель фазы гармонического сигнала

6.l - измеритель фазы гармонического сигнала  7.l-7.n - выходы устройства.

7.l-7.n - выходы устройства.

Входы устройства 1.1. -l. n соединены с информационными входами соответствующих входных регистров 2.1-2.n, тактовые входы которых соединены с тактовым входом устройства 3, причем выход генератора гармонического сигнала 4 соединен с первым входом управляемого фазовращателя  выход управляемого фазовращателя 5.l.k подключен к первому входу управляемого фазовращателя

выход управляемого фазовращателя 5.l.k подключен к первому входу управляемого фазовращателя  выход управляемого фазовращателя 5.1. (l+1) - к первому входу измерителя фазы гармонического сигнала 6.1, ко второму входу которого подключен выход генератора гармонического сигнала 4, при этом выход входного регистра 2.l является выходом 7.l устройства, выход измерителя фазы гармонического сигнала 6.1 является выходом 7.(l+1 ) устройства, второй вход управляемого фазовращателя 5.1.1 соединен с выходом входного регистра 2.(l+l), второй вход управляемого фазовращателя

выход управляемого фазовращателя 5.1. (l+1) - к первому входу измерителя фазы гармонического сигнала 6.1, ко второму входу которого подключен выход генератора гармонического сигнала 4, при этом выход входного регистра 2.l является выходом 7.l устройства, выход измерителя фазы гармонического сигнала 6.1 является выходом 7.(l+1 ) устройства, второй вход управляемого фазовращателя 5.1.1 соединен с выходом входного регистра 2.(l+l), второй вход управляемого фазовращателя  подключен к выходу 7.(q-1) устройства.

подключен к выходу 7.(q-1) устройства.

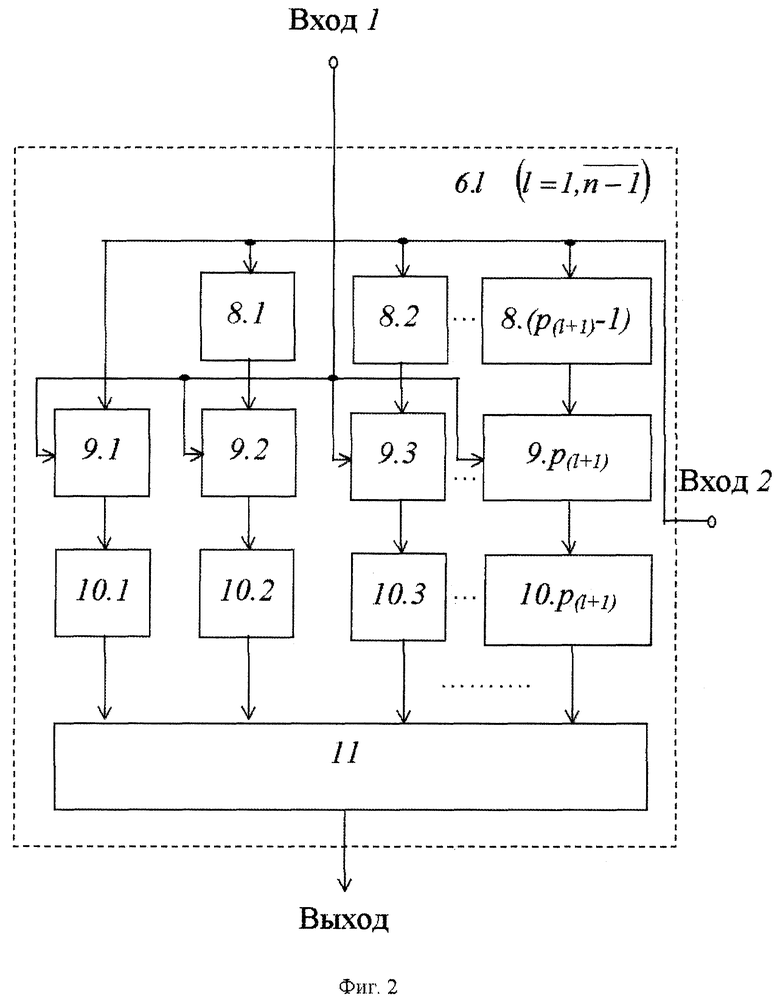

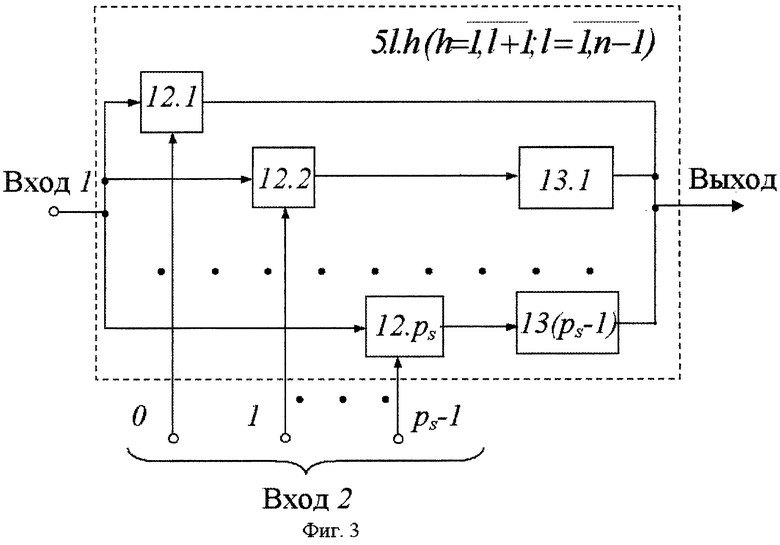

Реализация основных узлов устройства представлена на фиг.2 и фиг.3.

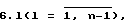

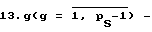

На фиг. 2 представлена структурная схема измерителя фазы гармонического сигнала  где 8.g - линия задержки на время

где 8.g - линия задержки на время

аналоговые умножители, 10.1-10.p(l+l) - интеграторы, 11 решающее устройство.

аналоговые умножители, 10.1-10.p(l+l) - интеграторы, 11 решающее устройство.

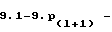

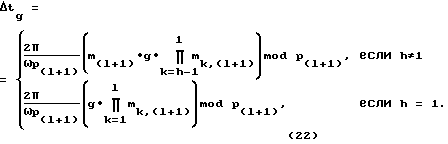

На фиг. 3 представлена структурная схема управляемого фазовращателя  где 12.1-12.pS - коммутаторы гармонического сигнала,

где 12.1-12.pS - коммутаторы гармонического сигнала,

линия задержки на время:

линия задержки на время:

Рассмотрим работу устройства:

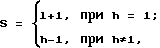

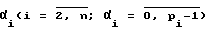

Остатки (α1, α2,...,αn) числа А в СОК в унитарном коде по входам 1.1-l.n подаются на информационные входы соответствующих регистров 2.1-2.n. С приходом тактового сигнала на вход 3 устройства, значения

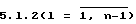

α1, α2,..., αn записываются в регистры 2.1-2.n. С выхода регистра 2.1 унитарный код числа β1 = α1 (первого разряда полиадического кода числа А) поступает на выход 7.l устройства и одновременно на входы 2 управляемых фазовращателей 5.1.2-5.(n-1).2.

Под управлением унитарного кода числа  открывается соответствующий коммутатор гармонического сигнала 12.(β1+1) в управляемом фазовращателе

открывается соответствующий коммутатор гармонического сигнала 12.(β1+1) в управляемом фазовращателе  и вход l этого фазовращателя, как следует из (22), подключится к выходу управляемого фазовращателя непосредственно (при β1= 0), либо через линию задержки 13.(β1)(при β1≠0) на время

и вход l этого фазовращателя, как следует из (22), подключится к выходу управляемого фазовращателя непосредственно (при β1= 0), либо через линию задержки 13.(β1)(при β1≠0) на время

Одновременно с выхода регистров 2.2-2.n унитарный код чисел α1-αn соответственно поступает на входы 2 управляемых фазовращателей 5.1.1-5.(n-l). 1. Под управлением унитарного кода числа  откроется соответствующий коммутатор гармонического сигнала 12.(αi+1) в управляемом фазовращателе 5.(i-l).l и вход l этого фазовращателя, как следует из (22), подключится к выходу управляемого фазовращателя непосредственно (при αi = 0), либо через линию задержки 13.(αi)(при αi ≠ 0) на время

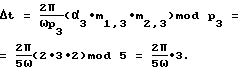

откроется соответствующий коммутатор гармонического сигнала 12.(αi+1) в управляемом фазовращателе 5.(i-l).l и вход l этого фазовращателя, как следует из (22), подключится к выходу управляемого фазовращателя непосредственно (при αi = 0), либо через линию задержки 13.(αi)(при αi ≠ 0) на время  Фазовый набег гармонического сигнала, снимаемого с выхода генератора 4, после прохождения последовательно через управляемые фазовращатели 5.1.1 и 5.1.2 в соответствии с (2), (7)-(10) и (22) будет равен

Фазовый набег гармонического сигнала, снимаемого с выхода генератора 4, после прохождения последовательно через управляемые фазовращатели 5.1.1 и 5.1.2 в соответствии с (2), (7)-(10) и (22) будет равен

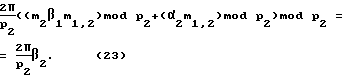

В измерителе фазы 6.1 происходит сравнение фазы гармонического сигнала, снимаемого с выхода управляемого фазовращателя 5.1.2, с фазами опорных сигналов, соответственно равными

Через время t= ТИ= 3Т в измерителе фазы 6.1 на выходе интегратора 10.(β2+1) установится максимальное напряжение. В соответствии с этим на выходе решающего устройства 11 измерителя фазы 6.1 сформируется унитарный код β2 второго разряда полиадического представления числа А, который поступит на выход 7.2 устройства и на входы 2 управляемых фазовращателей 5.2.3-5.(n-1).3.

Под управлением унитарного кода числа β2 откроется соответствующий коммутатор гармонического сигнала 12.(β2+1) в управляемом фазовращателе  и вход 1 этого фазовращателя, как следует из (22), подключится к выходу управляемого фазовращателя 5.1.3 непосредственно (при β2 = 0), либо через линию задержки 13.(β2)(при β2≠0) на время

и вход 1 этого фазовращателя, как следует из (22), подключится к выходу управляемого фазовращателя 5.1.3 непосредственно (при β2 = 0), либо через линию задержки 13.(β2)(при β2≠0) на время

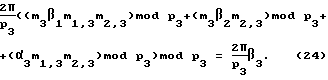

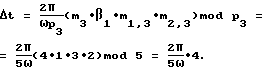

Фазовый набег гармонического сигнала, снимаемого с выхода генератора 4, после прохождения последовательно через управляемые фазовращатели 5.2.1, 5.2.2 и 5.2.3 в соответствии с (2), (7) (10) и (22) будет равен

Затем, подобно изложенному, в измерителе фазы 6.2 определяется унитарный код β3 третьего разряда полиадического представления числа А, который поступает на выход 7.3 устройства и на входы 2 управляемых фазовращателей 5.3.4 5. (n-l). 4. Аналогично определяются значения унитарных кодов β4, β5,..., βn старших разрядов полиадического представления числа А.

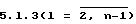

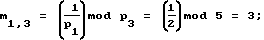

Пример. Пусть p1=2, р2=3, р3=5; А =23=(1, 2, 3). Тогда

m2 = p2-1 = 2; m3 = p3-1 = 4.

Код числа А= (1, 2, 3) в СОК поступает на входы 1.1-1.3 устройства. С приходом тактового сигнала на вход 3 устройства унитарные коды чисел α1 = 1, α2 = 2 и α3 = 3 запишутся соответственно в регистры 2.1, 2.2 и 2.3. С выхода регистра 2.1 унитарный код числа β1 = α1 = 1 поступает на выход 7.l устройства и одновременно на входы 2 управляемых фазовращателей 5.l.2 и 5.2.2. Под управлением унитарного кода числа β1 = 1 откроются коммутаторы гармонического сигнала 12.2 в управляемых фазовращателях 5.l.2 и 5.2.2 и их входы подключатся к выходам через линии задержки 13.1 соответственно на время

Одновременно с выхода регистров 2.2 и 2.3 унитарные коды чисел α2 = 2 и α3 = 3 поступают соответственно на входы 2 управляемых фазовращателей 5.1.1 и 5.2.1. Под управлением унитарного кода чисел α2 = 2 и α3 = 3 откроется соответственно коммутатор гармонического сигнала 12.3 в управляемом фазовращателе 5.l.l и коммутатор гармонического сигнала 12.4 в управляемом фазовращателе 5.2.1. Входы l этих фазовращателей подключатся к их выходу соответственно через линии задержки 13.2 и 13.3 на время

Фазовый набег гармонического сигнала, снимаемого с выхода генератора 4, после прохождения через управляемые фазовращатели 5.1.1 и 5.1.2 будет равен  На выходе интегратора 10.3 измерителя фазы 6.1 через время t=ТИ=3Т установится максимальное напряжение. В соответствии с этим на выходе решающего устройства 11 измерителя фазы 6.1 сформируется унитарный код β2 = 2 второго разряда полиадического представления числа А, который поступит на выход 7.2 устройства и на вход 2 управляемого фазовращателя 5.2.3. Под управлением унитарного кода числа β2 = 2 откроется коммутатор гармонического сигнала 12.3 в управляемом фазовращателе 5.2.3 и вход l этого фазовращателя подключится к его выходу через линию задержки 13.2 на время

На выходе интегратора 10.3 измерителя фазы 6.1 через время t=ТИ=3Т установится максимальное напряжение. В соответствии с этим на выходе решающего устройства 11 измерителя фазы 6.1 сформируется унитарный код β2 = 2 второго разряда полиадического представления числа А, который поступит на выход 7.2 устройства и на вход 2 управляемого фазовращателя 5.2.3. Под управлением унитарного кода числа β2 = 2 откроется коммутатор гармонического сигнала 12.3 в управляемом фазовращателе 5.2.3 и вход l этого фазовращателя подключится к его выходу через линию задержки 13.2 на время

Фазовый набег гармонического сигнала, снимаемого с выхода генератора 4, после прохождения через управляемые фазовращатели 5.2.1, 5.2.2 и 5.2.3 будет равен  На выходе интегратора 10.4 измерителя фазы 6.2 через время t = 3Т установится максимальное напряжение. В соответствии с этим на выходе решающего устройства 11 измерителя фазы 6.2 сформируется унитарный код β3 = 3 третьего разряда полиадического представления числа А, который поступит на выход 7.3 устройства.

На выходе интегратора 10.4 измерителя фазы 6.2 через время t = 3Т установится максимальное напряжение. В соответствии с этим на выходе решающего устройства 11 измерителя фазы 6.2 сформируется унитарный код β3 = 3 третьего разряда полиадического представления числа А, который поступит на выход 7.3 устройства.

Таким образом, в результате сформируются следующие коэффициенты полиадического представления числа А: β1 = 1; β2 = 2; β3 = 3.

Проверка:

A = β1+β2•p1+β3•p1•p2 = 1+2•2+3•2•3 = 23;

α1 = (A)mod p1 = (23)mod 2 = 1;

α2 = (A)mod p2 = (23)mod 3 = 2;

α3 = (A)mod p3 = (23)mod 5 = 3.

Источники информации

1. Чернявский А. Ф., Данилевич В.В., Коляда А.А., Селянинов М.Ю. Высокоскоростные методы и системы цифровой обработки информации. - Минск: БГУ, 1996. - 376 с.

2. Долгов А. И. Диагностика устройств, функционирующих в системе остаточных классов. - М.: Радио и связь, 1982, 64 с.

3. Тихонов В.И. Статистическая радиотехника. - М.: Сов. Радио, 1966, 678 с.

4. Радиоприемные устройства: Учеб. пособие для радиотехнич. спец. вузов/Ю.Т. Давыдов, Ю.С. Данилич, А.П. Жуковский. - М.: Высш. шк., 1989, 342 с.

5. Карцев М. А., Брик В.А. Вычислительные системы и синхронная арифметика. - М.: Радио и связь, 1981. - 360 с.

6. Акаев А.А., Майоров С.А. Оптические методы обработки информации. - М. : Высшая шк., 1988, 237 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ n-РАЗРЯДНОГО ДВОИЧНОГО ПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД ОСТАТКА ПО МОДУЛЮ m | 2001 |

|

RU2192092C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2000 |

|

RU2188448C2 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2143723C1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЛА В МОДУЛЯРНОМ КОДЕ НА ОСНОВАНИЕ СИСТЕМЫ СЧИСЛЕНИЯ | 2002 |

|

RU2231822C2 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЛА В МОДУЛЯРНОМ КОДЕ НА ОСНОВАНИЕ СИСТЕМЫ СЧИСЛЕНИЯ | 2002 |

|

RU2237274C2 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2137181C1 |

| ФОРМИРОВАТЕЛЬ ПЕРИОДИЧЕСКИХ СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2003 |

|

RU2271602C2 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2004 |

|

RU2263948C1 |

| УСТРОЙСТВО ДЛЯ МАСШТАБИРОВАНИЯ ЧИСЛА В МОДУЛЯРНОЙ СИСТЕМЕ СЧИСЛЕНИЯ | 2002 |

|

RU2246753C2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ n-РАЗРЯДНОГО ДВОИЧНОГО ПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД ОСТАТКА ПО МОДУЛЮ m | 2003 |

|

RU2242085C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для перевода чисел из кода системы остаточных классов (СОК) в код полиадической системы счисления (ПСС). Техническим результатом является повышение быстродействия преобразования. Устройство содержит входные регистры, генератор гармонического сигнала, управляемые фазовращатели, измерители фазы гармонического сигнала. 3 ил.

Устройство для преобразования чисел из кода системы остаточных классов (СОК) в полиадический код, содержащее n входных регистров (n - число оснований в СОК), информационные входы которых являются входами устройства, а тактовые входы соединены с тактовым входом устройства, отличающееся тем, что в него введены генератор гармонического сигнала, (n-l) групп управляемых фазовращателей, содержащих по (1+1) (l - номер группы управляемых фазовращателей,  ) управляемых фазовращателей в каждой группе, и (n-l) измерителей фазы гармонического сигнала, причем в l-й группе управляемых фазовращателей первый вход первого управляемого фазовращателя группы соединен с выходом генератора гармонического сигнала, выход k-го

) управляемых фазовращателей в каждой группе, и (n-l) измерителей фазы гармонического сигнала, причем в l-й группе управляемых фазовращателей первый вход первого управляемого фазовращателя группы соединен с выходом генератора гармонического сигнала, выход k-го  управляемого фазовращателя группы - с первым входом (k+l)-го управляемого фазовращателя группы, выход (l+l)-го управляемого фазовращателя группы - с первым входом l-го

управляемого фазовращателя группы - с первым входом (k+l)-го управляемого фазовращателя группы, выход (l+l)-го управляемого фазовращателя группы - с первым входом l-го  измерителя фазы гармонического сигнала, ко второму входу которого подключен выход генератора гармонического сигнала, при этом выход первого входного регистра является первым выходом устройства, выход l-го измерителя фазы гармонического сигнала является (l+1)-м выходом устройства, второй вход первого управляемого фазовращателя в l-й группе управляемых (фазовращателей соединен с выходом (l+l)-го входного регистра, второй вход q-го

измерителя фазы гармонического сигнала, ко второму входу которого подключен выход генератора гармонического сигнала, при этом выход первого входного регистра является первым выходом устройства, выход l-го измерителя фазы гармонического сигнала является (l+1)-м выходом устройства, второй вход первого управляемого фазовращателя в l-й группе управляемых (фазовращателей соединен с выходом (l+l)-го входного регистра, второй вход q-го  управляемого фазовращателя l-й группы управляемых фазовращателей соединен с (q-1)-м выходом устройства.

управляемого фазовращателя l-й группы управляемых фазовращателей соединен с (q-1)-м выходом устройства.

| Устройство для прямого преобразования чисел из кода системы остаточных классов в полиадический код и обратно | 1990 |

|

SU1817246A1 |

| Устройство для перевода числа, представленного в системе остаточных классов, в полиадическую систему счисления | 1989 |

|

SU1619403A2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1991 |

|

RU2023346C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ОТ ЧИСЛА | 1999 |

|

RU2157589C1 |

| US 4963869 A, 16.11.1990 | |||

| УСТРОЙСТВО ДЛЯ ЗАГРУЗКИ СКИПОВ | 0 |

|

SU308963A1 |

Авторы

Даты

2002-08-20—Публикация

2001-04-25—Подача