Изобретение относится к вычислительной технике и предназначено для использования в цифровых вычислительных устройствах, а также в устройствах для формирования конечных полей.

Известно устройство [1], содержащее счетчик, два формирователя импульсов, пять элементов ИЛИ, элемент сравнения, вычитатель, семь регистров, три элемента И и мультиплексор. Недостаток устройства - низкое быстродействие формирования остатка.

Известно также устройство [2], содержащее два регистра, накапливающий сумматор по модулю, генератор тактовых импульсов, счетчик, мультиплексор, триггер, два элемента И, элемент ИЛИ и элемент задержки. Недостаток устройства - низкое быстродействие формирования остатка.

Наиболее близким по технической сущности (прототипом к предлагаемому изобретению) является устройство [3] , содержащее n-разрядный входной регистр, блок умножения на константу по модулю m, сумматор по модулю m, коммутатор, первый и второй регистры. Время формирования остатка по модулю в этом устройстве составляет tnp=]n/]log2m[[•τΣ, где].[ - символ округления в большую сторону до ближайшего целого числа; τΣ - время выполнения операции сложения двух ]log2m[ - разрядных чисел по модулю m.

Недостаток - большое время формирования остатка ввиду того, что оно ограничено временем выполнения операции сложения τΣ, зависящей от времени переключения логических элементов τлэ, не превышающим значение 10-10...10-9 с [4, c. 173].

Задача, на решение которой направлено заявляемое устройство, состоит в повышении производительности перспективных образцов вычислительной техники.

Технический результат выражается в повышении быстродействия формирования остатка по модулю m n-разрядного числа в двоичном позиционном коде.

Технический результат достигается тем, что в устройство, содержащее n-разрядный входной регистр, информационные входы которого являются входами устройства, а тактовый вход - тактовым входом устройства, введены генератор гармонического сигнала, n управляемых фазовращателей, измеритель фазы гармонического сигнала и шифратор, причем выход генератора гармонического сигнала соединен с первым входом первого управляемого фазовращателя, выход i-го управляемого фазовращателя - с первым входом (i+1)-го управляемого фазовращателя  выход n-го управляемого фазовращателя с первым входом измерителя фазы гармонического сигнала, ко второму входу которого подключен выход генератора гармонического сигнала, при этом выход измерителя фазы гармонического сигнала соединен со входом шифратора, выход которого является выходом устройства, а выход l-го разряда n-разрядного входного регистра

выход n-го управляемого фазовращателя с первым входом измерителя фазы гармонического сигнала, ко второму входу которого подключен выход генератора гармонического сигнала, при этом выход измерителя фазы гармонического сигнала соединен со входом шифратора, выход которого является выходом устройства, а выход l-го разряда n-разрядного входного регистра  подключен ко второму входу l-го управляемого фазовращателя.

подключен ко второму входу l-го управляемого фазовращателя.

На фиг. 1 представлена структурная схема предлагаемого устройства, где 1.1-1. n - входы устройства, 2 - n-разрядный входной регистр, 3 - тактовый вход устройства, 4 - генератор гармонического сигнала, 5.1-5.n - управляемые фазовращатели, 6 - измеритель фазы гармонического сигнала, 7 - шифратор, 8 - вход устройства.

Входы устройства 1.1-1. n соединены с соответствующими информационными входами n-разрядного входного регистра 2, тактовый вход которого подключен к тактовому входу устройства 3, при этом вход i-го разряда n-разрядного входного регистра 2 соединен со вторым входом управляемого фазовращателя 5.i  причем выход генератора гармонического сигнала 4 соединен с первым входом управляемого фазовращателя 5.(i+1),

причем выход генератора гармонического сигнала 4 соединен с первым входом управляемого фазовращателя 5.(i+1),  выход управляемого фазовращателя 5.n - с первым входом измерителя фазы гармонического сигнала 6, ко второму входу которого подключен выход генератор гармонического сигнала 4, а выход измерителя фазы гармонического сигнала 6 соединен со входом шифратора 7, выход которого является выходом 8 устройства.

выход управляемого фазовращателя 5.n - с первым входом измерителя фазы гармонического сигнала 6, ко второму входу которого подключен выход генератор гармонического сигнала 4, а выход измерителя фазы гармонического сигнала 6 соединен со входом шифратора 7, выход которого является выходом 8 устройства.

На фиг. 2 представлена структурная схема измерителя фазы гармонического сигнала 6, где 8.k - линия задержки на время  9.1-9. m - аналоговые умножители, 10.1-10. m - интеграторы, 11- решающее устройство.

9.1-9. m - аналоговые умножители, 10.1-10. m - интеграторы, 11- решающее устройство.

На фиг. 3 представлена структурная схема управляемого фазовращателя 5.i  где 12.1 - коммутатор, соединяющий вход 1 с выходом при βi = 0, 12.2 - коммутатор, соединяющий вход 1 со входом линии задержки 13.i

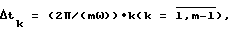

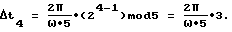

где 12.1 - коммутатор, соединяющий вход 1 с выходом при βi = 0, 12.2 - коммутатор, соединяющий вход 1 со входом линии задержки 13.i  при βi = l, 13.i - линия задержки на время Δti = 2π/(mω)•βi•(2i-l)modm.

при βi = l, 13.i - линия задержки на время Δti = 2π/(mω)•βi•(2i-l)modm.

Рассмотрим работу устройства.

Значения разрядов позиционного кода числа βi поступают на соответствующие входы 1.1-1. n устройства и соответственно на информационные входы n-разрядного входного регистра 2. С приходом тактового сигнала на вход 3 устройства, значения

поступают на соответствующие входы 1.1-1. n устройства и соответственно на информационные входы n-разрядного входного регистра 2. С приходом тактового сигнала на вход 3 устройства, значения  записываются в соответствующие разряды входного регистра 2. С выхода i-го разряда регистра 2 значение βi поступает на второй вход управляемого фазовращателя 5.i

записываются в соответствующие разряды входного регистра 2. С выхода i-го разряда регистра 2 значение βi поступает на второй вход управляемого фазовращателя 5.i  В соответствии со значениями разрядов βi коммутаторы 12.1 и 12.2 подключают вход 1 управляемого фазовращателя 5. i к его выходу непосредственно (при βi = 0), либо через линию задержки на время Δti = 2π/(mω)•βi•(2i-l) mod m (при βi = 1).

В соответствии со значениями разрядов βi коммутаторы 12.1 и 12.2 подключают вход 1 управляемого фазовращателя 5. i к его выходу непосредственно (при βi = 0), либо через линию задержки на время Δti = 2π/(mω)•βi•(2i-l) mod m (при βi = 1).

После прохождения гармонического сигнала с выхода генератора гармонического сигнала 4 через n управляемых фазовращателей 5.1-5-n на выходе управляемого фазовращателя 5.n суммарный набег фазы этого сигнала будет равен

В измерителе фазы 6 происходит сравнение фазы сигнала с выхода фазовращателя 5.n, поступающего на первый вход измерителя фазы 6, с фазой опорных сигналов (16).

Через время t=tu=3T в измерителе фазы 6 на выходе интегратора с номером 10. (p+1p)  установится максимальное напряжение. В соответствии с этим на выходе решающего устройства 11 сформируется унитарный код остатка α=A mod m, который затем преобразуется в шифраторе 7 в двоичный позиционный код и поступает на выход 8 устройства.

установится максимальное напряжение. В соответствии с этим на выходе решающего устройства 11 сформируется унитарный код остатка α=A mod m, который затем преобразуется в шифраторе 7 в двоичный позиционный код и поступает на выход 8 устройства.

Пример. Пусть n= 4; A=1210=11002; m=5. Двоичный четырехразрядный позиционный код числа A=11002 поступают на входы 1.1-1.4 устройства. С приходом тактового сигнала на вход 3 устройства значения разрядов β1 = 0, β2 = 0, β3 = 1, β4 = 1 запишутся в четырехразрядный входной регистр 2. Сигналы с выхода регистра 2(βi) откроют коммутаторы 12.1 в управляемых фазовращателях 5.1 и 5.2 и коммутаторы 12.2 в управляемых фазовращателях 5.3 и 5.4. Следовательно входы управляемых фазовращателей 5.1 и 5.2 подключаются непосредственно к их выходам, а входы управляемых фазовращателей 5.3 и 5.4 подключаются к их выходам соответственно через линии задержки на время

и

Фазовый набег гармонического сигнала, снимаемого с выхода генератора 4, после прохождения через управляемые фазовращатели 5.1-5.4 будет равен

На выходе интегратора 10.3 измерителя фазы 6 через время t=tu=3T установится максимальное напряжение. В соответствии с этим на выходе решающего устройства 11 измерителя фазы 6 сформируется унитарный код остатка α=2, который преобразуется в шифраторе 7 в двоичный позиционный код и поступит па выход 8 устройства.

Проверка: А=12; α=A mod 5=2.

Источники информации

1. А.с. СССР 1658388, МКИ Н 03 М 7/18, БИ 23, 1991.

2. Патент РФ 2023346, МКИ Н 03 М 7/18, БИ 21, 1994.

3. А.с. СССР 1322483, МКИ Н 03 М 7/18, БИ 25, 1987.

4. Акаев А.А., Майоров С.А. Оптические методы обработки информации. М.: Высш.шк., 1988, 237 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ n-РАЗРЯДНОГО ДВОИЧНОГО ПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД ОСТАТКА ПО МОДУЛЮ m | 2003 |

|

RU2242085C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЕЛ ИЗ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЛИАДИЧЕСКИЙ КОД | 2001 |

|

RU2187886C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2000 |

|

RU2188448C2 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЛА В МОДУЛЯРНОМ КОДЕ НА ОСНОВАНИЕ СИСТЕМЫ СЧИСЛЕНИЯ | 2002 |

|

RU2237274C2 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЛА В МОДУЛЯРНОМ КОДЕ НА ОСНОВАНИЕ СИСТЕМЫ СЧИСЛЕНИЯ | 2002 |

|

RU2231822C2 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2002 |

|

RU2220441C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОЗИЦИОННЫХ СУММАТОРОВ ПО МОДУЛЮ | 2002 |

|

RU2231823C2 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2007 |

|

RU2338241C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ОТ ЧИСЛА | 1999 |

|

RU2157589C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2006 |

|

RU2313124C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах для формирования конечных полей. Техническим результатом является повышение быстродействия преобразования. Устройство содержит входной регистр, генератор гармонического сигнала, управляемые фазовращатели, измеритель фазы гармонического сигнала, шифратор. 3 ил.

Устройство для преобразования n-разрядного двоичного позиционного кода в двоичный код остатка по модулю m, содержащее n-разрядный входной регистр, информационные входы которого являются входами устройства, а тактовый вход - тактовым входом устройства, отличающееся тем, что в него введены генератор гармонического сигнала, n управляемых фазовращателей, измеритель фазы гармонического сигнала и шифратор, причем выход генератора гармонического сигнала соединен с первым входом первого управляемого фазовращателя, выход i-го управляемого фазовращателя - c первым входом (i+1)-го управляемого фазовращателя  выход n-го управляемого фазовращателя - c первым входом измерителя фазы гармонического сигнала, ко второму входу которого подключен выход генератора гармонического сигнала, при этом выход измерителя фазы гармонического сигнала соединен со входом шифратора, выход которого является выходом устройства, а выход l-го разряда n-разрядного входного регистра

выход n-го управляемого фазовращателя - c первым входом измерителя фазы гармонического сигнала, ко второму входу которого подключен выход генератора гармонического сигнала, при этом выход измерителя фазы гармонического сигнала соединен со входом шифратора, выход которого является выходом устройства, а выход l-го разряда n-разрядного входного регистра  подключен ко второму входу l-го управляемого фазовращателя.

подключен ко второму входу l-го управляемого фазовращателя.

| Преобразователь двоичного кода в код системы остаточных классов | 1985 |

|

SU1322483A1 |

| Устройство для формирования остатка по произвольному модулю от числа | 1988 |

|

SU1658388A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1991 |

|

RU2023346C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ОТ ЧИСЛА | 1999 |

|

RU2157589C1 |

| US 4996527 А, 26.02.1991 | |||

| УСТРОЙСТВО для ЗАКРУТКИ ПРОВОЛОКИ | 0 |

|

SU312030A1 |

Авторы

Даты

2002-10-27—Публикация

2001-05-10—Подача