Область техники, к которой относится изобретение

Настоящее изобретение относится к устройству обработки данных и способу обработки данных и, более конкретно, например, к устройству обработки данных и способу обработки данных, способным повысить устойчивость к ошибкам данных.

Уровень техники

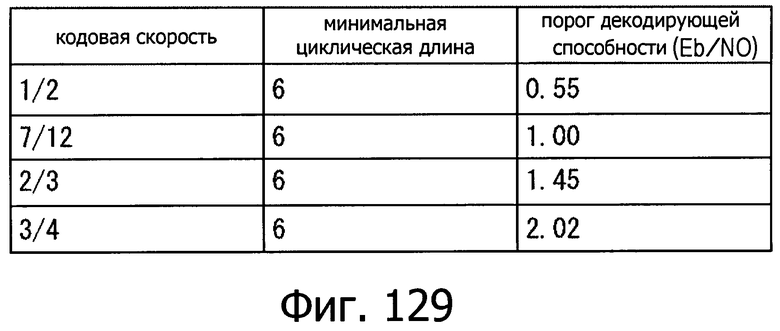

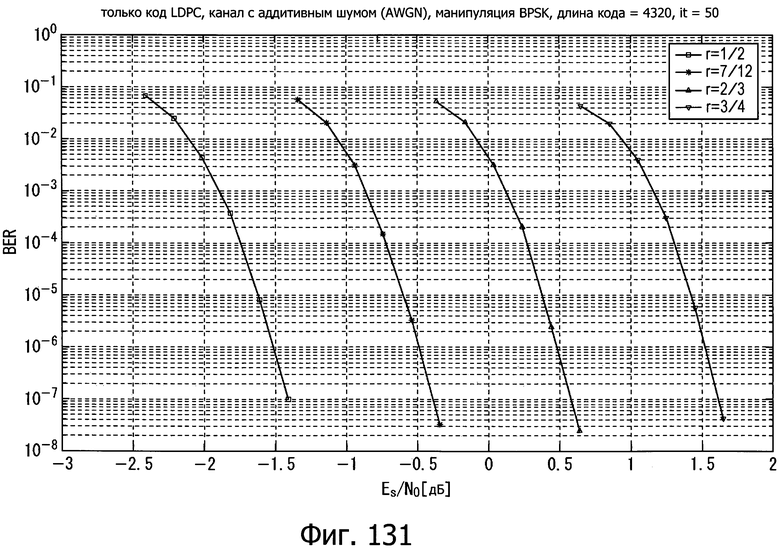

Код LDPC (кода с низкой плотностью проверок на четность) обладает высокой способностью корректировать ошибки, так что недавно, например, этот код начал широко применяться в системах связи и передачи информации, включая системы спутникового цифрового вещания, такие как система DVB (цифровое видео вещание)-S.2 (например, см. непатентный документ 1), используемая в Европе. Кроме того, код LDPC сейчас рассматривают для применения в системах наземного цифрового вещания следующего поколения.

Согласно последним исследованиям, можно понять, что при использовании кода LDPC аналогично турбо-коду или другому подобному коду увеличение длины кода позволяет приблизиться к пределу Шеннона. Кроме того, поскольку код LDPC обладает тем свойством, что минимальное расстояние пропорционально длине кода, этот код LDPC имеет хорошую характеристику вероятности блочных ошибок и обладает тем преимуществом, что явление так называемого минимального уровня ошибок, наблюдаемое при декодировании турбо-кода или аналогичного кода, в большинстве случаев не возникает.

Далее код LDPC будет описан более конкретно. Такой код LDPC представляет собой линейный код, и здесь этот код будет описан в качестве двоичного кода, что, в принципе, не обязательно.

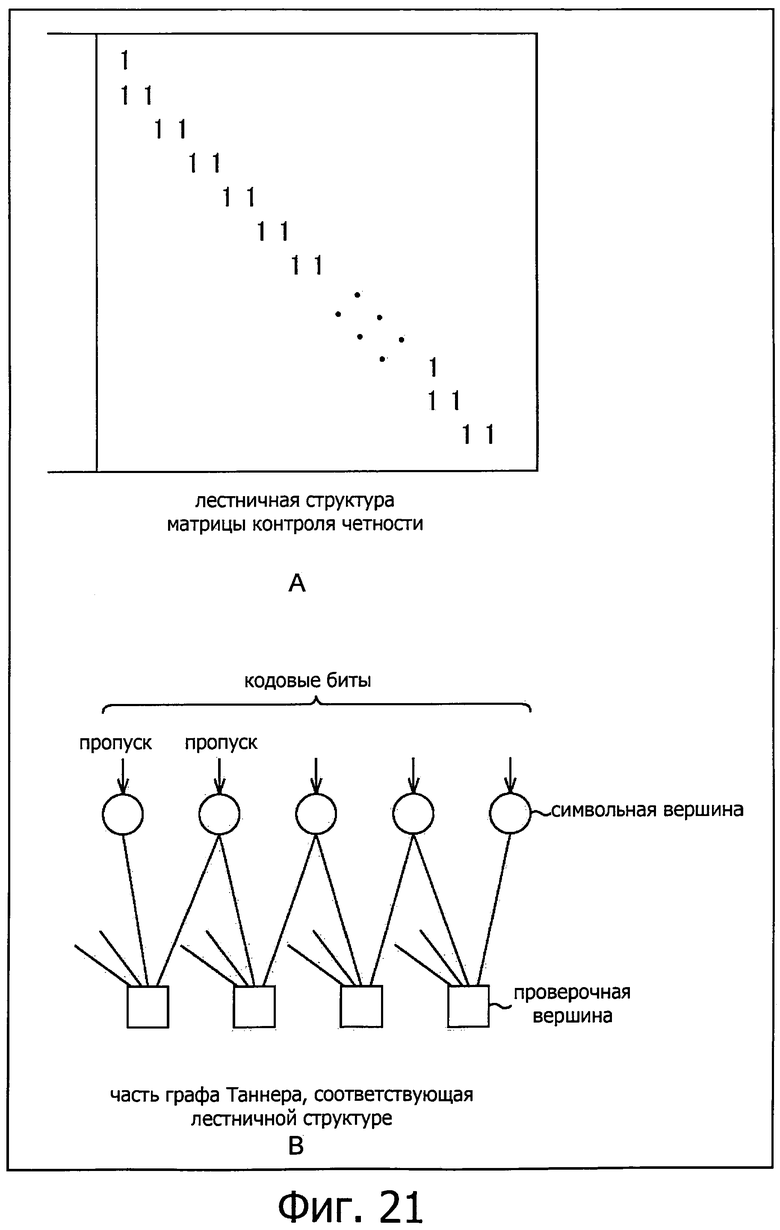

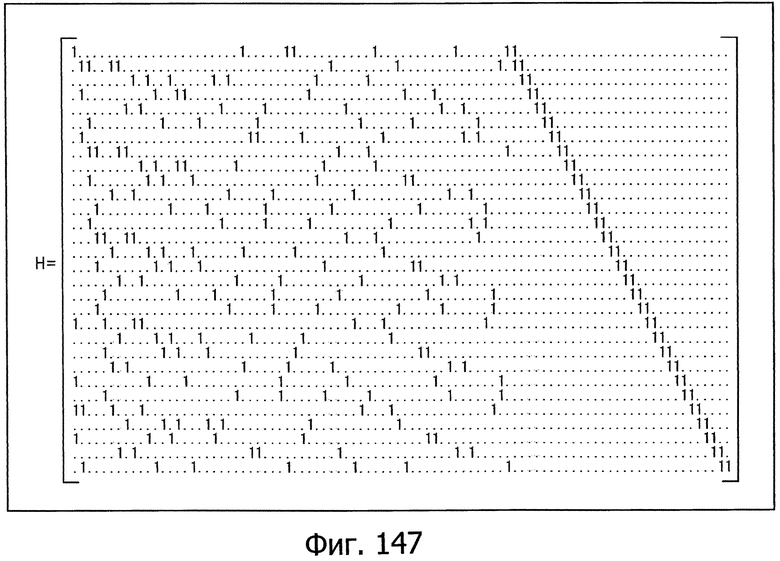

Отличительным свойством кода LDPC является тот факт, что проверочная матрица четности, определяющая код LDPC, является разреженной. Здесь под разреженной матрицей понимают матрицу, в которой число единичных "1" элементов матрицы очень мало (матрица, в которой большинство элементов являются нулевыми "0").

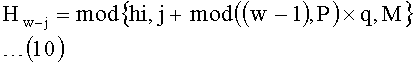

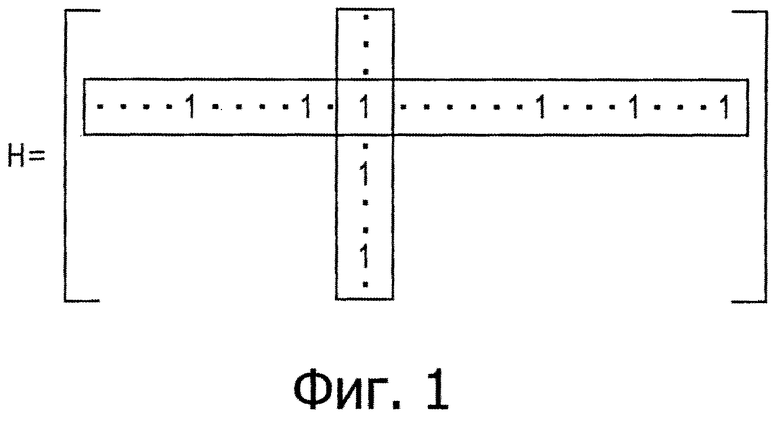

На Фиг.1 представлен пример проверочной матрицы Н для кода LDPC.

В проверочной матрице H, показанной на Фиг.1, вес (число "1") (вес столбца) каждого столбца равен "3", а вес (вес строки) каждой строки "6".

При кодировании (кодирование в коде LDPC) в соответствии с кодом LDPC, например, генерируют порождающую матрицу G на основе указанной проверочной матрицы Н и формируют кодовое слово (код LDPC) путем умножения бит двоичной информации на порождающую матрицу G.

Более конкретно, устройство кодирования, осуществляющее кодирование в коде LDPC, сначала вычисляет порождающую матрицу G в соответствии с уравнением GHT=0, где HT представляет транспонированную версию проверочной матрицы H. Здесь, если порождающая матрица G представляет собой матрицу размером K×N, устройство кодирования генерирует кодовое слово с (=uG) длиной N бит путем умножения порождающей матрицы G на строку бит (вектор и) информации, содержащую K бит. Кодовое слово (код LDPC), сгенерированное устройством кодирования, принимают после прохождения заданного канала связи на приемной стороне.

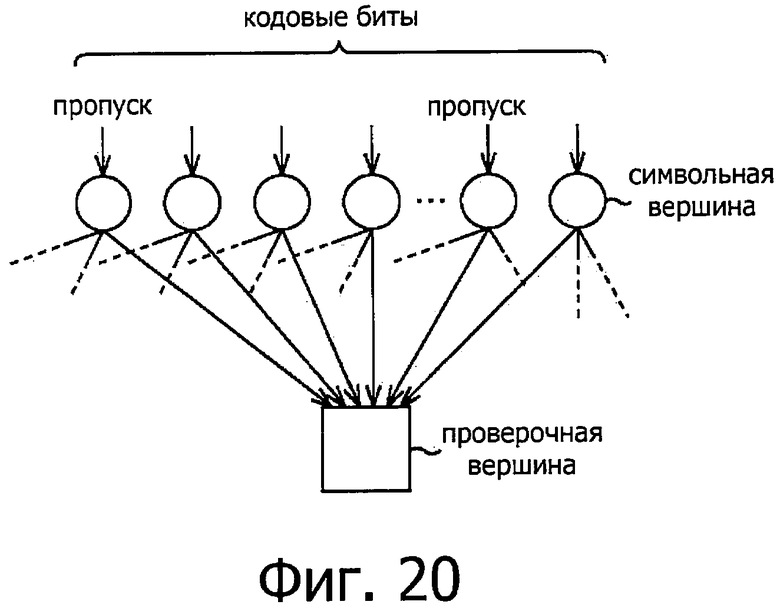

Для декодирования кода LDPC применяют алгоритм, предложенный Галлагером, назвавшим этот алгоритм вероятностным декодированием. Такое декодирование может быть произведено в соответствии с алгоритмом передачи сообщений, основанным на распространении надежности в так называемом графе Таннера, образованном символьными вершинами (также именуемыми вершинами сообщений) и проверочными вершинами. В последующем эти символьные вершины и проверочные вершины будут, где это возможно именоваться просто вершинами.

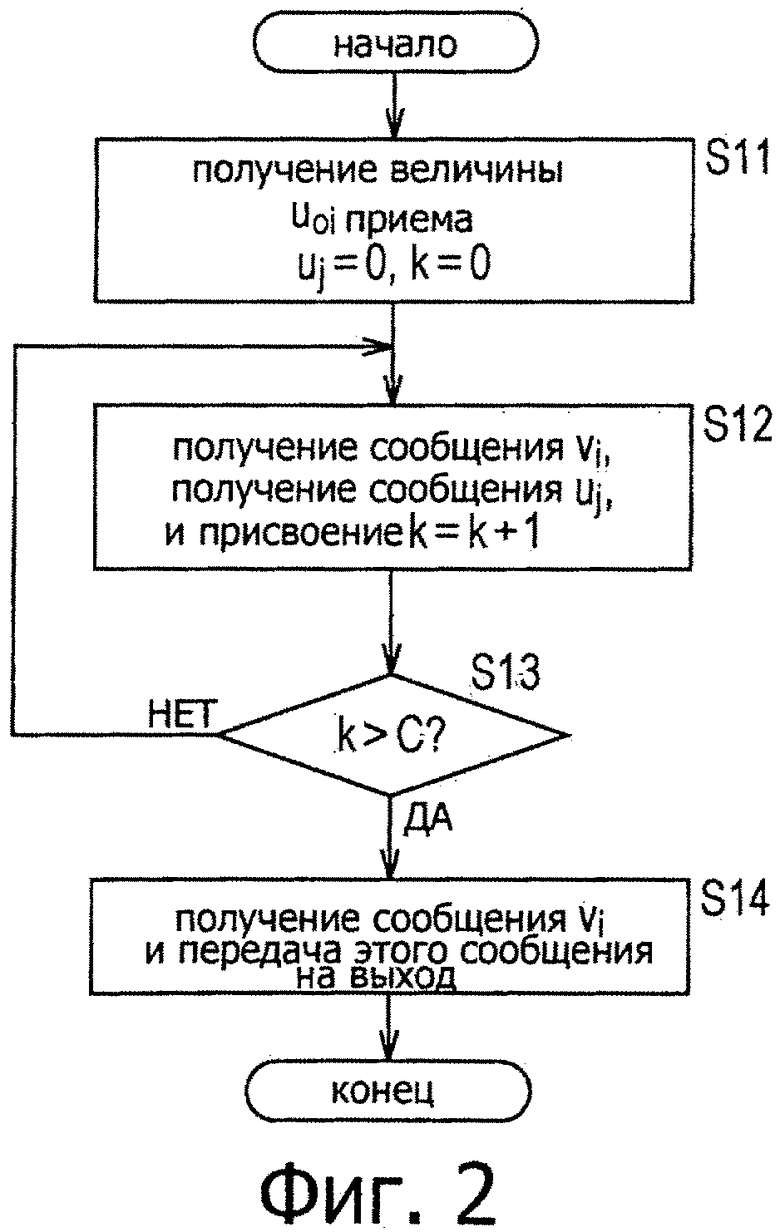

На Фиг.2 представлена последовательность декодирования кода LDPC.

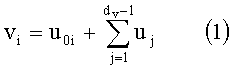

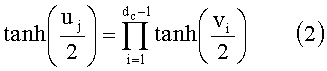

В последующем, действительная величина (величина логарифмического отношения правдоподобия (LLR) при приеме), полученная в результате представления вероятности того, что величина i-го кодового бита в составе кода LDPC (одно кодовое слово), принятого на приемной стороне, равна "0", в виде логарифмического отношения правдоподобия, будет именоваться принятой величиной u0i, где это возможно. Кроме того, сообщение, исходящее из проверочной вершины, обозначают uj, а сообщение, исходящее из символьной вершины, обозначают vi.

Во-первых, при декодировании кода LDPC, как показано на Фиг.2, на этапе S11, принимают код LDPC, инициализируют сообщение (сообщение проверочной вершины) uj, приравняв его "0", целочисленную переменную к, служащую счетчиком повторений процесса, также инициализируют, приравняв ее "0", и процесс переходит к этапу S12. На этапе S12 на основе принятой величины u0i, полученной в результате приема кода LDPC, получают сообщение (сообщение символьной вершины) vi путем выполнения вычислений (вычисления для символьной вершины), представленных Уравнением (1), и получают сообщение uj путем выполнения вычислений (вычисления для проверочной вершины), представленных Уравнением (2), на основе сообщения vi.

Уравнение 1

Уравнение 2

Здесь, dv и dc, представленные в Уравнениях (1) и (2), являются параметрами, представляющими число единиц "1" в проверочной матрице Н в вертикальном направлении (столбец) и горизонтальном направлении (строка), так что значения этих параметров могут быть выбраны произвольно, например, в случае кода (3, 6), dv=3 и dc=6.

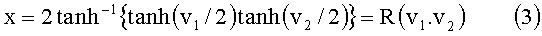

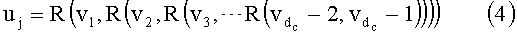

Кроме того, при вычислениях для символьной вершины, представленных Уравнением (1), и вычислениях для проверочной вершины, представленных Уравнением (2), каждое сообщение, поступившее из ветви (ребра) (линия, соединяющая символьную вершину и проверочную вершину), в которую нужно передать сообщение, не задают в качестве цели вычислений, вследствие чего вычисления производят в диапазонах с 1 по dv-1 и с 1 по dc-1. Вычисления для проверочной вершины, представленные Уравнением (2), реально осуществляют путем организации таблицы функции R(v1,v2), представленной в Уравнении (3), т.е. определенной в качестве одной выходной величины для двух входных величин v1 и v2, заранее, и затем последовательно (рекурсивно) используя эту таблицу, как представлено Уравнением (4).

Уравнение 3

Уравнение 4

В дополнение к этому, на этапе S12, увеличивают переменную к на единицу и переходят к этапу S13. На этапе S13 определяют, превосходит ли переменная к заданное число С повторений операций декодирования. Если на этапе S13 определено, что переменная к не больше величины С, процесс возвращается к этапу S12, и повторяются те же операции.

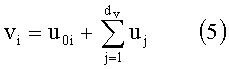

С другой стороны, если на этапе S13 определено, что переменная к больше величины С, процесс переходит к этапу S14, получают сообщение vi в качестве конечного результата декодирования, выполняя вычисления, представленные в Уравнении (5), и передают это сообщение на выход, так что процесс декодирования кода LDPC завершается.

Уравнение 5

Здесь, вычисления, представленные в Уравнении (5), в отличие от вычислений для символьной вершины, представленных Уравнением (1), осуществляют с использованием сообщений uj, поступающих из всех ветвей, соединенных с этой символьной вершиной.

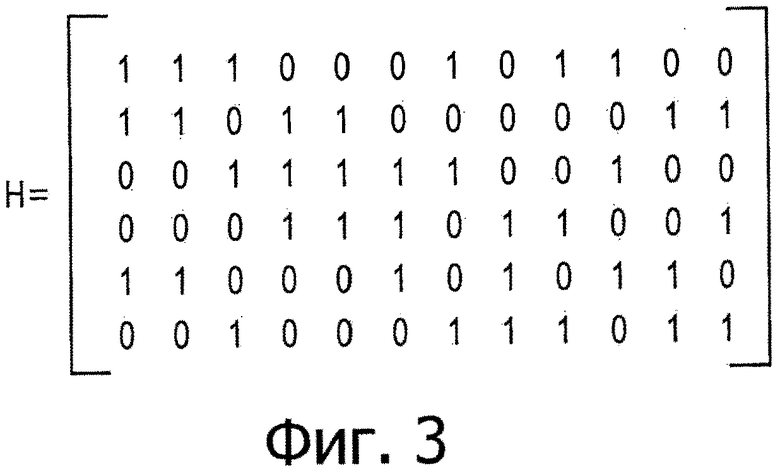

На Фиг.3 представлен пример проверочной матрицы H для кода LDPC (3, 6) (кодовая скорость равна 1/2, длина кода равна 12).

В проверочной матрице Н, показанной на Фиг.3, аналогично матрице, изображенной на Фиг.1, вес столбца равен 3 и вес строки равен 6.

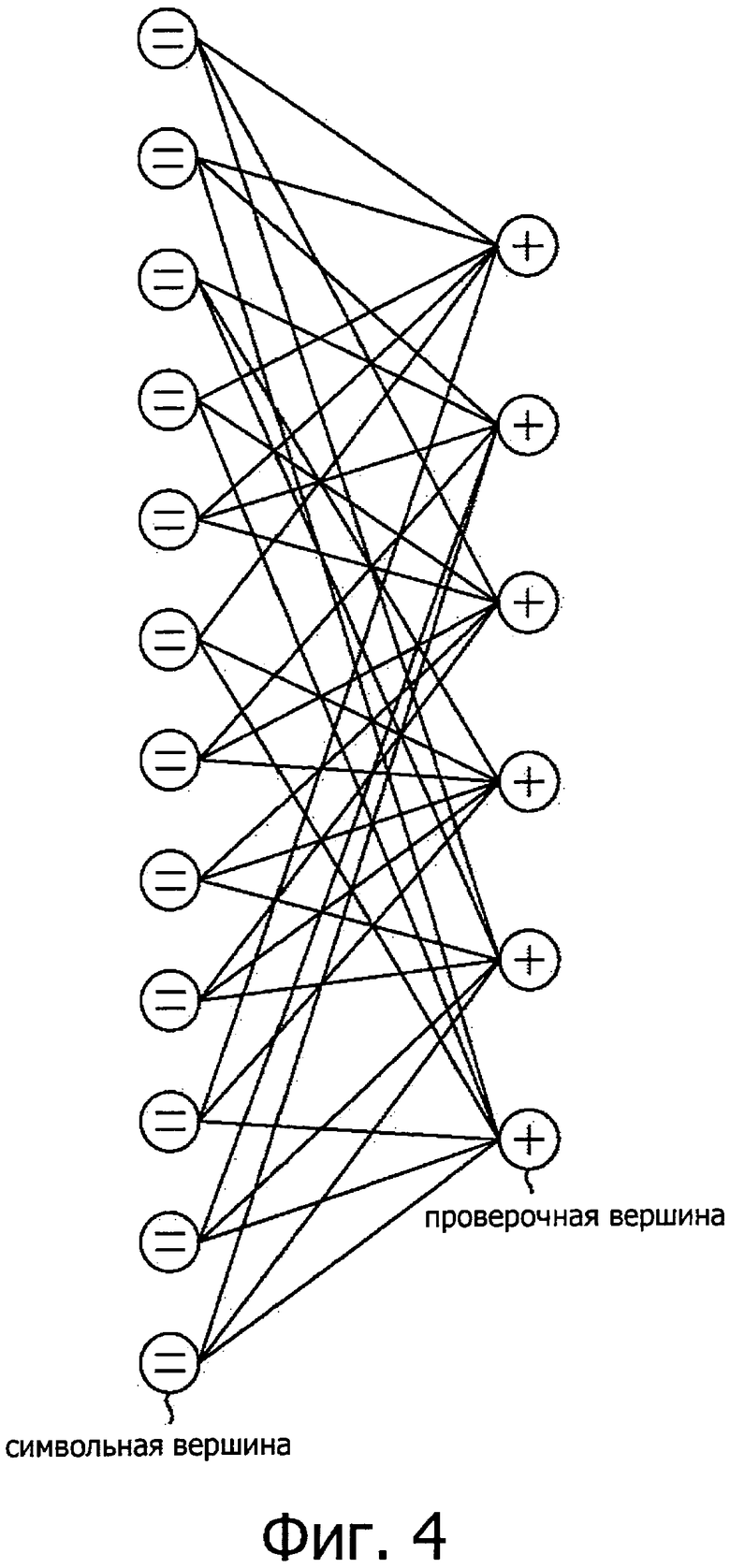

На Фиг.4 представлен граф Таннера для проверочной матрицы Н, показанной на Фиг.3.

Здесь, на Фиг.4 вершина, обозначенная знаком плюс "+", является проверочной вершиной, а вершина, обозначенная знаком равенства "=", является символьной вершиной. Проверочная вершина и символьная вершина соответствуют строке и столбцу проверочной матрицы H. Линия, соединяющая проверочную вершину с символьной вершиной, представляет собой ветвь (ребро) и соответствует единичному ("1") элементу проверочной матрицы.

Другими словами, если элемент j-й строки и i-го столбца в матрице контроля четности равен "1", на Фиг.4, i-я символьная вершина (вершина, обозначенная знаком "=") сверху и j-я проверочная вершина (вершина, обозначенная знаком "+") сверху соединены ветвью одна с другой. Ветвь представляет, что бит кода, соответствующий символьной вершине, имеет ограничительное условие, соответствующее проверочной вершине.

В процессе реализации алгоритма суммы произведения, представляющего собой способ декодирования кода LDPC, многократно выполняют вычисления для символьной вершины и вычисления для проверочной вершины.

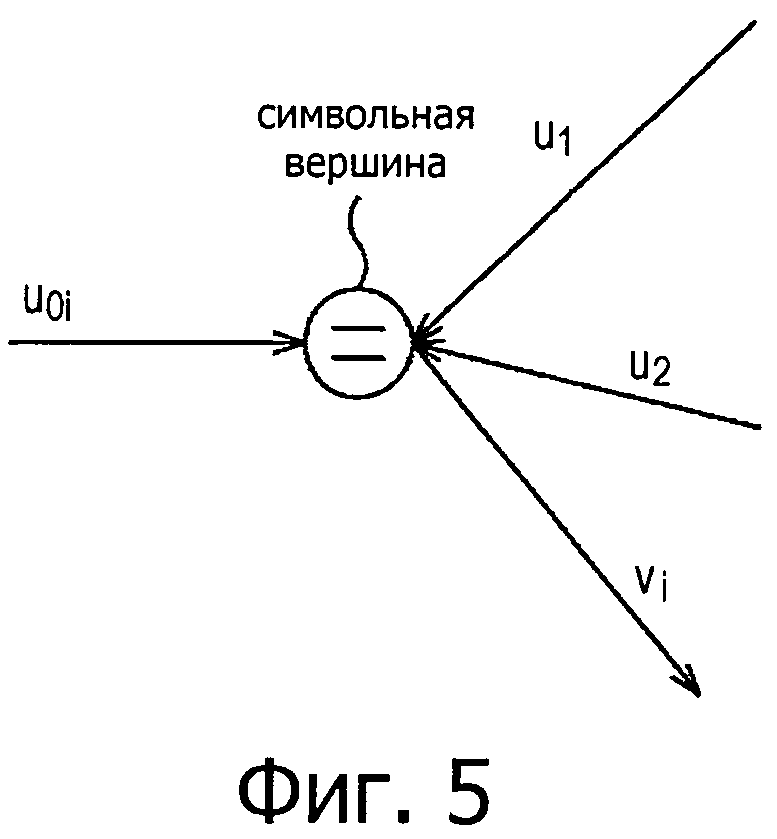

На Фиг.5 представлены вычисления для символьной вершины, выполняемые в такой символьной вершине.

В символьной вершине сообщение vi, которое соответствует ветви, являющейся целью вычислений, получают посредством процедуры вычислений для символьной вершины, представленной Уравнением (1), с использованием сообщений u1 и u2, поступающих от остальных ветвей, соединенных с этой символьной вершиной, и принятой величины u0i. Сообщения, соответствующие другим ветвям, получают аналогичным способом.

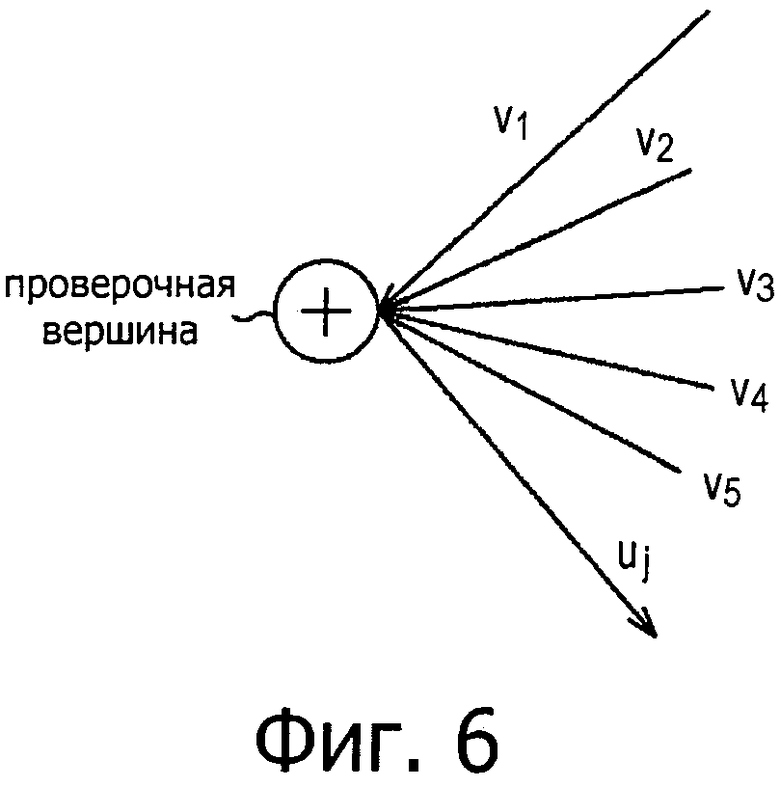

На Фиг.6 представлены вычисления для проверочной вершины, выполняемые в такой проверочной вершине.

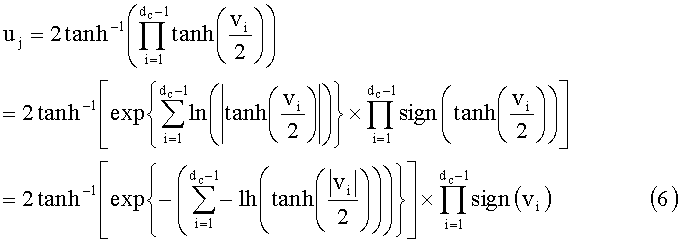

Здесь, вычисления для проверочной вершины, представленные Уравнением (2), могут быть преобразованы в Уравнение (6) с использованием соотношения, соответствующего уравнению "а×b=exp{ln(|а|)+ln(|b|)}×sign(a)×sign(b). Здесь, sign(x) равно 1, когда when x≥0, и равно -1, когда х<0.

Уравнение 6

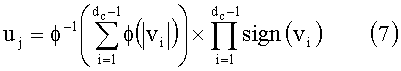

В случае, где x≥0, когда функция ϕ(х) определена соотношением "ϕ(x)=ln(tanh(x/2))", удовлетворяется соотношение "ϕ-1(x)=2tanh-1(e-x)" и, соответственно, Уравнение (6) может быть преобразовано в Уравнение (7).

Уравнение 7

В проверочной вершине указанные вычисления для проверочной вершины, представленные Уравнением (2), осуществляют на основе Уравнения (7).

Другими словами, как показано на Фиг.6, в проверочной вершине сообщение uj, соответствующее ветви, являющейся целью вычислений, может быть получено в результате вычислений для проверочной вершины, представленных Уравнением (7), с использованием сообщений v1, v2, v3, v4 и v5, поступающих из остальных ветвей, соединенных с этой проверочной вершиной. Сообщения, соответствующие другим ветвям, получают аналогичным способом.

Кроме того, функция ϕ(x), входящая в Уравнение (7), может быть представлена уравнением ϕ(x)=ln((ex+1)/(ех-1)), и ϕ(х)=ϕ-1(x) для x>0. При реализации функций ϕ(x) и ϕ-1(x) аппаратным способом есть случаи, когда эти функции реализуют с использованием просмотровых таблиц LUT (Look Up Table), причем эти таблицы LUT является одинаковыми для обеих функций.

Список литературы

Непатентный документ

Непатентный документ 1: DVB-S.2: ETSI EN 302 307 V1.1.2 (2006-06)

Раскрытие изобретения

Проблемы, раскрываемые изобретением

Код LDPC используют в системе DVB-S.2, являющейся стандартом спутникового цифрового вещания, или в системе DVB-T.2, являющейся стандартом наземного цифрового вещания следующего поколения. Кроме того, планируется использовать код LDPC в системе DVB-C.2, являющейся стандартом цифрового вещания в сетях кабельного телевидения (CATV) следующего поколения.

В системе цифрового вещания, соответствующей стандарту DVB, такому как DVB-S.2, код LDPC задают (представляют в символьной форме) в виде символа системы с ортогональной модуляцией (цифровой модуляции), такой как QPSK (квадратурная фазовая манипуляция), преобразуют этот символ в сигнальную точку и передают.

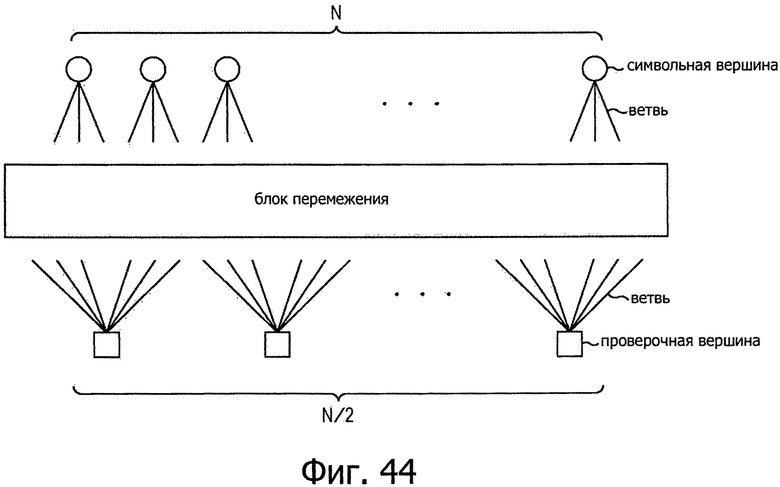

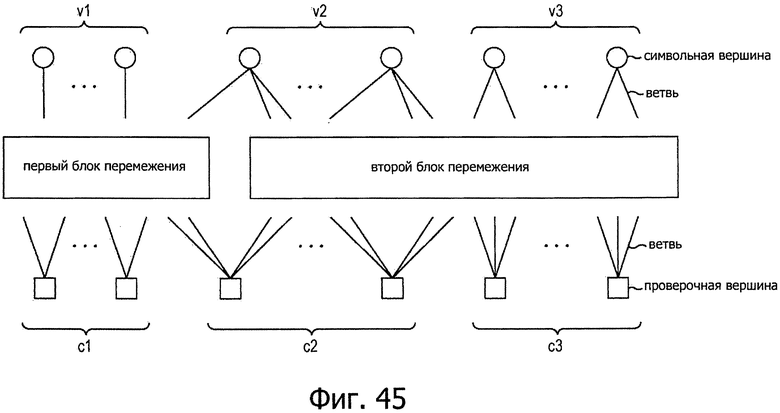

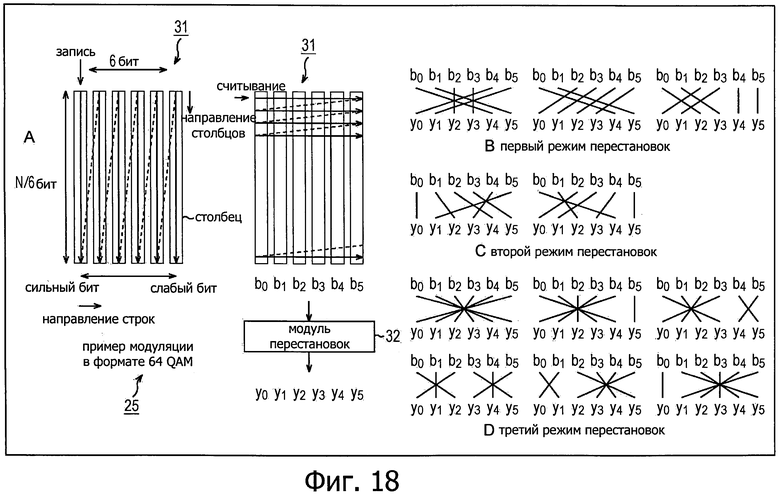

В процессе представления кода LDPC в символьной форме перестановка кодовых бит кода LDPC осуществляют блоками по два или более кодовых бит, а после перестановки эти кодовые биты рассматриваются в качестве бит символа.

В качестве системы для перестановки кодовых бит с целью представления кода LDPC в символьной форме предложены разнообразные системы, и, например, такая система определена также в стандарте DVB-T.2.

Однако DVB-T.2 представляет собой стандарт цифрового вещания, специально предназначенный для использования в стационарных оконечного устройствах, таких как телевизионные приемники, установленных в домах или аналогичных местах, и может не подходить для цифрового вещания, специально предназначенного для применения мобильным оконечным устройством.

Другими словами, схема мобильного оконечного устройства должна быть по размерам меньше схемы стационарного оконечного устройства, а также необходимо обеспечить низкое потребление энергии в мобильном оконечном устройстве. Соответственно, в системах цифрового вещания, специально предназначенных для работы с мобильными оконечными устройствами для уменьшения нагрузки, необходимой для такого процесса, как декодирование кода LDPC, или аналогичного процесса, в мобильном оконечном устройстве, например, в некоторых случаях число повторений при декодировании кода LDPC (число С повторений) или длину кода LDPC ограничивают в большей степени, чем в системе цифрового вещания, специально предназначенной для работы со стационарными оконечными устройствами.

Однако даже при таких ограничениях необходимо поддерживать в некоторой степени устойчивость против ошибок.

Настоящее изобретение создано с учетом такой ситуации и предназначено для повышения устойчивости данных, таких как код LDPC, к ошибкам.

Решение проблем

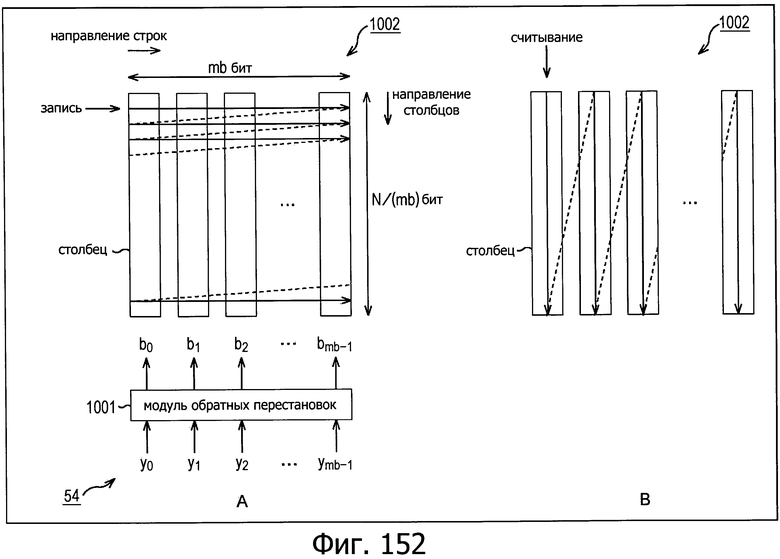

Устройство обработки данных/способ обработки данных согласно первому аспекту настоящего изобретения включает:

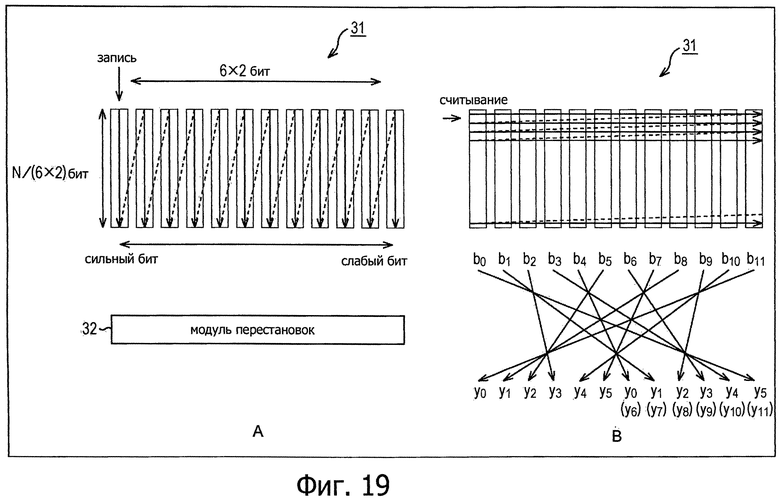

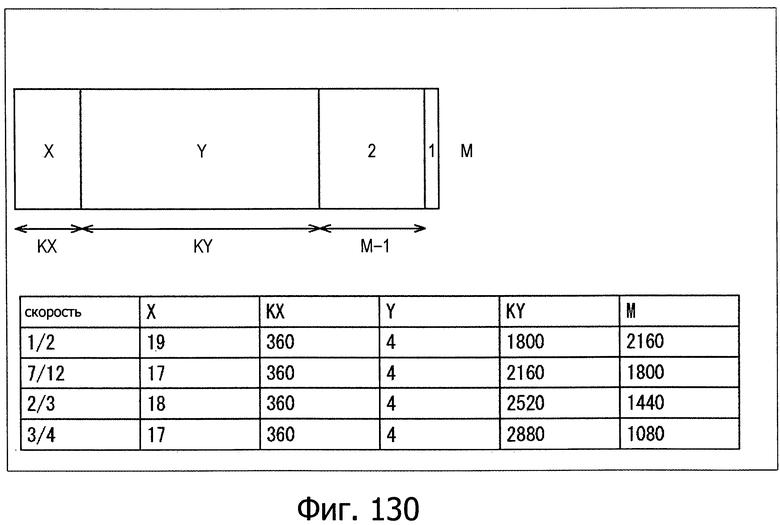

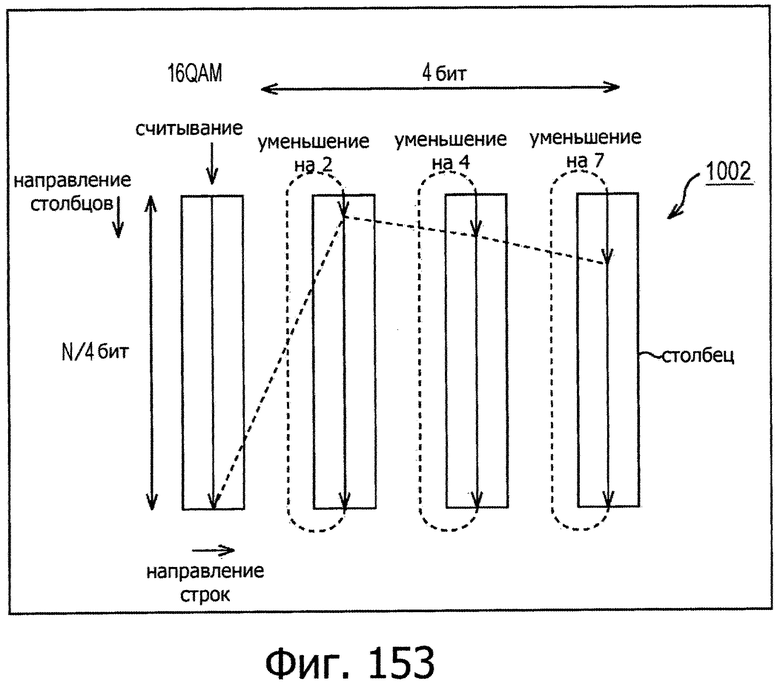

модуль/этап перестановки для перестановки кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ и установки кодовых бит после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, хранящего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемых в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемые в направлении строк устройства хранения, образуют b символов,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

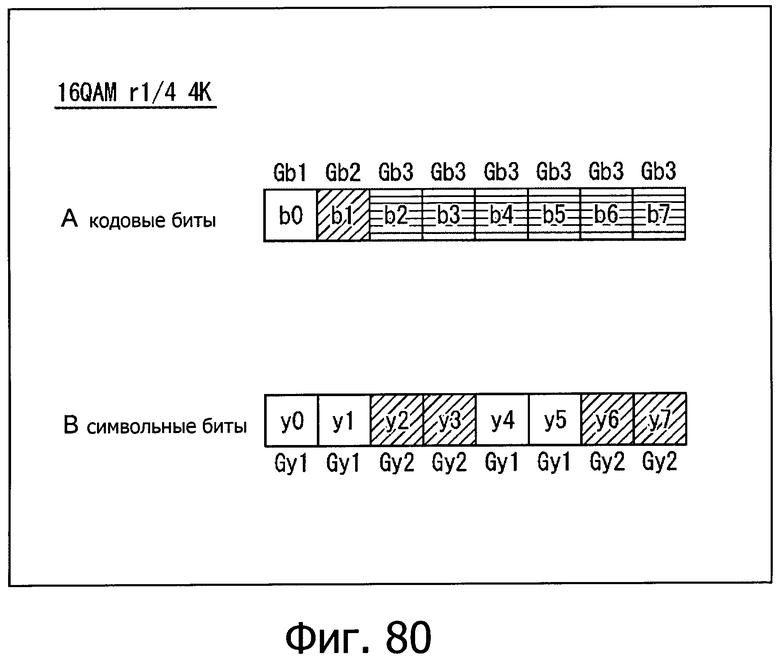

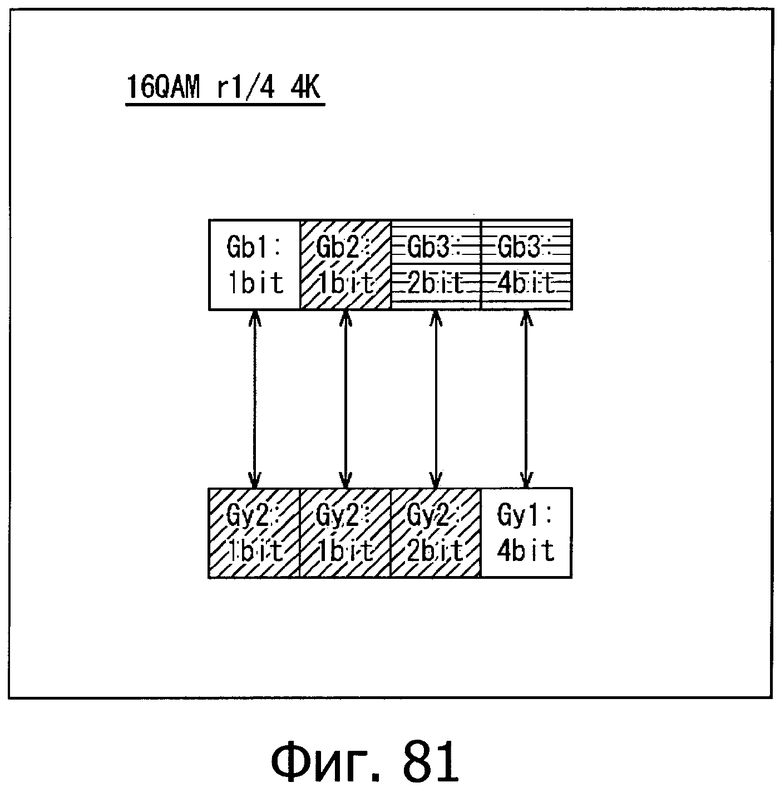

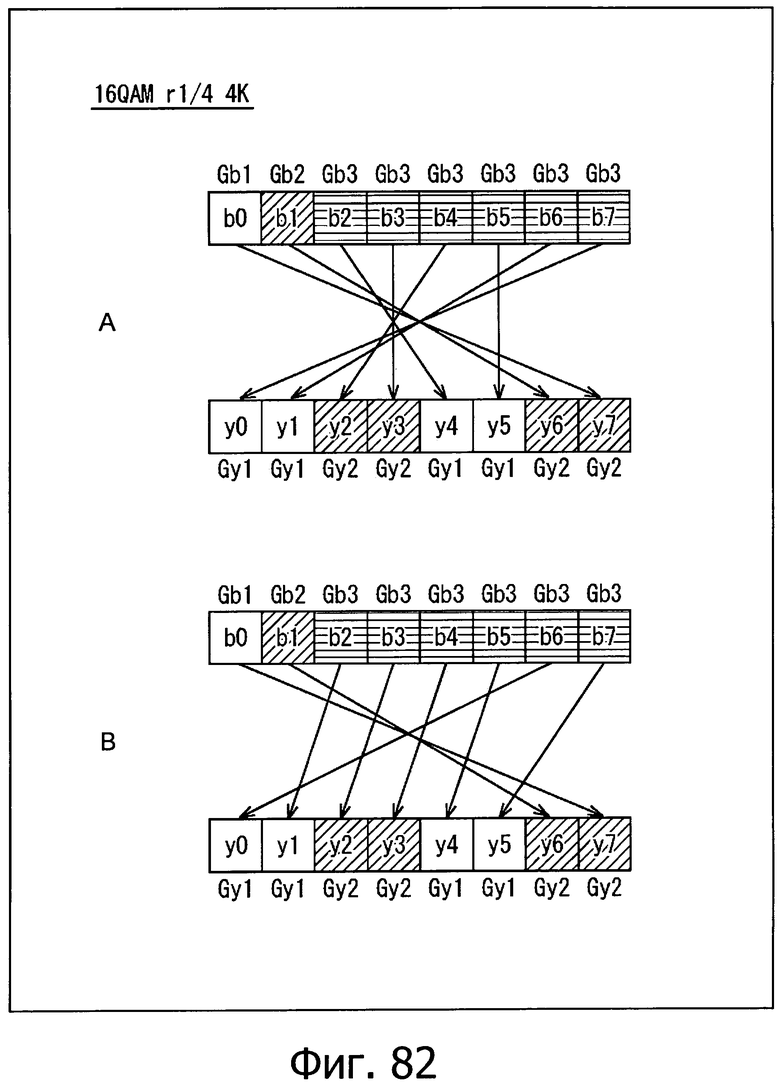

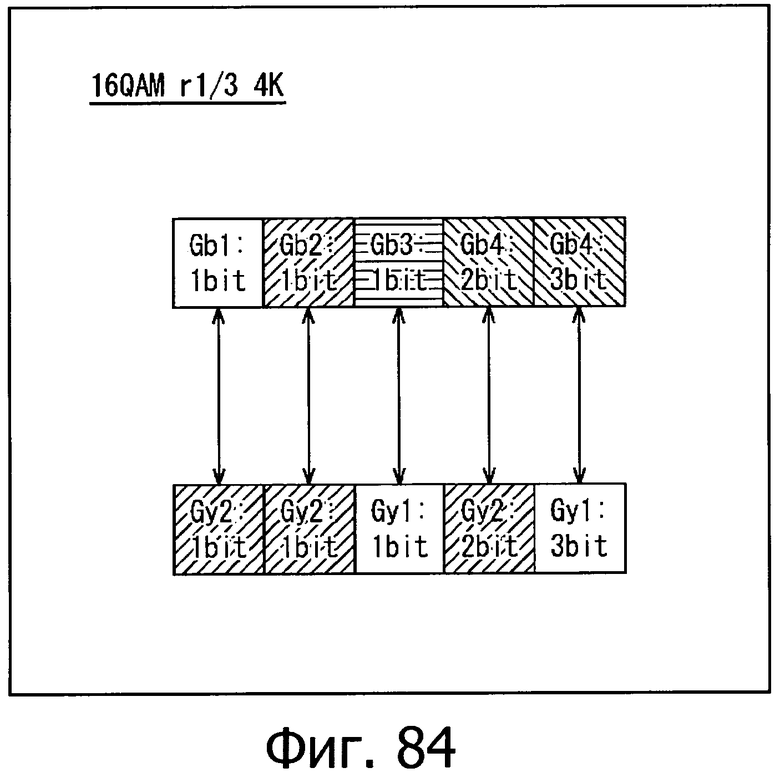

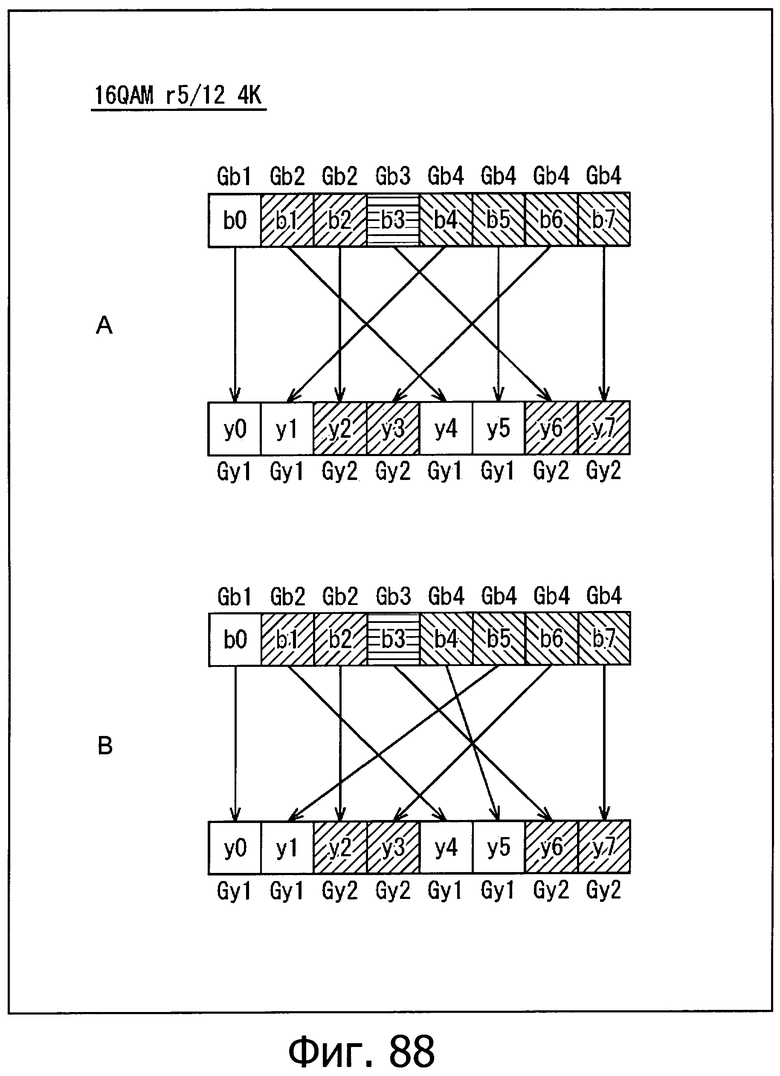

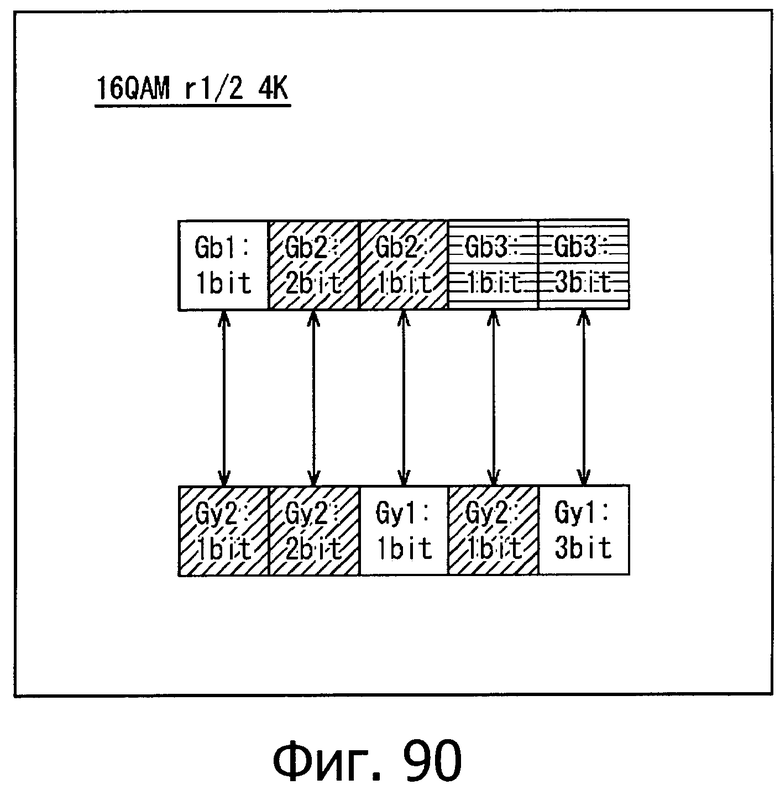

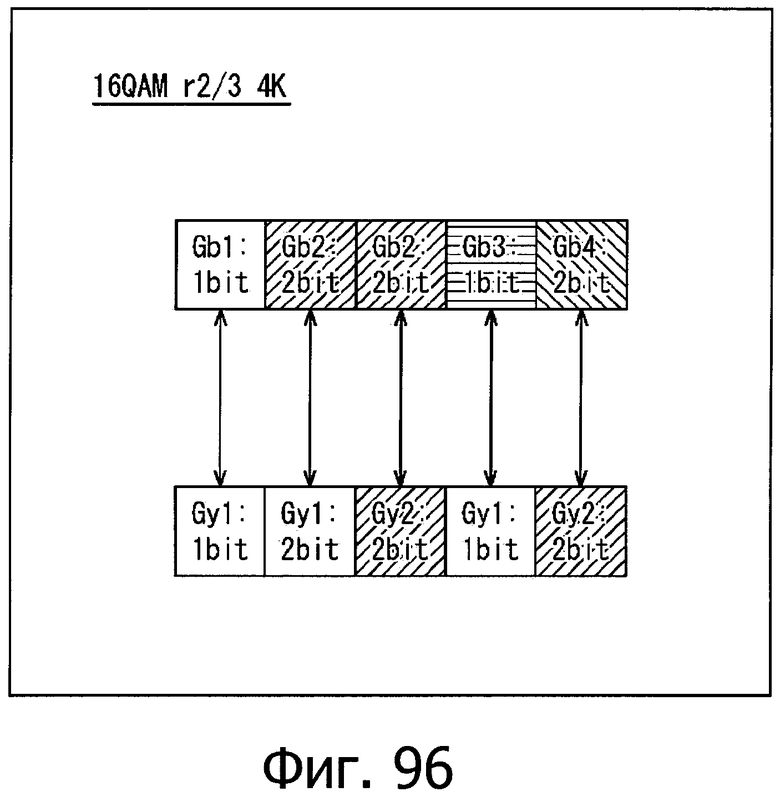

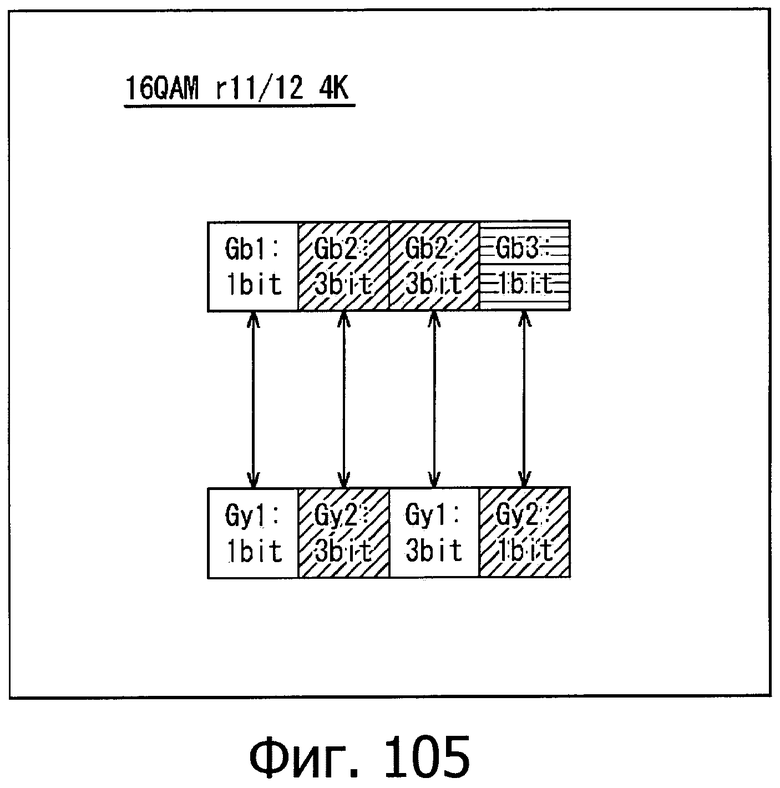

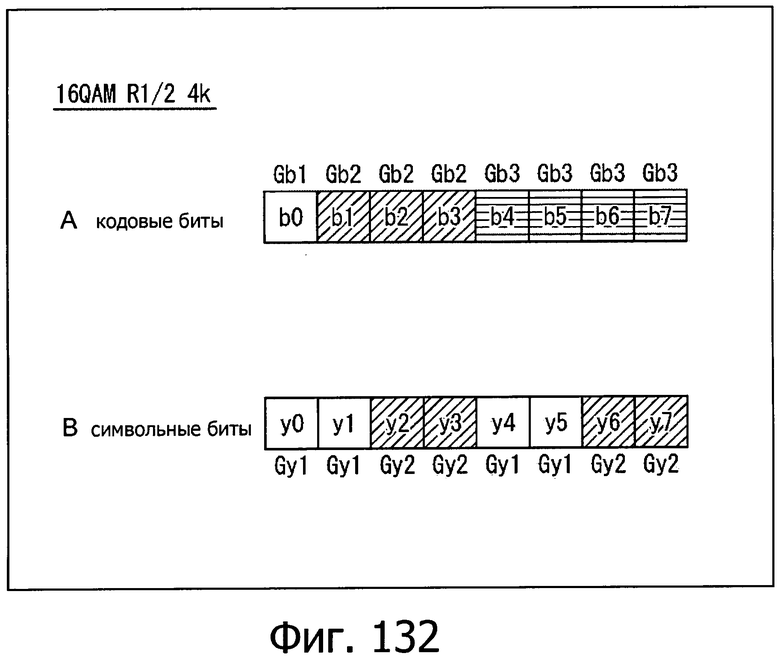

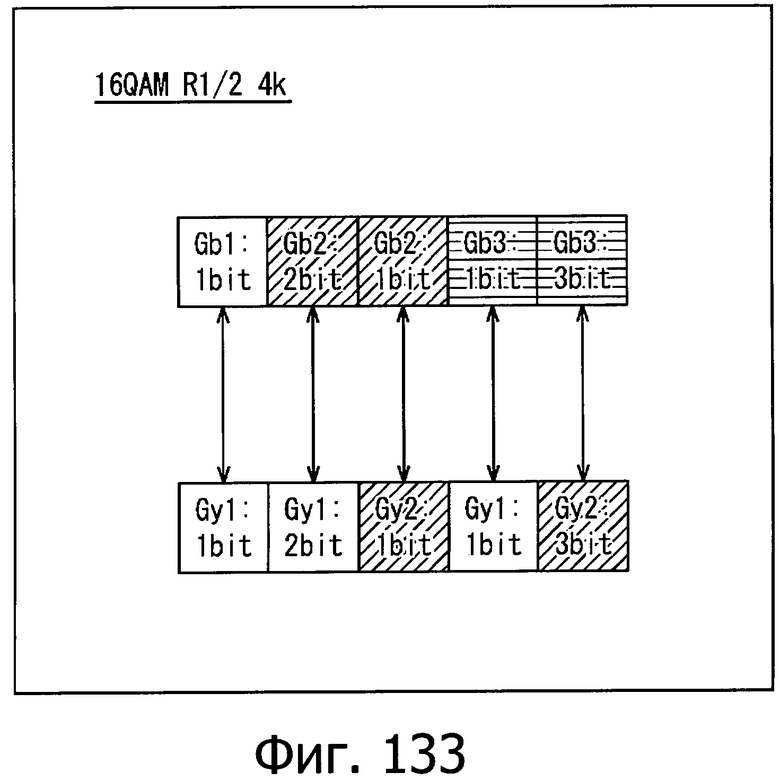

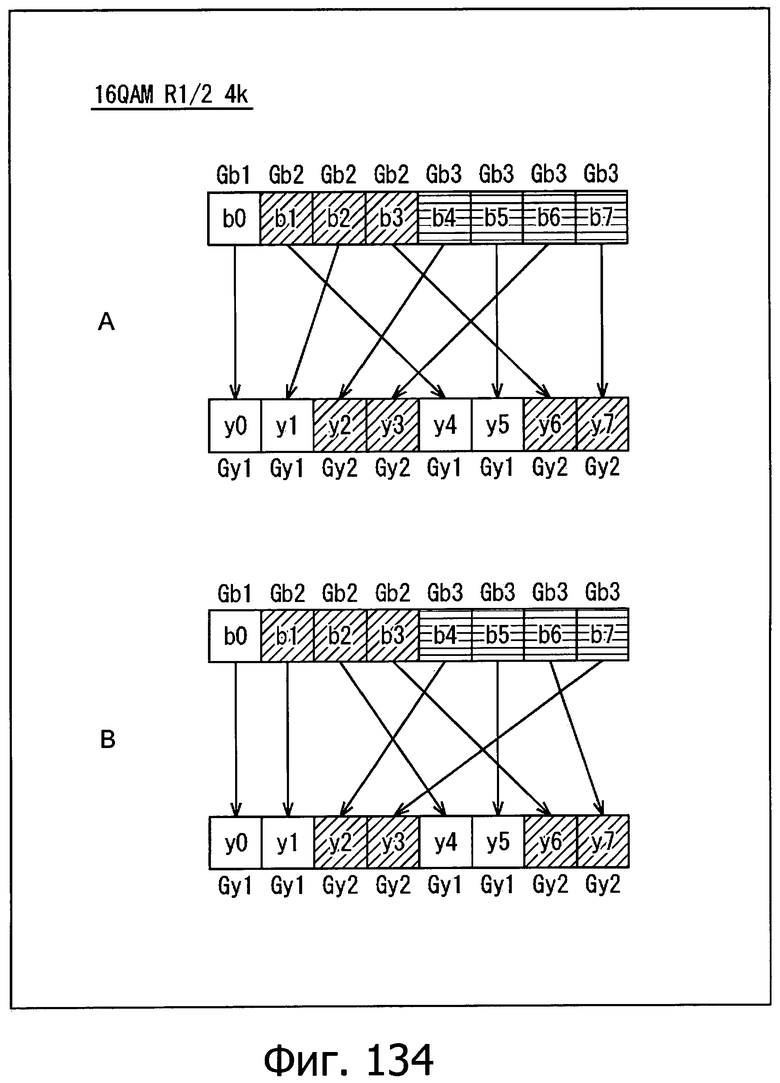

при этом правило назначения представляет собой правило, устанавливающее группы бит, полученные посредством группирования кодовых бит в количестве mb бит в соответствии с вероятностью ошибки, в качестве групп кодовых бит и группы, полученные посредством группирования символьных бит в количестве mb бит в соответствии с вероятностью ошибки, в качестве групп символьных бит, при этом определяет набор групп, представляющих собой сочетание группы кодовых бит и группы символьных бит, которым назначены кодовые биты из этой группы кодовых бит, и определяет число кодовых бит и число символьных бит в каждой группе кодовых бит и в каждой группе символьных бит в составе этого набора групп, при этом в случае, где m бит являются четырьмя битами, целое число b равно двум и четыре бита из совокупности кодовых бит преобразуют в одну из 16 сигнальных точек, определенных в системе с 16-уровневой квадратурной амплитудной модуляцией (16 QAM), в качестве одного символа, кодовые биты в количестве 4×2 бит группируют в три группы кодовых бит и символьные биты в количестве 4×2 бит группируют в две группы символьных бит,

при этом по правилу назначения происходит назначение одного бита кодовых бит в группе кодовых бит, для которой вероятность ошибки является наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение двух бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве двух бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение одного бита кодовых бит группы кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей, назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является третьей после наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, и назначение трех бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является третьей после наилучшей, в качестве трех бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей,

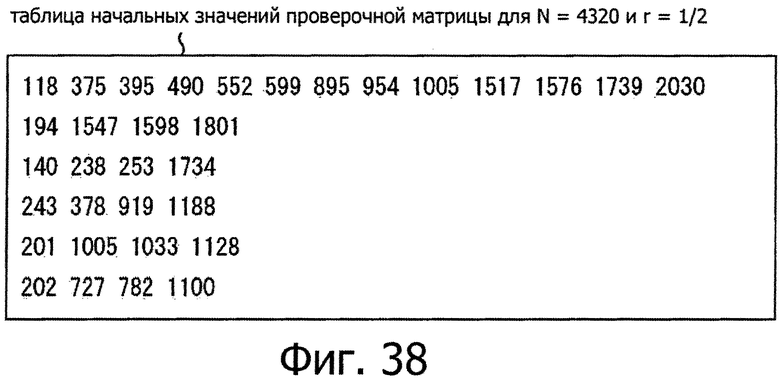

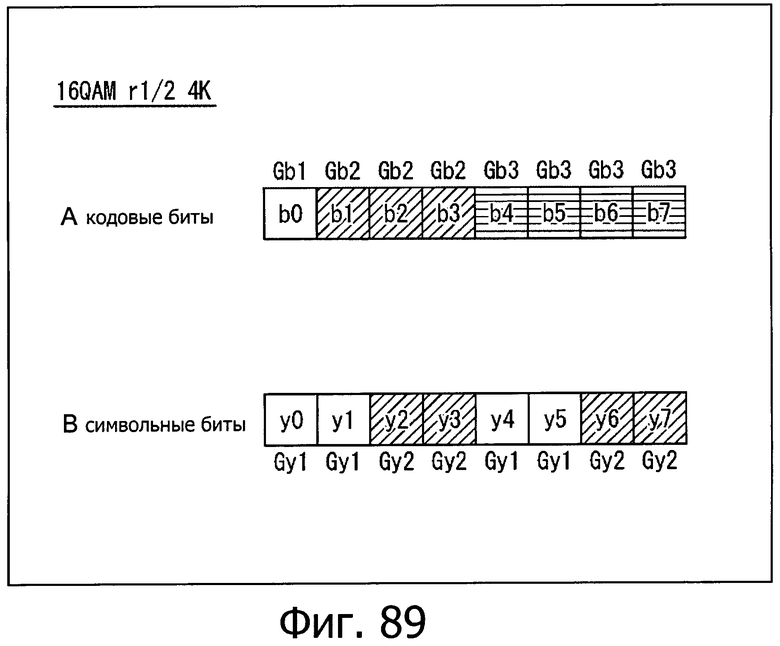

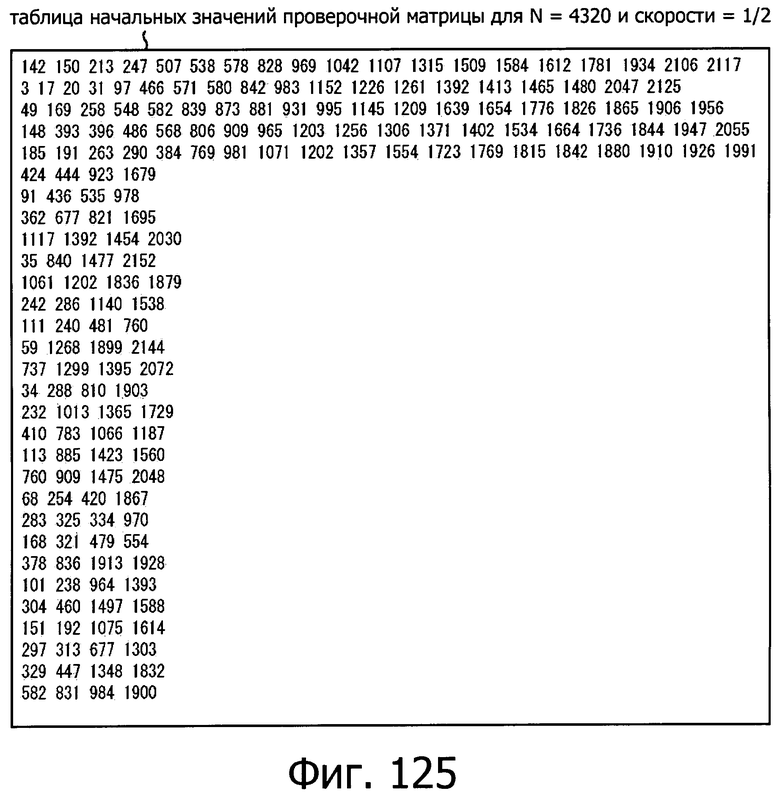

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 1/2,

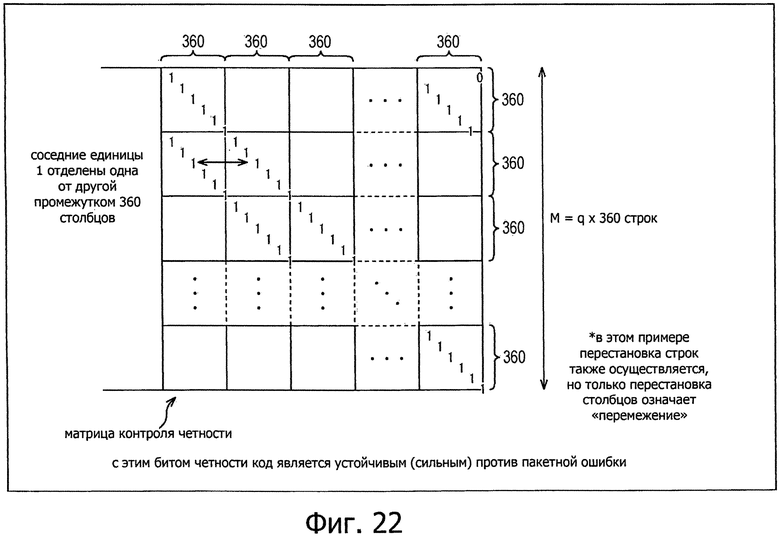

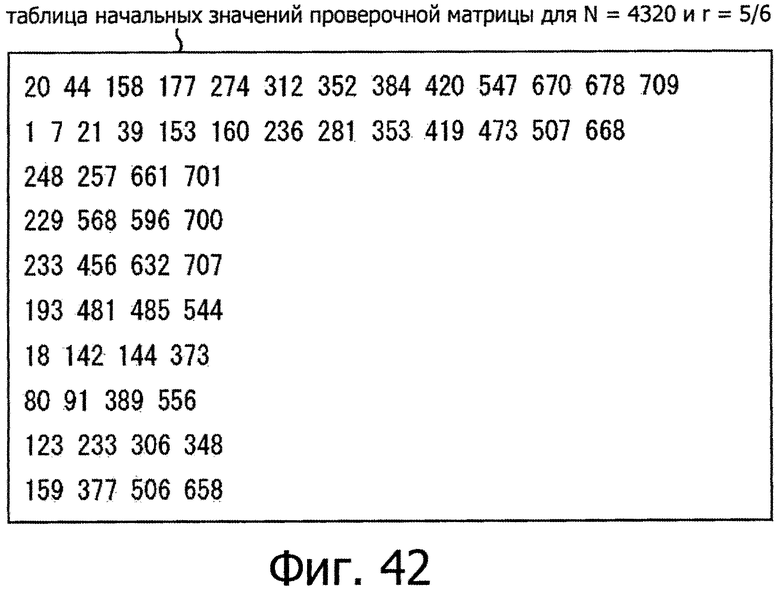

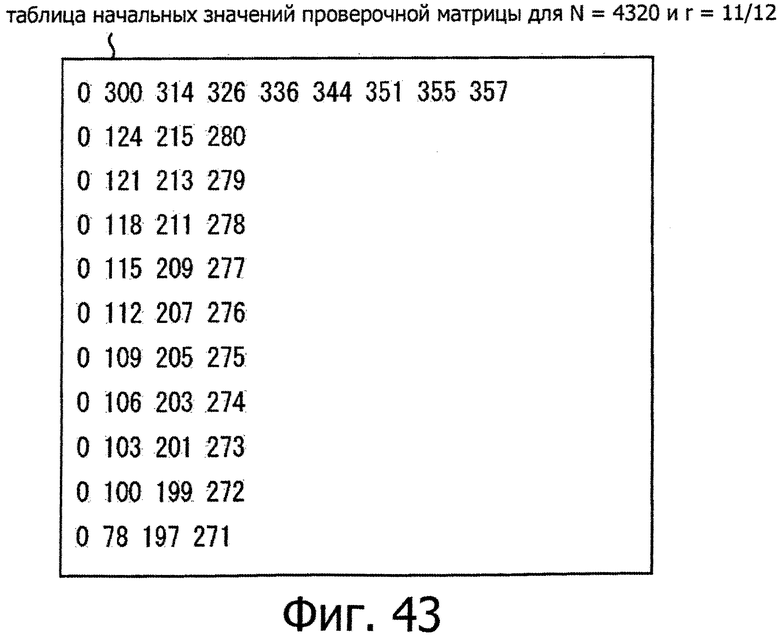

при этом проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

142 150 213 247 507 538 578 828 969 1042 1107 1315 1509 1584 1612 1781 1934 2106 2117

3 17 20 31 97 466 571 580 842 983 1152 1226 1261 1392 1413 1465 1480 2047 2125 49 169 258 548 582 839 873 881 931 995 1145 1209 1639 1654 1776 1826 1865 1906 1956

148 393 396 486 568 806 909 965 1203 1256 1306 1371 1402 1534 1664 1736 1844 1947 2055

185 191 263 290 384 769 981 1071 1202 1357 1554 1723 1769 1815 1842 1880 1910 1926 1991

424 444 923 1679

91 436 535 978

362 677 821 1695

1117 1392 1454 2030

35 840 1477 2152

1061 1202 1836 1879

242 286 1140 1538

111 240481 760

59 1268 1899 2144

737 1299 1395 2072

34 288 810 1903

232 1013 1365 1729

410 783 1066 1187

113 885 1423 1560

760 909 1475 2048

68 254 420 1867

283 325 334 970

168 321 479 554

378 836 1913 1928

101 238 964 1393

304 460 1497 1588

151 192 1075 1614

297 313 677 1303

329 447 1348 1832

582 831 984 1900

Устройство обработки данных/способ обработки данных согласно второму аспекту настоящего изобретения включает:

модуль/этап перестановки для перестановки кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и установки кодовых бит после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, хранящего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемые в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, при этом устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

при этом m бит являются четырьмя битами и целое число b равно двум,

при этом четыре бита из совокупности кодовых бит преобразуют в одну из 16

сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа,

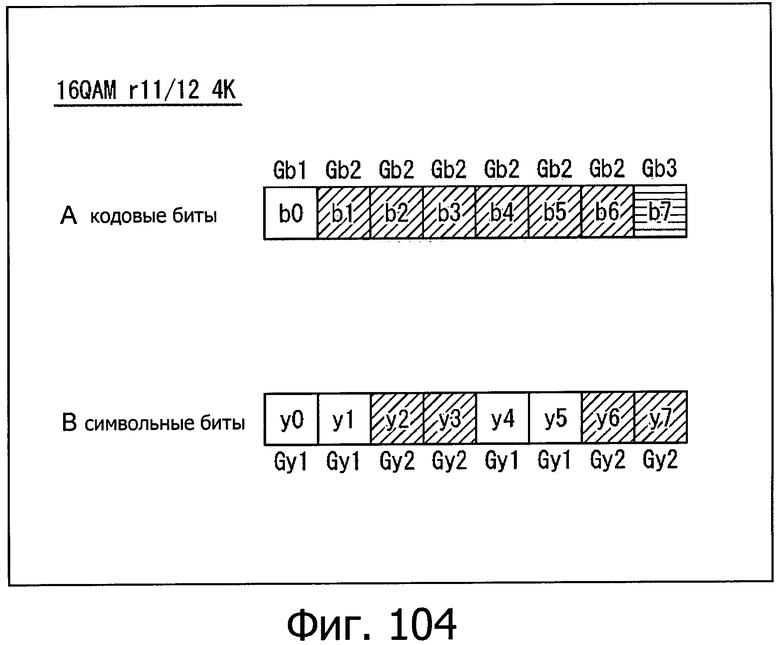

при этом устройство хранения включает 8 столбцов, сохраняющих 4×2 бит в направлении строк, и сохраняет 4320/(4×2) бит в направлении столбцов,

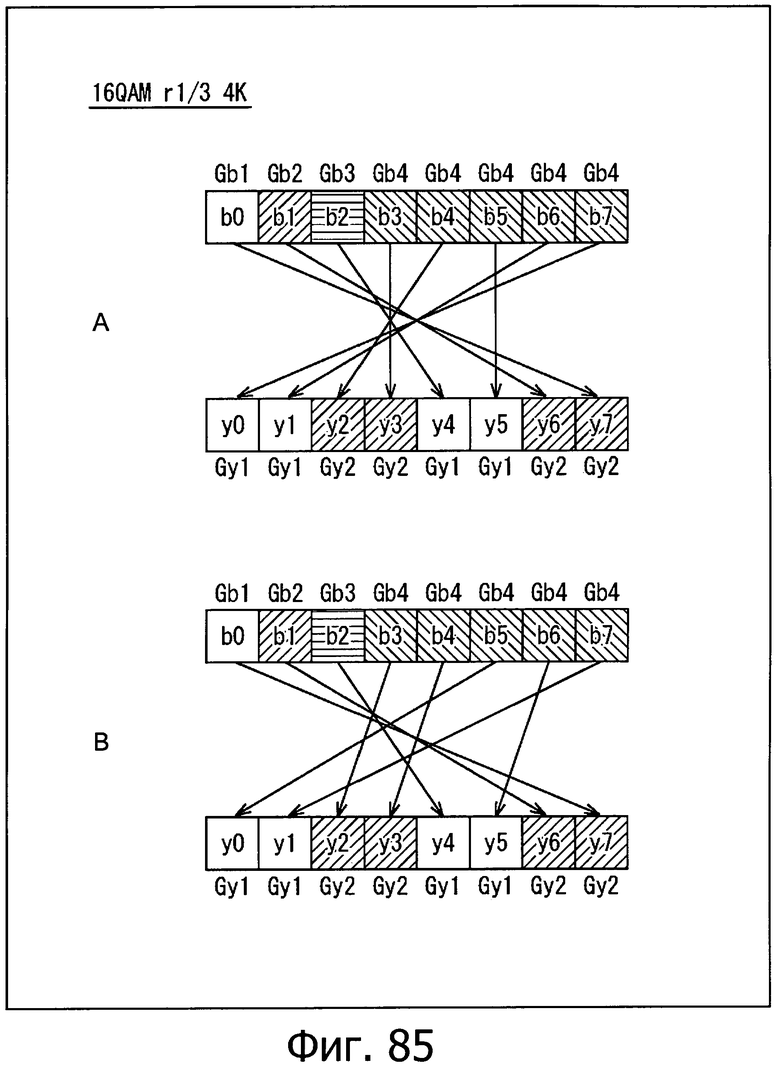

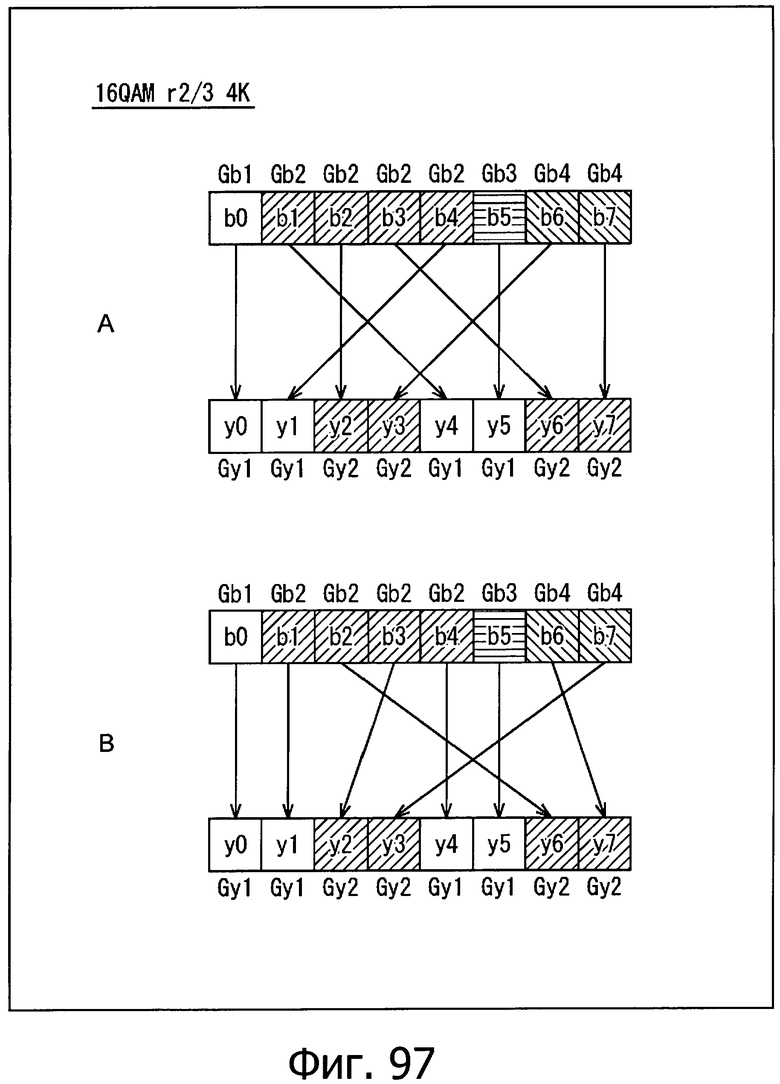

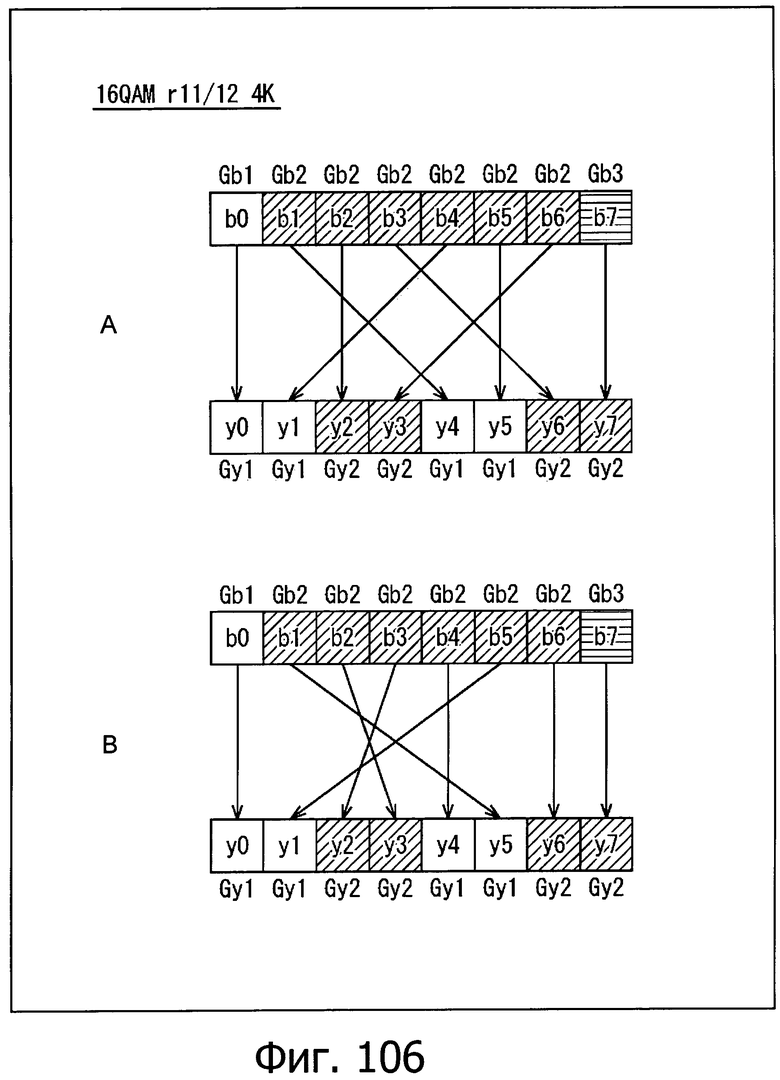

при этом при перестановке кодовых бит перестановка для назначения согласно указанному правилу назначения осуществляется таким образом, что (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 кодовых бит, считываемых в направлении строк из устройства хранения, является битом b#i и (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 символьных бит двух последовательных символов, является битом y#i,

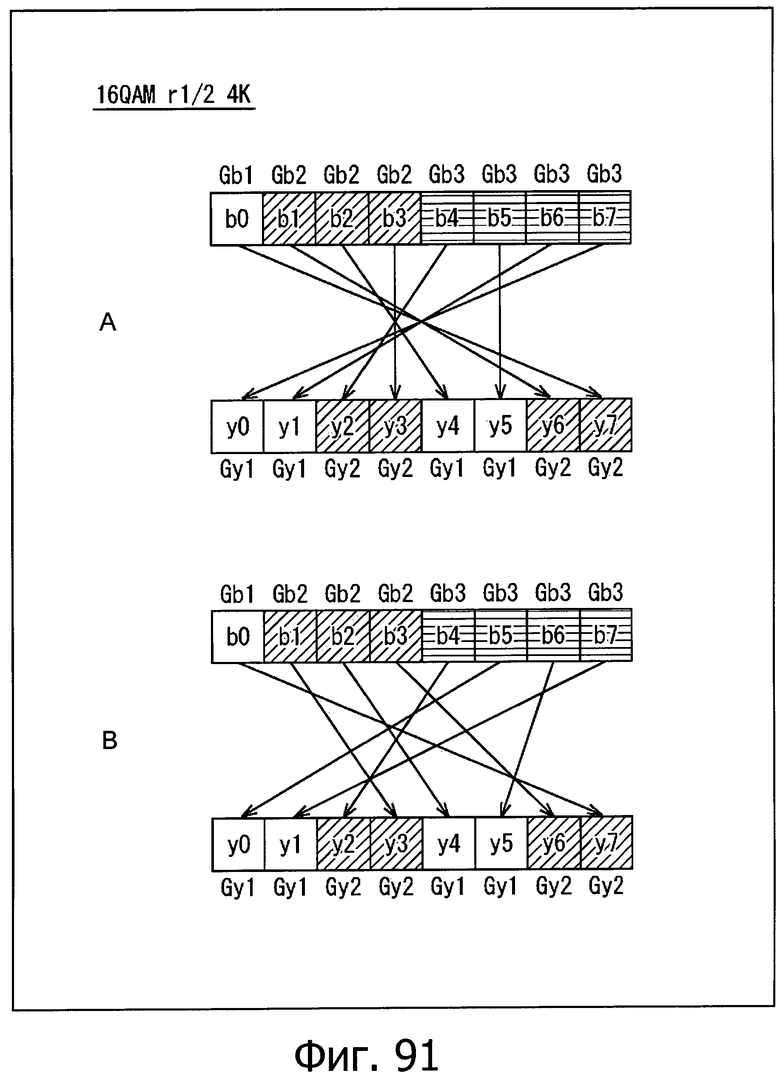

при этом бит b0 назначают биту y0, бит b1 назначают биту y4, бит b2 назначают биту y1, бит b3 назначают биту y6, бит b4 назначают биту y2, бит b5 назначают биту y5, бит b6 назначают биту y3 и бит b7 назначают биту y7,

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 1/2,

при этом проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

142 150 213 247 507 538 578 828 969 1042 1107 1315 1509 1584 1612 1781 1934 2106 2117

3 17 20 31 97 466 571 580 842 983 1152 1226 1261 1392 1413 1465 1480 2047 2125 49 169 258 548 582 839 873 881 931 995 1145 1209 1639 1654 1776 1826 1865 1906 1956

148 393 396 486 568 806 909 965 1203 1256 1306 1371 1402 1534 1664 1736 1844 1947 2055

185 191 263 290 384 769 981 1071 1202 1357 1554 1723 1769 1815 1842 1880 1910 1926 1991

424 444 923 1679

91 436 535 978

362 677 821 1695

1117 1392 1454 2030

35 840 1477 2152

1061 1202 1836 1879

242 286 1140 1538

111 240 481 760

59 1268 1899 2144

737 1299 1395 2072

34 288 810 1903

232 1013 1365 1729

410 783 1066 1187

113 885 1423 1560

760 909 1475 2048

68 254 420 1867

283 325 334 970

168 321 479 554

378 836 1913 1928

101 238 964 1393

304 460 1497 1588

151 192 1075 1614

297 313 677 1303

329 447 1348 1832

582 831 984 1900

Устройство обработки данных/способ обработки данных согласно третьему аспекту настоящего изобретения включает:

модуль/этап перестановки для перестановки кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и задает кодовые биты после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, хранящего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемых в направлении строк, устанавливают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

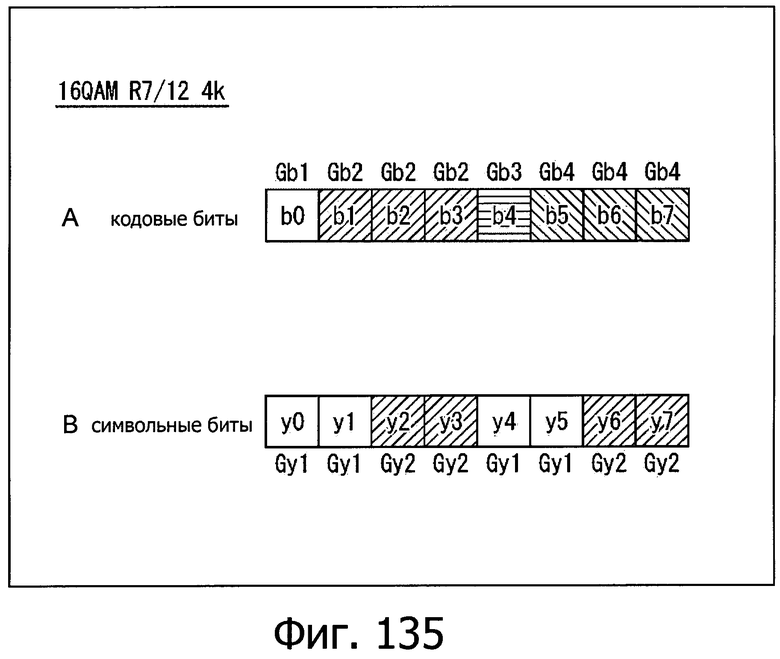

при этом правило назначения представляет собой правило, которое устанавливает группы бит, полученные посредством группирования кодовых бит в количестве mb бит в соответствии с вероятностью ошибки, в качестве групп кодовых бит и групп, полученных путем группирования символьных бит в количестве mb бит в соответствии с вероятностью ошибки, в качестве групп символьных бит, а также определяет набор групп, являющегося сочетанием группы кодовых бит и группы символьных бит, которым назначены кодовые биты из этой группы кодовых бит, и определяет число кодовых бит и число символьных бит в каждой группе кодовых бит и в каждой группе символьных бит в составе указанного набора групп,

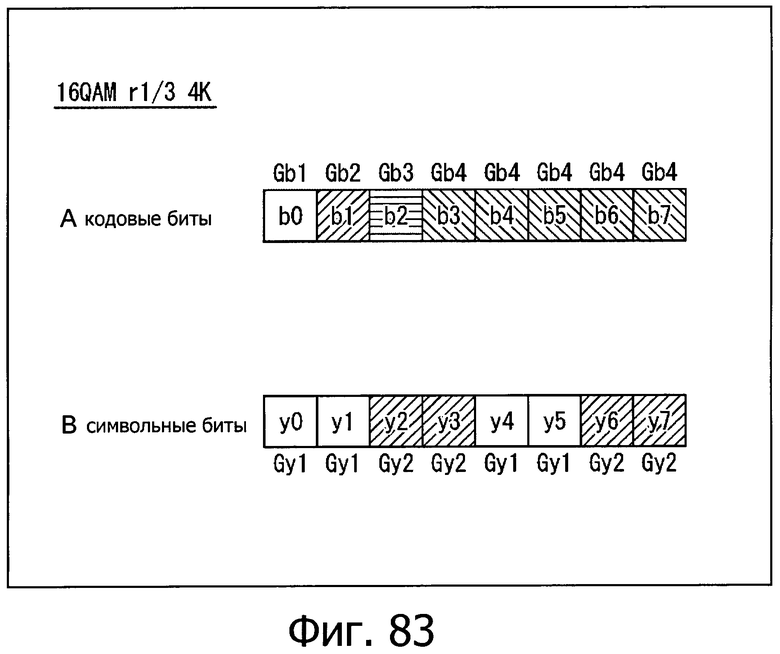

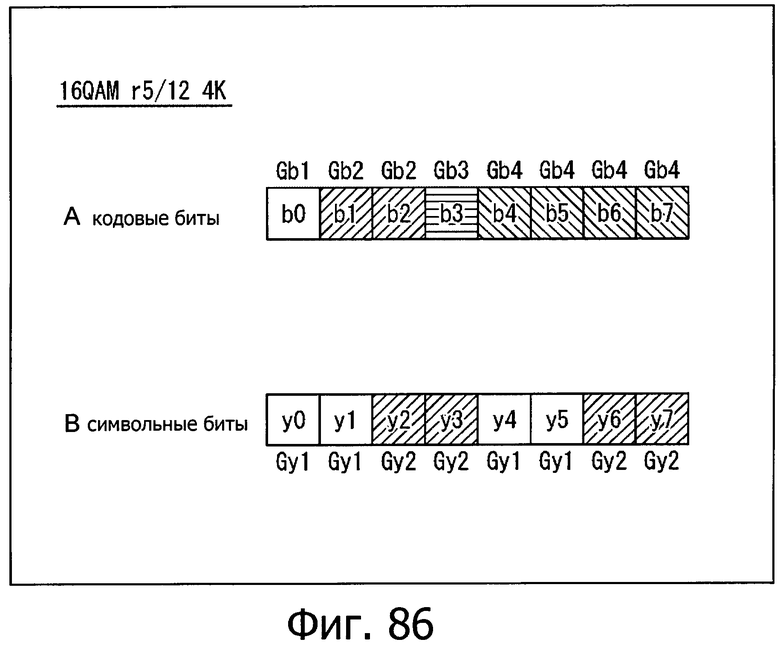

при этом в случае, когда m бит являются четырьмя битами, целое число b равно двум и четыре бита из совокупности кодовых бит преобразуют в одну из 16 сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа, кодовые биты в количестве 4×2 бит группируют в четыре группы кодовых бит и символьные биты в количестве 4×2 бит группируют в две группы символьных бит,

при этом по правилу назначения происходит назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение двух бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве двух бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей, назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является третьей после наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, и назначение трех бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является четвертой после наилучшей, в качестве трех бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей,

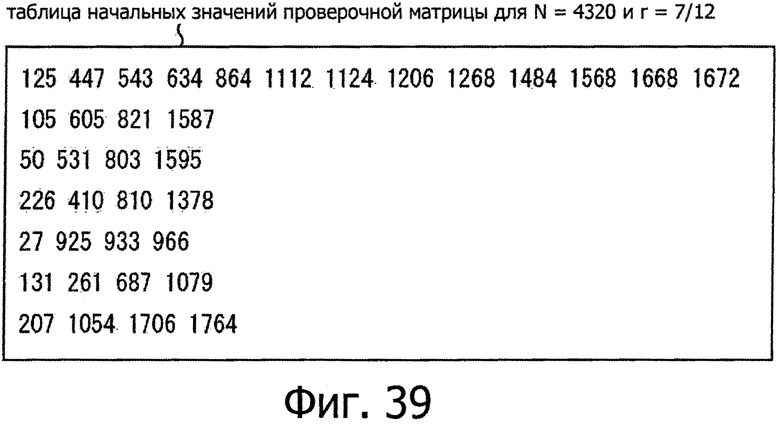

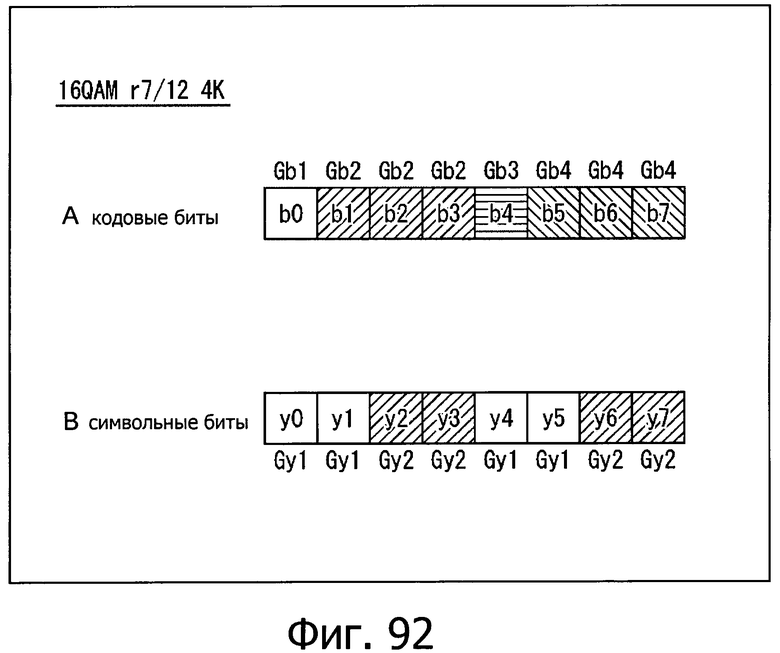

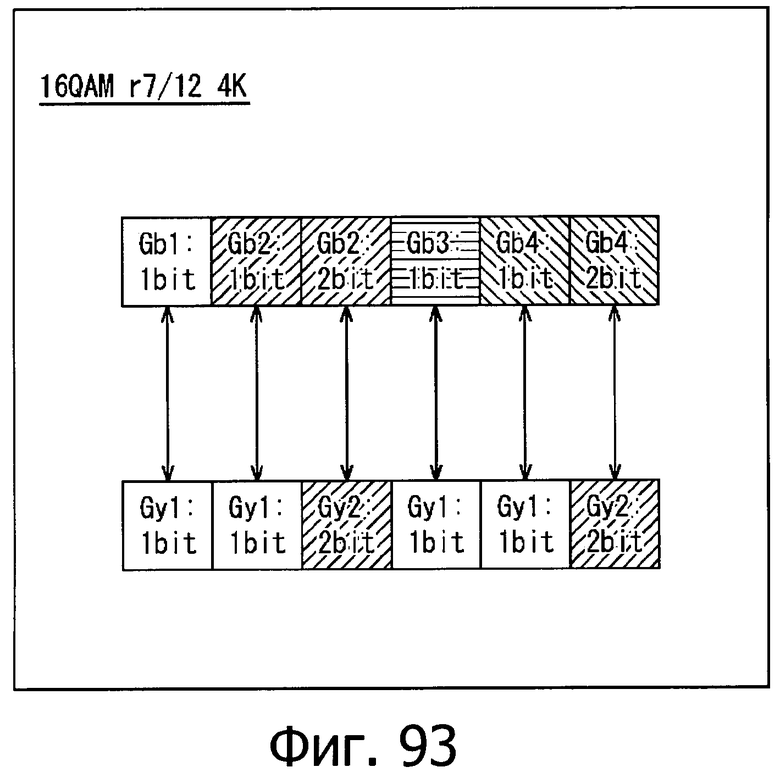

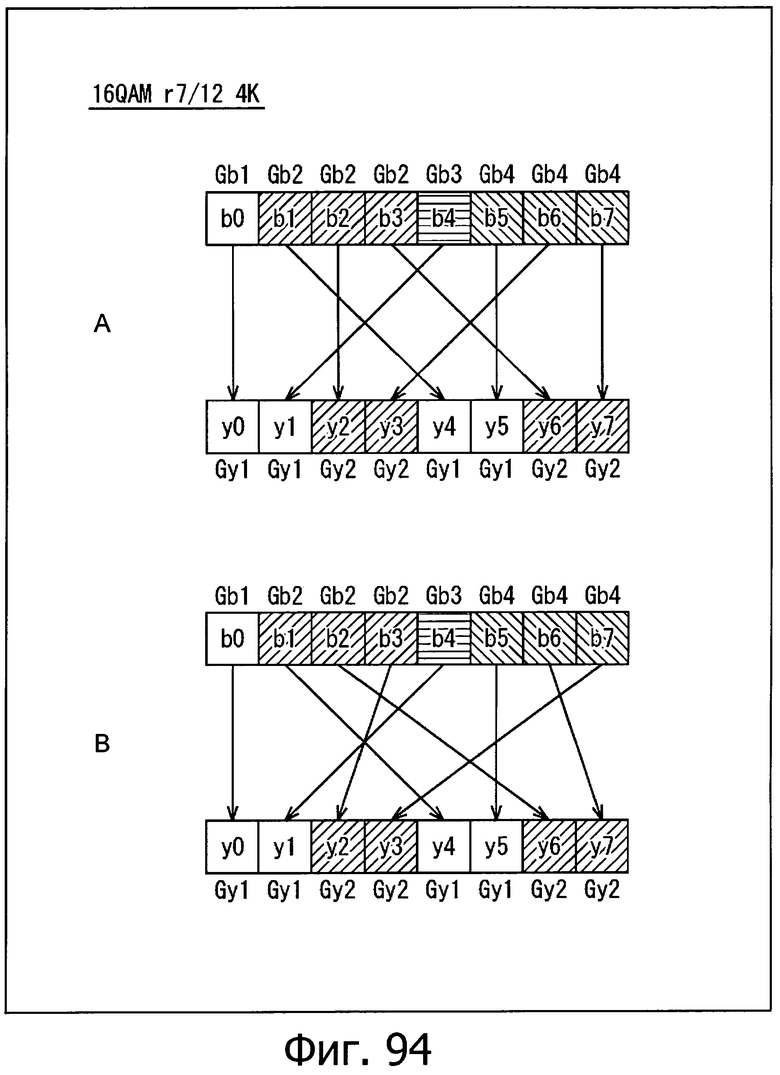

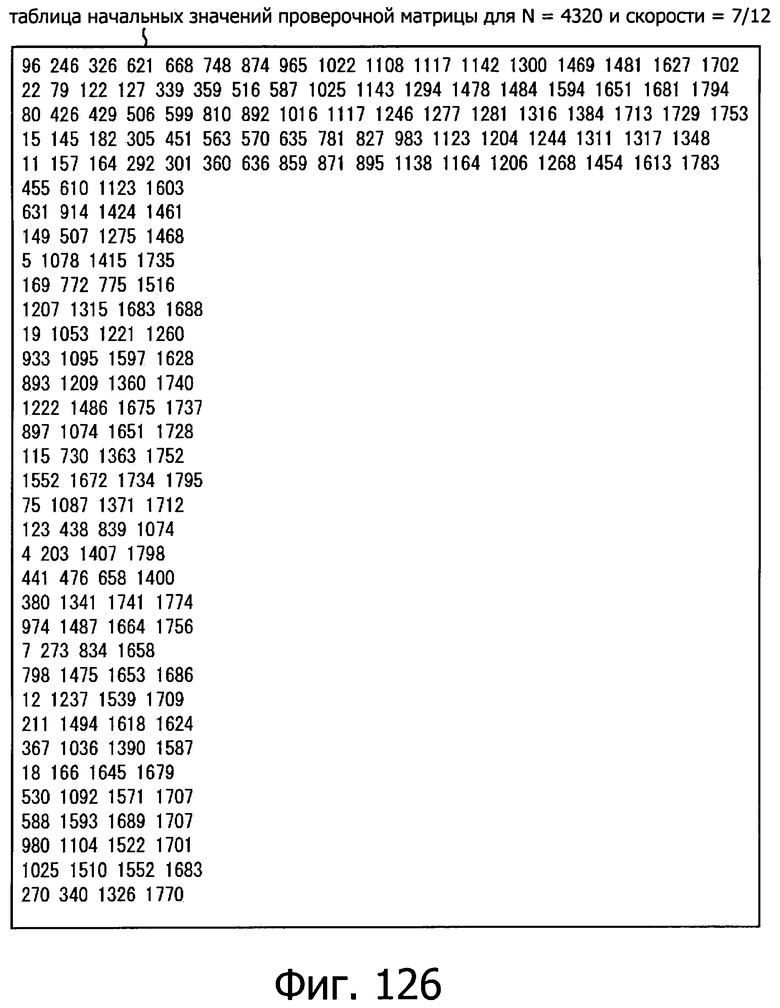

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4,320 бит, равна 7/12,

при этом проверочная матрица четности для кода LDPC сконфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

96 246 326 621 668 748 874 965 1022 1108 1117 1142 1300 1469 1481 1627 1702

22 79 122 127 339 359 516 587 1025 1143 1294 1478 1484 1594 1651 1681 1794

80 426 429 506 599 810 892 1016 1117 1246 1277 1281 1316 1384 1713 1729 1753

15 145 182 305 451 563 570 635 781 827 983 1123 1204 1244 1311 1317 1348

11 157 164 292 301 360 636 859 871 895 1138 1164 1206 1268 1454 1613 1783

455 610 1123 1603

631 914 1424 1461

149 507 1275 1468

5 1078 1415 1735

169 772 775 1516

1207 1315 1683 1688

19 1053 1221 1260

933 1095 1597 1628

893 1209 1360 1740

1222 1486 1675 1737

897 1074 1651 1728

115 730 1363 1752

1552 1672 1734 1795

75 1087 1371 1712

123 438 839 1074

4 203 1407 1798

441 476 658 1400

380 1341 1741 1774

974 1487 1664 1756

7 273 834 1658

798 1475 1653 1686

12 1237 1539 1709

211 1494 1618 1624

367 1036 1390 1587

18 166 1645 1679

530 1092 1571 1707

588 1593 1689 1707

980 1104 1522 1701

1025 1510 1552 1683

270 340 1326 1770

Устройство обработки данных/способ обработки данных согласно четвертому аспекту настоящего изобретения включает:

модуль/этап перестановки для перестановки кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и задает кодовые биты после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, сохраняющего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемые в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

при этом m бит являются четырьмя битами и целое число b равно двум,

при этом четыре бита из кодовых бит преобразуют в одну из 16 сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа,

при этом устройство хранения включает 8 столбцов, сохраняющих 4×2 бит в направлении строк, и сохраняет 4320/(4×2) бит в направлении столбцов,

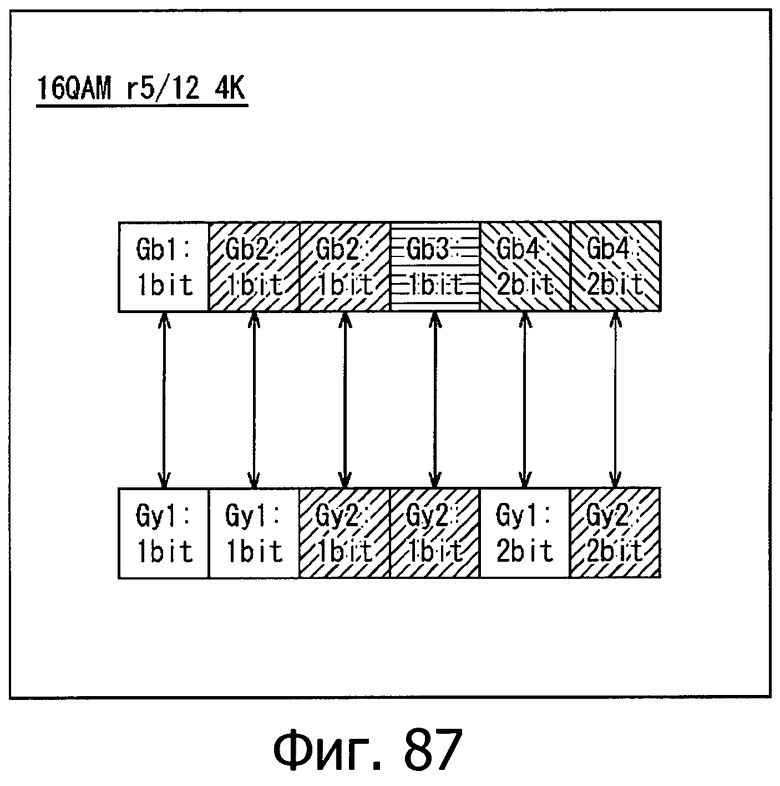

при этом в ходе перестановки кодовых бит перестановка для назначения согласно указанному правилу назначения осуществляется таким образом, что (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 кодовых бит, считываемых в направлении строк из устройства хранения, является битом b#i и (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 символьных бит двух последовательных символов, является битом y#i,

при этом бит b0 назначают биту y0, бит b1 назначают биту y4, бит b2 назначают биту y5, бит b3 назначают биту y2, бит b4 назначают биту y1, бит b5 назначают биту y6, бит b6 назначают биту y3 и бит b7 назначают биту y7,

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 7/12,

при этом проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

96 246 326 621 668 748 874 965 1022 1108 1117 1142 1300 1469 1481 1627 1702

22 79 122 127 339 359 516 587 1025 1143 1294 1478 1484 1594 1651 1681 1794

80 426 429 506 599 810 892 1016 1117 1246 1277 1281 1316 1384 1713 1729 1753

15 145 182 305 451 563 570 635 781 827 983 1123 1204 1244 1311 1317 1348

11 157 164 292 301 360 636 859 871 895 1138 1164 1206 1268 1454 1613 1783

455 610 1123 1603

631 914 1424 1461

149 507 1275 1468

5 1078 1415 1735

169 772 775 1516

1207 1315 1683 1688

19 1053 1221 1260

933 1095 1597 1628

893 1209 1360 1740

1222 1486 1675 1737

897 1074 1651 1728

115 730 1363 1752

1552 1672 1734 1795

75 1087 1371 1712

123 438 839 1074

4 203 1407 1798

441 476 658 1400

380 1341 1741 1774

974 1487 1664 1756

7 273 834 1658

798 1475 1653 1686

12 1237 1539 1709

211 1494 1618 1624

367 1036 1390 1587

18 166 1645 1679

530 1092 1571 1707

588 1593 1689 1707

980 1104 1522 1701

1025 1510 1552 1683

270 340 1326 1770

Устройство обработки данных/способ обработки данных согласно пятому аспекту настоящего изобретения включает:

модуль/этап перестановки для перестановки кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и задает кодовые биты после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, хранящего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемые в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

при этом правило назначения представляет собой правило, устанавливающее группы бит, полученные посредством группирования кодовых бит в количестве mb бит в соответствии с вероятностью ошибки, в качестве групп кодовых бит и группы, полученные посредством группирования символьных бит в количестве mb бит в соответствии с вероятностью ошибки, в качестве групп символьных бит, а также определяет набор групп, являющегося сочетанием группы кодовых бит и группы символьных бит, которым назначены кодовые биты из этой группы кодовых бит, и определяет число кодовых бит и число символьных бит в каждой группе кодовых бит и в каждой группе символьных бит в составе этого множества групп,

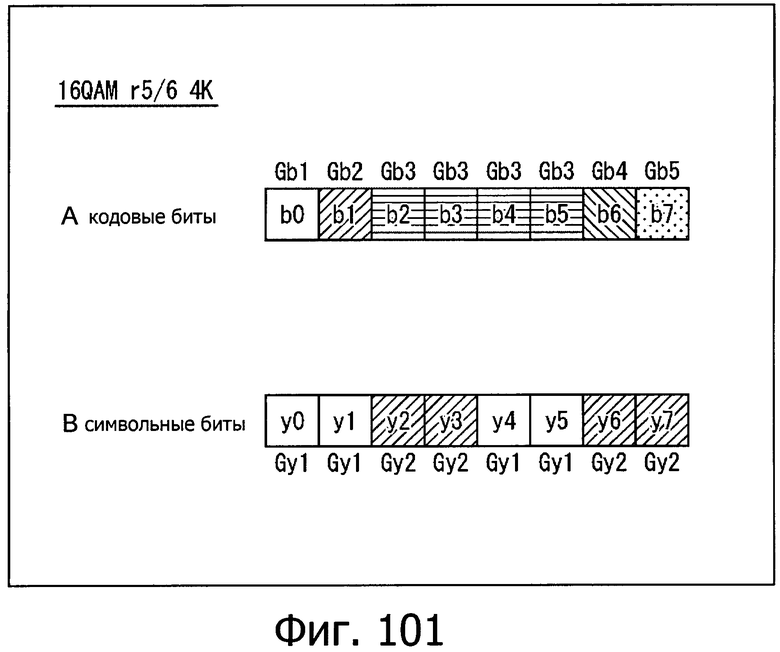

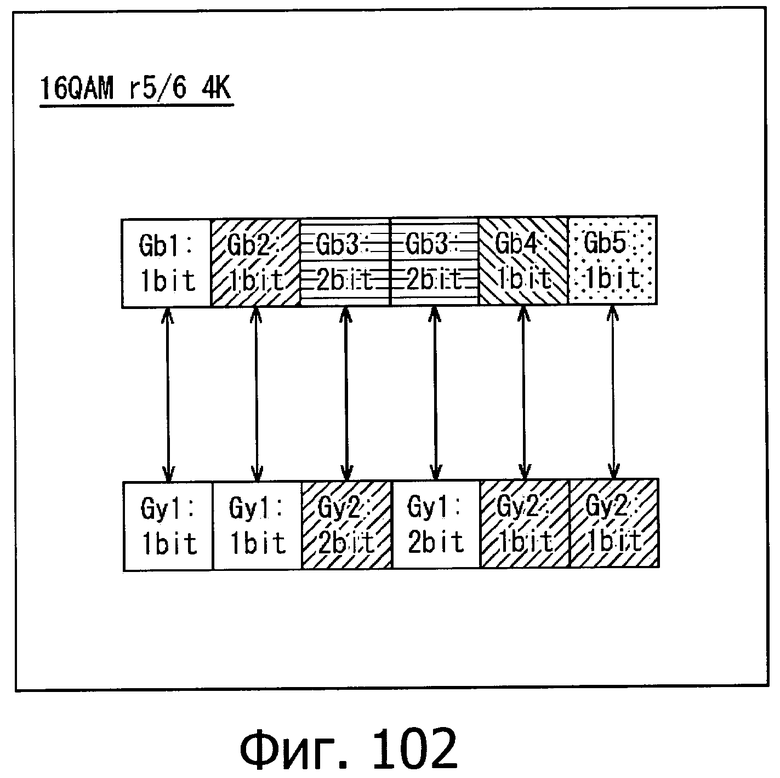

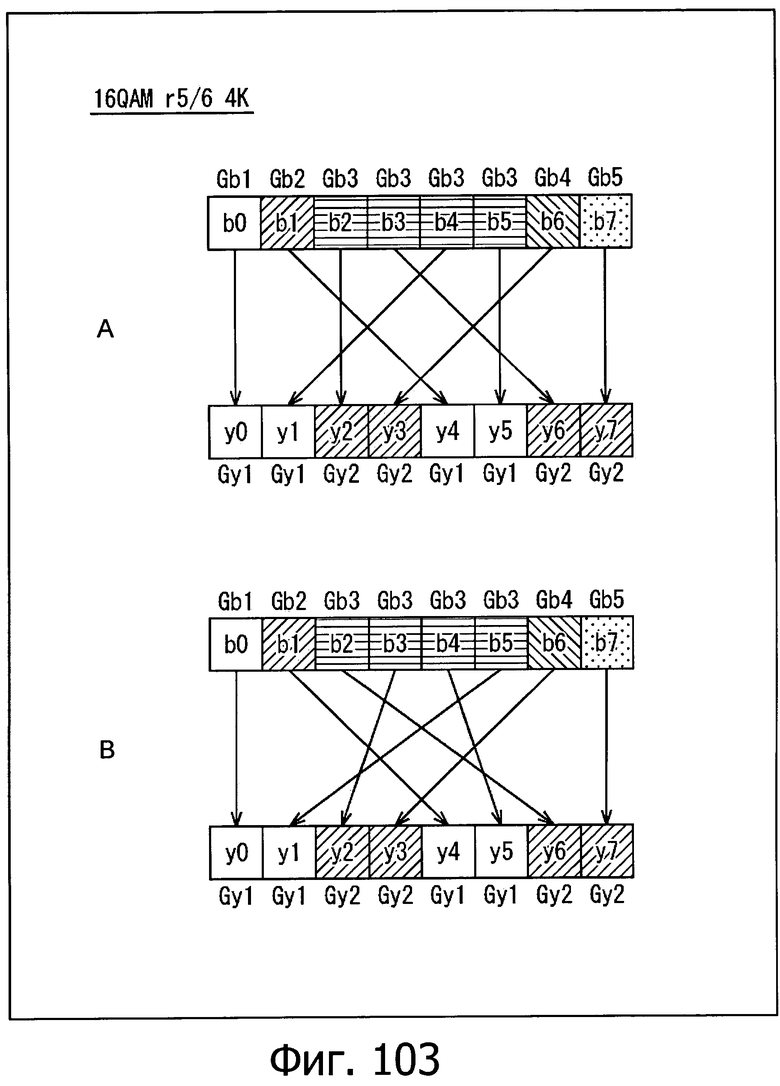

при этом в случае, где m бит являются четырьмя битами, целое число b равно двум и четыре бита из совокупности кодовых бит преобразуют в одну из 16 сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа, кодовые биты в количестве 4×2 бит группируют в четыре группы кодовых бит и символьные биты в количестве 4×2 бит группируют в две группы символьных бит,

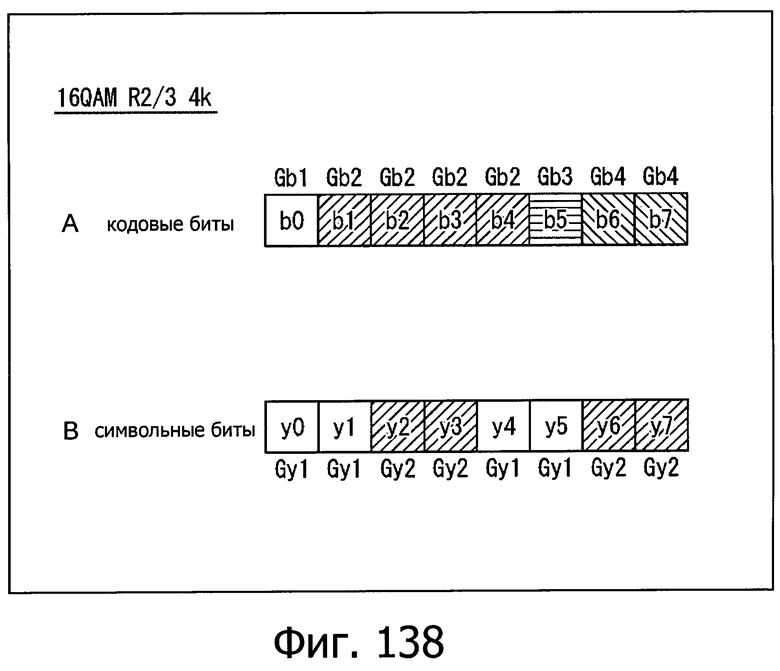

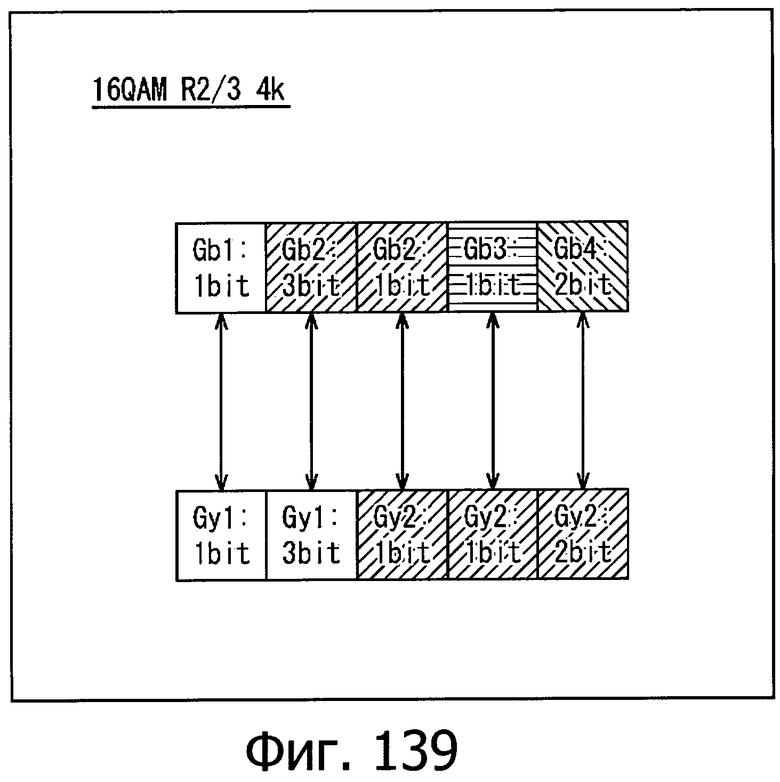

при этом по правилу назначения происходит назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение трех бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве трех бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей, назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является третьей после наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей, и назначение двух бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является четвертой после наилучшей, в качестве двух бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей,

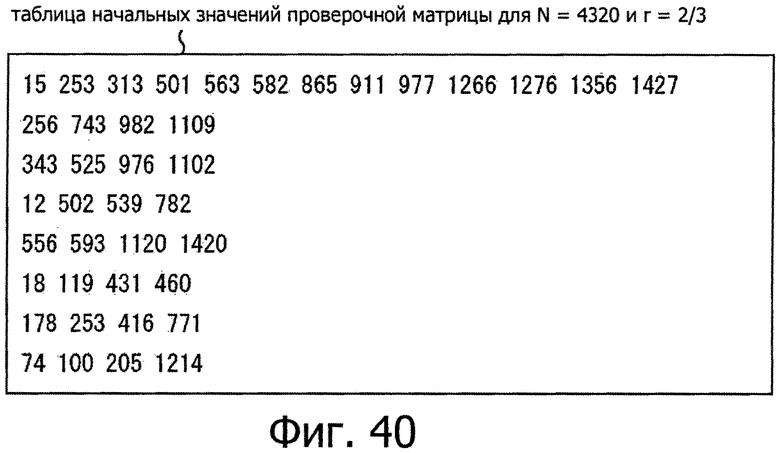

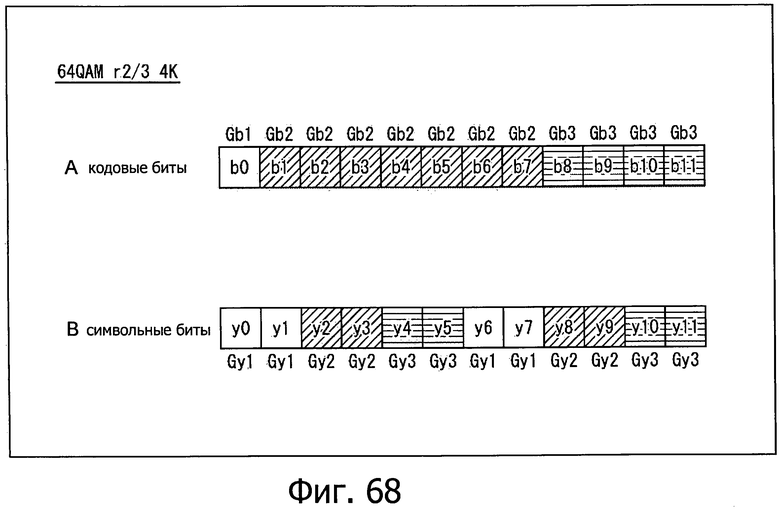

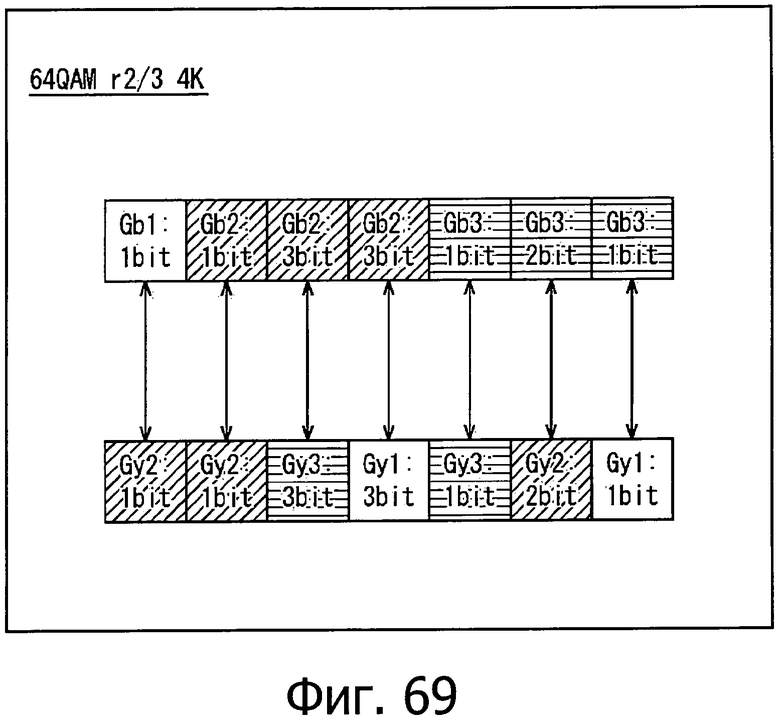

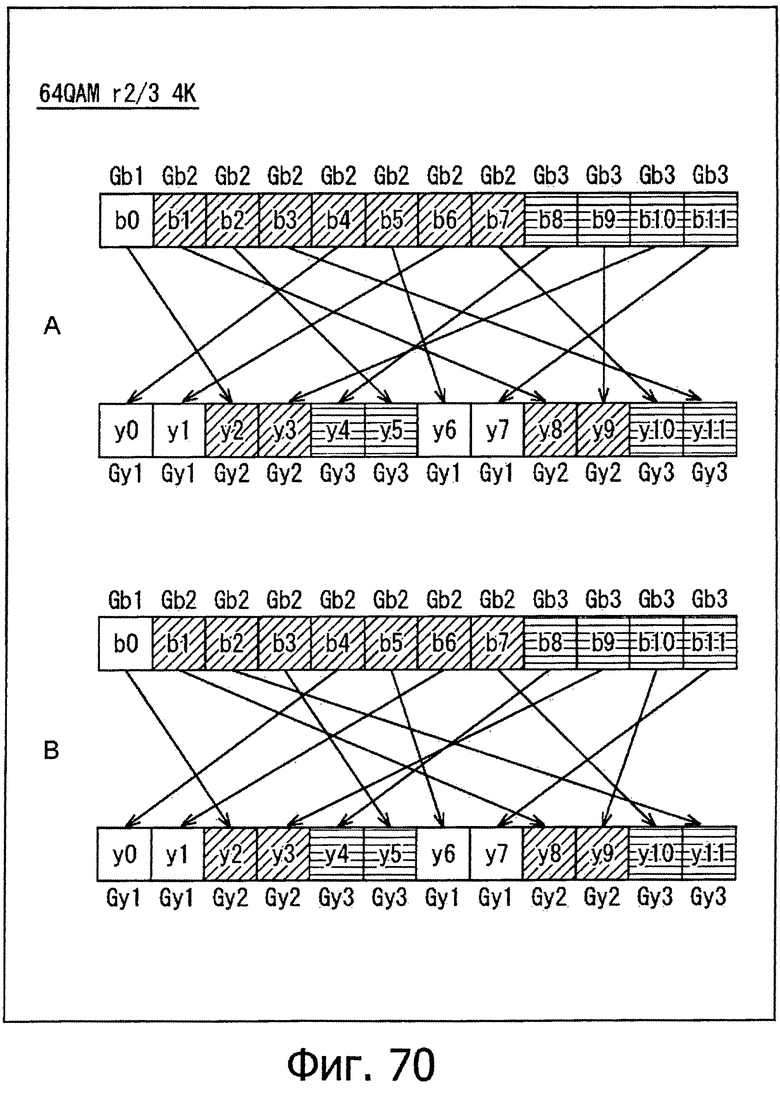

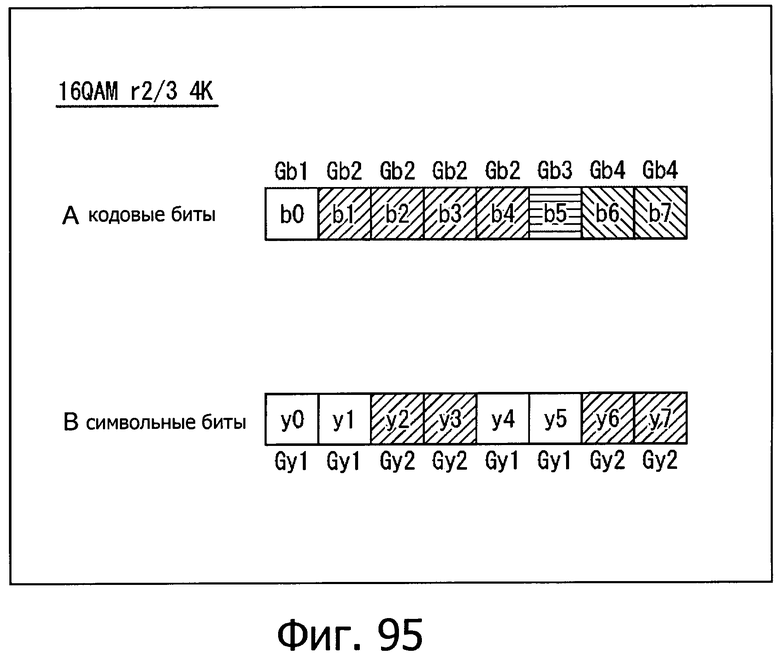

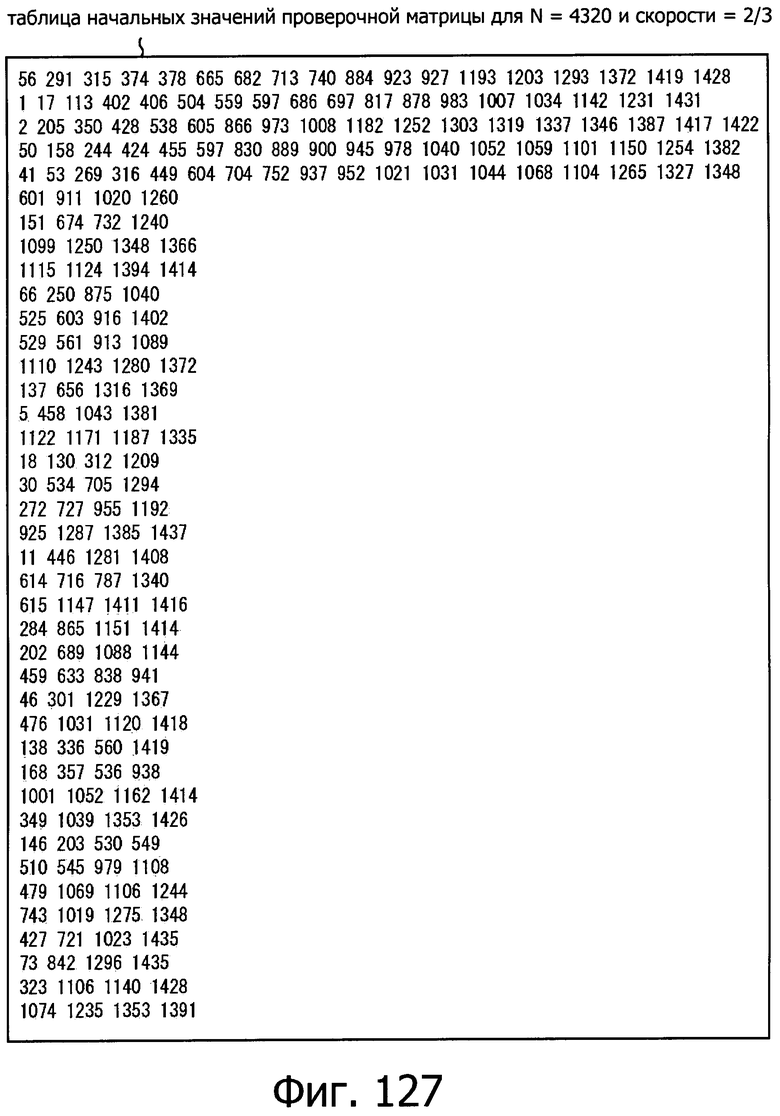

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 2/3,

при этом проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

56 291 315 374 378 665 682 713 740 884 923 927 1193 1203 1293 1372 1419 1428

1 17 113 402 406 504 559 597 686 697 817 878 983 1007 1034 1142 1231 1431

2 205 350 428 538 605 866 973 1008 1182 1252 1303 1319 1337 1346 1387 1417 1422

50 158 244 424 455 597 830 889 900 945 978 1040 1052 1059 1101 1150 1254 1382

41 53 269 316 449 604 704 752 937 952 1021 1031 1044 1068 1104 1265 1327 1348 601 911 1020 1260

151 674 732 1240

1099 1250 1348 1366

1115 1124 1394 1414

66 250 875 1040

525 603 916 1402

529 561 913 1089

1110 1243 1280 1372

137 656 1316 1369

5 458 1043 1381

1122 1171 1187 1335

18 130 312 1209

30 534 705 1294

272 727 955 1192

925 1287 1385 1437

11 446 1281 1408

614 716 787 1340

615 1147 1411 1416

284 865 1151 1414

202 689 1088 1144

459 633 838 941

46 301 1229 1367

476 1031 1120 1418

138 336 560 1419

168 357 536 938

1001 1052 1162 1414

349 1039 1353 1426

146 203 530 549

510 545 979 1108

479 1069 1106 1244

743 1019 1275 1348

427 721 1023 1435

73 842 1296 1435

323 1106 1140 1428

1074 1235 1353 1391

Устройство обработки данных/способ обработки данных согласно шестому аспекту настоящего изобретения включает:

модуль/этап перестановки, который осуществляет перестановку кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и задает кодовые биты после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, сохраняющего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемые в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

при этом m бит являются четырьмя битами и целое число b равно двум,

при этом четыре бита из совокупности кодовых бит преобразуют в одну из 16 сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа,

при этом устройство хранения включает 8 столбцов, сохраняющих 4×2 бит в направлении строк, и сохраняет 4320/(4×2) бит в направлении столбцов,

при этом в ходе перестановки кодовых бит перестановка для назначения согласно указанному правилу назначения осуществляется таким образом, что (#i+l)-biu бит, считая от самого старшего бита из совокупности 4×2 кодовых бит, считываемых в направлении строк из устройства хранения, является битом b#i и (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 символьных бит двух последовательных символов, является битом y#i,

при этом бит b0 назначают биту y0, бит b1 назначают биту y4, бит b2 назначают биту y5, бит b3 назначают биту y2, бит b4 назначают биту y1, бит b5 назначают биту y6, бит b6 назначают биту y3 и бит b7 назначают биту у7,

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 2/3,

при этом проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

56 291 315 374 378 665 682 713 740 884 923 927 1193 1203 1293 1372 1419 1428

1 17 113 402 406 504 559 597 686 697 817 878 983 1007 1034 1142 1231 1431

2 205 350 428 538 605 866 973 1008 1182 1252 1303 1319 1337 1346 1387 1417 1422 50 158 244 424 455 597 830 889 900 945 978 1040 1052 1059 1101 1150 1254 1382

41 53 269 316 449 604 704 752 937 952 1021 1031 1044 1068 1104 1265 1327 1348 601 911 1020 1260

151 674 732 1240

1099 1250 1348 1366

1115 1124 1394 1414

66 250 875 1040

525 603 916 1402

529 561 913 1089

1110 1243 1280 1372

137 656 1316 1369

5 458 1043 1381

1122 1171 1187 1335

18 130 312 1209

30 534 705 1294

272 727 955 1192

925 1287 1385 1437

11 446 1281 1408

614 716 787 1340

615 1147 1411 1416

284 865 1151 1414

202 689 1088 1144

459 633 838 941

46 301 1229 1367

476 1031 1120 1418

138 336 560 1419

168 357 536 938

1001 1052 1162 1414

349 1039 1353 1426

146 203 530 549

510 545 979 1108

479 1069 1106 1244

743 1019 1275 1348

427 721 1023 1435

73 842 1296 1435

323 1106 1140 1428

1074 1235 1353 1391

Устройство обработки данных/способ обработки данных согласно седьмому аспекту настоящего изобретения включает:

модуль/этап перестановки, который осуществляет перестановку кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и задает кодовые биты после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, сохраняющего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемые в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

при этом правило назначения представляет собой правило, устанавливающее группы бит, полученные посредством группирования кодовых бит в количестве mb бит в соответствии с вероятностью ошибки, в качестве групп кодовых бит и группы, полученные посредством группирования символьных бит в количестве mb бит в соответствии с вероятностью ошибки, в качестве групп символьных бит, а также определяет набор групп, являющееся сочетанием группы кодовых бит и группы символьных бит, которым назначены кодовые биты из этой группы кодовых бит, и определяет число кодовых бит и число символьных бит в каждой группе кодовых бит и в каждой группе символьных бит в составе указанного набора групп,

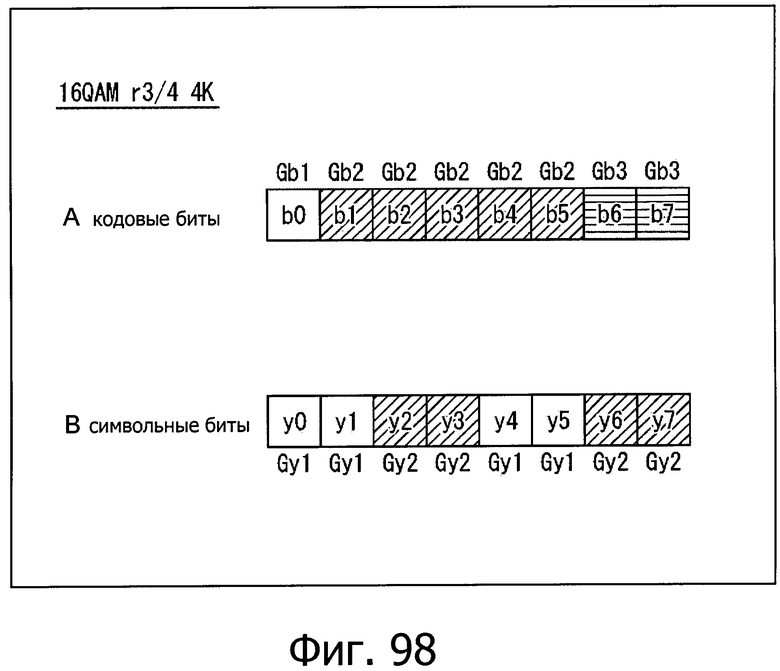

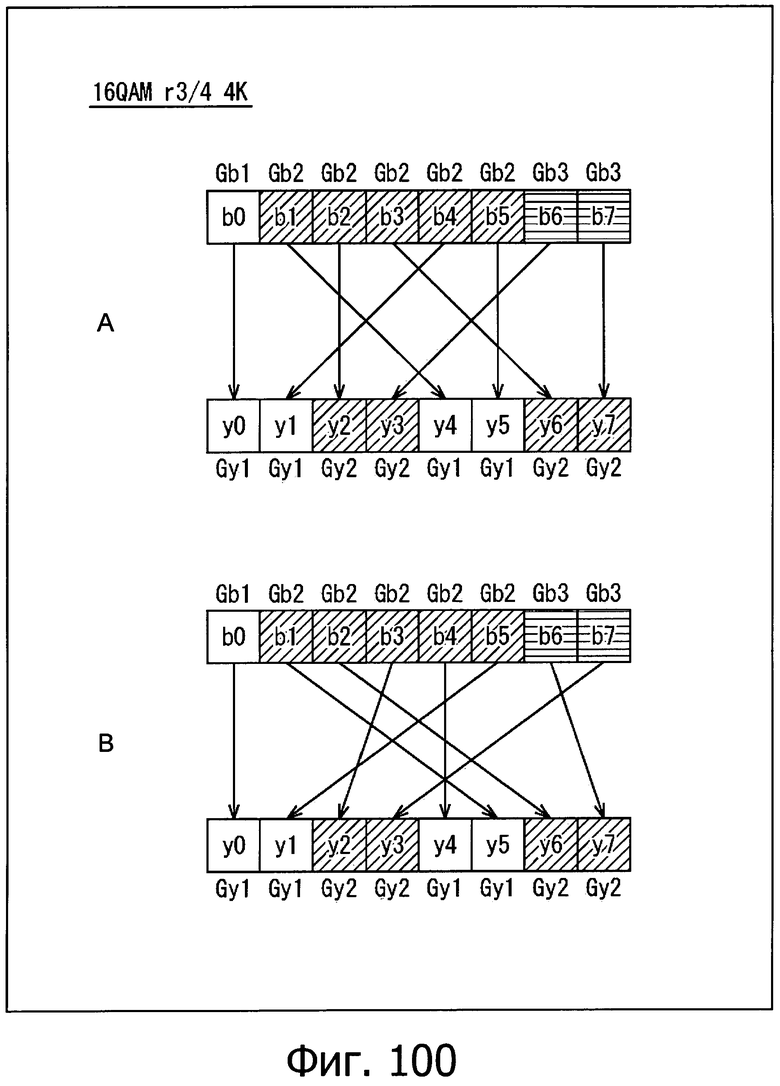

при этом в случае, где m бит являются четырьмя битами, целое число b равно двум, и четыре бита из совокупности кодовых бит преобразуют в одну из 16 сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа, кодовые биты в количестве 4×2 бит группируют в три группы кодовых бит и символьные биты в количестве 4×2 бит группируют в две группы символьных бит,

при этом по правилу назначения происходит назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение трех бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве трех бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение двух бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве двух бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей, и назначение двух бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является третьей после наилучшей, в качестве двух бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей,

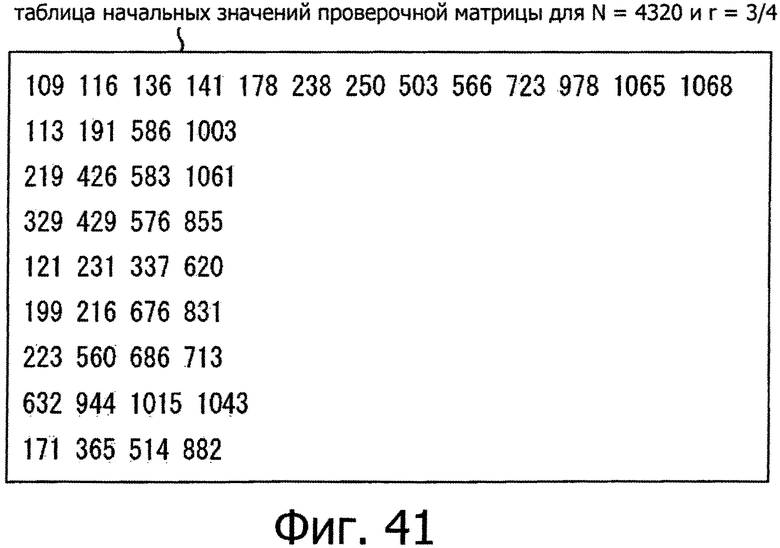

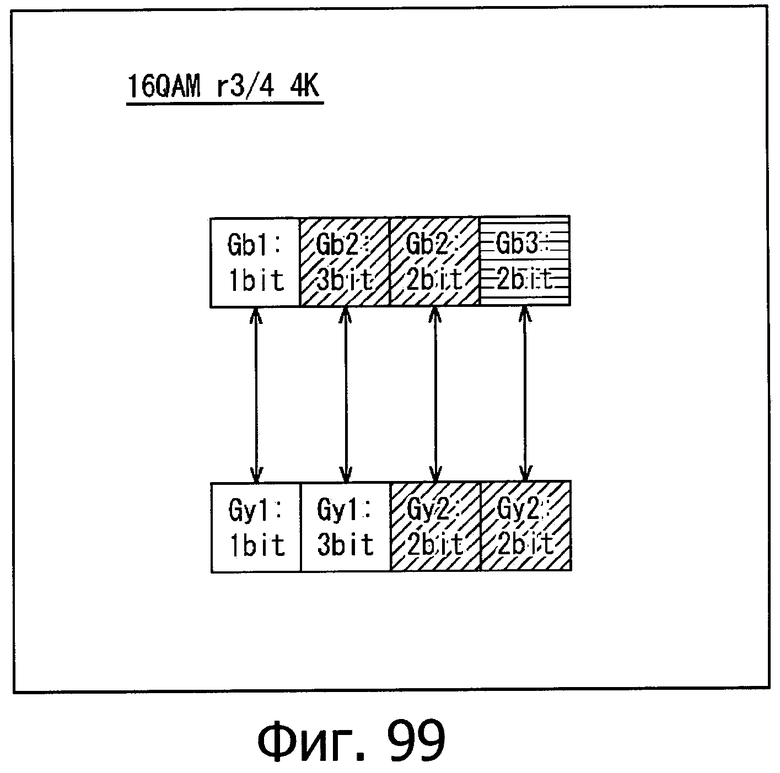

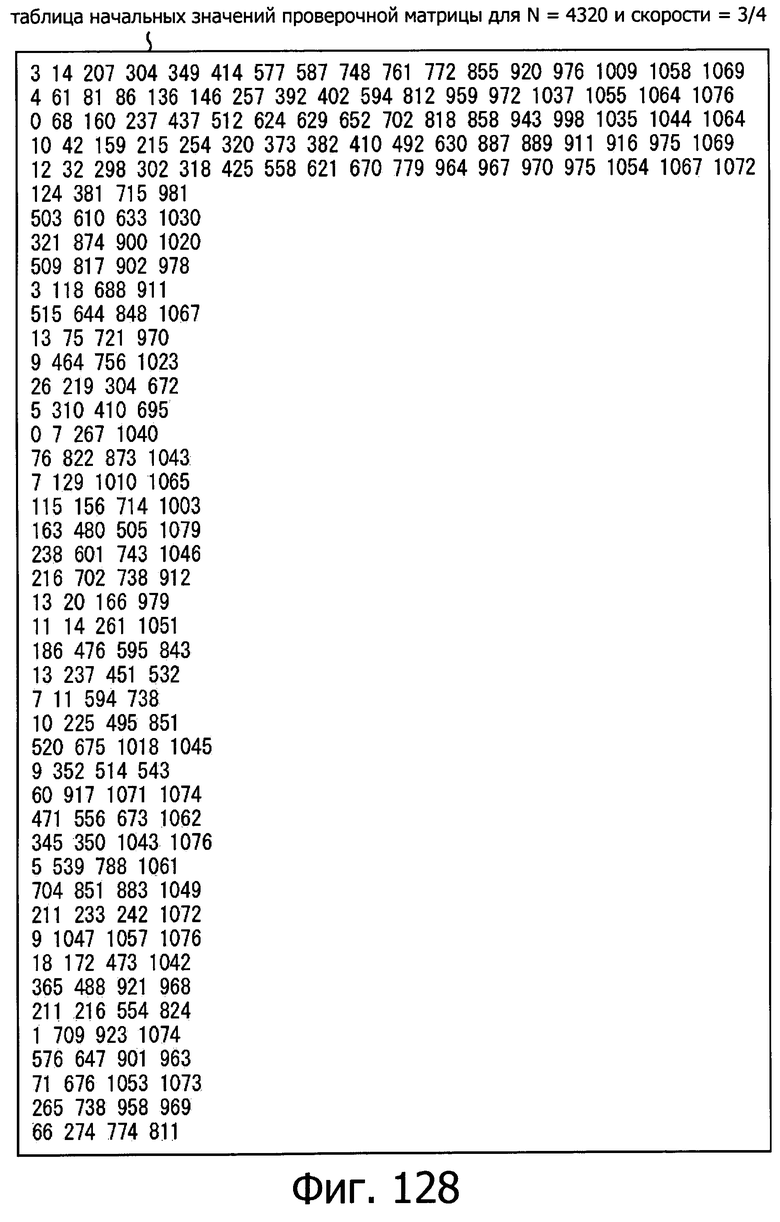

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 3/4,

при этом проверочная матрица четности для кода LDPC сконфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

3 14 207 304 349 414 577 587 748 761 772 855 920 976 1009 1058 1069

4 61 81 86 136 146 257 392 402 594 812 959 972 1037 1055 1064 1076

0 68 160 237 437 512 624 629 652 702 818 858 943 998 1035 1044 1064

10 42 159 215 254 320 373 382 410 492 630 887 889 911 916 975 1069

12 32 298 302 318 425 558 621 670 779 964 967 970 975 1054 1067 1072

124 381 715 981

503 610 633 1030

321 874 900 1020

509 817 902 978

3 118 688 911

515 644 848 1067

13 75 721 970

9 464 756 1023

26 219 304 672

5 310 410 695

0 7 267 1040

76 822 873 1043

7 129 1010 1065

115 156 714 1003

163 480 505 1079

238 601 743 1046

216 702 738 912

13 20 166 979

11 14261 1051

186 476 595 843

13 237 451 532

7 11 594 738

10 225 495 851

520 675 1018 1045

9 352 514 543

60 917 1071 1074

471 556 673 1062

345 350 1043 1076

5 539 788 1061

704 851 883 1049

211 233 242 1072

9 1047 1057 1076

18 172 473 1042

365 488 921 968

211 216 554 824

1 709 923 1074

576 647 901 963

71 676 1053 1073

265 738 958 969

66 274 774 811

Устройство обработки данных/способ обработки данных согласно восьмому аспекту настоящего изобретения включает:

модуль/этап перестановки для перестановки кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и задает кодовые биты после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, сохраняющего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемые в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

при этом m бит являются четырьмя битами и целое число b равно двум,

при этом четыре бита из совокупности кодовых бит преобразуют в одну из 16 сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа,

при этом устройство хранения включает 8 столбцов, сохраняющих 4×2 бит в направлении строк, и сохраняет 4320/(4×2) бит в направлении столбцов,

при этом в ходе перестановки кодовых бит перестановка для назначения согласно указанному правилу назначения осуществляется таким образом, что (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 кодовых бит, считываемых в направлении строк из устройства хранения, является битом b#i и (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 символьных бит двух последовательных символов, является битом y#i,

при этом бит b0 назначают биту y0, бит b1 назначают биту y4, бит b2 назначают биту y5, бит b3 назначают биту y2, бит b4 назначают биту y1, бит b5 назначают биту y6, бит b6 назначают биту y3 и бит b7 назначают биту y7,

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 3/4,

при этом проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

3 14 207 304 349 414 577 587 748 761 772 855 920 976 1009 1058 1069

4 61 81 86 136 146 257 392 402 594 812 959 972 1037 1055 1064 1076

0 68 160 237 437 512 624 629 652 702 818 858 943 998 1035 1044 1064 10 42 159 215 254 320 373 382 410 492 630 887 889 911 916 975 1069

12 32 298 302 318 425 558 621 670 779 964 967 970 975 1054 1067 1072

124 381 715 981

503 610 633 1030

321 874 900 1020

509 817 902 978

3 118 688 911

515 644 848 1067

13 75 721 970

9 464 756 1023

26 219 304 672

5 310 410 695

0 7 267 1040

76 822 873 1043

7 129 1010 1065

115 156 714 1003

163 480 505 1079

238 601 743 1046

216 702 738 912

13 20 166 979

11 14261 1051

186 476 595 843

13 237 451 532

7 11 594 738

10 225 495 851

520 675 1018 1045

9 352 514 543

60 917 1071 1074

471 556 673 1062

345 350 1043 1076

5 539 788 1061

704 851 883 1049

211 233 242 1072

9 1047 1057 1076

18 172 473 1042

365 488 921 968

211 216 554 824

1 709 923 1074

576 647 901 963

71 676 1053 1073

265 738 958 969

66 274 774 811

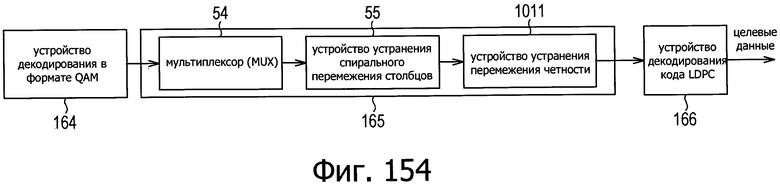

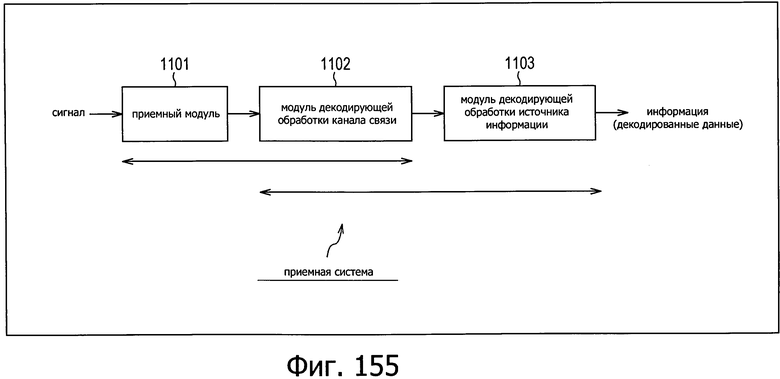

Устройство обработки данных согласно девятому аспекту настоящего изобретения включает:

модуль перестановки для перестановки кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и задает кодовые биты после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, сохраняющего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемые в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов; и

модуль обратной перестановки, осуществляющий процедуру обратной перестановки, в ходе которой полученные от передающего устройства кодовые биты, находящиеся в позициях после перестановки, возвращают в первоначальные позиции, в которых эти кодовые биты располагались до перестановки,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

при этом m бит являются четырьмя битами и целое число b равно двум,

при этом четыре бита из совокупности кодовых бит преобразуют в одну из 16 сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа,

при этом устройство хранения включает 8 столбцов, сохраняющих 4×2 бит в направлении строк, и сохраняет 4320/(4×2) бит в направлении столбцов,

при этом в ходе перестановки кодовых бит перестановка для назначения согласно указанному правилу назначения осуществляется таким образом, что (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 кодовых бит, считываемых в направлении строк из устройства хранения, является битом b#i и (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 символьных бит двух последовательных символов, является битом y#i,

при этом бит b0 назначают биту y0, бит b1 назначают биту y4, бит b2 назначают биту y1, бит b3 назначают биту y6, бит b4 назначают биту y2, бит b5 назначают биту y5, бит b6 назначают биту y3 и бит b7 назначают биту y7,

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 1/2,

при этом проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

142 150 213 247 507 538 578 828 969 1042 1107 1315 1509 1584 1612 1781 1934 2106 2117

3 17 20 31 97 466 571 580 842 983 1152 1226 1261 1392 1413 1465 1480 2047 2125 49 169 258 548 582 839 873 881 931 995 1145 1209 1639 1654 1776 1826 1865 1906 1956

148 393 396 486 568 806 909 965 1203 1256 1306 1371 1402 1534 1664 1736 1844 1947 2055

185 191 263 290 384 769 981 1071 1202 1357 1554 1723 1769 1815 1842 1880 1910 1926 1991

424 444 923 1679

91 436 535 978

362 677 821 1695

1117 1392 1454 2030

35 840 1477 2152

1061 1202 1836 1879

242 286 1140 1538

111 240 481 760

59 1268 1899 2144

737 1299 1395 2072

34 288 810 1903

232 1013 1365 1729

410 783 1066 1187

113 885 1423 1560

760 909 1475 2048

68 254 420 1867

283 325 334 970

168 321 479 554

378 836 1913 1928

101 238 964 1393

304 460 1497 1588

151 192 1075 1614

297 313 677 1303

329 447 1348 1832

582 831 984 1900

Устройство обработки данных согласно десятому аспекту настоящего изобретения включает:

модуль перестановки для перестановки кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и задает кодовые биты после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, сохраняющего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемые в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов; и

модуль обратной перестановки для обратной перестановки, в ходе которой полученные от передающего устройства кодовые биты, находящиеся в позициях после перестановки, возвращают в первоначальные позиции, в которых эти кодовые биты располагались до перестановки,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

при этом m бит являются четырьмя битами и целое число b равно двум,

при этом четыре бита из совокупности кодовых бит преобразуют в одну из 16

сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа,

при этом устройство хранения включает 8 столбцов, сохраняющих 4×2 бит в направлении строк, и сохраняет 4320/(4×2) бит в направлении столбцов,

при этом в ходе перестановки кодовых бит перестановка для назначения согласно указанному правилу назначения осуществляется таким образом, что (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 кодовых бит, считываемых в направлении строк из устройства хранения, является битом b#i и (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 символьных бит двух последовательных символов, является битом y#i,

при этом бит b0 назначают биту y0, бит b1 назначают биту y4, бит b2 назначают биту y5, бит b3 назначают биту y2, бит b4 назначают биту y1, бит b5 назначают биту y6, бит b6 назначают биту y3 и бит b7 назначают биту y7,

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 7/12,

при этом проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

96 246 326 621 668 748 874 965 1022 1108 1117 1142 1300 1469 1481 1627 1702

22 79 122 127 339 359 516 587 1025 1143 1294 1478 1484 1594 1651 1681 1794

80 426 429 506 599 810 892 1016 1117 1246 1277 1281 1316 1384 1713 1729 1753

15 145 182 305 451 563 570 635 781 827 983 1123 1204 1244 1311 1317 1348

11 157 164 292 301 360 636 859 871 895 1138 1164 1206 1268 1454 1613 1783

455 610 1123 1603

631 914 1424 1461

149 507 1275 1468

5 1078 1415 1735

169 772 775 1516

1207 1315 1683 1688

19 1053 1221 1260

933 1095 1597 1628

893 1209 1360 1740

1222 1486 1675 1737

897 1074 1651 1728

115 730 1363 1752

1552 1672 1734 1795

75 1087 1371 1712

123 438 839 1074

4 203 1407 1798

441 476 658 1400

380 1341 1741 1774

974 1487 1664 1756

7 273 834 1658

798 1475 1653 1686

12 1237 1539 1709

211 1494 1618 1624

367 1036 1390 1587

18 166 1645 1679

530 1092 1571 1707

588 1593 1689 1707

980 1104 1522 1701

1025 1510 1552 1683

270 340 1326 1770

Устройство обработки данных согласно одиннадцатому аспекту настоящего изобретения включает:

модуль перестановки для перестановки кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и установки кодовых биты после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, сохраняющего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемые в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов; и

модуль обратной перестановки, осуществляющий процедуру обратной перестановки, в ходе которой полученные от передающего устройства кодовые биты, находящиеся в позициях после перестановки, возвращают в первоначальные позиции, в которых эти кодовые биты располагались до перестановки,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

при этом m бит являются четырьмя битами и целое число b равно двум,

при этом четыре бита из совокупности кодовых бит преобразуют в одну из 16

сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа,

при этом устройство хранения включает 8 столбцов, сохраняющих 4×2 бит в направлении строк, и сохраняет 4320/(4×2) бит в направлении столбцов,

при этом в ходе перестановки кодовых бит перестановка для назначения согласно указанному правилу назначения осуществляется таким образом, что (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 кодовых бит, считываемых в направлении строк из устройства хранения, является битом b#i и (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 символьных бит двух последовательных символов, является битом y#i,

при этом бит b0 назначают биту y0, бит b1 назначают биту y4, бит b2 назначают биту y5, бит b3 назначают биту y2, бит b4 назначают биту y1, бит b5 назначают биту y6, бит b6 назначают биту y3 и бит b7 назначают биту y7,

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 2/3,

при этом проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

56 291 315 374 378 665 682 713 740 884 923 927 1193 1203 1293 1372 1419 1428

1 17 113 402 406 504 559 597 686 697 817 878 983 1007 1034 1142 1231 1431

2 205 350 428 538 605 866 973 1008 1182 1252 1303 1319 1337 1346 1387 1417 1422

50 158 244 424 455 597 830 889 900 945 978 1040 1052 1059 1101 1150 1254 1382 41 53 269 316 449 604 704 752 937 952 1021 1031 1044 1068 1104 1265 1327 1348 601 911 1020 1260

151 674 732 1240

1099 1250 1348 1366

1115 1124 1394 1414

66 250 875 1040

525 603 916 1402

529 561 913 1089

1110 1243 1280 1372

137 656 1316 1369

5 458 1043 1381

1122 1171 1187 1335

18 130 312 1209

30 534 705 1294

272 727 955 1192

925 1287 1385 1437

11 446 1281 1408

614 716 787 1340

615 1147 1411 1416

284 865 1151 1414

202 689 1088 1144

459 633 838 941

46 301 1229 1367

476 1031 1120 1418

138 336 560 1419

168 357 536 938

1001 1052 1162 1414

349 1039 1353 1426

146 203 530 549

510 545 979 1108

479 1069 1106 1244

743 1019 1275 1348

427 721 1023 1435

73 842 1296 1435

323 1106 1140 1428

1074 1235 1353 1391

Устройство обработки данных согласно двенадцатому аспекту настоящего изобретения включает:

модуль перестановки для перестановки кодовых бит в количестве mb бит в соответствии с правилом назначения, используемым для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и установки кодовых бит после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, сохраняющего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемые в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов; и

модуль обратной перестановки, осуществляющий процедуру обратной перестановки, в ходе которой полученные от передающего устройства кодовые биты, находящиеся в позициях после перестановки, возвращают в первоначальные позиции, в которых эти кодовые биты располагались до перестановки,

при этом код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит,

при этом m бит являются четырьмя битами и целое число b равно двум,

при этом четыре бита из совокупности кодовых бит преобразуют в одну из 16

сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа,

при этом устройство хранения включает 8 столбцов, сохраняющих 4×2 бит в направлении строк, и сохраняет 4320/(4×2) бит в направлении столбцов,

при этом в ходе перестановки кодовых бит перестановка для назначения согласно указанному правилу назначения осуществляется таким образом, что (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 кодовых бит, считываемых в направлении строк из устройства хранения, является битом b#i и (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 символьных бит двух последовательных символов, является битом y#i,

при этом бит b0 назначают биту y0, бит b1 назначают биту y4, бит b2 назначают биту y5, бит b3 назначают биту y2, бит b4 назначают биту y1, бит b5 назначают биту y6, бит b6 назначают биту y3 и бит b7 назначают биту y7,

при этом кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 3/4,

при этом проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, и

при этом таблица начальных значений проверочной матрицы сформирована следующим образом:

3 14 207 304 349 414 577 587 748 761 772 855 920 976 1009 1058 1069

4 61 81 86 136 146 257 392 402 594 812 959 972 1037 1055 1064 1076

0 68 160 237 437 512 624 629 652 702 818 858 943 998 1035 1044 1064

10 42 159 215 254 320 373 382 410 492 630 887 889 911 916 975 1069

12 32 298 302 318 425 558 621 670 779 964 967 970 975 1054 1067 1072

124 381 715 981

503 610 633 1030

321 874 900 1020

509 817 902 978

3 118 688 911

515 644 848 1067

13 75 721 970

9 464 756 1023

26 219 304 672

5 310 410 695

0 7 267 1040

76 822 873 1043

7 129 1010 1065

115 156 714 1003

163 480 505 1079

238 601 743 1046

216 702 738 912

13 20 166 979

11 14 261 1051

186 476 595 843

13 237 451 532

7 11 594 738

10 225 495 851

520 675 1018 1045

9 352 514 543

60 917 1071 1074

471 556 673 1062

345 350 1043 1076

5 539 788 1061

704 851 883 1049

211 233 242 1072

9 1047 1057 1076

18 172 473 1042

365 488 921 968

211 216 554 824

1 709 923 1074

576 647 901 963

71 676 1053 1073

265 738 958 969

66 274 774 811

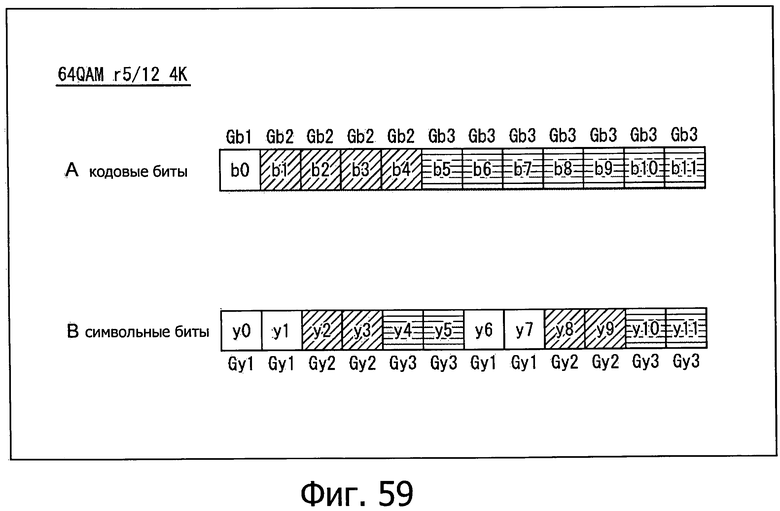

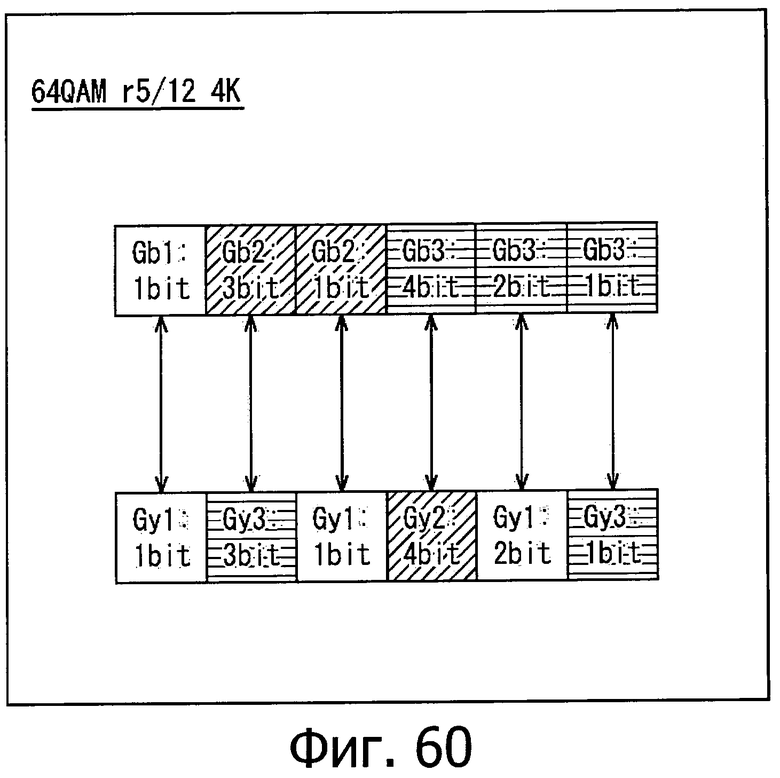

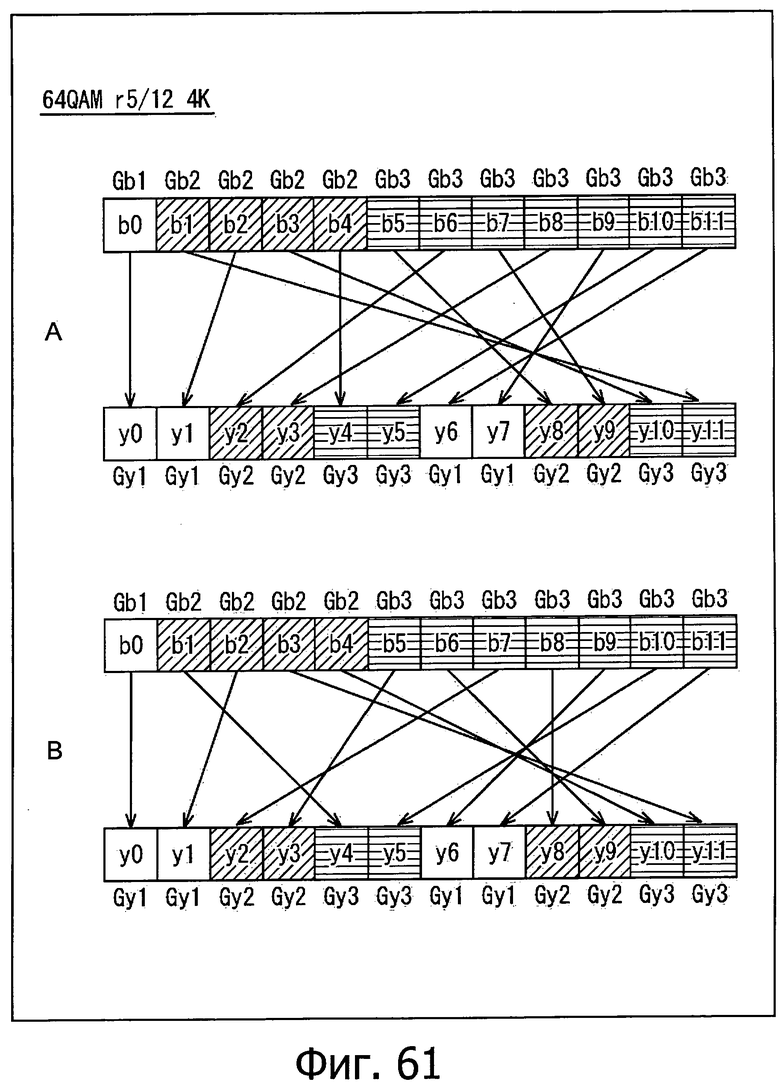

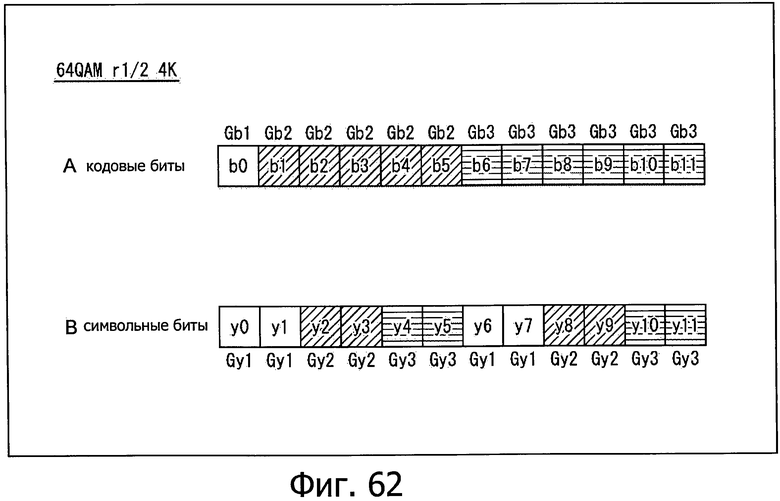

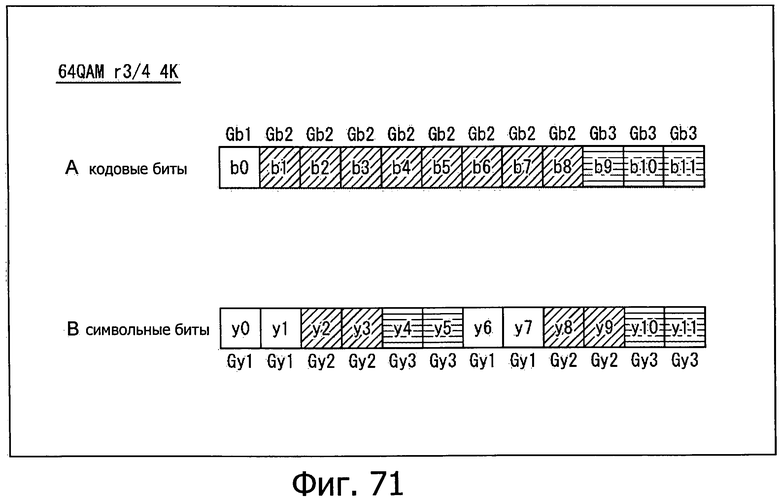

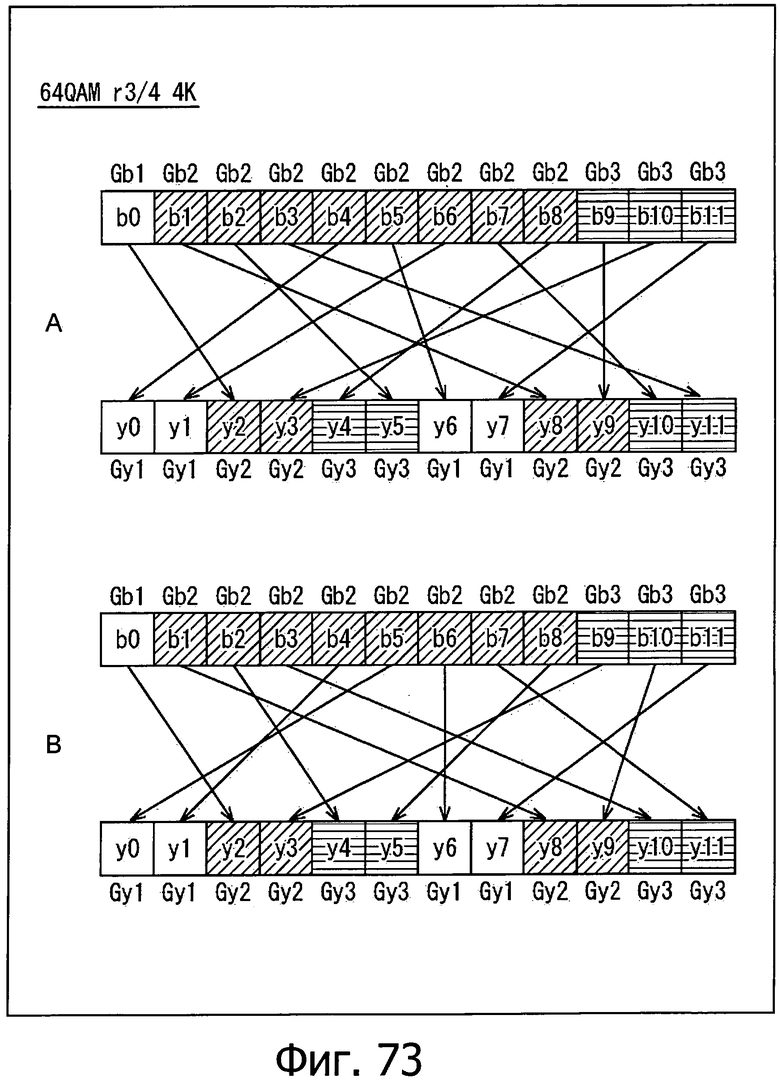

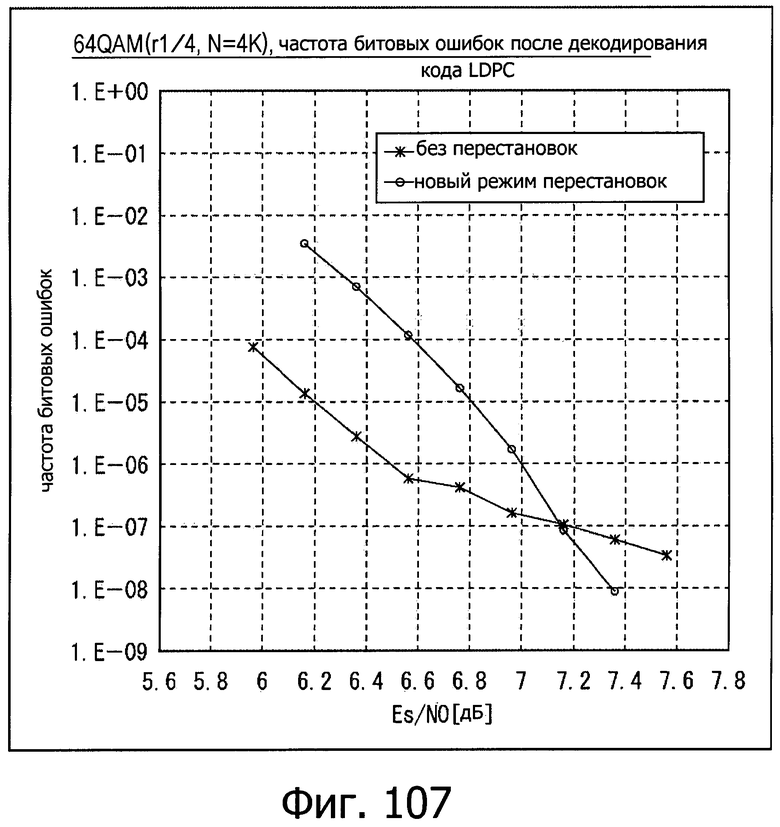

Согласно аспектам настоящего изобретения с первого по восьмой осуществляют перестановку кодовых бит в количестве mb бит в соответствии с правилом назначения кодовых бит кода LDPC символьным битам, представляющим символ, согласно правилу назначения, используемому для назначения кодовых бит кода LDPC символьным битам, представляющим символ, и задает кодовые биты после перестановки в качестве символьных бит в случае, когда кодовые биты кода LDPC (код низкой плотности с контролем четности), имеющего длину кода, равную N бит, записаны в направлении столбцов устройства хранения, сохраняющего кодовые биты в направлении строк и в направлении столбцов, m бит из числа кодовых бит кода LDPC, считываемые в направлении строк, задают в качестве одного символа, величине b присваивают заданное целое положительное значение, устройство хранения сохраняет mb бит в направлении строк и сохраняет N/(mb) бит в направлении столбцов, кодовые биты кода LDPC записывают в направлении столбцов устройства хранения и затем считывают в направлении строк, а кодовые биты в количестве mb бит, считываемых в направлении строк устройства хранения, образуют b символов.

Код LDPC представляет собой код LDPC, имеющий длину N кода, равную 4320 бит, а правило назначения представляет собой правило, которое задает группы бит, полученные посредством группирования кодовых бит в количестве mb бит в соответствии с вероятностью ошибки, в качестве групп кодовых бит и группы, полученные посредством группирования символьных бит в количестве mb бит в соответствии с вероятностью ошибки, в качестве групп символьных бит, а также определяет набор групп, являющееся сочетанием группы кодовых бит и группы символьных бит, которым назначены кодовые биты из этой группы кодовых бит, и определяет число кодовых бит и число символьных бит в каждой группе кодовых бит и в каждой группе символьных бит в составе этого множества групп.

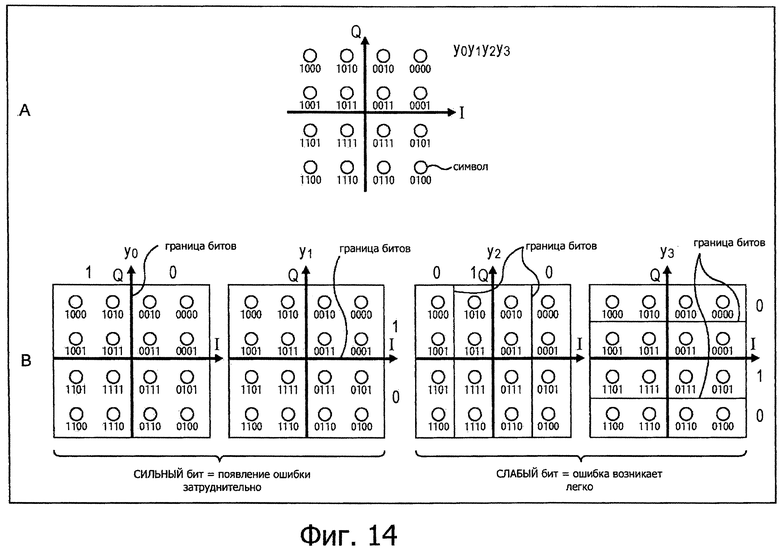

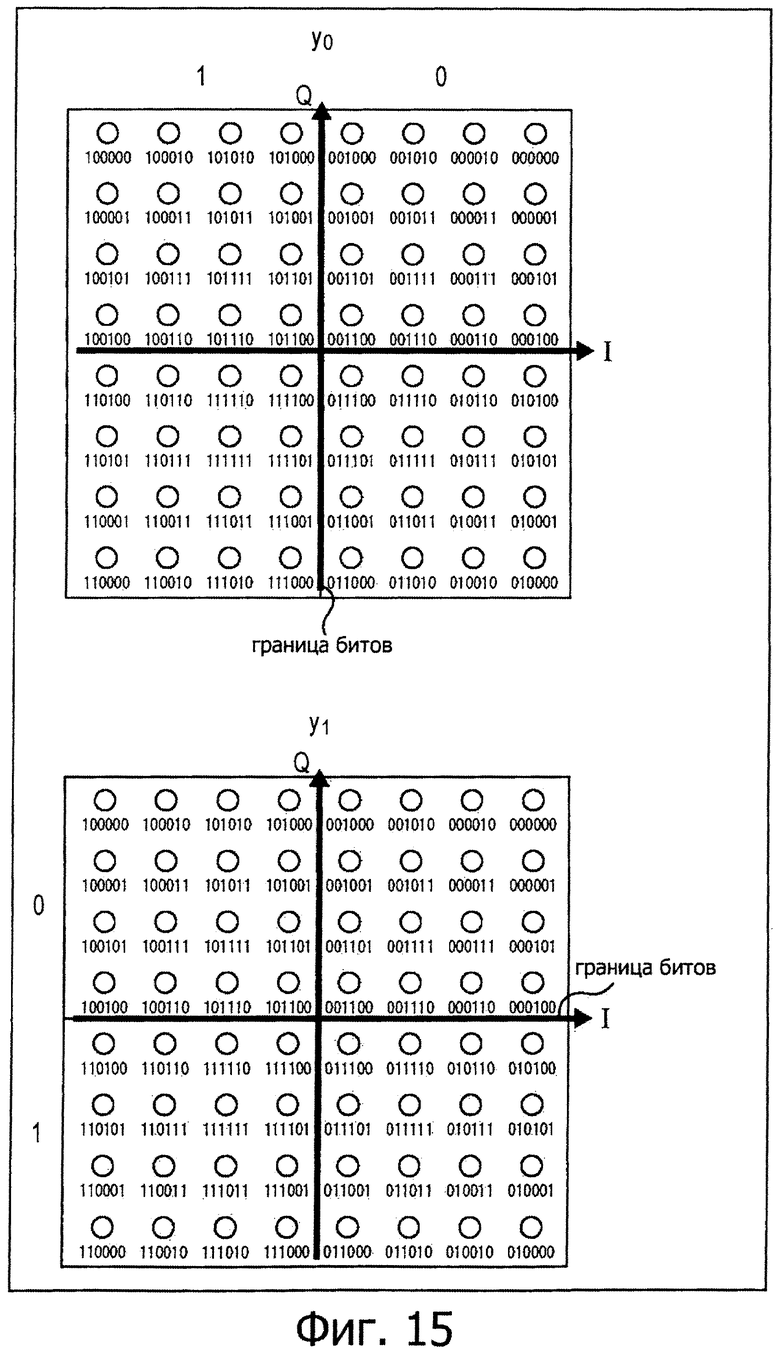

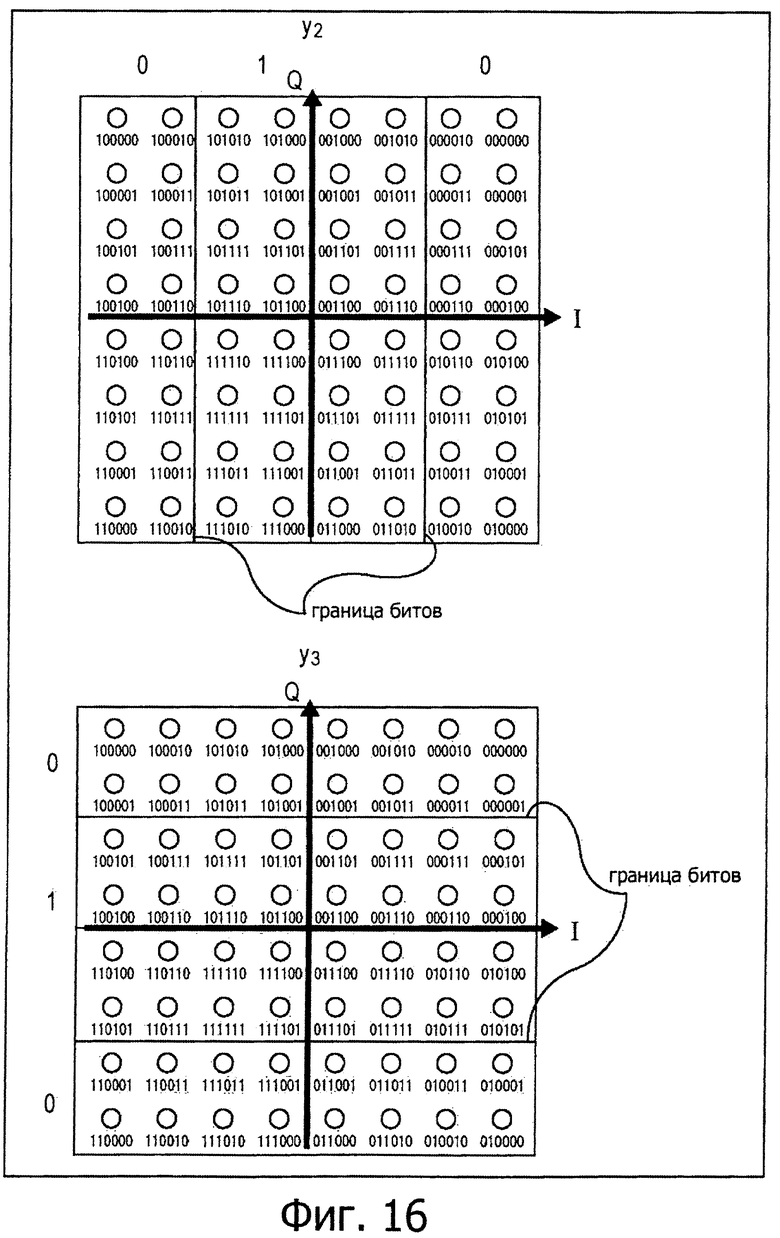

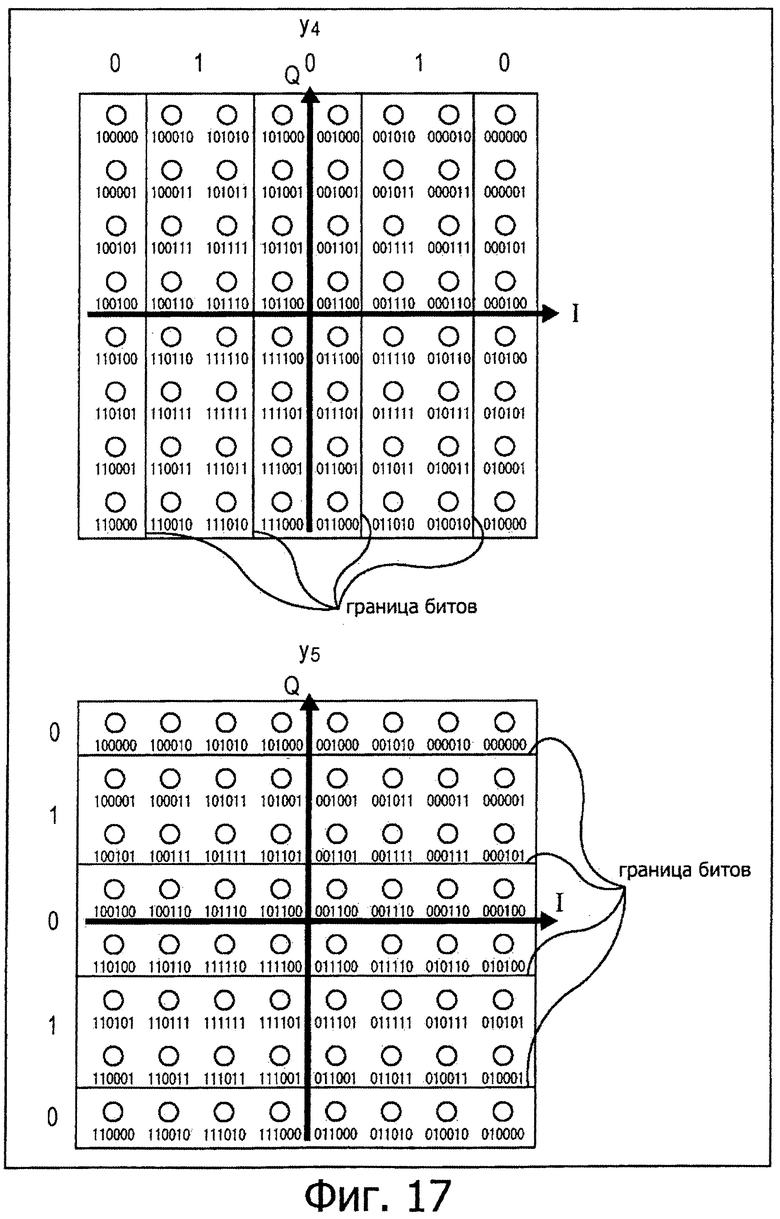

Кроме того, m бит являются четырьмя битами, целое число b равно двум и четыре бита из совокупности кодовых бит преобразуют в одну из 16 сигнальных точек, определенных в системе с модуляцией 16 QAM, в качестве одного символа.

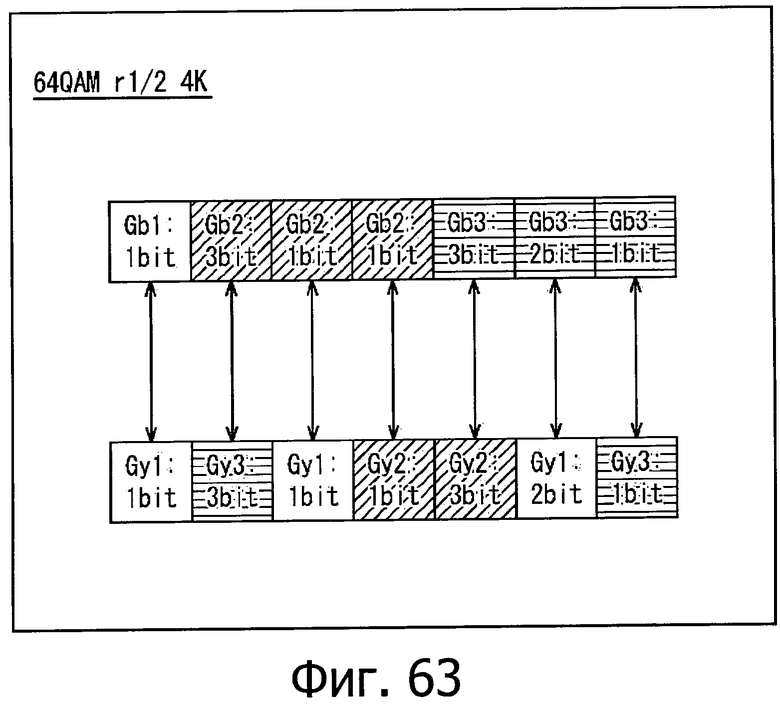

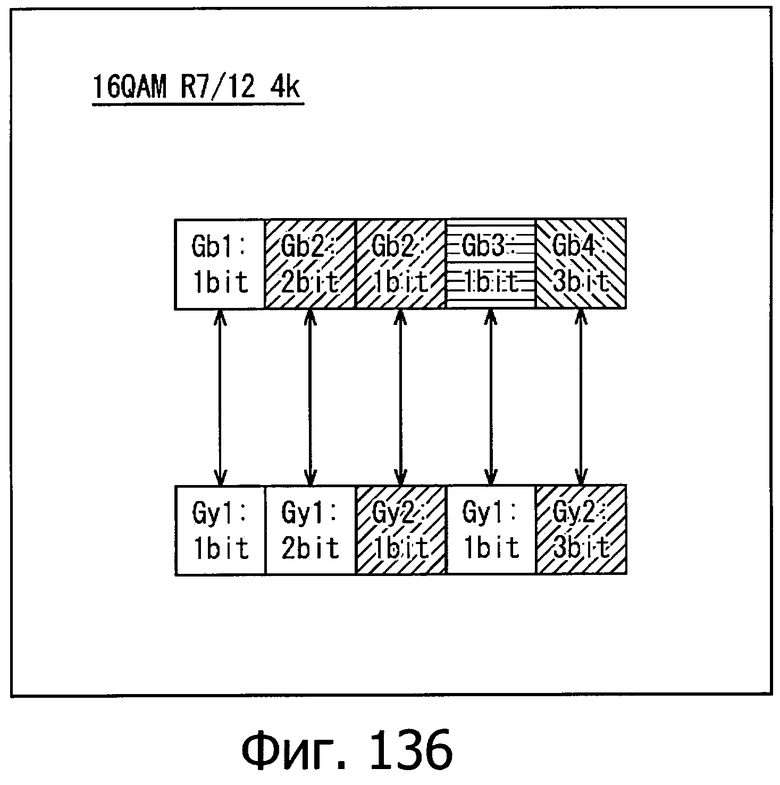

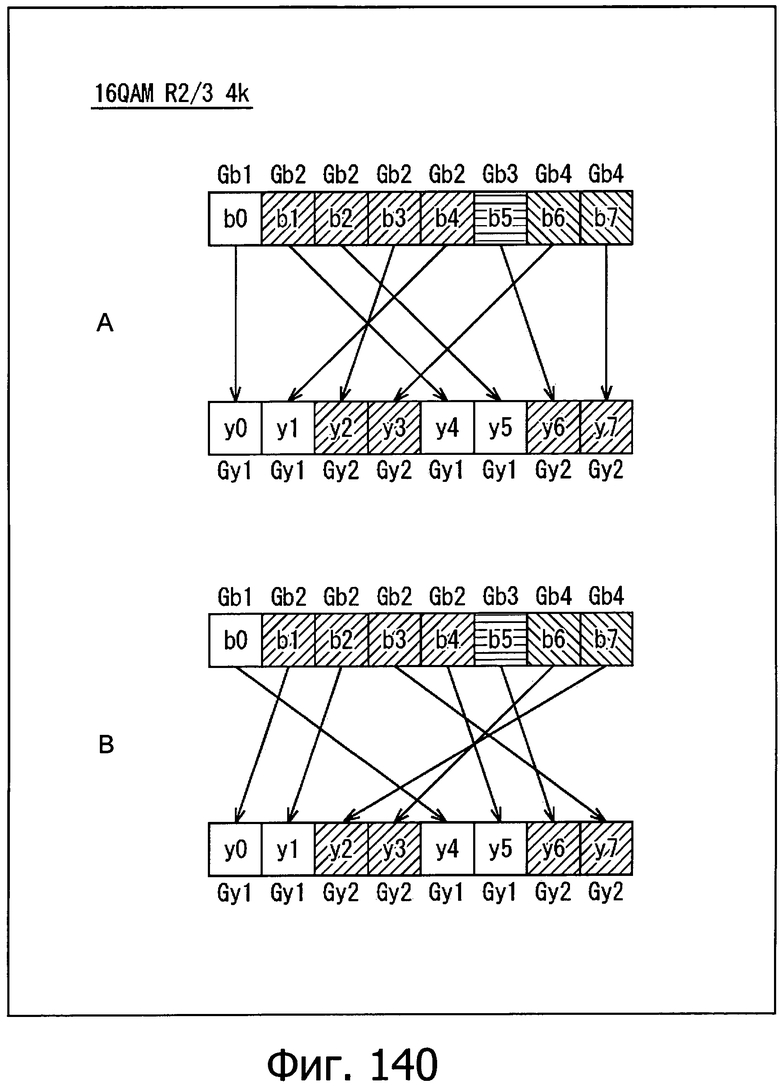

Согласно первому аспекту кодовые биты в количестве 4×2 бит группируют в три группы кодовых бит и символьные биты в количестве 4×2 бит группируют в две группы символьных бит, при этом кодовые биты переставляют в соответствии с правилом назначения, согласно которому происходит назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение двух бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве двух бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей, назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является третьей после наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, и назначение трех бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является третьей после наилучшей, в качестве трех бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей.

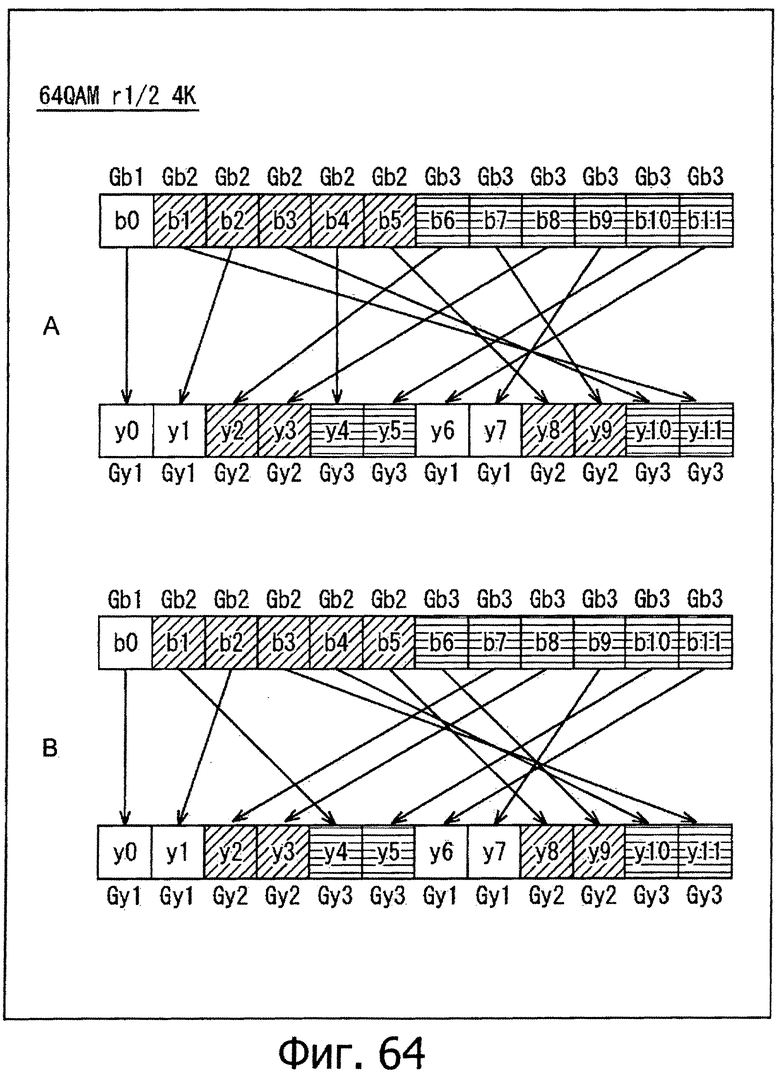

Согласно второму аспекту имеются 8 столбцов, сохраняющих 4×2 бит в направлении строк, (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 кодовых бит, считываемых в направлении строк из устройства хранения, сохраняющего 4320/(4×2) бит в направлении столбцов, задают в качестве бита b#i и (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 символьных бит двух последовательных символов, задают в качестве бита y#i, при этом перестановку осуществляют в соответствии с правилом назначения, согласно которому бит b0 назначают биту y0, бит b1 назначают биту y4, бит b2 назначают биту y1, бит b3 назначают биту y6, бит b4 назначают биту y2, бит b5 назначают биту y5, бит b6 назначают биту y3 и бит b7 назначают биту y7.

Здесь согласно первому и второму аспектам кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 1/2, проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, причем таблица начальных значений проверочной матрицы сформирована следующим образом.

142 150 213 247 507 538 578 828 969 1042 1107 1315 1509 1584 1612 1781 1934 21062117

3 17 20 31 97 466 571 580 842 983 1152 1226 1261 1392 1413 1465 1480 2047 2125 49 169 258 548 582 839 873 881 931 995 1145 1209 1639 1654 1776 1826 1865 1906 1956

148 393 396 486 568 806 909 965 1203 1256 1306 1371 1402 1534 1664 1736 1844 1947 2055

185 191 263 290 384 769 981 1071 1202 1357 1554 1723 1769 1815 1842 1880 1910 1926 1991

424 444 923 1679

91 436 535 978

362 677 821 1695

1117 1392 1454 2030

35 840 1477 2152

1061 1202 1836 1879

242 286 1140 1538

111 240 481 760

59 1268 1899 2144

737 1299 1395 2072

34 288 810 1903

232 1013 1365 1729

410 783 1066 1187

113 885 1423 1560

760 909 1475 2048

68 254 420 1867

283 325 334 970

168 321 479 554

378 836 1913 1928

101 238 964 1393

304 460 1497 1588

151 192 1075 1614

297 313 677 1303

329 447 1348 1832

582 831 984 1900

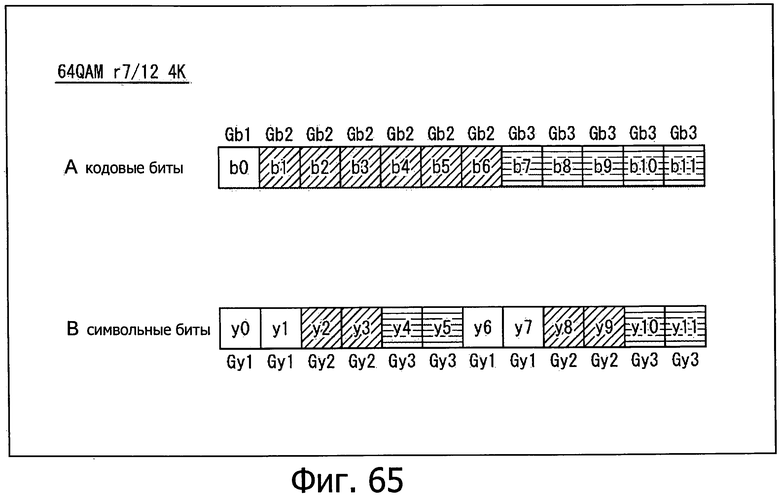

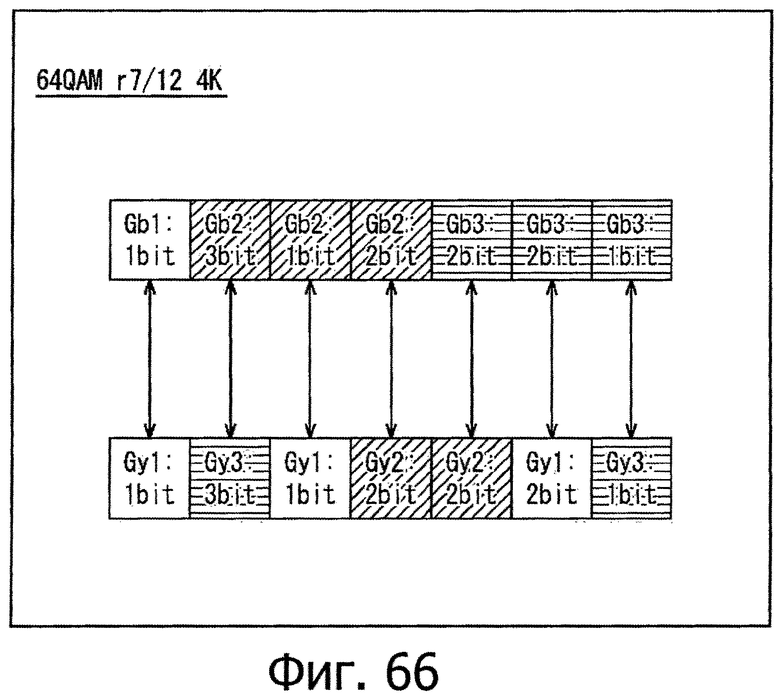

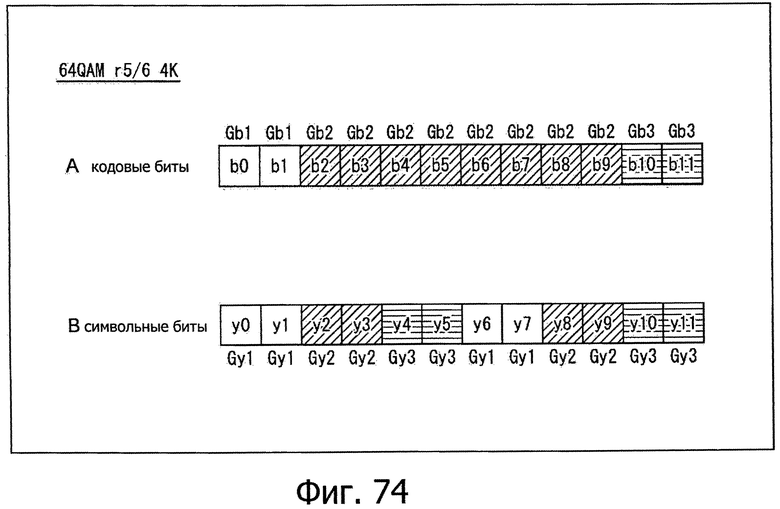

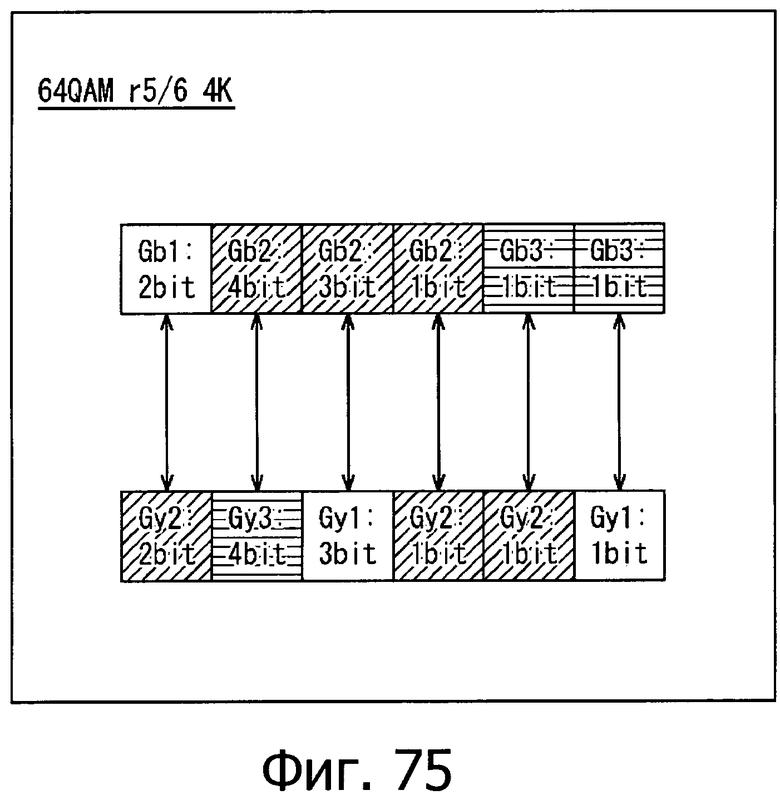

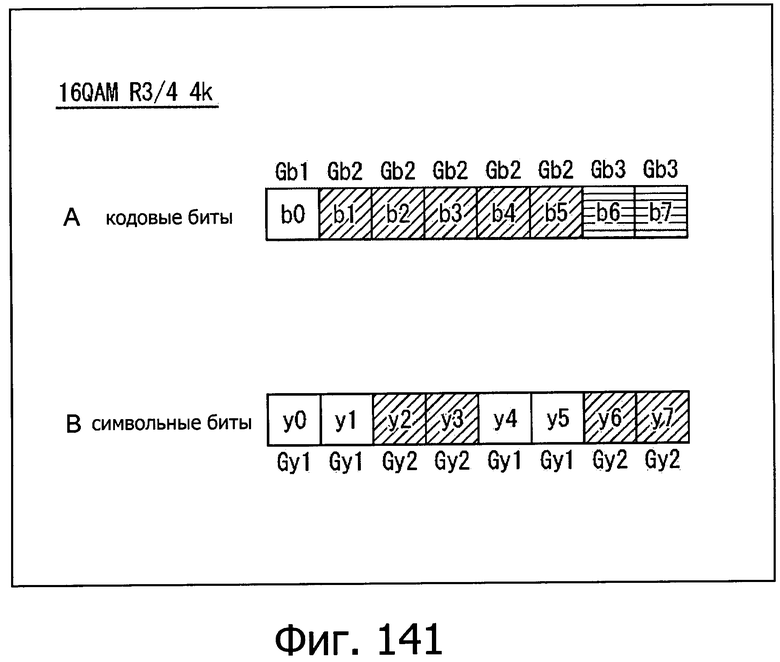

Согласно третьему аспекту кодовые биты в количестве 4×2 бит группируют в четыре группы кодовых бит и символьные биты в количестве 4×2 бит группируют в две группы символьных бит, при этом кодовые биты переставляют в соответствии с правилом назначения, согласно которому происходит назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение двух бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве двух бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является второй после наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей, назначение одного бита из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является третьей после наилучшей, в качестве одного бита в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является наилучшей, и назначение трех бит из совокупности кодовых бит в группе кодовых бит, для которой вероятность ошибки является четвертой после наилучшей, в качестве трех бит в совокупности символьных бит в группе символьных бит, для которой вероятность ошибки является второй после наилучшей.

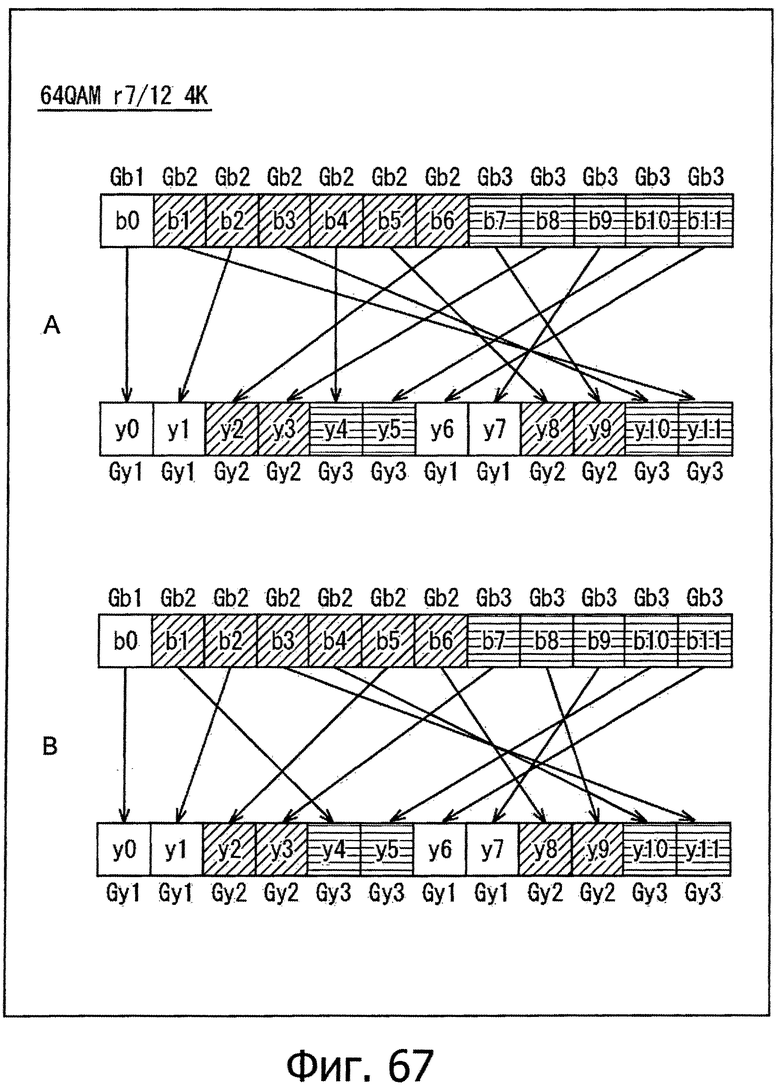

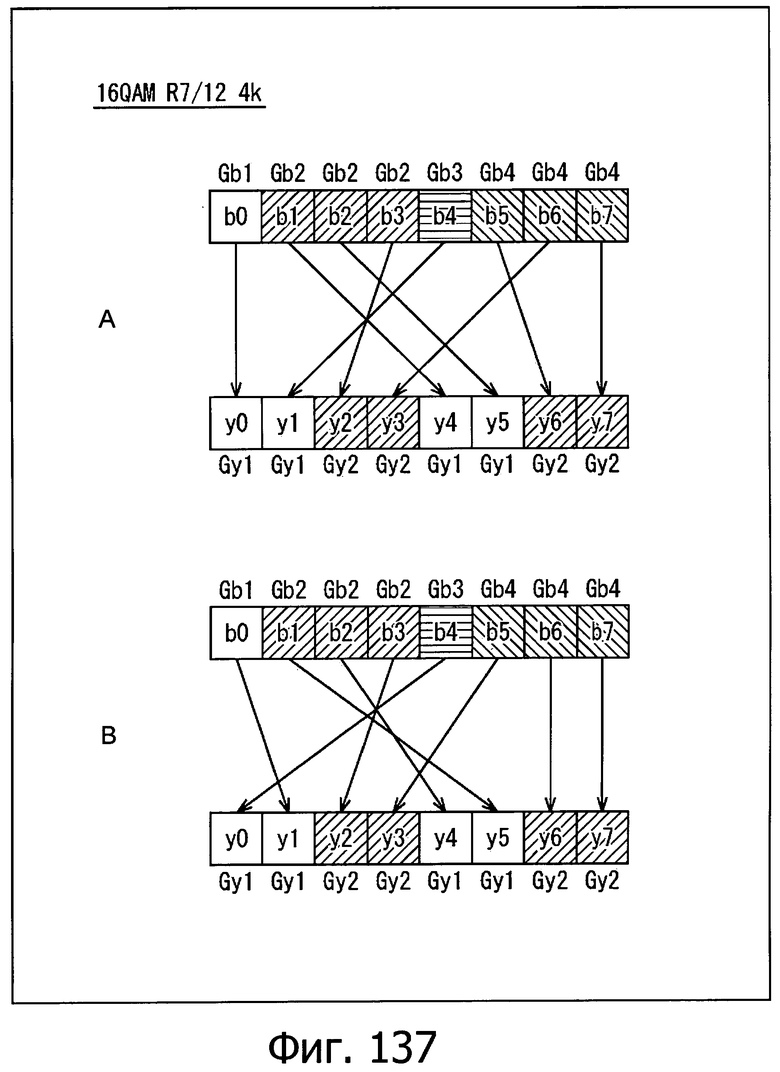

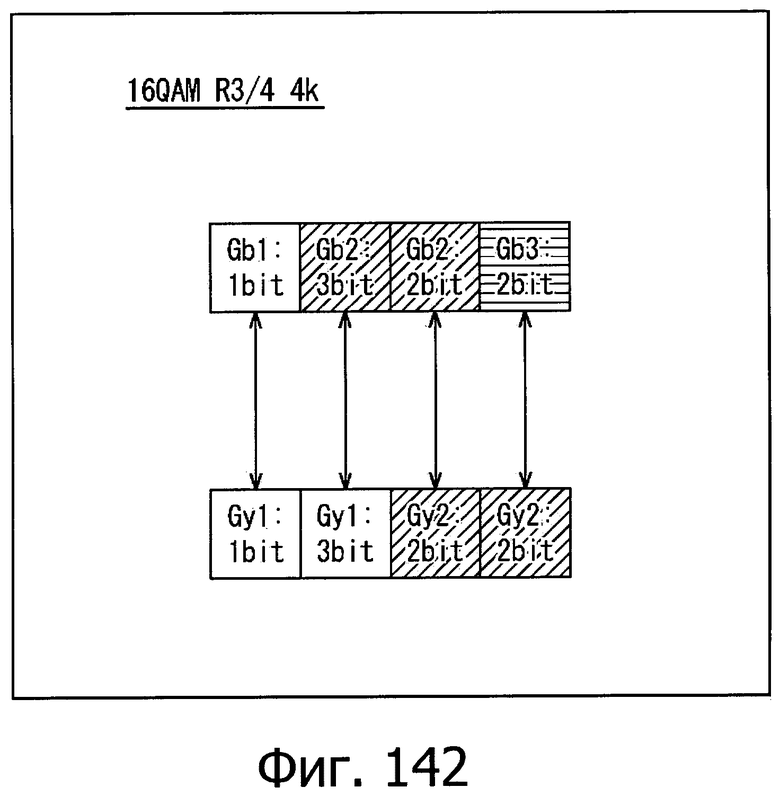

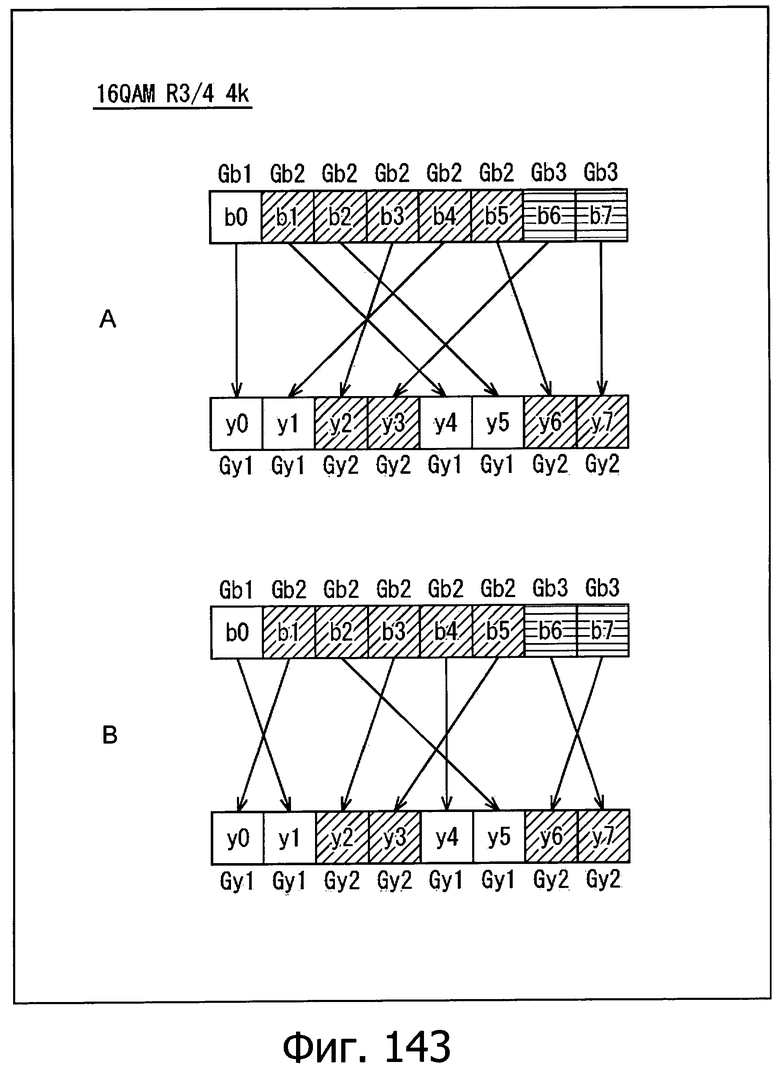

Согласно четвертому аспекту имеются 8 столбцов, сохраняющих 4×2 бит в направлении строк, (#i+1)-й бит, считая от самого старшего бита из совокупности 4×2 кодовых бит, считываемых в направлении строк из устройства хранения, сохраняющего 4320/(4×2) бит в направлении столбцов, задают в качестве бита b#i и (#1+1)-й бит, считая от самого старшего бита из совокупности 4×2 символьных бит двух последовательных символов, задают в качестве бита y#i, при этом перестановку осуществляют в соответствии с правилом назначения, согласно которому бит b0 назначают биту y0, бит b1 назначают биту y4, бит b2 назначают биту y5, бит b3 назначают биту y2, бит b4 назначают биту y1, бит b5 назначают биту y6, бит b6 назначают биту y3 и бит b7 назначают биту y7.

Здесь согласно третьему и четвертому аспектам кодовая скорость кода LDPC, имеющего длину кода, равную 4320 бит, равна 7/12, проверочная матрица четности для кода LDPC конфигурирована путем размещения единичных элементов 1 информационной матрицы, определяемой посредством таблицы начальных значений проверочной матрицы, представляющей позиции единичных элементов 1 информационной матрицы из состава проверочной матрицы, соответствующей длине кода и длине информации согласно кодовой скорости для каждых 72 столбцов в направлении столбцов и с периодом 72 столбца, причем таблица начальных значений проверочной матрицы сформирована следующим образом.

96 246 326 621 668 748 874 965 1022 1108 1117 1142 1300 1469 1481 1627 1702

22 79 122 127 339 359 516 587 1025 1143 1294 1478 1484 1594 1651 1681 1794

80 426 429 506 599 810 892 1016 1117 1246 1277 1281 1316 1384 1713 1729 1753

15 145 182 305 451 563 570 635 781 827 983 1123 1204 1244 1311 1317 1348

11 157 164 292 301 360 636 859 871 895 1138 1164 1206 1268 1454 1613 1783

455 610 1123 1603

631 914 1424 1461

149 507 1275 1468

5 1078 1415 1735

169 772 775 1516

1207 1315 1683 1688

19 1053 1221 1260

933 1095 1597 1628

893 1209 1360 1740

1222 1486 1675 1737

897 1074 1651 1728

115 730 1363 1752

1552 1672 1734 1795

75 1087 1371 1712

123 438 839 1074

4 203 1407 1798

441 476 658 1400

380 1341 1741 1774

974 1487 1664 1756

7 273 834 1658

798 1475 1653 1686

12 1237 1539 1709

211 1494 1618 1624

367 1036 1390 1587

18 166 1645 1679

530 1092 1571 1707

588 1593 1689 1707

980 1104 1522 1701

1025 1510 1552 1683

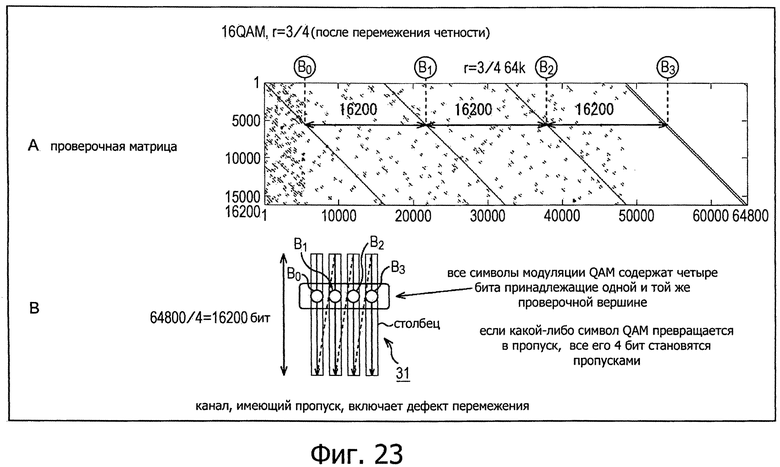

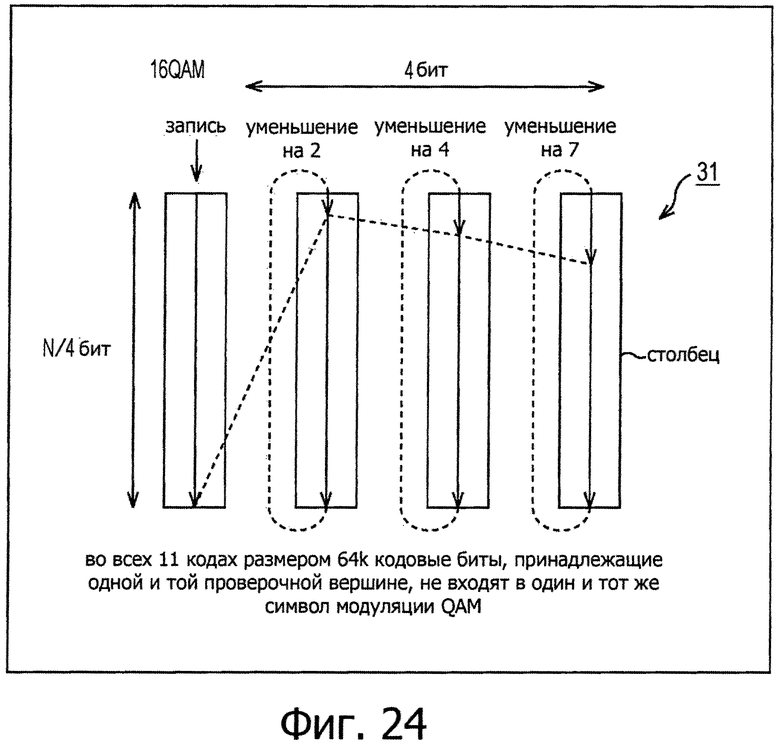

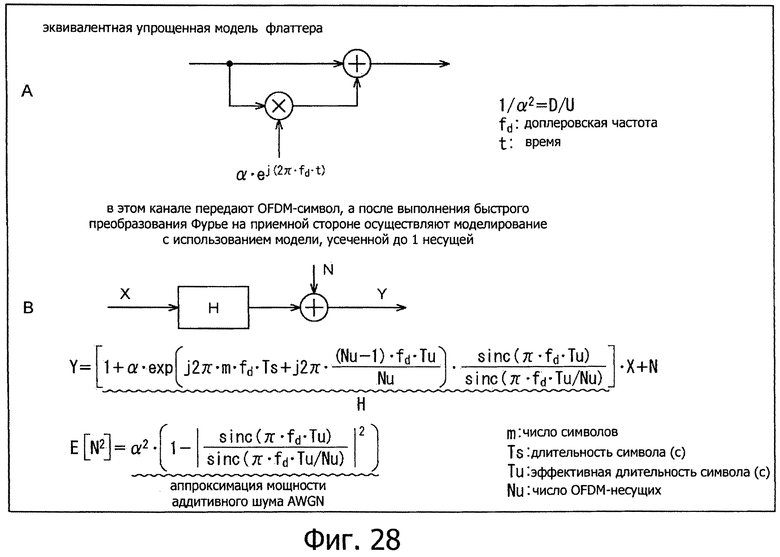

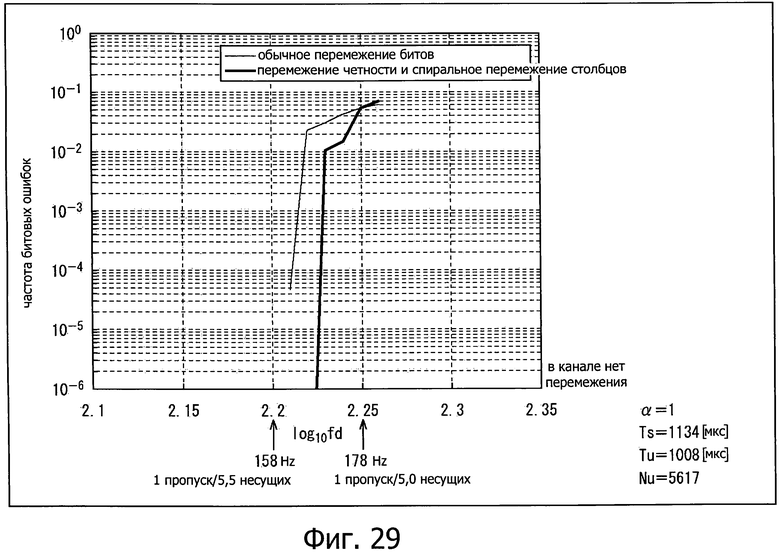

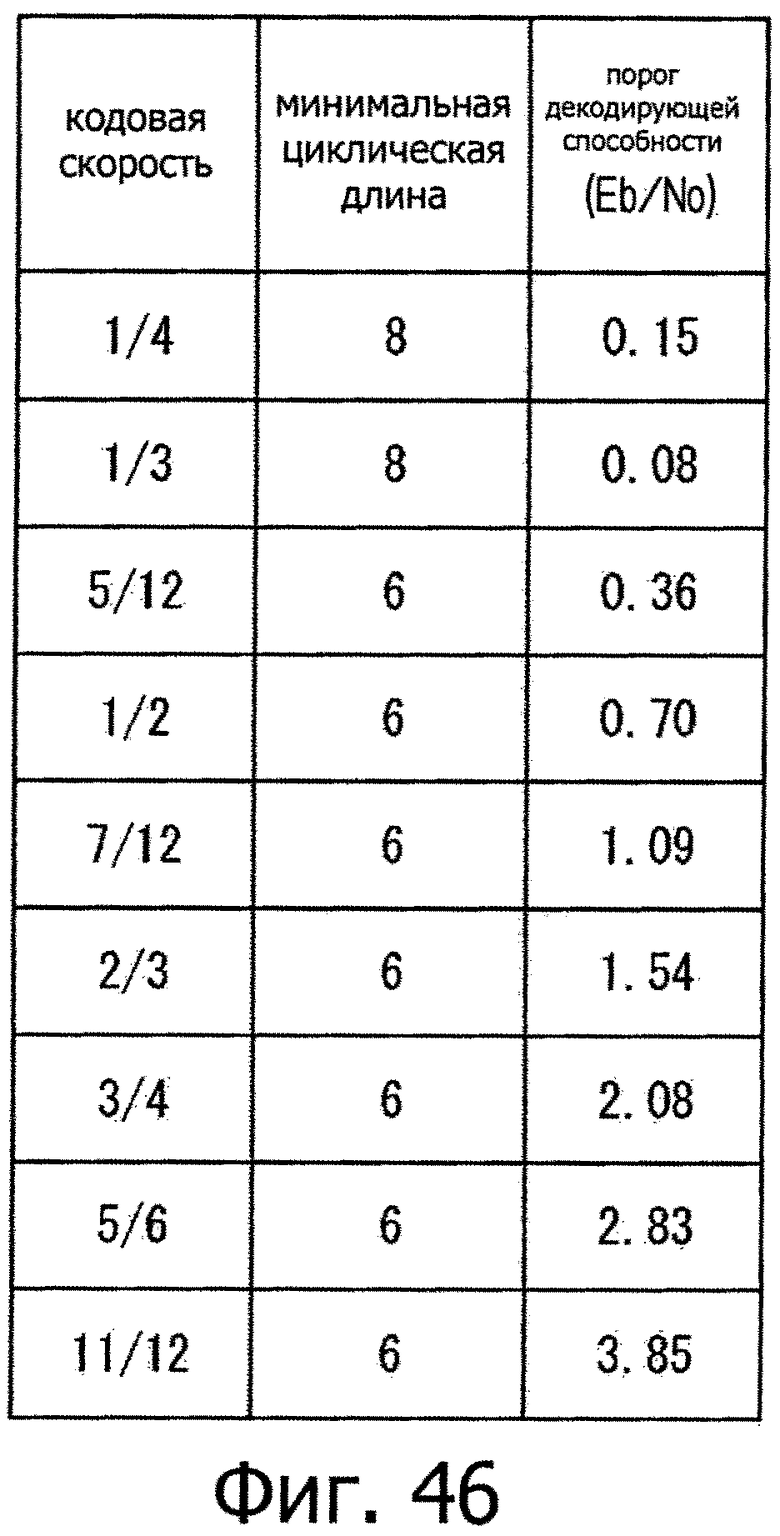

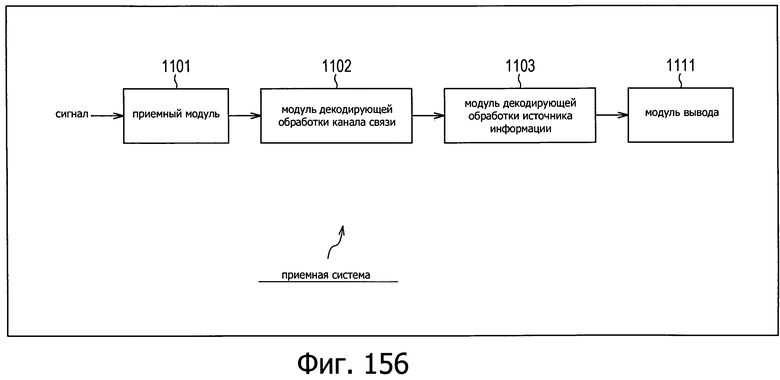

270 340 1326 1770