Изобретение относится к схеме для генерации отрицательных напряжений с первым транзистором, первый вывод которого соединен с входным выводом схемы и второй вывод которого соединен с выходным выводом схемы и вывод затвора которого соединен через первый конденсатор с первым выводом тактового сигнала, со вторым транзистором, первый вывод которого соединен с выводом затвора первого транзистора, второй вывод которого соединен со вторым выводом первого транзистора и вывод затвора которого соединен с первым выводом первого транзистора и со вторым конденсатором, первый вывод которого соединен со вторым выводом первого транзистора, а второй вывод которого соединен со вторым выводом тактового сигнала, причем транзисторы являются МОП-транзисторами, выполненными, по меньшей мере, в одном тройном кармане (Triple Well).

Такая схема известна из патента DE 196 01 369 C1. Там транзисторы реализованы в виде n-канальных транзисторов в р-кармане. Р-карман со своей стороны выполнен в глубоком, изолирующем n-кармане, который расположен в р-подложке.

В принципе схема может быть реализована таким образом также с р-канальными МОП-транзисторами в n-подложке.

Глубокий n-карман соединен, так же как и р-подложка, с потенциалом корпуса. Если теперь к n-карману прикладывают более отрицательное напряжение смещения, чем самое отрицательное напряжение или на выводе стока, или на выводе истока первого транзистора, в установившемся состоянии схемы через паразитные биполярные транзисторы карман-подложка не может течь никакой ток утечки. Так, например, nрn-транзистор образуется n+-областью стока n-МОП-транзистора, которая служит в качестве эмиттера, р-карманом, который образует базу, и n-карманом, который образует коллектор. Если потенциал кармана является более положительным, чем область стока n-МОП-транзистора, паразитный nрn-транзистор будет проводить и оказывать отрицательное воздействие на эффективность генератора накачки заряда.

Принцип известной, работающей в качестве генератора накачки заряда схемы основывается на том, что заряды от конденсатора, который соединен с выводом стока первого транзистора, "накачивают" к конденсатору, который соединен с его выводом истока, за счет того, что попеременно прикладывают напряжение к соответственно следующим конденсаторным выводам. Если друг за другом включают N таких схем, вход первой схемы и следующий вывод соединенного с выходом конденсатора соединены с выводом корпуса, то теоретически может быть достигнуто выходное напряжение |(N-1)U0|, причем U0 является напряжением на выводах тактового сигнала.

Процесс заряда является динамическим процессом, при котором напряжения на выводах истока и стока первого транзистора схемы постоянно изменяются, так что регулярно включается паразитный биполярный транзистор.

Для решения этой проблемы DE 196 01 369 C1 предлагает соединять карманы, в которых расположены транзисторы, с соответствующими выводами истока транзисторов, так как там в установившемся состоянии приложено соответственно самое отрицательное напряжение. Это предположение, однако, справедливо в действительности только для статического конечного состояния схемы генератора накачки заряда, которое на практике никогда не наступает, так как от генератора накачки заряда постоянно отбирается заряд за счет нагрузки.

Уже при включении в случае известной схемы карман будет находиться при соответствующем напряжению тактового сигнала более высоком потенциале, чем вывод стока, и тем самым включаться биполярный транзистор, что приводит к сильной потере эффективности, так как за счет этого генератор накачки заряда, с одной стороны, не достигает теоретически максимально возможного выходного напряжения и, с другой стороны, принимает подлежащее достижению выходное напряжение значительно медленнее.

Задачей изобретения поэтому является указание схемы для генерации отрицательных напряжений с более высокой эффективностью.

Эта задача решается схемой согласно пункта 1 формулы изобретения. Предпочтительные формы выполнения указаны в зависимых пунктах формулы изобретения.

В случае соответствующей изобретению схемы или, соответственно, генератора накачки заряда, образованного из нескольких таких схем, предусмотрен третий транзистор, который соединяет карман с выводом истока первого (зарядного) транзистора только тогда, когда потенциал на выводе истока является более отрицательным, чем потенциал на выводе стока первого транзистора. В этом случае карманный конденсатор, который получается за счет рn-запирающего слоя между обоими карманами, заряжается до потенциала истока и поддерживает карман достаточно долго на этом потенциале, также если третий транзистор снова запирается, поскольку потенциал вывода стока первого транзистора становится более отрицательным, чем его потенциал вывода истока.

В дальнейшей форме выполнения изобретения предусмотрен четвертый транзистор, который соединяет карман с выводом стока первого транзистора, если потенциал вывода стока является более отрицательным, чем потенциал вывода истока первого транзистора. В этой форме выполнения карманный конденсатор таким образом всегда заряжается до более отрицательного потенциала так, что статические состояния, в которых карман является более положительным, чем один из выводов первого транзистора, не могут наступать, и таким образом паразитный биполярный транзистор становится проводящим.

Дальнейшая предпочтительная форма выполнения изобретения предусматривает расположение конденсатора между выводом стока первого транзистора и карманом. Этот конденсатор заряжается во время фазы включения третьего конденсатора, так же как и карманный конденсатор, до потенциала вывода истока и включается в фазе запирания третьего транзистора последовательно с карманным конденсатором так, что при понижении потенциала вывода стока напряжение на карманном конденсаторе сдвигается к отрицательным значениям. Карман поэтому является более отрицательным, чем это было бы возможно за счет чистого заряда через вывод истока первого транзистора.

За счет включения друг за другом нескольких соответствующих изобретению схем можно получить генератор накачки заряда, которым можно генерировать напряжения - 12 В или даже - 20 В, как это требуется для программирования и/или стирания энергонезависимых запоминающих устройств, в частности, быстрых СППЗУ (программируемых стираемых ПЗУ) при напряжениях питания микросхем только 2,5 В.

В таком генераторе накачки заряда на нечетные схемы подают первый и второй тактовые сигналы, а на четные схемы подают третий и четвертый тактовые сигналы, которые имеют одинаковые характеристики, что и первый и второй тактовые сигналы, однако, смещены на половину периода. В предпочтительной форме дальнейшего развития тактовые сигналы на втором выводе тактового сигнала схем имеют скважность импульсов больше, чем 0,5, так что вторые и четвертые тактовые сигналы накладываются друг на друга. За счет этого первые транзисторы предварительно заряжаются, что приводит к повышению эффективности.

Изобретение поясняется в последующем более подробно на примерах выполнения с помощью чертежей, на которых показано:

фиг. 1 детальная блок-схема соответствующей изобретению схемы;

фиг. 2 - принципиальное представление реализации такой схемы в р-подложке в технике тройного кармана (Triple Well);

фиг. 3 - первая форма выполнения генератора накачки заряда;

фиг. 4 - вторая форма выполнения генератора накачки заряда;

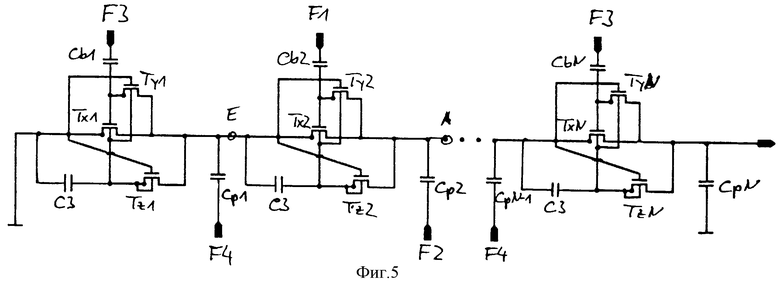

фиг. 5 - третья форма выполнения генератора накачки заряда;

фиг. 6 - временная характеристика тактовых сигналов.

Согласно фиг. 1 в соответствующей изобретению схеме, которую можно рассматривать как каскад многокаскадного генератора накачки заряда для генерации отрицательного напряжения, между входным выводом Е и выходным выводом А включен первый n-МОП транзистор Тх2.

Как представлено на фиг. 2, первый транзистор Тх2 выполнен в р-кармане, который расположен, со своей стороны, в глубоком, изолирующем n-кармане. Этот глубокий n-карман выполнен в р-подложке. Как n-карман, так и р-подложка подключены к корпусу.

Вывод затвора первого транзистора Тх2 через первый конденсатор Сb2 соединен с первым выводом тактового сигнала, к которому может прикладываться первый тактовый сигнал F1. Вывод истока первого транзистора Тх2 соединен с первым выводом второго конденсатора Ср2, второй вывод которого связан со вторым выводом тактового сигнала, к которому может прикладываться второй тактовый сигнал F2.

Входной вывод Е схемы может быть соединен с выходным выводом следующей подобной схемы, как это подробно представлено на фиг. 3 и намечено на фиг. 1 путем второго конденсатора Ср1 этой последующей схемы.

Как представлено на фиг. 6, второй и четвертый тактовые сигналы F2, F4 имеют такую же временную характеристику, однако смещены относительно друг друга на половину длительности периода. За счет этой попеременной подачи положительного напряжения на второй и четвертый выводы тактового сигнала заряды от второго конденсатора Ср1 следующей или, соответственно, предыдущей схемы цепочки схем согласно фиг. 3 "накачиваются" ко второму конденсатору Ср2 следующей, представленной на фиг. 1 схемы через первый транзистор Тх2. Его вывод затвора во время фазы накачки за счет первого тактового сигнала F1, временная характеристика которого также представлена на фиг. 6, подтягивается до положительного относительно вывода истока первого транзистора Тх2 потенциала, так что он проводит. Предпочтительным образом тактовые сигналы F2 и F4 несколько перекрываются, так что первый транзистор предварительно заряжается до тех пор, пока он не включается первым тактовым сигналом F1 в проводящее состояние.

За счет накачки зарядов ко второму конденсатору Ср2 он заряжается и после отключения второго тактового сигнала F2 выходной вывод А или, соответственно, связанный с ним вывод истока первого транзистора Тх2 становится отрицательным. Таким образом вывод истока стал бы более отрицательным, чем вывод затвора первого транзистора Тх2, за счет чего он бы не заперся и второй конденсатор Ср2 мог бы снова разряжаться. Поэтому между выводом затвора и выводом истока первого транзистора Тх2 включен второй транзистор Ту2, вывод затвора которого связан с выводом стока первого транзистора Тх2. За счет этого второго транзистора Ту2 также вывод затвора первого транзистора Тх2 приводится к потенциалу вывода истока первого транзистора Тх2 так, что он запирается.

Чтобы воспрепятствовать разряду второго конденсатора Ср2 через второй транзистор Ту2 и первый вывод тактового сигнала, предусмотрен первый конденсатор Сb2.

Согласно изобретения между выводом истока первого транзистора Тх2 и выводом кармана Kw, в котором выполнен транзистор Тх2, включен третий n-МОП-транзистор Tz2, вывод затвора которого также связан с выводом стока первого транзистора Тх2.

Как можно понять из фиг. 2, второй и третий транзисторы Ту2, Tz2 также расположены в р-кармане, в котором выполнен первый транзистор Тх2. Как намечено штриховыми линиями, они могут быть выполнены также в собственных карманах, причем карманы предпочтительным образом соединены друг с другом проводниками.

За счет третьего транзистора Tz2 карман, который представлен на фиг. 1 узлом Kw, удерживается на отрицательном потенциале так, что рn-переход между р-карманом и n-карманом включен в направлении запирания и не может течь никакой ток утечки. За счет третьего транзистора Tz2 кроме того заряжается конденсатор карман-карман-запорный слой Cw так, что р-карман также при запирании третьего транзистора Tz2 удерживается на отрицательном потенциале.

На фиг. 2 кроме того представлен паразитный nрn-транзистор Тр, который образован n+-областью стока первого транзистора Тх2, р-карманом, а также n-карманом. Этот паразитный транзистор Тр показан также на фиг. 1. Можно явно понять, что этот транзистор Тр стал бы проводящим и привел бы к токам утечки, если бы р-карман стал бы более положительным, чем вывод стока первого транзистора Тх2. Это однако эффективно предотвращается за счет соответствующего изобретению третьего транзистора.

Как уже сказано, можно включать друг за другом несколько таких соответствующих изобретению схем, чтобы генерировать не только отрицательное напряжение, но и по сравнению с напряжением питания высокое отрицательное напряжение, какое, например, требуется для программирования и стирания быстрых СППЗУ.

На фиг. 3 друг за другом включено количество N таких схем согласно фиг. 1. Первые транзисторы обозначены Txl-TxN. Другие части схемы снабжены цифрами эквивалентным образом. На второй конденсатор CpN n-й схемы не подано напряжение тактового сигнала, так как на нем должно сниматься высокое отрицательное напряжение. Таким генератором накачки заряда, как он представлен на фиг. 3, который состоит из N-каскадов накачки, можно получить напряжение (N-l)•U0, если вход первого каскада накачки соединен с корпусом и U0 является уровнем тактовых сигналов. Тактовые сигналы F1...F4 имеют временные характеристики, которые представлены на фиг. 6. Тактовые сигналы F3 и F4 имеют такую же временную характеристику, что и тактовые сигналы F1 и F2, однако сдвинуты на половину длительности периода.

На нечетные каскады накачки генератора накачки заряда согласно фиг. 3 подаются тактовый сигнал F3 и F4, а на четные - тактовые сигналы F1 и F2.

Фиг. 4 показывает следующую форму выполнения изобретения. В случае схем представленного там генератора накачки заряда четвертые n-МОП-транзисторы Tzal...TzaN расположены между выводами стока первых транзисторов Тх1...TxN и карманами. Выводы затвора четвертых транзисторов Tzal...TzaN связаны соответственно с выводами истока первых транзисторов Zxl...TxN. Третьи транзисторы обозначены здесь Tzbl...TzbN.

Четвертые транзисторы Tzal...TzaN служат для того, чтобы также в случае, когда на выводах стока первых транзисторов Txl...TxN приложен более низкий потенциал, чем на их выводах истока, этот самый низкий потенциал переключался к карманам и карманы тем самым всегда находились на самом низком из обоих потенциалов.

Вместо четвертых транзисторов Tzal. . . TzaN в предпочтительной форме дальнейшего развития схемы согласно фиг. 1 или, соответственно, генератора накачки заряда согласно фиг. 3 может быть включен третий конденсатор С3 между выводами стока первых транзисторов Txl. ..TxN и карманами Kw. Это представлено на фиг. 5. Третьи конденсаторы С3 в соединении с конденсаторами карман-карман Cw (которые на фиг. 5 в явном виде не представлены) приводят к дальнейшему падению потенциала кармана.

Представленные на фиг. 3-5 соответствующие изобретению генераторы накачки заряда отличаются более высокой эффективностью так, что также при малом напряжении питания порядка 2,5 В могут достигаться выходные напряжения -20 В.

Схема для генерации отрицательных напряжений с первым транзистором (Тх2), первый вывод которого соединен с входным выводом (Е), а второй вывод которого соединен с выходным выводом (А) схемы и вывод затвора которого через первый конденсатор (Сb2) соединен с первым выводом тактового сигнала, со вторым транзистором (Ту2), первый вывод которого соединен с выводом затвора Тх2, второй вывод которого соединен со вторым выводом Тх2 и вывод затвора которого соединен с первым выводом Тх2 и со вторым конденсатором Ср2, первый вывод которого соединен со вторым выводом Тх2 и второй вывод которого соединен со вторым выводом тактового сигнала, и причем Тх2, Ту2 являются МОП-транзисторами, выполненными в технике тройного кармана. Первый вывод третьего транзистора (Tz2) соединен со вторым выводом Тх2, второй вывод Tz2 соединен с карманом/карманами (Kw), содержащими транзисторы Тх2, Ту2, Tz2, и вывод затвора Tz2 соединен с первым выводом Тх2. Технический результат: повышение эффективности за счет уменьшения токов утечки. 3 с. и 3 з.п. ф-лы, 6 ил.

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1992 |

|

RU2009602C1 |

| Модификатор | 1976 |

|

SU616329A1 |

| ПЕРЕДАЮЩЕЕ УСТРОЙСТВО ПОЗИЦИОННО-КОДОВОЙМОДУЛЯЦИИ | 0 |

|

SU319063A1 |

| US 5422586 А, 06.06.1995. | |||

Авторы

Даты

2002-09-20—Публикация

1997-09-23—Подача