Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах, функционирующих в модулярной системе счисления.

Известно устройство (аналог) (авт.св. СССР № 1571583, МКИ G06F 7/72, БИ № 22, 1990 г.), содержащее дешифраторы, группы элементов И, элементы ИЛИ, сумматор по модулю 2, элементы И, элементы НЕ, группы элементов ИЛИ, коммутатор, шифраторы. Недостаток устройства - невозможность выполнения модульной операции умножения.

Известно также устройство (аналог) (авт.св. СССР № 1689949, МКИ G06F 7/72, БИ № 41, 1991 г.), содержащее дешифраторы, элементы И и НЕ, элемент ИЛИ-НЕ, группы элементов ИЛИ, коммутатор, группы элементов И, шифратор. Недостаток устройства - невозможность выполнения модульной операции умножения.

Наиболее близким по технической сущности (прототипом к предлагаемому изобретению) является устройство (патент РФ № 2188448, МКИ G06F 7/72, БИ № 24, 2002 г.), содержащее дешифраторы, шифратор, управляемые фазовращатели, генератор гармонического сигнала, фазовращатели на фиксированное значение фазы и измеритель фазы гармонического сигнала.

Недостаток прототипа - низкие функциональные возможности, заключающиеся в том, что устройство реализует выполнение исключительно аддитивной модульной операции. Это определяется алгоритмом функционирования и структурой составляющих его узлов.

Задача, на решение которой направлено заявляемое устройство, состоит в реализации проведения мультипликативных модульных операций.

Технический результат выражается в возможности выполнения модульной операции умножения и нахождения остатка по модулю от числа.

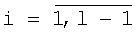

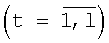

Технический результат достигается тем, что в устройство, содержащее l дешифраторов (l=]log2[, где р - модуль устройства), l управляемых фазовращателей, генератор гармонического сигнала, измеритель фазы гармонического сигнала, (р-1) фазовращателей на фиксированные значения фазы и шифратор, причем выход генератора гармонического сигнала соединен с первым входом первого управляемого фазовращателя, выход i-го управляемого фазовращателя - с первым входом (i+1)-го управляемого  фазовращателя, выход l-го управляемого фазовращателя - с первым входом измерителя фазы гармонического сигнала, второй вход которого соединен с выходом генератора гармонического сигнала, вход

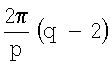

фазовращателя, выход l-го управляемого фазовращателя - с первым входом измерителя фазы гармонического сигнала, второй вход которого соединен с выходом генератора гармонического сигнала, вход  измерителя фазы гармонического сигнала соединен с выходом генератора гармонического сигнала через фазовращатель на фиксированное значение фазы, равное

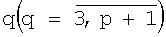

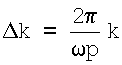

измерителя фазы гармонического сигнала соединен с выходом генератора гармонического сигнала через фазовращатель на фиксированное значение фазы, равное  , при этом вход (p+2) измерителя фазы гармонического сигнала является тактовым входом устройства, выход измерителя фазы гармонического сигнала соединен со входом шифратора, выход которого является выходом устройства, а выходы дешифраторов подключены ко вторым входам соответствующих управляемых фазовращателей, введены (l-1) блоков умножения на константу по модулю и l блоков элементов И, причем вход первого сомножителя устройства соединен со входами блоков умножения на константу по модулю и вторым входом l-го блока элементов И, входы разрядов второго сомножителя соединены с первыми входами соответствующих блоков элементов И, выходы которых подключены к входам соответствующих дешифраторов, а выходы блоков умножения на константу по модулю соединены со вторыми входами соответствующих блоков элементов И.

, при этом вход (p+2) измерителя фазы гармонического сигнала является тактовым входом устройства, выход измерителя фазы гармонического сигнала соединен со входом шифратора, выход которого является выходом устройства, а выходы дешифраторов подключены ко вторым входам соответствующих управляемых фазовращателей, введены (l-1) блоков умножения на константу по модулю и l блоков элементов И, причем вход первого сомножителя устройства соединен со входами блоков умножения на константу по модулю и вторым входом l-го блока элементов И, входы разрядов второго сомножителя соединены с первыми входами соответствующих блоков элементов И, выходы которых подключены к входам соответствующих дешифраторов, а выходы блоков умножения на константу по модулю соединены со вторыми входами соответствующих блоков элементов И.

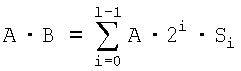

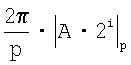

Сущность изобретения состоит в следующем: пусть А - первый операнд, В - второй и необходимо провести операцию модульного умножения |А·В|p, где р - модуль. Представим число В в виде B=Sl-1·2l-1+Sl-2·2l-2+...+S0·20(l=]log2p[). Тогда  (Si=0 либо 1, т.е. соответствует значению соответствующего разряда в двоичном представлении числа В). Произведение вида |А·2i|p можно получить при помощи блока умножения на константу по модулю (авт.св. СССР № 1617439, МКИ G06F 7/72, 1990 г.). Следовательно, для получения результата операции |А·В|p необходимо произвести последовательное сложение чисел вида |А·2i|p для тех разрядов двоичного представления числа В, Si которых равны 1. Немодульная операция - нахождение остатка по модулю от числа возможна, если операнд А равен единице, тогда на выходе устройства имеем результат операции |В|p при 2>р. Дополнительной возможностью заявляемого устройства является то, что при соответствующей коммутации его можно использовать для сложения ]log2p[ чисел по модулю.

(Si=0 либо 1, т.е. соответствует значению соответствующего разряда в двоичном представлении числа В). Произведение вида |А·2i|p можно получить при помощи блока умножения на константу по модулю (авт.св. СССР № 1617439, МКИ G06F 7/72, 1990 г.). Следовательно, для получения результата операции |А·В|p необходимо произвести последовательное сложение чисел вида |А·2i|p для тех разрядов двоичного представления числа В, Si которых равны 1. Немодульная операция - нахождение остатка по модулю от числа возможна, если операнд А равен единице, тогда на выходе устройства имеем результат операции |В|p при 2>р. Дополнительной возможностью заявляемого устройства является то, что при соответствующей коммутации его можно использовать для сложения ]log2p[ чисел по модулю.

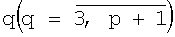

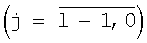

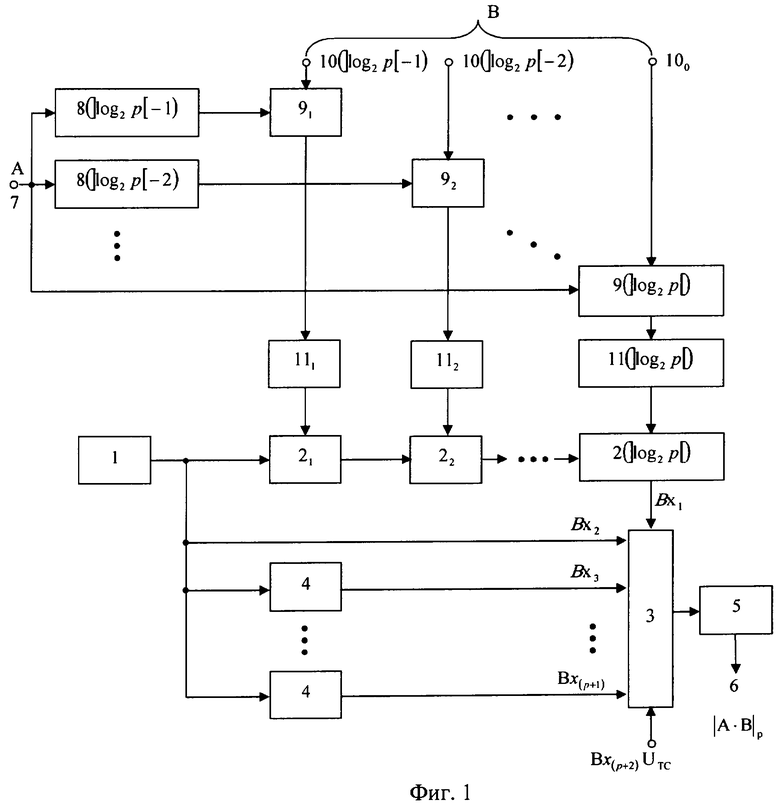

На фиг.1 представлена структурная схема предлагаемого устройства, где: 1 - генератор гармонического сигнала, 21÷2l (l=]log2p[) - управляемые фазовращатели, 3 - измеритель фазы гармонического сигнала, 4 - группа фазовращателей на фиксированное значение фазы  , 5 - шифратор, 6 - выход устройства, 7 - вход первого сомножителя, 81÷8(l-1) - блоки умножения на константу по модулю, 91÷9l - блоки элементов И, 101÷10(l-1) - входы разрядов второго сомножителя, 111÷11l - дешифраторы. Выход генератора гармонического сигнала 1 соединен с первым входом первого управляемого фазовращателя 21, выход управляемого фазовращателя 2i - с первым входом управляемого фазовращателя 2(i+1) (

, 5 - шифратор, 6 - выход устройства, 7 - вход первого сомножителя, 81÷8(l-1) - блоки умножения на константу по модулю, 91÷9l - блоки элементов И, 101÷10(l-1) - входы разрядов второго сомножителя, 111÷11l - дешифраторы. Выход генератора гармонического сигнала 1 соединен с первым входом первого управляемого фазовращателя 21, выход управляемого фазовращателя 2i - с первым входом управляемого фазовращателя 2(i+1) ( ; где l=]log2p[, а р - модуль устройства), выход управляемого фазовращателя 2l - с первым входом измерителя фазы гармонического сигнала 3, второй вход которого соединен с выходом генератора 1 гармонического сигнала, вход

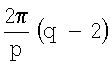

; где l=]log2p[, а р - модуль устройства), выход управляемого фазовращателя 2l - с первым входом измерителя фазы гармонического сигнала 3, второй вход которого соединен с выходом генератора 1 гармонического сигнала, вход  измерителя фазы гармонического сигнала 3 соединен с выходом генератора 1 гармонического сигнала через фазовращатель 4(q-2) на фиксированное значение фазы, равное

измерителя фазы гармонического сигнала 3 соединен с выходом генератора 1 гармонического сигнала через фазовращатель 4(q-2) на фиксированное значение фазы, равное  , при этом вход (р+2) измерителя фазы гармонического сигнала 3 является тактовым входом устройства, выход измерителя фазы гармонического сигнала 3 соединен со входом шифратора 5, выход которого является выходом 6 устройства, вход первого сомножителя 7 устройства соединен со входами блоков умножения 8i, на константу по модулю и вторым входом l-го блока 9l, элементов И, входы разрядов 10j

, при этом вход (р+2) измерителя фазы гармонического сигнала 3 является тактовым входом устройства, выход измерителя фазы гармонического сигнала 3 соединен со входом шифратора 5, выход которого является выходом 6 устройства, вход первого сомножителя 7 устройства соединен со входами блоков умножения 8i, на константу по модулю и вторым входом l-го блока 9l, элементов И, входы разрядов 10j второго сомножителя соединены с первыми входами блоков 9m

второго сомножителя соединены с первыми входами блоков 9m элементов И соответственно, выходы которых подключены к входам соответствующих дешифраторов 11m, выходы блоков умножения на константу по модулю 8i соединены со вторыми входами соответствующих блоков 9i элементов И, вторые входы управляемых фазовращателей 2m, соединены с выходами соответствующих дешифраторов 11m.

элементов И соответственно, выходы которых подключены к входам соответствующих дешифраторов 11m, выходы блоков умножения на константу по модулю 8i соединены со вторыми входами соответствующих блоков 9i элементов И, вторые входы управляемых фазовращателей 2m, соединены с выходами соответствующих дешифраторов 11m.

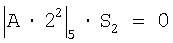

На фиг.2 представлена структурная схема измерителя фазы гармонического сигнала 3, где Bx1÷Вх(p+2) - входы измерителя фазы, 121÷12p - аналоговые перемножители, 131÷13p - интеграторы, 14 - решающее устройство.

На фиг.3 представлена структурная схема управляемого фазовращателя 2t , где Вх1 и Вх2 - входы управляемого фазовращателя, 151÷15p - коммутаторы гармонического сигнала, 16k

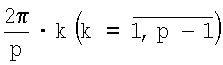

, где Вх1 и Вх2 - входы управляемого фазовращателя, 151÷15p - коммутаторы гармонического сигнала, 16k - линии задержки на

- линии задержки на  (ω - несущая частота гармонического сигнала).

(ω - несущая частота гармонического сигнала).

Рассмотрим работу устройства. Первый сомножитель А поступает на входы блоков 8i умножения на константу по модулю, а также на второй вход блока 9l элементов И. На выходах блоков 8i умножения на константу по модулю получаем произведения вида  , а на втором входе блока 9l элементов И имеем

, а на втором входе блока 9l элементов И имеем  . Данные числа будут представлены в двоичном коде. На входы разрядов 10j второго сомножителя поступает второй операнд В. С выходов блоков 9l элементов И на входы дешифраторов 11m поступают числа в двоичном коде вида

. Данные числа будут представлены в двоичном коде. На входы разрядов 10j второго сомножителя поступает второй операнд В. С выходов блоков 9l элементов И на входы дешифраторов 11m поступают числа в двоичном коде вида  для тех разрядов операнда В, которые не равны нулю. В противном случае на вход соответствующего дешифратора 11 поступит двоичный позиционный код числа ноль.

для тех разрядов операнда В, которые не равны нулю. В противном случае на вход соответствующего дешифратора 11 поступит двоичный позиционный код числа ноль.

После их преобразования в дешифраторах 11m, в унитарные коды числа поступают на Вх2 соответствующих управляемых фазовращателей 21÷2l. В соответствии со значениями унитарных кодов чисел  в управляемых фазовращателях 21÷2l путем подключения коммутаторами 151÷15p соответствующих линий задержки 161÷16p-1 устанавливаются набеги фазы, равные

в управляемых фазовращателях 21÷2l путем подключения коммутаторами 151÷15p соответствующих линий задержки 161÷16p-1 устанавливаются набеги фазы, равные  . После прохождения гармонического сигнала с выхода генератора 1 гармонического сигнала через l фазовращателей 2i суммарный набег фазы этого сигнала будет равен

. После прохождения гармонического сигнала с выхода генератора 1 гармонического сигнала через l фазовращателей 2i суммарный набег фазы этого сигнала будет равен  .

.

Пример. Пусть p=5, А=4, В=3.

Двоичный код числа В равен 0112. Первый сомножитель поступает на вход блока 82 умножения на константу по модулю, на выходе которого получим число  , на выходе блока 81 умножения на константу по модулю будет число

, на выходе блока 81 умножения на константу по модулю будет число  , а на втором входе блока 93 элементов И -

, а на втором входе блока 93 элементов И -  . На входах разрядов 102, 101 и 100 при B=3 будут соответствующие значения S2=0, S1=1 и S0=1. Следовательно после преобразования двоичных позиционных кодов

. На входах разрядов 102, 101 и 100 при B=3 будут соответствующие значения S2=0, S1=1 и S0=1. Следовательно после преобразования двоичных позиционных кодов  ,

,  и

и  в дешифраторах 111÷113 устройства в унитарные коды в управляемых фазовращателях 21÷23 коммутаторами 151÷155 подключаются соответствующие линии задержки 161÷163 на время, равное

в дешифраторах 111÷113 устройства в унитарные коды в управляемых фазовращателях 21÷23 коммутаторами 151÷155 подключаются соответствующие линии задержки 161÷163 на время, равное  ,

,  и

и  .

.

После прохождения гармонического сигнала через управляемые фазовращатели 21÷23 фаза этого сигнала на выходе управляемого фазовращателя 23 будет равна  , а исходя из периодичности гармонической функции

, а исходя из периодичности гармонической функции  . Таким образом, суммарная фаза гармонического сигнала прямо пропорциональна числу 2. Напряжение на выходе интегратора 13 в канале измерителя фазы будет максимальным для второго номера канала. Следовательно, на выход 6 устройства после шифратора 5 поступит число 2 в двоичном коде.

. Таким образом, суммарная фаза гармонического сигнала прямо пропорциональна числу 2. Напряжение на выходе интегратора 13 в канале измерителя фазы будет максимальным для второго номера канала. Следовательно, на выход 6 устройства после шифратора 5 поступит число 2 в двоичном коде.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2007 |

|

RU2338241C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2000 |

|

RU2188448C2 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЛА ПО МОДУЛЮ НА КОНСТАНТУ | 2017 |

|

RU2653310C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2004 |

|

RU2270476C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2004 |

|

RU2263948C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ m | 2020 |

|

RU2748744C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ n-РАЗРЯДНОГО ДВОИЧНОГО ПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД ОСТАТКА ПО МОДУЛЮ m | 2003 |

|

RU2242085C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ n-РАЗРЯДНОГО ДВОИЧНОГО ПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД ОСТАТКА ПО МОДУЛЮ m | 2001 |

|

RU2192092C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ m | 2020 |

|

RU2748743C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах, функционирующих в модулярной системе счисления. Техническим результатом является расширение функциональных возможностей устройства за счет выполнения модульной операции умножения и нахождение остатка по модулю от числа. Устройство содержит генератор гармонического сигнала, управляемые фазовращатели, измеритель фазы гармонического сигнала, фазовращатели на фиксированное значение фазы, шифратор, блоки умножения на константу по модулю, блоки элементов И, дешифраторы. 3 ил.

Устройство для умножения чисел по модулю, содержащее l дешифраторов (l=[log2p], где р - модуль устройства), l управляемых фазовращателей, генератор гармонического сигнала, измеритель фазы гармонического сигнала, (р-1) фазовращателей на фиксированные значения фазы и шифратор, причем выход генератора гармонического сигнала соединен с первым входом первого управляемого фазовращателя, выход i-го управляемого фазовращателя - с первым входом (i+1)-го управляемого фазовращателя (i=1, l-1), выход l-го управляемого фазовращателя - со входом 1 измерителя фазы гармонического сигнала, вход 2 которого соединен с выходом генератора гармонического сигнала, вход  измерителя фазы гармонического сигнала соединен с выходом генератора гармонического сигнала через фазовращатель на фиксированное значение фазы, равное

измерителя фазы гармонического сигнала соединен с выходом генератора гармонического сигнала через фазовращатель на фиксированное значение фазы, равное  , при этом вход (р+2) измерителя фазы гармонического сигнала является тактовым входом устройства, выход измерителя фазы гармонического сигнала соединен со входом шифратора, выход которого является выходом устройства, а выходы дешифраторов подключены ко вторым входам соответствующих управляемых фазовращателей, отличающееся тем, что в него введены (l-1) блоков умножения на константу по модулю и l блоков элементов И, причем вход первого сомножителя устройства соединен со входами блоков умножения на константу по модулю и вторым входом l-го блока элементов И, входы разрядов второго сомножителя соединены с первыми входами соответствующих блоков элементов И, выходы которых подключены к входам соответствующих дешифраторов, а выходы блоков умножения на константу по модулю соединены со вторыми входами соответствующих блоков элементов И.

, при этом вход (р+2) измерителя фазы гармонического сигнала является тактовым входом устройства, выход измерителя фазы гармонического сигнала соединен со входом шифратора, выход которого является выходом устройства, а выходы дешифраторов подключены ко вторым входам соответствующих управляемых фазовращателей, отличающееся тем, что в него введены (l-1) блоков умножения на константу по модулю и l блоков элементов И, причем вход первого сомножителя устройства соединен со входами блоков умножения на константу по модулю и вторым входом l-го блока элементов И, входы разрядов второго сомножителя соединены с первыми входами соответствующих блоков элементов И, выходы которых подключены к входам соответствующих дешифраторов, а выходы блоков умножения на константу по модулю соединены со вторыми входами соответствующих блоков элементов И.

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2000 |

|

RU2188448C2 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ | 1997 |

|

RU2131618C1 |

| Устройство для умножения чисел по модулю | 1988 |

|

SU1697079A1 |

| Устройство для умножения чисел по модулю | 1988 |

|

SU1617439A1 |

| WO 00/05645 A1, 03.02.2000 | |||

| US 6321247 A, 20.11.2001. | |||

Авторы

Даты

2007-12-20—Публикация

2006-05-02—Подача