Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для перевода чисел из двоичной позиционной системы в систему остаточных классов,,

Цель изобретения - упрощение преобразователя.

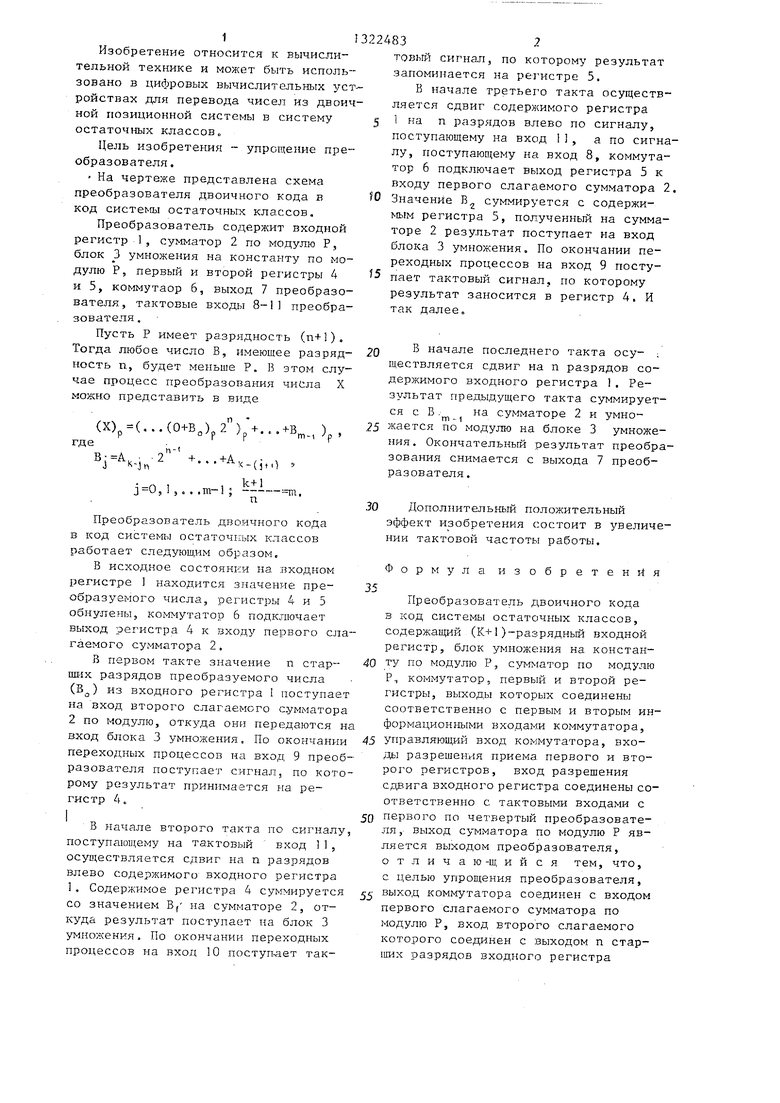

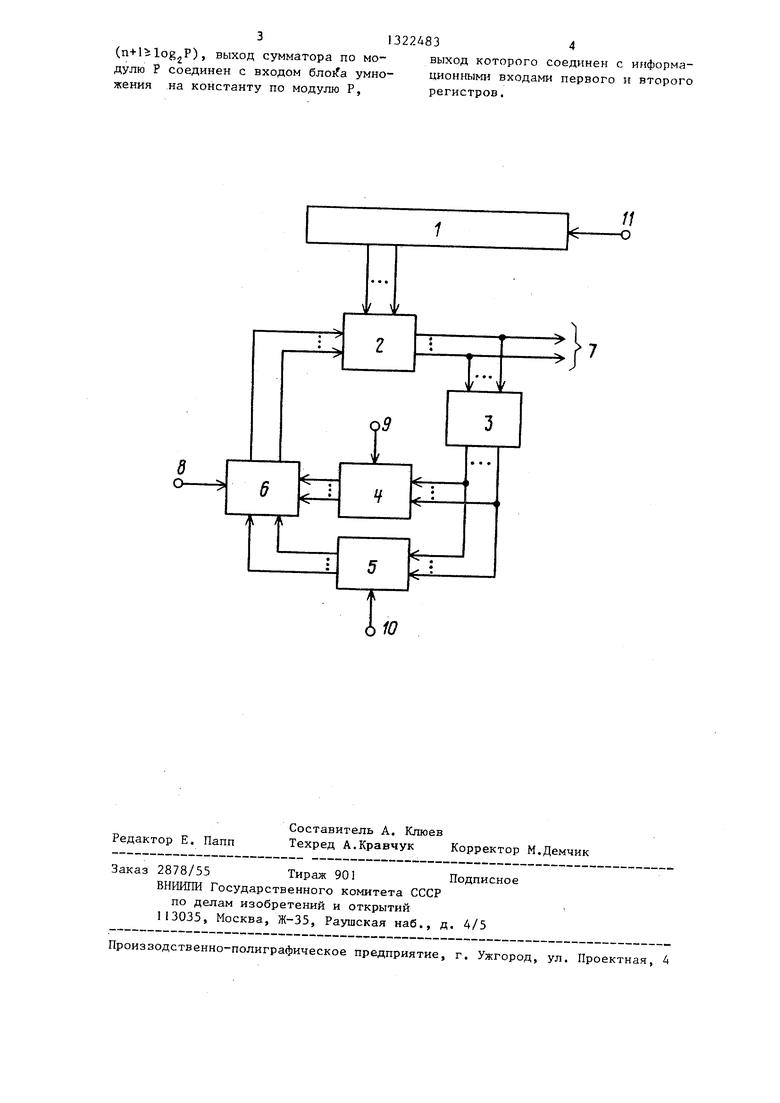

На чертеже представлена схема преобразователя двоичного кода в код системы остаточных классов.

Преобразователь содержит входной регистр 1, сумматор 2 по модулю Р, блок 3 умножения на константу по модулю Р, первый и второй регистры 4 и 5, коммутаор 6, выход 7 преобразователя, тактовые входы 8-11 преобразователя ,

Пусть Р имеет разрядность (п+1). Тогда любое число В, имеющее разряд- ность п, будет меньше Р. В этом случае процесс преобразования числа X можно представить в виде

где

(Х)р(,..(0+В,)р2 ),.,,

, +...+А,.(.,,, ,

k+1 ,1,.., .

Преобразователь двоичного кода в код системы остаточнгых классов работает следующим образом,

В исходное состоянии на входном регистре 1 1аходится значение пре- образуемого числа, регистры 4 и 5 обнулены, коммутатор 6 подключает выход регистра 4 к входу первого слагаемого сумматора 2,

В первом такте значение и стар- ших разрядов преобразуемого числа (B,j) из входного регистра I поступает на вход второго слагаемого сумматора 2 по модулю, откуда они передаются на вход блока 3 умножения. По окончании переходных процессов на вход 9 преобразователя поступает сигнал, по которому результат принимается па регистр 4.

I

В начале второго такта по сигналу

поступающему на тактовый вход 11, осуп;ествляется сдвиг на п разрядов влево содержимого входного регистра 1, Содержимое регистра 4 суммируется со значением В( на сумматоре 2, откуда результат поступает на блок 3 умножения. По окончании переходных процессов на вход 10 поступ-ает так

5

0

5

0

5

0 5

0

товый сигнал, по которому результат запоминается на регистре 5.

В начале третьего такта осуществляется сдвиг содержимого регистра 1 на п разрядов влево по сигналу, поступающему на вход 11, а по сигналу, поступающему на вход 8, коммутатор 6 подключает выход регистра 5 к входу первого слагаемого сумматора 2. Значение В суммируется с содержимым регистра 5, полученный на сумматоре 2 результат поступает на вход блока 3 умножения. По окончании переходных процессов на вход 9 поступает тактовый сигнал, по которому результат заносится в регистр 4. И так далее.

В начале последнего такта осу- ; ществляется сдвиг на п разрядов содержимого входного регистра 1. Результат предыдущего такта суммируется с В . на сумматоре 2 и умножается по модулю на блоке 3 умножения. Окончательный результат преобразования снимается с выхода 7 преобразователя .

Дополнительный положительный эффект изобретения состоит в увеличении тактовой частоты работы.

Формула изобретения

Преобразователь двоичного кода в код системы остаточных классов, содержащий (К+1)-разрядный входной регистр, блок умножения на константу по модулю РЭ сумматор по модулю Р., коммутатор, первый и второй регистры, выходы которых соединены соответственно с первым и вторым информационными входами коммутатора, управляющий вход коммутатора, вхо- fsjbi разрешения приема первого и второго регистров, вход разрешения входного регистра соединены соответственно с тактовыми входами с первого по четвертый преобразователя, выход сумматора по модулю Р является выходом преобразователя, о т л и ч а ю-щ и и с я тем, что, с целью упроп ения преобразователя, выход коммутатора соединен с входом первого слагаемого сумматора по модулю Р, вход второго слагаемого которого соединерЕ с выходом п старших разрядов входного регистра

313224834

(n+lilog-P), выход сумматора по мо- выход которого соединен с имформа- дулю Р соединен с входом умно- ционными входами первого н второго жения на константу по модулю Р, регистров.

Редактор Е. Папп

Составитель А. Клюев

Техред А.Кравчук Корректор М.Демчик

Заказ 2878/55 Тираж 901Подписное

ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий I13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в код системы остаточных классов | 1984 |

|

SU1156058A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1985 |

|

SU1269271A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

| Устройство для вычисления остатка по модулю 2 @ +1 | 1990 |

|

SU1734212A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU983701A1 |

| Преобразователь непозиционного кода в двоичный код | 1988 |

|

SU1578810A1 |

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Авторское свидетельство СССР что в преобразователе, содержащем № 1269271, .кл, Н 03 М 7/18, 1985 | |||

| входной регистр, сумматор по модулю Авторское свидетельство СССР Р, блок умножения на константу по № 1176383, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| модулю Р, два регистра и коммутатор, изменены связи между блоками устройства | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| S сл | |||

Авторы

Даты

1987-07-07—Публикация

1985-06-03—Подача