Область техники

Изобретение относится к радиотехническим средствам связи, а конкретно к устройствам для определения скорости передачи пакетов данных в системах сотовой радиосвязи, например с кодовым разделением каналов, и может найти применение как в прямом, так и обратном каналах системы CDMA 2000.

Уровень техники

Как известно, аналогично прямому каналу IS-95 основные прямой и обратный каналы CDMA 2000 обеспечивают четыре скорости передачи данных из двух комплектов:

первый комплект (Set1): 9600, 4800, 2400, 1200 бит/с;

второй комплект (Set2): 14400, 7200, 3600, 1800 бит/с.

В основном канале во всех диапазонах скоростей передачи используется сверточное кодирование различной избыточности. При этом длина кода во всех случаях равна 9.

Повторение бит для коррекции скорости производится как в прямом, так и обратном каналах при скоростях передачи данных, меньших максимальной. Одновременно, когда скорость передачи данных ниже максимально используемой, мощность сигнала снижается. Это приводит к значительному снижению помех многостанционного доступа и, следовательно, к повышению пропускной способности системы связи. Однако на приемном конце скорость передачи данных неизвестна, поэтому необходимо применять устройство для ее определения.

Известен метод для "слепого" определения скорости передачи данных, использующий корреляцию между повторяющимися битами при скоростях передачи данных, меньших максимальной, описанный в статьях Е. Cohen and Lou "Multirate Detection for the IS-95 СDМА forward traffic channels ", IEEE GLOBECOM 95, November 1995 [1] и E. Cohen and H. Lou "Multirate Detection for the IS-95A CDMA forward traffic channels using 13 kbps speech coder", IEEE GLOBECOM 96, November 1996 [2].

Термин "слепой" является переводом с английского языка общепринятого понятия "Blind Data Rate Detection", означающего метод определения скорости без использования какой-либо специально предназначенной для этого информации, индикатора или признака. Такой многоскоростной детектор использует алгоритм расчета трех решающих величин, согласованных с возможными скоростями, и с последующим сравнением с порогами.

Метод расчета решающих величин при этом прост с точки зрения объема вычислений - без умножения, но с использованием только суммы абсолютной величины, однако метод сравнения решающих переменных с пороговой системой очень сложен и не оптимален, что также снижает достоверность принятия решений.

Известен способ, описанный в патенте WO 9508888 "Multirate serial decoding method for code division multiple access mobile", QUALCOMM Inc. [3].

Такой способ служит для обеспечения автоматического декодирования каждого фрейма с любой неизвестной скоростью передачи информации.

Последовательный декодер (декодер Витерби) выполняет автоматическое декодирование для каждого из множества режимов путем выполнения множества проходов для декодирования каждого фрейма с каждой из всех возможных заданных скоростей передачи информации и обеспечивает определение начальной скорости передачи информации.

Такой метод позволяет достаточно точно определить скорости переданных данных, однако четырехкратное (в случае CDMA 2000) использование декодера Витерби значительно усложняет устройство для реализации такого способа.

Наиболее близким по технической сущности к предлагаемому является способ определения скорости передачи информации, описанный в патенте US 5774496 "Method and apparatus for determining data rate of transmitted variable rate in a communications receiver", QUALCOMM Inc., Jun. 30, 1998 [4]. Описанный в указанном патенте способ определения скорости данных принимаемого сигнала также основан на четырехкратном декодировании и анализе циклической контрольной суммы на приеме. Термин "циклическая контрольная сумма" (cyclic redundancy check), это последовательность бит, доставляемая в передаваемый пакет данных на передающем конце линии связи и предназначенная для проверки качества принятых данных на приемном конце. Данную последовательность получают на основе всех передаваемых информационных бит пакета. На приемном конце связи также выполняется вычисление данной последовательности, но на основе принятых информационных бит. Несовпадение переданной контрольной суммы и вновь вычисленной на приемном конце линии связи говорит о том, что либо информационные биты, либо контрольная сумма принята ошибочно. Описанные в [4] способ заключается в следующем:

- декодируют и повторно кодируют на первой скорости данных пакет указанного принимаемого сигнала для формирования первой оценки принимаемого сигнала и первой циклической контрольной суммы (CRC) на приеме;

- сравнивают первую оценку принимаемого сигнала с принимаемым сигналом и подсчитывают первое количество ошибок (SER), при этом ошибка происходит в случае, когда указанный принимаемый сигнал не соответствует указанной первой оценке сигнала, указанное количество ошибок (SER) и первый показатель качества - CRC на приеме, определяют первую метрику ошибки;

- перерабатывают указанный принимаемый сигнал для формирования второго принимаемого сигнала, представляющего вторую скорость передачи данных;

- декодируют и повторно кодируют на второй скорости данных указанного принимаемого сигнала для формирования второй оценки принимаемого сигнала и второй CRC на приеме;

- сравнивают вторую оценку принимаемого сигнала с принимаемым сигналом и подсчитывают второе SER, при этом ошибка происходит в случае, когда указанный принимаемый сигнал не соответствует указанной второй оценке сигнала, указанное количество SER и второй показатель качества определяют вторую метрику ошибки;

- перерабатывают указанный принимаемый сигнал для формирования третьего принимаемого сигнала, представляющего третью скорость передачи данных;

- декодируют и повторно кодируют на третьей скорости данных указанного принимаемого сигнала для формирования третьей оценки принимаемого сигнала и третьей CRC на приеме;

- сравнивают третью оценку принимаемого сигнала с принимаемым сигналом и подсчитывают третье количество SER, при этом ошибка происходит в случае, когда указанный принимаемый сигнал не соответствует указанной третьей оценке сигнала, указанное количество SER и третья CRC на приеме определяют третью метрику ошибки;

- перерабатывают указанный принимаемый сигнал для формирования четвертого принимаемого сигнала, представляющего четвертую скорость передачи данных;

- декодируют и повторно кодируют на четвертой скорости данных указанного принимаемого сигнала для формирования четвертой оценки принимаемого сигнала и четвертой CRC на приеме;

- сравнивают четвертую оценку принимаемого сигнала с принимаемым сигналом и подсчитывают четвертое количество ошибок (SER), при этом ошибка происходит в случае, когда указанный принимаемый сигнал не соответствует указанной четвертой оценке сигнала, указанное количество ошибок (SER) и четвертый показатель качества - CRC на приеме определяют четвертую метрику ошибки;

- предсказывают скорость данных указанного принимаемого сигнала на основе сравнения каждой из обозначенных метрик ошибки;

- при переработке принимаемого сигнала в режиме повторения (прямой канал IS-95) суммируют по 2, 4 или 8 отсчетов, в режиме DBR (обратный канал IS-95) выбирают определенные отсчеты.

Недостатком такого способа является использование четырехкратного декодирования Витерби, что усложняет устройство, его реализующее, увеличивает время обработки и потребляемую мощность.

Сущность изобретения

Задачей, которую решает заявляемое изобретение, является упрощение способа слепого определения скорости передачи пакета данных на приемном конце линии связи (далее "на приеме"), сокращение среднего времени обработки и потребляемой мощности при сохранении высокой точности различения скоростей.

Для решения этой задачи в способ слепого определения скорости передачи данных, заключающийся в том, что поочередно декодируют принимаемый сигнал в соответствии с гипотезой о скорости передачи данных, вычисляют циклическую контрольную сумму на приеме, производят обратное кодирование (при этом "обратное кодирование" предполагает, что все декодированные информационные биты, а также биты циклической контрольной суммы вновь кодируются с целью получения оценки принятых кодовых символов) и формируют оценку вероятности символьной ошибки, сравнивают вероятности символьной ошибки с порогом, дополнительно вводят новую последовательность операций: декодирование прекращают и принимают решение о скорости передачи данных, если при проверке очередной гипотезы вероятность символьной ошибки меньше порога и циклическая контрольная сумма на приеме совпадает, при этом порядок проверки гипотез выбирают таким образом, чтобы минимизировать средние вычислительные затраты, если после проверки всех гипотез скорость не определена, то ее определяют из условий:

- если циклическая контрольная сумма на приеме совпадает только для одной гипотезы, то решение о скорости передачи данных принимают в пользу этой гипотезы;

- если циклические контрольные суммы на приеме совпадают для нескольких гипотез одновременно, то решение о скорости передачи данных выносят в пользу той из них, которая обеспечивает минимальную вероятность символьной ошибки;

- если циклическая контрольная сумма на приме не совпадает ни для одной гипотезы, то решение о скорости передачи данных принимают в пользу той гипотезы, которая обеспечивает минимальную вероятность символьной ошибки.

Кроме того, проверку гипотез проводят последовательно, начиная с минимальной и до максимальной.

Проверку гипотез на текущем пакете можно начинать с принятого решения о скорости предыдущего пакета.

Еще одним вариантом проверки гипотез является то, что проверку гипотез выполняют в таком порядке, который обеспечивает минимальную сумму произведений скорости передачи на соответствующую ей апостериорную вероятность.

Предлагаемый способ заключается в следующем:

1) поочередно декодируют принимаемый сигнал в соответствии с гипотезой о скорости передачи данных до момента правильного определения скорости;

2) вычисляют циклическую контрольную сумму (CRC) на приеме;

3) производят обратное кодирование и формируют оценку вероятности символьной ошибки (SER);

4) сравнивают вероятности символьной ошибки с порогом;

5) с учетом проверки циклической контрольной суммы (CRC) на приеме определяют скорость передачи данных;

6) декодирование прекращают и принимают решение о скорости передачи данных, если при проверке очередной гипотезы вероятность символьной ошибки меньше порога и циклическая контрольная сумма на приеме совпадает;

7) порядок проверки гипотез выбирают таким образом, чтобы минимизировать средние вычислительные затраты, если после проверки всех гипотез скорость не определена, то ее определяют из условий:

- если циклическая контрольная сумма на приеме совпадает только для одной гипотезы, то решение о скорости передачи данных принимают в пользу этой гипотезы;

- если циклические контрольные суммы на приеме совпадают для нескольких гипотез одновременно, то решение о скорости передачи данных выносят в пользу той из них, которая обеспечивает минимальную вероятность символьной ошибки;

- если циклическая контрольная сумма на приеме не совпадает ни для одной гипотезы, то решение о скорости передачи данных принимают в пользу той гипотезы, которая обеспечивает минимальную вероятность символьной ошибки.

Проверку гипотез можно проводить различными путями:

- проверку гипотез проводят последовательно, начиная с минимальной и до максимальной;

- проверку гипотез на текущем пакете начинают с принятого решения о скорости предыдущего пакета;

- альтернативно, проверку гипотез выполняют в таком порядке, который обеспечивает минимальную сумму произведений скорости передачи на соответствующую ей апостериорную вероятность.

Перечень чертежей

Графические материалы, поясняющие заявляемое изобретение:

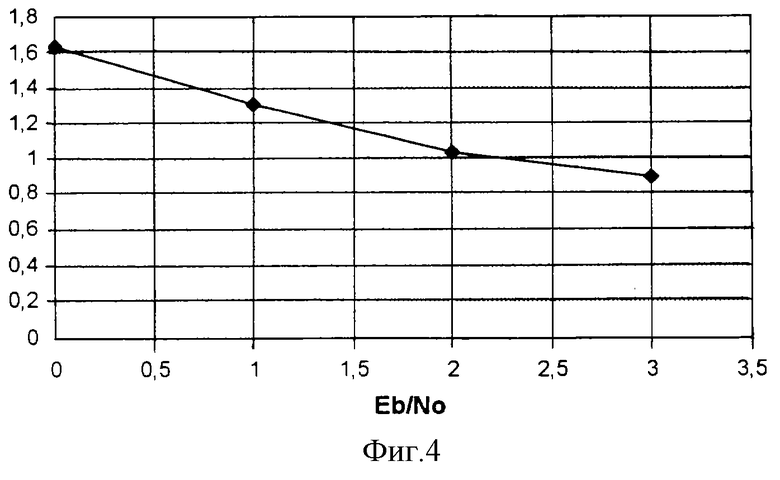

фиг. 1 - блок схема для реализации предлагаемого способа определения скорости передачи данных;

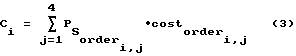

фиг.2 - пример выполнения блока определения апостериорной вероятности;

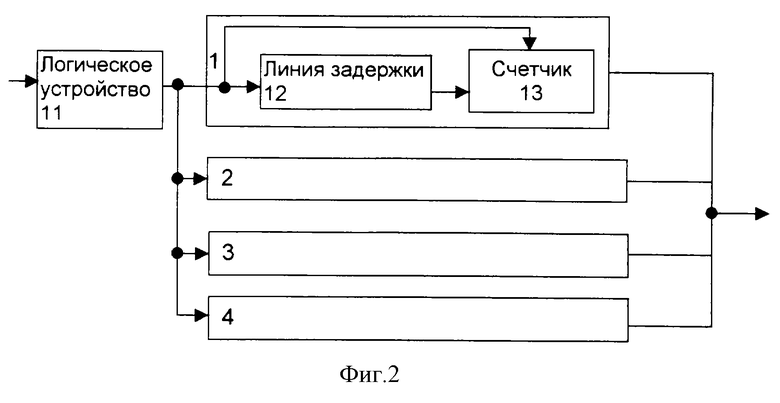

фиг. 3 - зависимость вероятности пакетной ошибки от величины отношения энергии бита к спектральной плотности шума;

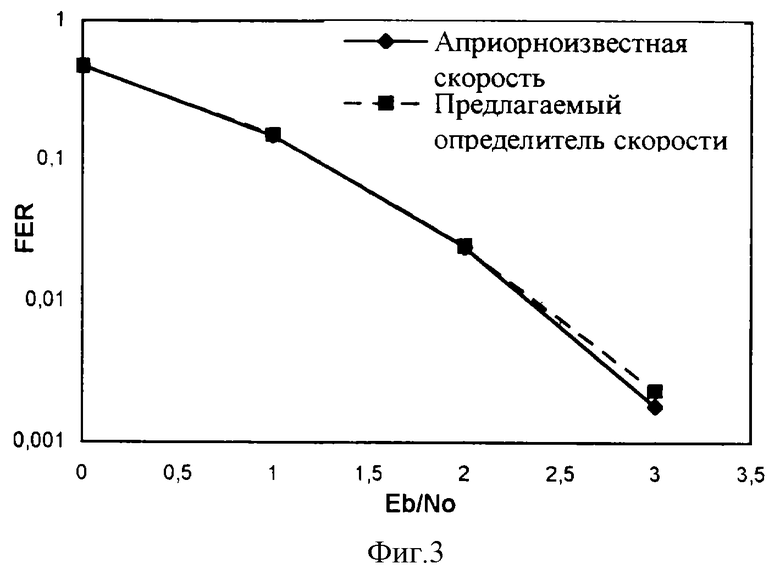

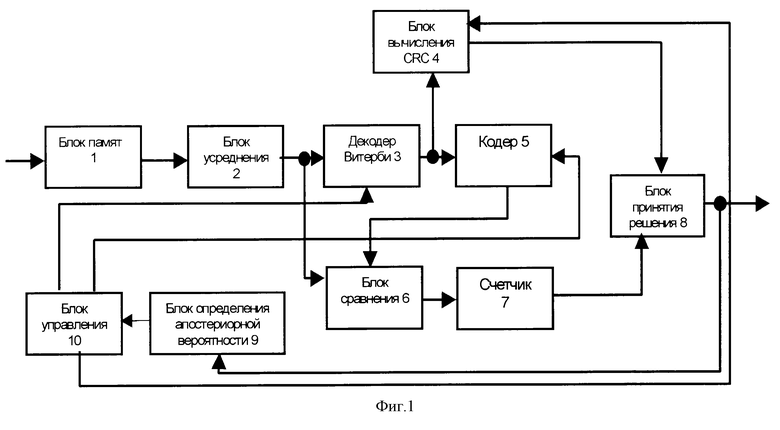

фиг.4 - вычислительная сложность декодирования.

Предпочтительный способ осуществления изобретения

Для реализации предложенного способа используется устройство, представленное на фиг.2, где обозначено:

1 - блок памяти,

2 - блок усреднения,

3 - декодер Витерби,

4 - блок вычисления циклической контрольной суммы (CRC) на приеме,

5 - кодер,

6 - блок сравнения,

7 - счетчик,

8 - блок принятия решения,

9 - блок определения апостериорной вероятности,

10 - блок управления.

Устройство содержит последовательно соединенные блок памяти 1, вход которого является входом устройства, блок усреднения 2, декодер Витерби 3, кодер 5, блок сравнения 6, счетчик 7, блок принятия решения 8, выход которого является выходом устройства, блок определения априорной вероятности 9, блок управления 10. Первый выход блока управления 10 соединен со вторым входом декодера Витерби 3, второй выход блока управления 10 соединен со вторым входом кодера 5 и третий выход блока управления 10 соединен со вторым входом блока 4 вычисления CRC на приеме. Выход блока усреднения 2 также соединен со вторым входом блока сравнения 6. Выход декодера Витерби 3 соединен со входом блока 4 вычисления CRC на приеме, выход которого соединен со вторым входом блока принятия решения 8.

Работает устройство следующим образом.

Отсчеты принятого сигнала запоминают в блоке памяти 1. Так как скорость передачи информации для каждого принимаемого сигнала различна, то осуществляют подготовку входного сигнала декодера, заключающуюся в усреднении одного, двух, четырех и восьми отсчетов в соответствии с гипотезой о скорости пакета данных с помощью блока усреднения 2. Декодируют отсчеты принятого сигнала в декодере Витерби 3 и для каждого принимаемого сигнала вычисляют циклическую контрольную сумму на приеме в блоке 4 вычисления CRC. Сигнал после декодирования подвергают обратному кодированию в кодере 5 для формирования оценки принимаемого сигнала. В блоке сравнения 6 производят сравнение оценки принятого сигнала с порогом (причем величина порога определяется типом кодера) и затем счетчик 7 посчитывает количество ошибок, формируя вероятность символьной ошибки (SER).

Результаты сравнения передаются в блок принятия решения 8, где производят определение скорости принятой информации путем сравнения вероятности символьной ошибки с порогом и с учетом результатов проверки циклической контрольной суммы на приеме. Для каждого этапа определения скорости блок принятия решения 8 рассматривает следующие варианты решений. Если вероятность символьной ошибки меньше порога и циклическая контрольная сумма на приеме совпадает, то декодирование прекращают и данную гипотезу считают верной. При этом порядок проверки гипотез выбирают таким образом, чтобы минимизировать средние вычислительные затраты.

Если после проверки всех гипотез скорость не определена, то ее определяют из следующих условий. Если CRC на приеме совпадает только для одной гипотезы, то решение о скорости передачи пакета данных принимают в пользу этой гипотезы. Если CRC на приеме совпадают для нескольких гипотез одновременно, то решение о скорости передачи пакета данных выносят в пользу той из них, которая обеспечивает и минимальную вероятность символьной ошибки. Если CRC на приеме не совпадает ни для одной гипотезы, то решение о скорости передачи пакета данных выбирают из той гипотезы, которая обеспечивает минимальную вероятность символьной ошибки.

Для определения порядка декодирования используется блок определения апостериорной вероятности 9, пример выполнения которого приведен на фиг.2. В начальный момент времени все счетчики 13 установлены в состояние 1. Когда на логическое устройство 11 с блока принятия решения 8 поступает 1, то логическое устройство 11 подает 1 на вход канала, соответствующего определенной скорости, а на все остальные каналы - 0. Результат накопления счетчика 13 пропорционален апостериорной вероятности скорости. При этом при поступлении сигнала на верхний вход счетчика 13 накопление счетчика увеличивается на 1, при поступлении сигнала на нижний вход счетчика 13 - уменьшается на 1.

Управляет работой устройства блок управления 10.

Докажем достижение поставленной цели.

В рамках общепринятого подхода выполняется четырехкратное декодирование Витерби. Если принять вычислительную сложность декодирования пакета данных максимальной скорости за 1, то, с учетом уменьшения длины пакета на младших скоростях, сложность общепринятого слепого детектора скорости равна

1 + 0,5 + 0,25 + 0,125 = 1,875, (1)

где cost=[1, 0.5, 0.25, 0.125] - вычислительная сложность декодирования соответствующих скоростей.

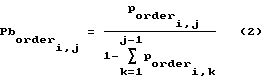

Предлагается выполнять декодирование соответствующих скоростей поочередно и в случае совпадения CRC и выполнения условия SER<T останавливать декодирование. Основной целью дальнейших выводов является нахождение такого порядка декодирования скоростей, при котором средняя вычислительная сложность будет минимальна. При использовании четырехскоростного вокодера возможно 4!=24 различных порядка (т.е. order1=[1 2 3 4], order2=[1 2 4 3] и т.д. ). Другими словами необходимо найти оптимальный порядок проверки гипотез о скорости, причем следует учесть, что i-я гипотеза имеет определенную вероятность рi и ее проверка требует вычислительных затрат costi. Пусть p1, р2, р3 и р4 - вероятности соответствующих скоростей и orderi - i-й порядок декодирования (i∈[1, 24]), то вероятность того, что декодирование будет остановлено на j-м шаге (если декодирование дошло до j-го шага) равна

Вероятность того, что декодирование дойдет до соответствующего шага, равна:

Ps1= 1, Ps2= 1-Pborderi,1, Ps3=(1-Pborderi,1)•(1-Pborderi,2), Ps4=(1-Pborderi,1)•(1-Pborderi,2)•(1-Pborderi,3).

Средняя вычислительная стоимость декодирования в соответствии с i-м порядком равна

Оптимальная очередность декодирования будет соответствовать порядку с минимальной средней стоимостью. Для примера рассмотрим случай равновероятных гипотез, т. е. p1= p2= p3=p4=0.25. Минимальная стоимость, соответствующая, очевидно, порядку декодирования [4 3 2 1], равна С=0.8124. Если же вероятности гипотез равны р=[0.4 0.1 0. 0.4], то оптимальным является порядок декодирования [4 1 3 2] со стоимостью С=0.88.

Необходимо отметить, что в приведенных выше рассуждениях результат проверки гипотез предполагался безошибочным. В реальных условиях средняя стоимость будет несколько выше.

Результаты моделирования декодера с предлагаемым определителем скорости в канале с белым гауссовским шумом приведены на фиг.3 и фиг.4. Там же для сравнения приведены параметры при априорно известной скорости данных.

Как следует из результатов моделирования, характеристики декодирования в обоих случаях практически одинаковы, в то время как на интересующем уровне пакетной ошибки 1% вычислительная сложность предлагаемого метода, в среднем, составляет 0,9, что в 2,0 раза ниже, чем сложность общепринятого подхода.

Сопоставительный анализ способа слепого определения скорости передачи пакета данных с прототипом показывает, что предлагаемое изобретение существенно отличается от прототипа, так как поочередное декодирование Витерби позволяет значительно сократить время обработки и потребляемую мощность при сохранении высокой точности различения скоростей.

Изобретение относится к радиотехническим средствам связи, а конкретно к устройствам для определения скорости передачи пакетов данных в системах сотовой радиосвязи, например, с кодовым разделением каналов и может найти применение как в прямом, так и в обратном каналах системы CDMA 2000. Технический результат - упрощение способа слепого определения скорости передачи пакета данных, сокращение времени обработки и потребляемой мощности при сохранении высокой точности различения скоростей. Для решения этой задачи предлагается выполнять декодирование соответствующих скоростей поочередно, и в случае совпадения циклических контрольных сумм CRC на приеме и выполнения условия, когда вероятность символьной ошибки меньше порога SER<Т, останавливать декодирование. Основной целью дальнейших выводов является нахождение такого порядка декодирования скоростей, при котором средняя вычислительная сложность будет минимальна. Порядок декодирования скоростей может быть выбран различными путями, например, проверку гипотез проводят последовательно, начиная с минимальной и до максимальной. Другим вариантом выбора порядка декодирования является тот, когда проверку гипотез на текущем пакете начинают с принятого решения о скорости предыдущего пакета. Проверку гипотез можно выполнять в таком порядке, который обеспечивает минимальную сумму произведений скорости передачи на соответствующую ей апостериорную вероятность. 2 з.п.ф-лы, 4 ил.

| US 5774496 А, 30.06.1998 | |||

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| US 5453997 А., 26.09.1995 | |||

| Способ получения алкилзамещенных 3-метиламино-1-пропанолов | 1977 |

|

SU643493A1 |

| 1972 |

|

SU413505A1 | |

| 1973 |

|

SU430428A1 | |

| Прибор для контроля линий контакта роликов с наружным кольцом подшипника | 1972 |

|

SU446745A1 |

Авторы

Даты

2003-01-27—Публикация

1999-07-16—Подача