Изобретение относится к электронике и предназначено для использования в сумматорах чисел в двоичном представлении.

Известны схемы переноса сумматоров двух слагаемых, в которых сигнал переноса каждого разряда формируется с использованием сигнала переноса предыдущего разряда (см., например, Киносита К., Асада К., Карацу О. Логическое проектирование СБИС: Пер. с япон. - М.: Мир, 1988, с. 67, рис. 2.26 [1]). С увеличением числа разрядов в таких схемах пропорционально удлиняется цепочка переноса и поэтому растет наихудшее значение временной задержки, что является недостатком.

Уменьшить задержку сигналов переноса в старшие разряды позволяет пирамидальная схема ускоренного переноса (см. Киносита К., Асада К., Карацу О. Логическое проектирование СБИС: Пер. с япон. - М.: Мир, 1988, с. 69, рис. 2.27 и 2.28. [2]). В этой схеме сигнал переноса в каждый разряд формируется непосредственно из сигналов предыдущих разрядов суммирующих чисел, используя древовидный алгоритм, позволяющий укоротить цепочки переноса. Данное устройство по технической сущности наиболее близко к изобретению.

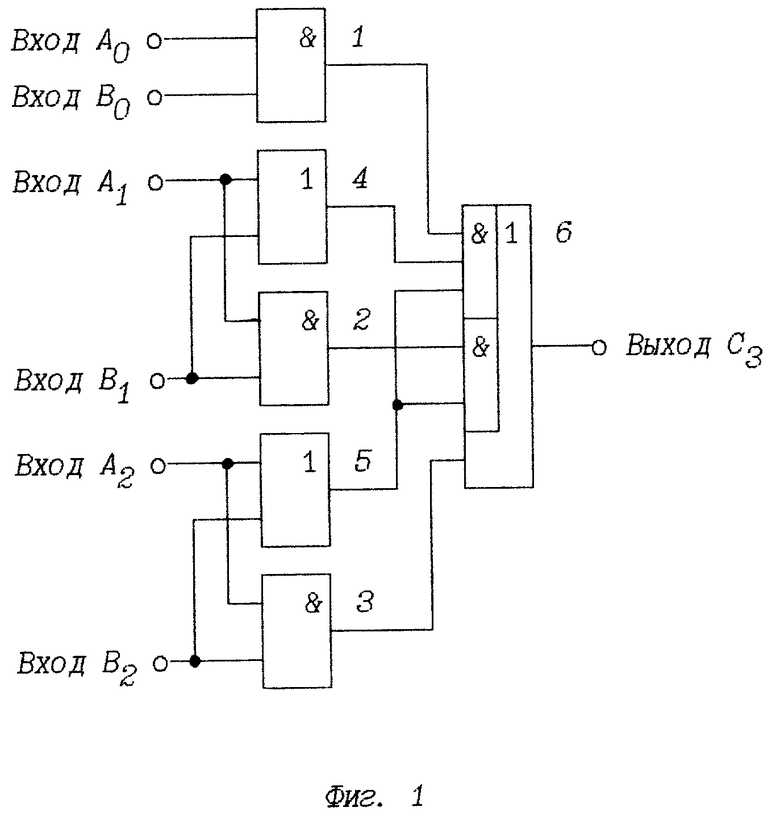

Наиболее близкий аналог содержит элементы 1-3 2И, формирующие сигналы возникновения переноса, в количестве, равном числу суммируемых разрядов n, из которых осуществляется перенос, элементы 4, 5 2ИЛИ, формирующие сигналы распространения переноса в количестве n-1 и выходной элемент 6 nИ-(n-1)И-... 2И-nИЛИ. Входы элементов 2И подключены ко входам пар разрядов суммируемых чисел, начиная с младших, в соответствии с номерами элементов. Входы элементов 2ИЛИ подключены ко входам пар разрядов суммируемых чисел, начиная со следующих за младшими, в соответствии с номерами элементов. У элемента 6 nИ-(n-1)И-...2И-nИЛИ первые входы в группах объединений nИ, (n-1)И, ... 2И и внешний вход функции nИЛИ подключены соответственно к выходам с первой по n-й элементов 2И, остальные входы в группах объединения iИ, где i = 2,...n, соединены с выходами с первого по i-1-й элементов 2ИЛИ. Выход элемента 6 nИ-(n-1)И-...2И-nИЛИ является выходом сигнала переноса Cn из n разрядов суммируемых чисел.

Устройство-аналог работает следующим образом.

Известное из литературы логическое выражение для сигнала переноса Cn в n-й разряд суммы двух чисел, разряды которых обозначены как A0, A1,...An-1 и B0, B1,...Bn-1, выглядит следующим образом.

Cn = Pn-1...P1G0 + Pn-1...P2G1 + Pn-1Gn-2 + Gn-1 (*)

где Gj = AjBj (j = 0,..., n-1) указывает на условия возникновения переноса в j-м разряде, а Pk = Ak + Bk (k = 1,..., n-1) - на условия распространения переноса из разрядов младше k-го в следующие за k-м.

Перенос из какого-либо разряда суммы двух чисел в следующий возникает при одновременном наличии единиц в соответствующих разрядах обоих слагаемых. Эти ситуации позволяют выявить элементы 1-3 2И, на входы которых поступают разряды складываемых чисел.

В i-й разряд суммы возникающие переносы передаются, если в парах предыдущих разрядов слагаемых вплоть до i-1-го присутствует хотя бы по одной единице, условия распространения переносов проверяют при помощи элементов 4, 5 2ИЛИ.

Выходной элемент 6 nИ-(n-1)И-...2И-nИЛИ формирует сигналы переноса Cn в соответствии с выражением (*).

Недостатком устройства-аналога является ограниченность его разрядности - n количеством входов в группах объединений И и ИЛИ выходного элемента 6, определяющего быстродействие устройства.

Задачей настоящего изобретения является достижение технического результата, заключающегося в повышении разрядности схемы ускоренного переноса без увеличения количества каскадов в критическом тракте распространения сигнала переноса, снижающего быстродействие устройства.

Поставленная задача решается тем, что в схеме ускоренного переноса, содержащей с первого по n-й формирователи сигналов возникновения переноса и с первого по n-1-й формирователи сигналов распространения переноса и выходной элемент nИ-(n-1)И-...2И-nИЛИ, у которого первые входы в группах объединений nИ, (n-1)И, ... 2И и внешний вход функции nИЛИ подключены соответственно к выходам с первого по n-й формирователей сигналов возникновения переноса, остальные входы в группах объединения iИ, где i = 2,..., n, соединены с выходами с первого по i-1-й формирователей сигналов распространения переноса, n-й формирователь сигнала возникновения переноса выполнен на элементе 2И, входы которого подключены ко входам пары старших разрядов суммирующих чисел, с первого по n-1-й формирователи сигналов возникновения переноса представляют собой элементы 2И-2И-2ИЛИ, входы каждой пары объединений по И которых подключены ко входам пар разрядов суммируемых чисел в соответствии с возрастанием номеров, начиная с младшего, формирователи сигналов распространения переноса представляют собой элементы 2ИЛИ-2ИЛИ-2И, входы каждой пары объединений по ИЛИ которых подключены ко входам пар разрядов суммируемых чисел в соответствии с возрастанием номеров, начиная со следующей за младшей.

Данное выполнение устройства применимо в случаях формирования переноса из нечетного количества разрядов суммируемых чисел.

В случаях четной разрядности в схеме ускоренного переноса, содержащей с первого по n-й формирователи сигналов возникновения переноса и с первого по n-1-й формирователи сигналов распространения переноса и выходной элемент nИ-(n-1)И-. . . 2И-nИЛИ, у которого первые входы в группах объединений nИ, (n-1)И, . .. 2И и внешний вход функции nИЛИ подключены соответственно к выходам с первого по n-й формирователей сигналов возникновения переноса, остальные входы в группах объединения, iИ, где i = 2,...n, соединены с выходами с первого по i-1-й формирователей сигналов распространения переноса, формирователи сигналов возникновения переноса представляют собой элементы 2И-2И-2ИЛИ, входы каждой пары объединений по И которых подключены ко входам пар разрядов суммируемых чисел в соответствии с возрастанием номеров, начиная с младшего, с первого по n-1-й формирователи сигналов распространения переноса представляют собой элементы 2ИЛИ-2ИЛИ-2И, входы каждой пары объединений по ИЛИ которых подключены ко входам пар разрядов суммируемых чисел в соответствии с возрастанием номеров, начиная со следующего за младшим, в устройство дополнительно введен n-й формирователь сигнала распространения переноса на элементе 2ИЛИ, входы которого подключены ко входам пары старших разрядов суммируемых чисел, у выходного элемента добавлен вход, объединенный операцией 2И с выходом функции nИЛИ, этот вход подключен к выходу n-го формирователя сигнала распространения переноса.

Таким образом, отличительными признаками изобретения является выполнение формирователей сигналов возникновения переноса и формирователей сигналов распространения переноса, а также выполнение и связи выходного элемента.

Указанное выполнение схемы ускоренного переноса позволяет повысить разрядность без увеличения количества логических каскадов в критическом тракте распространения сигнала переноса, избежав тем самым ухудшения быстродействия.

Проведенные патентные исследования подтвердили новизну изобретения, а также показали, что в литературе отсутствуют данные, указывающие на влияние отличий патентуемого изобретения на достижение технического результата. Поэтому следует считать, что патентуемое изобретение соответствует критериям новизны и изобретательского уровня.

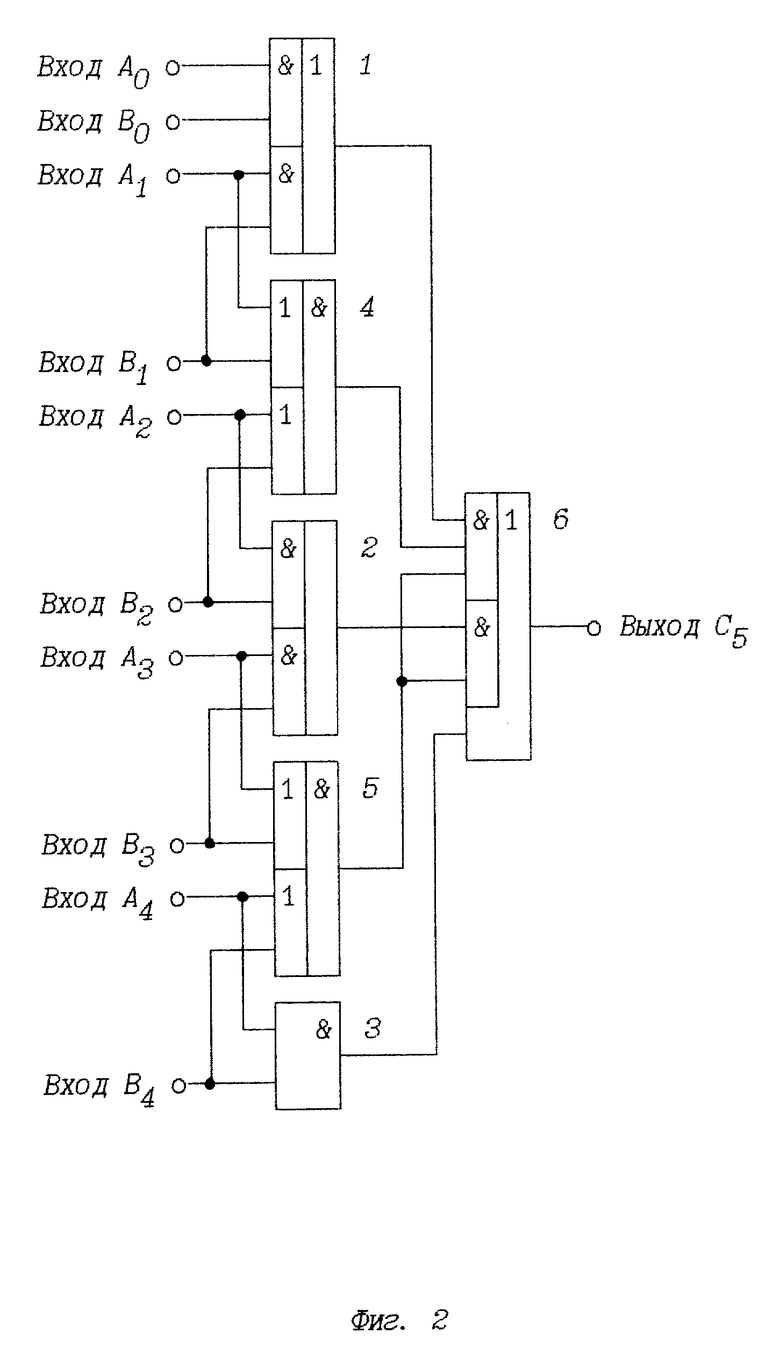

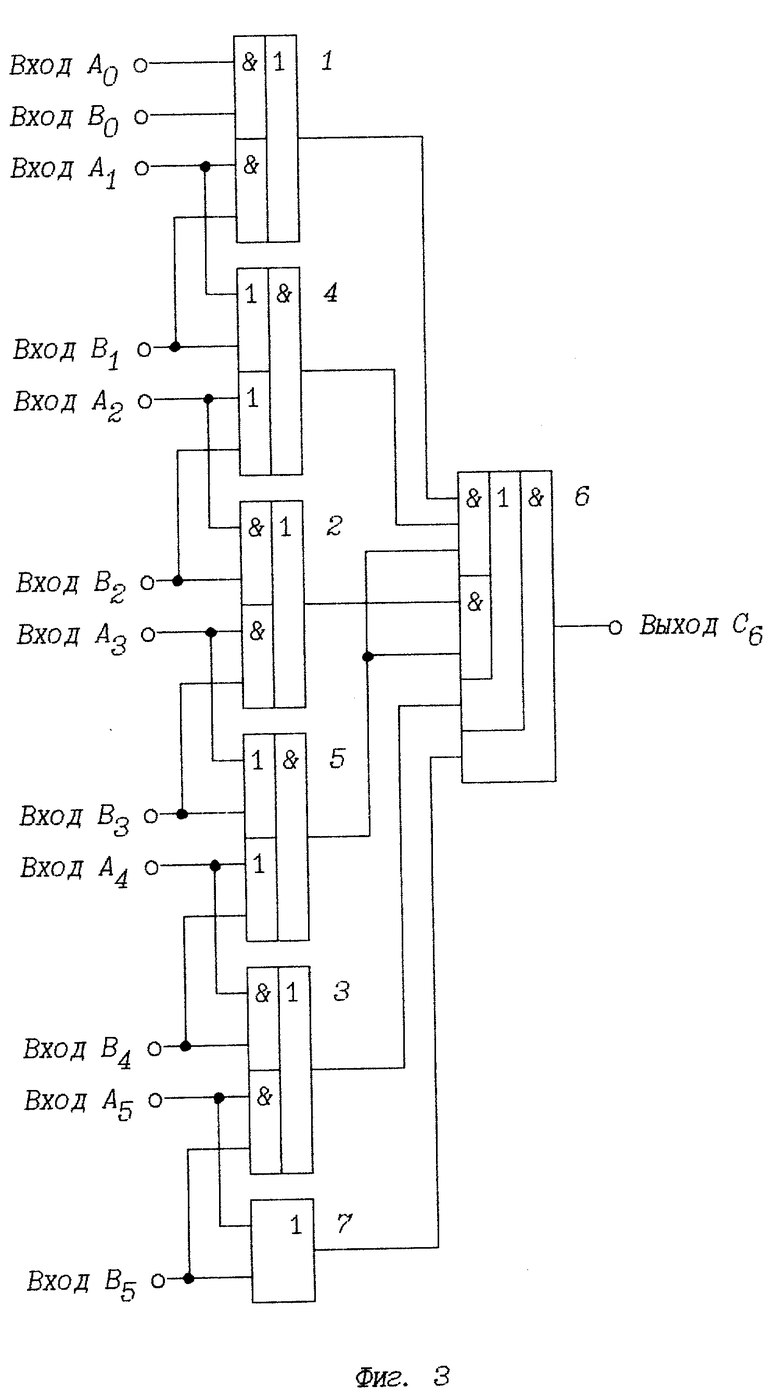

Изобретение поясняется чертежами, на которых изображены функциональные электрические схемы трехразрядного аналога изобретения с элементом 3И-2И-3ИЛИ на выходе - фиг. 1 и варианты патентуемой схемы ускоренного переноса с аналогичными выходными элементами разрядностью пять - фиг. 2 и шесть - фиг. 3.

Схема ускоренного переноса из пяти разрядов содержит с первого по третий формирователи 1 - 3 сигналов возникновения переноса, первый и второй формирователи 4 и 5 сигналов распространения переноса и выходной элемент 6 3И-2И-3ИЛИ, у которого первые входы в группах объединений 3И, 2И и внешний вход функции 3ИЛИ подключены соответственно к выходам с первого по третий формирователей 1 - 3 сигналов возникновения переноса, второй вход в группе объединения 3И соединен с выходом первого формирователя 4 сигнала распространения переноса, а третий вход в группе объединения 3И и второй вход в группе объединения 2И подключены к выходу второго формирователя 5 сигнала распространения переноса, выход элемента 6 является выходом сигнала переноса C5. Первый и второй формирователи 1 и 2 сигналов возникновения переноса представляют собой элементы 2И-2И-2ИЛИ, входы каждой пары объединений по И которых подключены ко входам пар разрядов суммируемых чисел A0 и B0, A1 и B1, A2 и B2, A3 и B3 соответственно, третий формирователь 3 сигнала возникновения переноса выполнен на элементе 2И, входы которого подключены ко входам разрядов A4 и B4 суммируемых чисел. Формирователи 4, 5 сигналов распространения переноса представляют собой элементы 2ИЛИ-2ИЛИ-2И, входы каждой пары объединений по ИЛИ которых подключены ко входам пар разрядом A1 и B1, A2 и B2, A3 и B3, A4 и B4 соответственно.

Работу устройства описывает логическое выражение

C5= A0B0(A1+B1)(A2+B2)(A3+B3)(A4+B4) + A1B1(A2+B2)(A3+B3)(A4+B4) + A2B2(A3+B3)(A4+B4) + A3B3(A4+B4) + A4B4. (1)

Его можно представить в виде логической суммы трех выражений

(A0B0 + A1B1)(A1 + B1)(A2 + B2)(A3 + B3)(A4 + B4), (2)

(A2B2 + A3B3)(A3 + B3)(A4 + B4), (3)

A4B4, (4)

первое из которых (2) формирует элемент 6 с помощью логического умножения трех сигналов с выходов формирователей 1, 4 и 5, соответствующих выражениям A0B0 + A1B1, (A1 + B1)(A2 + B2) и (A3 + B3)(A4 + B4), второе выражение (3) - с помощью логического умножения двух сигналов с выходов формирователей 2 и 5, соответствующих выражениям A2B2 + A3B3 и (A3 + B3)(A4 + B4). Выражение (4) соответствует сигналу на выходе формирователя 3. Логическое сложение выражений (2), (3) и (4) выполняет элемент 6.

Схема ускоренного переноса из шести разрядов отличается от пятиразрядной наличием третьего формирователя 7 сигнала распространения переноса, представляющего собой элемент 2ИЛИ, входы которого подключены к паре разрядов A5 и B5, и выполнением третьего формирователя 3 сигнала возникновения переноса на элементе 2И-2И-2ИЛИ, входы каждой пары объединений по И которого подключены ко входам пар разрядов A4 и B4, A5 и B5. Выходной элемент 6 выполняет функцию 3И-2И-3ИЛИ-2И, внешний вход завершающей функции 2И которого подключен к выходу третьего формирователя 7 сигнала распространения переноса.

Описывающее работу шестиразрядного устройства выражение

C6=A0B0(A1+B1)(A2+B2)(A3+B3)(A4+B4)(A5 + B5) + A1B1(A2+B2)(A3+B3)(A4+B4)(A5 + B5) + A2B2(A3+B3)(A4+B4)(A5+B5) + A3B3(A4+B4)(A5+B5) + A4B4(A5+B5) + A5B5. (5)

может быть преобразовано к виду

C6 = [(A0B0+ A1B1)(A1 + B1)(A2 + B2)(A3 + B3)(A4 + B4) + (A2B2 + A3B3)(A3 + B3)(A4 + B4) + (A4B4 + A5B5)](A5 + B5). (6)

Выходной элемент 6 формирует выражение (6), выполняя конъюнкцию трех выходных сигналов формирователей 1, 4 и 5, соответствующих формулам A0B0 + A1B1, (A1 + B1)(A2 + B2) и (A3 + B3)(A4 + B4), конъюнкцию двух сигналов с выходов формирователей 2 и 5, описываемых выражениями A2B2 + A3B3 и (A3 + B3)(A4 + B4), а затем дизъюнкцию результатов логических умножений с выходным сигналом формирователя 3 - A4B4 + A5B5 и конъюнкцию результата дезъюнкции с выходным сигналом формирователя 7 - A5 + B5.

Таким образом, данное техническое решение обеспечивает повышение разрядности схемы ускоренного переноса без увеличения количества каскадов в критическом тракте благодаря формированию сигналов возникновения и распространения переноса соответствующими элементами устройства по состояниям сразу двух пар разрядов суммируемых чисел.

| название | год | авторы | номер документа |

|---|---|---|---|

| СХЕМА УСКОРЕННОГО ПЕРЕНОСА (ВАРИАНТЫ) | 1999 |

|

RU2155371C1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ЗАПИСИ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1994 |

|

RU2097843C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1995 |

|

RU2101785C1 |

| ПРЕОБРАЗОВАТЕЛЬ ДЛИТЕЛЬНОСТЬ-КОД | 2001 |

|

RU2210097C2 |

| БАЗОВЫЙ МАТРИЧНЫЙ КРИСТАЛЛ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1992 |

|

RU2089012C1 |

| СПОСОБ ИЗМЕРЕНИЯ ТОЛЩИНЫ ОСТАТОЧНЫХ ПЛЕНОК В ОКНАХ МАЛЫХ РАЗМЕРОВ | 2000 |

|

RU2193158C2 |

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ ЭСЛ-КМОП | 1994 |

|

RU2097914C1 |

Изобретение относится к электронике и предназначено для использования в сумматорах чисел в двоичном представлении. Технический результат заключается в повышении разрядности схемы ускоренного переноса без увеличения количества каскадов в критическом тракте распространения сигнала переноса, снижающего быстродействие устройства. Технический результат достигается за счет выполнения формирователей сигналов возникновения переноса на элементах 2И-2И-2ИЛИ и формирователей сигналов распространения переноса на элементах 2ИЛИ-2ИЛИ-2И, а также за счет изменения выполнения выходного элемента и его связей, обеспечивающих формирование сигналов возникновения и распространения переноса формирователями сигналов возникновения переноса и формирователями сигналов распространения переноса по состояниям двух пар разрядов суммируемых чисел. 2 с. п. ф-лы, 3 ил.

| КИНОСИТА К | |||

| и др | |||

| Логическое проектирование СБИС | |||

| - М.: Мир, 1988, с.69, рис.2.27 и 2.28 | |||

| RU 94041149 A1, 27.09.1996 | |||

| Схема формирования переносов сумматора | 1988 |

|

SU1624443A1 |

| JP 04299733 A, 22.10.1992 | |||

| DE 3507508 A1, 01.08.1985. | |||

Авторы

Даты

2000-05-20—Публикация

1999-01-14—Подача