Изобретение относится к электронике и предназначено для использования в интегральных микросхемах оперативных запоминающих устройств.

Известны оперативные запоминающие устройства [1] для работы которых в режиме записи информации на соответствующие входы необходимо подавать импульсы записи, временные позиции и длительность которых строго регламентированы с целью обеспечения надежной работы запоминающих устройств. Это приводит к усложнению временных диаграмм работы микросхемы, затрудняющему их использование в аппаратуре при максимальной частоте обращения.

Данный недостаток оперативных запоминающих устройств полностью устраняется введением в их состав формирователя импульсов записи, управляемого, например, внешними тактовыми сигналами, синхронизирующими вход микросхемы. Формируемые внутри оперативного запоминающего устройства импульсы записи обладают необходимыми для нормальной работы временными характеристиками, задаваемыми конструктивными параметрами элементов микросхемы, определяемыми при проектировании.

В качестве такого формирователя может быть использовано известное устройство [2] По технической сущности это устройство наиболее близко к данному изобретению.

Наиболее близкий аналог содержит первый D-триггер с инверсией на входе D данных, второй D-триггер с инверсией на входе C синхронизации, линию задержки и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход первого D-триггера подключен к входу D второго D-триггера, выход которого соединен с входом линии задержки, входом D первого D-триггера и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу линии задержки, а выход является выходом формируемых импульсов. Входы C синхронизации первого и второго D-триггеров объединены и являются входом тактовых сигналов.

Этот формирователь импульсов работает следующим образом.

При переключении сигнала на входе тактовых сигналов с уровня нуля на уровень единицы, соответствующий переднему фронту тактового импульса, D-триггер устанавливается в состояние, противоположное фиксируемому в этот момент во втором D-триггере. По заднему фронту тактового импульса, соответствующего переключению тактового сигнала с уровня единицы на уровень нуля, первый D-триггер переходит в режим хранения, а второй D-триггер переключается в противоположное состояние. Фронт выходного сигнала второго D-триггера поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, в это время на его втором входе, благодаря действию линии задержки, сохраняется прежний уровень. Различие логических уровней на входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ приводит к переключению его выходного уровня из нуля в единицу, что соответствует переднему фронту формируемого импульса записи. Уровень единицы на выходе формирователя сохраняется в течение времени, необходимого для прохождения через линию задержки фронта сигнала с выхода второго D-триггера. По истечении времени задержки на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается такой же уровень, как на первом входе, и его выходной сигнал переключается в логический нуль, формируя задний фронт импульса записи на выходе формируемых импульсов.

Недостатком описанного устройства является отсутствие конструктивной обусловленности длительности формируемых импульсов записи реальными процессами переключения элементов памяти и распространения сигналов в тракте записи информации, продолжительность которых меняется при воздействии различных производственных и эксплуатационных факторов. Это затрудняет достижение при проектировании оптимальной длительности импульсов записи, одновременно обеспечивающей максимальное быстродействие и достаточную надежность работы оперативного запоминающего устройства в режиме записи информации.

Задачей изобретения является устранение данного недостатка.

Поставленная задача решается тем, что в формирователе импульсов записи оперативного запоминающего устройства, содержащем линию задержки, определяющую длительность формируемых импульсов, линия задержки состоит из эквивалента тракта записи информации запоминающего устройства и элемента памяти, идентичного элементу накопителя информации запоминающего устройства, причем вход эквивалента является входом линии задержки, а его выход соединен с входом записи информации памяти, выход считывания которого является выходом линии задержки.

Указанное выполнение формирователя импульсов записи оперативного запоминающего устройства позволяет посредством введения новых признаков достичь равенства времени распространения сигналов в линии задержки, определяющей длительность формируемых импульсов записи, реальному времени, необходимому для изменения состояния выбранного элемента памяти под воздействием распространяемых в накопителе информационных сигналов, и сохранения этого равенства в условиях дестабилизирующих воздействий, благодаря конструктивной эквивалентности элементов линии задержки и накопителя информации оперативного запоминающего устройства.

По сравнению с аналогами в устройстве впервые используются эквивалент тракта записи информации и элемент памяти оперативного запоминающего устройства в составе линии задержки, что позволяет получить новый технический результат.

Проведенные патентные исследования подтвердили новизну изобретения, а также показали, что в литературе отсутствуют данные, указывающие на влияние отличий патентуемого изобретения на достижение технического результата. Поэтому следует считать, что патентуемое изобретение соответствует критериям новизны и изобретательского уровня.

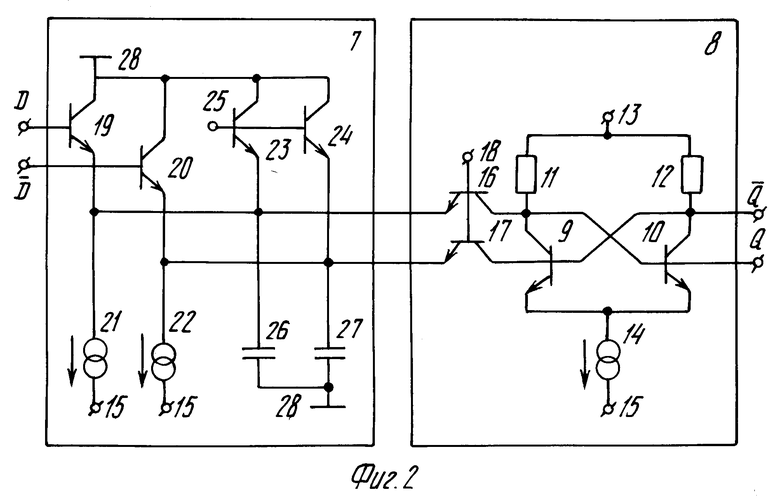

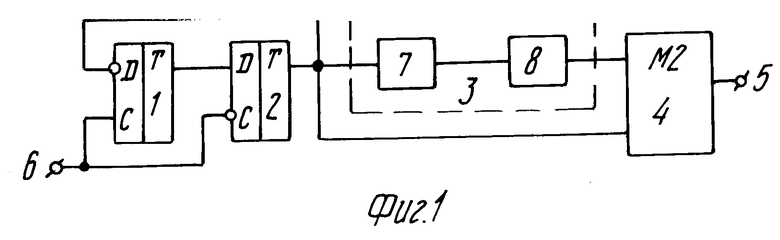

На фиг. 1 изображена структурная схема варианта реализации формирователя импульсов записи оперативного запоминающего устройства; на фиг. 2 пример схемотехнического исполнения линий задержки в оперативном запоминающем устройстве ЭСЛ-типа.

Формирователь импульсов записи оперативного запоминающего устройства содержит первый D-триггер 1 с инверсией на входе D данных, второй D-триггер 2 с инверсией на входе C синхронизации, линию 3 задержки и элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, имеет выход 5 формируемых импульсов и вход 6 тактовых сигналов. Линия 3 задержки состоит из эквивалента 7 тракта записи информации запоминающего устройства и элемента 8 памяти, идентичного элементу накопителя информации запоминающего устройства. Выход D-триггера 1 подключен к входу D данных D-триггера 2, выход которого соединен с входом эквивалента 7 тракта записи информации запоминающего устройства, входом D данных D-триггера 1 и первым входом элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу считывания элемента 8 памяти, а выход является выходом 5 формируемых импульсов. Выход эквивалента 7 соединен с входом записи информации элемента 8 памяти. Входы C синхронизации D-триггеров 1 и 2 объединены и являются входом 6 тактовых сигналов.

Формирователь импульсов работает следующим образом.

При переключении сигнала на входе 6 с уровня нуля на уровень единицы, соответствующий переднему фронту тактового импульса, D-триггер 1 устанавливается в состояние, противоположное состоянию, фиксируемому в этот момент в D-триггере 2. По заднему фронту тактового импульса, соответствующего переключению тактового сигнала с уровня единицы на уровень нуля, D-триггер 1 переходит в режим хранения, а D-триггер 2 переключается в противоположное состояние. Фронт выходного сигнала D-триггера 2 поступает на первый вход элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, в это время на его втором входе, благодаря действию линии 3 задержки сохраняется прежний уровень. Различие логических уровней на входах элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ приводит к переключению его выходного уровня из нуля в единицу, что соответствует переднему фронту формируемого на выходе 5 импульса записи. Уровень единицы на выходе 5 формирователя сохраняется в течение времени, необходимого для прохождения через эквивалент 7 тракта записи информации запоминающего устройства и переключения элемента 8 памяти в противоположное состояние. По истечении этого времени на втором входе элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается такой же уровень, как на его первом входе, и сигнал на выходе 5 переключается в логический нуль, формируя задний фронт импульса записи.

В течение всего времени присутствия на выходе 5 уровня логической единицы накопитель информации оперативного запоминающего устройства будет находиться под воздействием информационного сигнала записи, продолжительность которого оказывается достаточной для его распространения и завершения вызываемого им переключения выбранного для записи элемента накопителя информации в требуемое состояние. Благодаря конструктивной эквивалентности элементов 7 и 8 линии 3 задержки соответствующим элементам накопителя информации оперативного запоминающего устройства достигается равенство времени распространения сигналов в линии 3 задержки, определяющей длительность формируемых импульсов записи, реальной продолжительности процесса записи информации в условиях дестабилизирующих воздействий различных производственных и эксплуатационных факторов, в чем и состоит технический результат изобретения.

Изобретение может быть использовано в оперативном запоминающем устройств, содержащем накопитель информации, описанный в патенте США N 3.675.218, НПК 340/173 FF, опублик. 1972 г.

В данном примере (фиг. 2), элемент 8 памяти состоит из первого и второго ключевых транзисторов 9 и 10, соединенных двумя перекрестными связями база - коллектор, первого и второго нагрузочных резисторов 11, 12, первые выводы которых соединены с шиной 13 первого напряжения смещения, а вторые выводы соответственно подключены к коллекторам первого и второго ключевых транзисторов 9 и 10, источника 14 тока хранения, первый вывод которого подключен к первой шине 15 питания, а второй вывод соединен с эмиттерами транзисторов 9, 10, первого и второго транзисторов 16, 17 записи, коллекторы которых подключены к коллекторам первого и второго ключевых транзисторов 9, 10 соответственно, базы соединены с шиной 18 второго напряжения смещения, а эмиттеры образуют парафазный вход записи информации элемента 8 памяти.

Эквивалент 7 тракта записи состоит из первого и второго транзисторов 19, 20 управления, первого и второго источников 21, 22 тока записи, первые выводы которых соединены с первой шиной 15 питания, а вторые выводы соответственно подключены к эмиттерам транзисторов 19, 20 и являются парафазным выходом эквивалента 7, базы транзисторов 19, 20 являются парафазным входом эквивалента 7, первого и второго нагрузочных транзисторов 23 и 24, базы которых соединены с шиной 25 третьего напряжения смещения, а коллекторы вместе с коллекторами транзисторов 19, 20 соединены с второй шиной 28 питания, первого и второго нагрузочных конденсаторов 26, 27, первые выводы которых соединены с шиной 28, а вторые выводы соответственно подключены к эмиттерам транзисторов 19, 23 и к эмиттерам транзисторов 20, 24.

Линия 3 задержки, состоящая из элементов 7 и 8 описанной конфигурации работает следующим образом.

Уровень напряжения на шине 13 равен уровню напряжения смещения в накопителе информации запоминающего устройства, а уровни шин 18 и 25 соответственно равны уровням на входах выборки элементов накопителя в выбранном и невыбранном состояниях. Информационный сигнал, поступающий на базы транзисторов 19 и 20, сравнивается с уровнем на шине 18 в эмиттерно связанных парах транзисторов 19 и 23, 20 и 24, так как высокий и низкий уровни на базах транзисторов 19 и 20 лежат соответственно выше и ниже уровня шины 18 и превосходят уровень напряжения на шине 25.

Если на вход эквивалента 7 поступает логическая единица, высокий потенциал устанавливается на базе транзистора 19, а на базе транзистора 20 - низкий. При этом ток источника 21 протекает через транзистор 19 в шине 28, а ток источника 22 через транзистор 17 и резистор 12 в шине 13. Благодаря триггерным связям транзисторов 9, 10 в резисторе 12 кроме тока источника 22 - протекает ток источника 14 и напряжение на резисторе 12 превосходит напряжение на резисторе 11. Вследствие этого коллекторный потенциал транзистора 10 лежит ниже коллекторного потенциала транзистора 9, что соответствует логической единице на выходе элемента 8.

При изменении соотношения логических уровней на входах эквивалента 7, обуславливающего снижение базового потенциала транзистора 19, ток источника 21 отключается из эмиттера транзистора 19 и производит разряд емкостей конденсатора 26 и эмиттерного p-n перехода транзистора 23 до тех пор, пока потенциал на эмиттере транзистора 16 не понизится достаточно для его отпирания и полного переключения тока источника 21 в резистор 11. В это время ток, возникший в эмиттере транзистора 20 по причине повышения потенциала на его базе, заряжает емкости конденсатора 27 и эмиттерного p-n перехода транзистора 24, повышая потенциал эмиттера транзистора 17 до полного переключения тока источника 22 из транзистора 17 в транзистор 20.

По мере выключения тока источника 22 из резистора 12 и включения тока источника 21 в резистор 11, происходит изменение разности коллекторных потенциалов транзисторов 9 и 10. Приближение этой разности к нулю вызывает перераспределение тока источника 14: из эмиттера транзистора 10 он все больше ответвляется в эмиттер транзистора 9 и в момент, когда коллекторный потенциал транзистора 9 становится ниже потенциала на коллекторе транзистора 10, триггерные связи транзисторов 9 и 10 вызывают лавинообразное переключение остатка тока источника 14 в эмиттер транзистора 9, завершая процесс формирования логического нуля на выходе элемента 8.

В силу симметрии схемы линии 3 задержки обратный процесс переключения из нуля в единицу происходит аналогичным образом при взаимной перемене выполняемых действий в парах функционально одинаковых элементов.

Для достижения эквивалентности процесса прохождения логических сигналов в линии 3 задержки процессу изменения состояния выбранного элемента накопителя информации компоненты 9 12 и 16, 17 элемента 8 памяти и компоненты 19 22 эквивалента 7 тракта записи информации следует выполнить идентичными аналогичным им по функции компонентам накопителя запоминающего устройства, ток источника 14 должен быть равен току хранения, протекающему в выбранном элементе накопителя, эмиттеры транзисторов 23 и 24 эквивалентны объединенным эмиттерам транзисторов записи невыбранных элементов накопителя, имеющих общие с выбранным информационные входы, а конденсаторы 26 и 27 должны иметь емкость, равную емкости токоведущих дорожек информационных шин накопителя.

Таким образом, при выполнении определенных требований данное техническое решение обеспечивает обусловленность длительности формируемых импульсов записи реальными динамическими процессами в накопителе информации оперативного запоминающего устройства в условиях воздействия различных производственных и эксплуатационных дестабилизирующих факторов, одинаково влияющих на параметры эквивалентных компонентов накопителя и формирователя импульсов записи.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1995 |

|

RU2101785C1 |

| БАЗОВЫЙ МАТРИЧНЫЙ КРИСТАЛЛ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1992 |

|

RU2089012C1 |

| ПРЕОБРАЗОВАТЕЛЬ ДЛИТЕЛЬНОСТЬ-КОД | 2001 |

|

RU2210097C2 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ ЭСЛ-КМОП | 1994 |

|

RU2097914C1 |

| ИСТОЧНИК ОБРАЗЦОВЫХ НАПРЯЖЕНИЙ | 1993 |

|

RU2076351C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2018979C1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1991 |

|

RU2020614C1 |

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНОГО ТРАНЗИСТОРА | 1995 |

|

RU2099814C1 |

Изобретение относится к электронике и предназначено для использования в интегральных микросхемах оперативных запоминающих устройств, Задачей изобретения является достижение конструктивной обусловленности длительности формируемых импульсов записи реальными процессами переключения элементов памяти и распространения сигналов в тракте записи информации запоминающего устройства. Это достигается выполнением линии 3 задержки, определяющей длительность формируемых импульсов, в виде последовательной цепи из эквивалента 7 тракта записи информации запоминающего устройства и элемента 8 памяти, идентичного элементу накопителя информации. Кроме названных элементов на схеме устройства обозначены первый и второй D-триггеры 1 и 2, элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, выход 5 формируемых импульсов и вход 6 тактовых сигналов. 2 ил.

Формирователь импульсов записи оперативного запоминающего устройства, содержащий линию задержки, определяющую длительность формируемых импульсов, отличающийся тем, что линия задержки состоит из эквивалента тракта записи информации запоминающего устройства и элемента памяти, идентичного элементу накопителя информации запоминающего устройства, причем вход эквивалента является входом линии задержки, а его выход соединен с входом записи информации элемента памяти, выход считывания которого является выходом линии задержки.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сверхбольшие интегральные микросхемы оперативных запоминающих устройств / Под ред | |||

| Вернера В.Д | |||

| - М.: Радио и связь, 1991, с | |||

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Гитис Э.И | |||

| Преобразование информации для электронных цифровых вычислительных устройств | |||

| - М.: Энергия, 1970, с | |||

| Кулиса для фотографических трансформаторов и увеличительных аппаратов | 1921 |

|

SU213A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1997-11-27—Публикация

1994-05-23—Подача