Изобретение относится к телемеханике и вычислительной технике и может быть использовано в системах передачи и обработки дискретной информации для коррекции ошибок при пятикратном повторении сообщений.

Известны устройства для мажоритарного декодирования трехкратно дублированных сообщений при последовательном приеме (см. АС СССР 206634, 207247, 31а 7/01, 1968 г., 387521, Н 03 К 13/32, 1975 г.), содержащие два регистра сдвига и логические элементы.

Недостатком этих устройств является ограниченность функциональных возможностей, что не позволяет использовать их в адаптивных системах для широкого класса кодов с повторением.

Кроме того, известны устройства для мажоритарного декодирования (см. АС СССР 884263, Н 04 L 1/10, Н 03 К 13/32, 1981 г., 677123, H 04 L 1/10, 1979 г. , 944129, H 04 L 1/08, 1982 г., 980114, G 08 C 19/28, 1982 г., 1005151, G 08 C 25/00, 1982 г., патент РФ 1439750, Н 03 М 13/00, 1988 г., 2023348, Н 03 М 13/02, 2012134, Н 03 М 5/00, 1994 г.), содержащее регистры сдвига и логические элементы с соответствующими связями, позволяющими подвергать мажоритарной обработке три, пять и более повторений сообщения без потери промежуточных результатов.

Недостатком этих устройств является ограниченность функциональных возможностей, проявляющаяся в том, что анализируются не все возможные сочетания повторений сообщений.

Из известных устройств наиболее близким по технической сущности является устройство коррекции ошибок с расширенным набором решающих правил, описанное в патенте 2152129, Н 03 М 13/43, 2000 г.

Это устройство содержит четыре регистра сдвига, четыре переключателя, решающий блок, синхронизатор и соответствующие связи.

Недостатком этого устройства является низкая помехоустойчивость, так как, реализуя полный набор решающих правил, не учитывается сигнал "стирание" (Θ) по наиболее надежным одноименным символам многократно повторенного сообщения, что снижает помехоустойчивость устройства.

Целью настоящего изобретения является повышение помехоустойчивости устройства, которое учитывает сигнал "стирание" (Θ) по наиболее надежным одноименным символам многократно повторенного сообщения.

Поставленная цель достигается тем, что в устройство, содержащее решающий блок, выходы которого являются выходами устройства, четыре переключателя, выходы которых соединены с информационными входами одноименных регистров сдвига, синхронизатор, тактовый вход которого является тактовым входом устройства, первый - третий выходы синхронизатора соединены соответственно с объединенными первыми управляющими входами первого переключателя и первого регистра сдвига, объединенными первыми управляющими входами второго переключателя и второго регистра сдвига, объединенными первыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока, вторыми управляющими входами первого и второго переключателей, первого и второго регистров сдвига, при этом первый информационный вход решающего блока объединен с первыми информационными входами переключателей, вторые информационные входы которых одновременно связаны с соответствующими входами решающего блока и выходами регистров сдвига, установочные входы которых объединены с установочными входами устройства и установочным входом синхронизатора, четвертый выход которого соответственно соединен с объединенными третьими управляющими входами второго переключателя, второго регистра сдвига, вторыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока и первыми управляющими входами четвертого переключателя и четвертого регистра сдвига, при этом пятый выход синхронизатора одновременно подключен ко вторым управляющим входам четвертого переключателя и четвертого регистра сдвига, третьим управляющим входам третьего, первого переключателей, третьего, первого регистра сдвига, решающего блока и четвертым управляющим входам второго переключателя и второго регистра сдвига введены блок исправления стираний и детектор качества, первый и второй выходы которого соответственно соединены с первым и вторым входами блока исправления стираний, выход которого объединен с первыми информационными входами переключателей и решающего блока, третий - шестой входы блока исправления стираний подключены соответственно к выходам первого - четвертого регистров сдвига, а седьмой, девятый, одиннадцатый входы блока исправления стираний соответственно связаны с первым, третьим, пятым выходами синхронизатора, при этом восьмой, девятый входы блока исправления стираний соединены со вторым и четвертым входами синхронизатора и соответствующими управляющими входами первого переключателя и первого регистра сдвига, а вход детектора качества является информационным входом устройства.

Устройство содержит переключатели 1-4, регистры 5-8, синхронизатор 9, решающий блок 10, блок 11 исправления стираний и детектор качества 12.

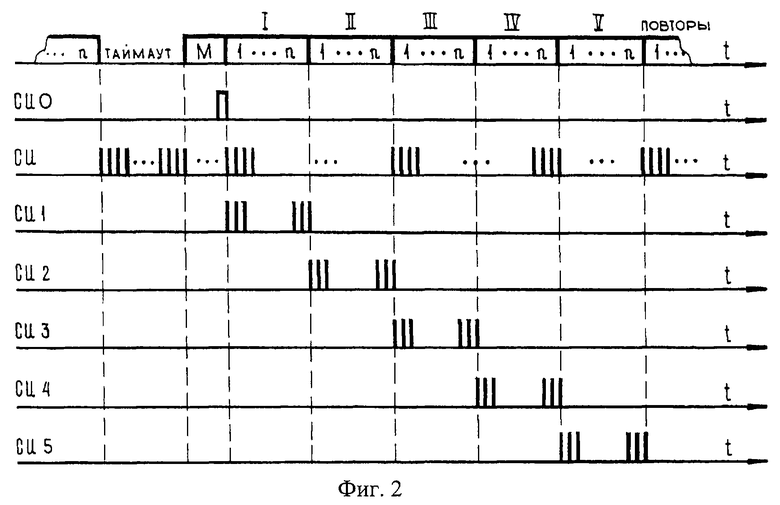

На фиг. 1 показана структурная схема устройства; на фиг.2 - временные диаграммы, поясняющие работу устройства; на фиг.3 - функциональная схема решающего блока; на фиг.4 - функциональная схема блока исправления стираний; на фиг. 5 - временная диаграмма, поясняющая принцип коррекции ошибок во втором повторе сообщения при учете сигнала "стирание".

Устройство содержит (фиг.1) первый - четвертый переключателя 1-4, первый - четвертый регистры 5-8 сдвига, синхронизатор 9, решающий блок 10, блок 11 исправления стираний и детектор 12 качества.

Переключатели 1-4 предназначены для коммутации информационных входов соответствующих регистров 5-8 сдвига. Выходы переключателей являются входами регистров.

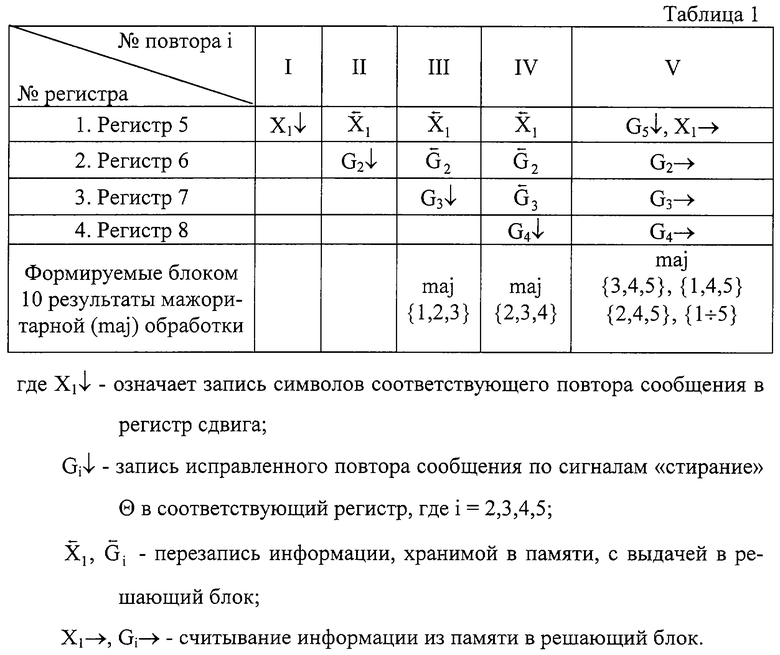

Регистры сдвига 5-8 являются стандартными элементами памяти и служат для хранения, перезаписи, выдачи информации, циркулирующей в устройстве. Распределение хранимой информации по регистрам 5-8 представлено в табл. 1.

Выходы регистров 5-8 одновременно связаны со вторыми информационными входами переключателей 1-4, соответствующими входами решающего блока 10 и третьим - шестым входом соответственно блока 11 исправления стираний.

Синхронизатор 9 обеспечивает нормальное функционирование всех элементов устройства. На фиг.2 представлена временная диаграмма работы синхронизатора. После выделения маркера цикловой синхронизации, определяющего начало кадра многократно повторенного сообщения, выделяется импульс установки элементов памяти устройства в нулевое состояние (см. фиг.2 СИО). После чего блок 9 обеспечивает пакетирование синхроимпульсов СИ, поступающих на его вход, в последовательности СИ1 ÷ СИ5. Число импульсов соответствует в пакете количеству n символов в одном повторе сообщения. Для выполнения функций такого блока уже существует большое множество технических решений, описанных в технической литературе. Например, в книге Гуров B.C., Емельянов А.Е., Етрухин Н. Н. , Осипов В. Г. "Передача дискретной информации и телеграфия". - М.: Связь, 1974. - C. 135.

Тактовый вход СИ синхронизатора 9 является тактовым входом устройства. Первый - третий выходы синхронизатора 9 соединены соответственно с объединенными первыми управляющими входами первого переключателя 1 и регистра 5, объединенными первыми управляющими входами второго переключателя 2 и второго регистра 6, объединенными первыми управляющими входами переключателя 3, регистра 7, решающего блока 10, вторыми управляющими входами 1 и 2 переключателей 5 и 6 регистров. Четвертый выход синхронизатора 9 соответственно соединен с объединенными третьими управляющими входами переключателя 2, регистра 6, вторыми управляющими входами переключателя 3, регистра 7, решающего блока 10 и первыми управляющими входами переключателя 4, регистра 8. Пятый выход блока 9 одновременно подключен ко вторым управляющим входам переключателя 4, регистра 8, третьим управляющим входам переключателей 1-3, регистров 5, 7, решающего блока 10 и четвертым управляющим входам переключателя 2 и регистра 6.

Решающий блок 10 предназначен для формирования расширенного набора решающих мажоритарных (maj) правил. На первом выходе блока 10 формируются разнесенные во времени результаты мажоритарной обработки первых трех повторов maj (X1, G2, G3) сообщения в момент приема третьего Х3 повтора и последних трех maj (G3, G4, G5) в момент приема пятого Х5 повторения. Результат maj (G2, G3, G4) обработки второго, третьего, четвертого повторений выдается на второй выход блока 10 в момент приема символов четвертого повтора Х4. На этот же выход выдается результат maj (X1, G4, G5) обработки одноименных символов первого, четвертого, пятого повторов в момент приема символов пятого повторения Х5. На третий выход блока 10 поступает результат мажоритарной обработки maj (G2, G4, G5) по приходу символов пятого повтора Х5. По четвертому выходу выдается результат мажоритарной обработки в целом по пяти повторам сообщения maj (X1, G2, G3, G4, G5).

Возможный вариант функциональной схемы блока 10 приведен на фиг.3, которая содержит логические элементы в базисе И-НЕ 10-1 ÷ 10-53.

На логических элементах 10-1 ÷ 10-3, 10-16 реализуется первое решающее правило

maj(X1, G2, G3)=X1G2+Х1G3+G2G3. (1)

Элементы 10-4 ÷ 10-6, 10-17 формируют второе правило

maj(G2, G3, G4)=G2G3+G2G4+G3G4. (2)

Элементы 10-7 ÷ 10-9, 10-18 определяют мажоритарный результат последних трех повторов из пяти, третье правило

maj(G3, G4, G5)=G3G4+G3G5+G4G5. (3)

Элементы 10-10 ÷ 10-12, 10-19 реализуют четвертое правило

maj(X1, G4, G5)=X1G4+X1G5+G4G5. (4)

Элементы 10-13 ÷ 10-15, 10-20 формируют пятое правило

maj(G2, G4, G5)=G2G4+G2G5+G4G5. (5)

Группа элементов 10-26 ÷ 10-35, 10-41, 10-42 позволяет провести мажоритарную обработку в целом по пяти повторам сообщения, шестое правило:

maj(X1, G2, G3, G4, G5)= G2G3G4+G3G4G5+G2G3G5+G2G4G5+X1G2G3+X1G3G4+Х1G4G5+Х1G2G5+X1G2G4+X1G3G5.

(6)

Остальные элементы блока 10 выполняют функции логических элементов И, ИЛИ.

Блок 11 исправления стираний содержит (фиг.4) элементы И 11-1 ÷ 11-8, 11-12 ÷ 11-23, 11-36 ÷ 11-38, элементы ИЛИ-НЕ 11-9 ÷ 11-11, Запрет 11-27 ÷ 11-32, ИЛИ 11-24 ÷ 11-26, 11-33 ÷ 11-35, 11-39.

Блок 11 исправления стираний осуществляет коррекцию ошибок по вектору стираний, т. е. вектору, отмечающему ненадежные символы принятых кодовых комбинаций, и выполняет следующие функции.

При приеме символов второго X2 повторения сообщения блок 11 производит поэлементное сравнение с символами первого X1 повтора, учитывая сигнал "стирание" (Θ) для соответствующего символа второго повторения. В случае несовпадения одноименных символов сравниваемых повторов инвертируется символ второго повтора сообщения, отмеченный сигналом Θ. Этот процесс отражен на временной диаграмме фиг. 5 и реализуется на элементах 11-2, 11-12, 11-20, 11-13, 11-39.

На третьем шаге N=3 работы устройства, когда принимаются символы третьего повтора Х3, блок 11 производит исправления ненадежного символа третьего повтора, отличного от однозначных одноименных символов в первом X1 и втором скорректированном G2 повторах, при наличии сигнала "стирание" Θ, отметившего ненадежный символ третьего повтора.

На последующих шагах работы устройства N≥4, т.е. при приеме символов четвертого Х4 и пятого Х5 повторов блок 11 производит аналогичное исправление тех символов, отмеченных сигналом Θ, у которых предшествующие одноименные символы удовлетворяют условию однозначности (R)

где N=3, 4, 5.

Работа блока 11 задана табл. 2.

Выход блока 11 исправления стираний объединен с первыми информационными входами 1-4 переключателей и решающего блока 10. Первый-второй входы блока 10 являются выходами детектора качества 12. Третий-шестой входы блока 10 подключены соответственно к выходам 5-8 регистров. Седьмой, девятый, одиннадцатый входы блока 11 соответственно связаны с первым, третьим, пятым выходами синхронизатора 9, а восьмой, десятый входы блока 11 соединены со вторым и четвертым выходами синхронизатора 9 и соответствующими управляющими входами переключателя 1 и регистра 5.

Детектор качества 12 предназначен для анализа каждого принимаемого символа кодовой комбинации Xi и выработки сигнала "стирания" Θ в том случае, если принимаемый символ не может быть отождествлен ни с "1", ни с "0". Вход детектора качества 12 является информационным входом устройства.

Примеры технической реализации детекторов качества приведены в книге: Л. П. Пуртов и др. Теория и техника передачи данных и телеграфия. - Л.: ВАС, 1973.

Устройство работает следующим образом.

Исходное состояние элементов памяти устройства нулевое, что обеспечивается установочным синхроимпульсом СИО (фиг.2). Символы первого повторения X1 сообщения из канала связи поступают на детектор 12 качества, где идентифицируются с "0" или "1", после чего проходят на первый вход блока 11, где через элемент И 11-1, открытый синхроимпульсами СИ1, элемент ИЛИ 11-39 поступают на выход блока 11. С выхода блока 11 символы первого повторения сообщения через переключатель 1, открытый синхроимпульсами СИ1, записываются в регистр 5 с частотой следования СИ1.

Таким образом, по окончанию приема первого повторения сообщения оно оказывается записанным в регистре сдвига 5.

Синхронизатор 9, отсчитав n синхроимпульсов, выдаст на втором выходе пачку синхроимпульсов СИ2, которая управляет работой блоков устройства. Выталкиваемые синхроимпульсами СИ2 из регистра 5 символы первого повтора поступают на третий вход блока 11. Одновременно на первый вход блока 11 через детектор 12 качества поступает информация из канала связи, а на второй вход блока 11 поступает сигнал Θ, вырабатываемый детектором качества 12. В блоке 11 элементы И 11-2, 11-20, сумматор по модулю два 11-12, 11-3 реализуют алгоритм исправления (см. фиг.5) ненадежного символа второго повтора. Скорректированный второй повтор G2 через открытый СИ2, переключатель 2 записывается в регистр 6. А символы первого повтора через переключатель 1 переписываются в регистр 5. Состояние регистров 7, 8 нулевое.

При приеме третьего повторения сообщения происходит считывание информации первого X1 и второго G2 повторов, хранимых соответственно в регистрах 5 и 6, на третий и четвертый входы блока 11, на первый вход которого поступают символы третьего Х3 повтора. Далее последние обрабатываются блоком 11 с учетом сигнала "стирания", поступающего на второй вход блока 11, по изложенному алгоритму условия (7), (8). При этом в работе блока 11 из всех возможных состояний одноименных символов двух повторов участвуют только совпавшие символы X1=G2.

В том случае, если X1=G2=1 (N=3 табл. 2) и присутствует сигнал "стирание" Θ=1, соответствующий ненадежному символу третьего повторения, то срабатывают элементы И 11-3, 11-15. Сигнал с выхода элемента И 11-15 через ИЛИ 11-24 запретит прохождение символа Х3 через Запрет 11-28 и пройдет через Запрет 11-27, ИЛИ 11-33, И 11-36, 11-39 на выход блока 11.

В том случае, когда X1= G2=0 и Θ=1, то срабатывает цепочка элементов 11-9, 11-14, 11-21, 11-24, 11-28, 11-33, 11-36, 11-39, препятствуя прохождению соответствующего символа Х3 через Запрет 11-28. Вследствие этого, отмеченный стиранием Θ символ третьего повтора становится нулевым.

Скорректированные символы третьего повтора G3 через переключатель 3 записываются в регистр 7, одновременно поступая на первый вход блока 10, на второй и третий входы которого считываются с регистров 5, 6 символы первого X1 и второго G2 повторения, одновременно перезаписываясь в свои регистры через переключатели 1, 2.

Символы первых трех повторений в блоке 10 проходят через мажоритарный элемент, реализующий критерий 2х3, с выхода которого формируемый результат мажоритарной обработки первого решающего правила (1) выдается на первый выход устройства. Работой всех блоков устройства при приеме символов третьего повтора управляют синхроимпульсы СИ3 (фиг.2).

При приеме четвертого повтора происходит считывание символов первых трех повторов с регистров 5-7 (см. табл. 1) с помощью синхроимпульсов СИ4. Считываемые символы поступают на соответствующие входы блока 11, на первый вход которого поступают символы четвертого Х4 повтора. В блоке 11 с учетом сигнала Θ по наиболее надежным одноименным предшествующим символам (см. табл. 2, условие 7) осуществляется коррекция ошибок в символах четвертого повторения G4.

Скорректированные символы четвертого повтора G4 через переключатель 4 записываются в регистр 8, одновременно поступая на первый вход решающего блока 10, на третий, четвертый входы которого считываются с регистров 6, 7 символы второго G2 и третьего G3 повторений, скорректированных сигналом Θ, одновременно перезаписываясь через переключатели 2, 3 в свои регистры.

Символы второго, третьего, четвертого повторений в блоке 10 проходят через мажоритарный элемент, реализующий критерий 2х3, формирующий второе (2) решающее правило. Этот результат выдается на выход устройства. Управление работой блоков осуществляется синхроимпульсами СИ4 (фиг.2).

При приеме пятого повтора Х5 формируемые блоком 9 синхроимпульсы СИ3 выталкивают хранимый в регистрах 5-8 результат X1, G2, G3, G4 на соответствующие входы блока исправления стираний 11. На первый вход блока 11 поступают символы Х5 пятого повтора. В блоке 11 с учетом сигнала Θ, поступающего по второму входу с выхода детектора качества 12, по наиболее надежным предшествующим символам (см. табл. 2 условие (7)) осуществляется коррекция ошибок в символах пятого повторения.

Скорректированные символы пятого повтора G5 через переключатель 1 записываются в регистр 5, для возможной обработки в следующем цикле, если кадр сообщения имеет большее N>5 число повторов. Одновременно G5 вместе с X1, G2, G3, G4 поступают в решающий блок 10, где реализуется расширенный набор решающих правил (3)÷(6) и выдается на соответствующие выходы устройства. Синхроимпульсы СИ5 управляют работой устройства, на этом шаге N=5.

Достоверность достижения цели изобретения подтверждается следующими данными. Если в известном устройстве вероятность искажения единичного символа в итоговой кодовой комбинации оценивается величиной Pэ1 = mР0 m, где m - показатель нечетного числа повторов N=2m-1, m=3; P0 - вероятность искажения единичного символа кодовой комбинации, то в предлагаемом устройстве:

Pэ2 ≅ (2m-1)•P

где PT - вероятность трансформации символа при отсутствии Θ.

В этом случае потери информации можно оценить выражением (В.И. Ключко. Методы и средства защиты информации от ошибок в АСУ. МО СССР, 1980. - 255 с. ):

PП = 1-(1-Pэ)n ≅ n•Pэ.

Тогда, если Р0=10-2 (канал низкого качества), Рт=2•10-2, m=3, то

Рп1=n•(2m-l)•Р0 m+1, а Рп2=n•(2m-1)•Р0 m+1•PT.

Следовательно, потери информации снижаются в

Таким образом, при приеме пяти повторений сообщения устройство реализует расширенный набор решающих правил. При этом учет сигнала "стирание" Θ позволяет исправить определенную долю ошибок в повторе по наиболее надежным предшествующим символам, что снижает общее число ошибок в принимаемом сообщении. Это облегчает коррекцию ошибок расширенным набором решающих правил, тем самым повышается помехоустойчивость.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

| Модифицированное устройство коррекции ошибок | 2016 |

|

RU2635253C1 |

| Модифицированное устройство коррекции ошибок с учетом сигнала стирания | 2019 |

|

RU2711035C1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ | 1998 |

|

RU2152129C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК ПРИ МНОГОКРАТНОМ ПОВТОРЕНИИ СООБЩЕНИЙ | 1991 |

|

RU2023348C1 |

| Устройство для приема и мажоритарного декодирования информации | 1988 |

|

SU1562977A2 |

| Устройство для приема и мажоритарного декодирования информации | 1987 |

|

SU1439750A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК ПРИ МНОГОКРАТНОМ ПОВТОРЕНИИ СООБЩЕНИЙ | 1991 |

|

RU2012134C1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1981 |

|

SU1005151A2 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1987 |

|

SU1453599A2 |

Изобретение относится к области телемеханики и вычислительной техники и может быть использовано в системах передачи и обработки дискретной информации для коррекции ошибок при пятикратном повторении сообщений. Техническим результатом является повышение помехоустойчивости, которое учитывает сигнал стирания. Технический результат достигается тем, что устройство коррекции ошибок с расширенным набором решающих правил и учетом сигнала стирания содержит решающий блок, четыре переключателя, четыре регистра сдвига и синхронизатор, отличающийся тем, что, с целью повышения помехоустойчивости устройства, в него дополнительно введены детектор качества для анализа каждого принимаемого символа кодовой комбинации и выработки сигнала стирания и блок исправления стираний, учитывающий сигнал "стирания" по наиболее надежным одноименным символам многократного повторения сообщения. 5 ил.

Устройство коррекции ошибок с расширенным набором решающих правил и учетом сигнала стирания, содержащее решающий блок, выходы которого являются выходами устройства, четыре переключателя, выходы которых соединены с информационными входами одноименных регистров сдвига, синхронизатор, тактовый вход которого является тактовым входом устройства, первый-третий выходы синхронизатора соединены соответственно с объединенными первыми управляющими входами первого переключателя и первого регистра сдвига, объединенными первыми управляющими входами второго переключателя и второго регистра сдвига, объединенными первыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока, вторыми управляющими входами первого и второго переключателей, первого и второго регистров сдвига, при этом первый информационный вход решающего блока объединен с первыми информационными входами переключателей, вторые информационные входы которых одновременно связаны с соответствующими входами решающего блока и выходами регистров сдвига, установочные входы которых объединены с установочными входами устройства и установочным входом синхронизатора, четвертый выход которого соответственно соединен с объединенными третьими управляющими входами второго переключателя, второго регистра сдвига, вторыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока и первыми управляющими входами четвертого переключателя и четвертого регистра сдвига, при этом пятый выход синхронизатора одновременно подключен ко вторым управляющим входам четвертого переключателя и четвертого регистра сдвига, третьим управляющим входам третьего, первого переключателей, третьего, первого регистров сдвига, решающего блока и четвертым управляющим входам второго переключателя и второго регистра сдвига, отличающееся тем, что в него введены блок исправления стираний и детектор качества, первый и второй выходы которого соединены соответственно с первым и вторым входами блока исправления стираний, выход которого объединен с первыми информационными входами переключателей и решающего блока, третий - шестой входы блока исправления стираний подключены соответственно к выходам первого - четвертого регистров, седьмой, девятый, одиннадцатый входы блока исправления стираний соответственно связаны с первым, третьим, пятым выходами синхронизатора, а восьмой, десятый входы блока исправления стираний соединены со вторым и четвертым выходами синхронизатора и соответствующими управляющими входами первого переключателя и первого регистра, вход детектора качества является информационным входом устройства.

| Устройство для исправления стираний | 1986 |

|

SU1399893A1 |

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1446695A1 |

| Устройство для исправления стираний | 1989 |

|

SU1647916A2 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ | 1998 |

|

RU2152129C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК ПРИ МНОГОКРАТНОМ ПОВТОРЕНИИ СООБЩЕНИЙ | 1991 |

|

RU2023348C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ КОДА РИДА - СОЛОМОНА | 1991 |

|

RU2007040C1 |

| US 3949208, 06.04.1976 | |||

| Центробежный смеситель | 1982 |

|

SU1101288A2 |

Авторы

Даты

2003-07-20—Публикация

2001-03-06—Подача