Изобретение относится к телемеханике и вычислительной технике и может быть использовано в системах передачи и обработки дискретной информации для коррекции ошибок при пятикратном повторении сообщений.

Известны устройства для мажоритарного декодирования трехкратно дублированных сообщений при последовательном приеме (см. А. с. СССР N 206634, 207247, 3la 7/01, 1968 г., N 387521, H 03 K 13/32, 1975 г.), содержащие два регистра сдвига и логические элементы. Недостатком этих устройств является ограниченность функциональных возможностей, что не позволяет использовать их в адаптивных системах для широкого класса кодов с повторением.

Кроме того, известны устройства для мажоритарного декодирования (см. А. с. СССР N 884263 H 04 1/10, H 03 K 13/32 1981 г., 677123 H 04 L 1/10 1979 г. , 944129 H 04 L 1/08 1982 г., 980114 G 08 C 19/28 1982 г., 1005151 G 08 C 25/00 1982 г., патент РФ 2023348 H 03 M 13/02, 2012134 H 03 M 5/00 1994 г.), содержащее регистры сдвига и логические элементы с соответствующими связями, позволяющие подвергать мажоритарной обработке три, пять и более повторений сообщения без потери промежуточных результатов. Недостатком этих устройств является ограниченность функциональных возможностей, проявляющаяся в том, что анализируются не все возможные сочетания повторений сообщений.

Из известных устройств наиболее близким по технической сущности является устройство первичной мажоритарной обработки с расширенным набором решающих правил, описанное в А. с. СССР N 1439750 H 03 M 13/00, 1988 г.

Это устройство содержит кодопреобразователь, три переключателя, три регистра сдвига, решающий блок, синхронизатор и соответствующие связи.

Недостатком этого устройства является низкая помехоустойчивость, так как, подвергая мажоритарной обработке первые три, последние три, средние три и в целом пять повторений сообщений, устройство не исправляет все возможные трехкратные ошибки в одноименных символах пяти повторений.

Целью настоящего изобретения является повышение помехоустойчивости.

Поставленная цель достигается тем, что в устройство, содержащее решающий блок, выходы которого являются выходами устройства, три переключателя, выходы которых соединены с информационными входами одноименных регистров сдвига, синхронизатор, тактовый вход которого является тактовым входом устройства, первый-третий выходы синхронизатора соединены соответственно с объединенными первыми управляющими входами первого переключателя и первого регистра сдвига, объединенными первыми управляющими входами второго переключателя и второго регистра сдвига, объединенными первыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока, вторыми управляющими входами первого и второго переключателей, первого и второго регистров сдвига, введен четвертый регистр сдвига, вход которого является выходом четвертого переключателя, первый информационный вход которого объединен с первыми информационными входами переключателей, решающего блока и является информационным входом устройства, вторые информационные входы переключателей одновременно связны с соответствующими выходами регистров сдвига и входами решающего блока, установочные входы регистров сдвига объединены с установочным входом устройства и установочным входом синхронизатора, четвертый выход которого соответственно соединен с объединенными третьими управляющими входами второго переключателя, второго регистра сдвига, вторыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока и первыми управляющими входами четвертого переключателя и четвертого регистра сдвига, при этом пятый выход синхронизатора одновременно подключен ко вторым управляющим входам четвертого переключателя и четвертого регистра сдвига, третьим управляющим входам третьего, первого переключателей, третьего, первого регистров сдвига, решающего блока и четвертым управляющим входам второго переключателя и второго регистра сдвига.

Этим достигается анализ и мажоритарная обработка всех групп, состоящих из трех повторений (X1 X2X3), (X2Х3X4), (X3X4X5), где X1 - одноименные символы соответствующего i-го повтора (где i= 1,2,3,4,5), которые входят в кадр пятикратного повторения сообщения. Кроме того, анализируются сочетания (X1X4X5), (X2X4X5) и пяти повторений в целом X1X2X3X4X5). Теперь появляется возможность исправить дополнительную долю трехкратных ошибок в одноименных символах пятикратно повторенного сообщения. Известное устройство позволяло исправить только семь комбинаций из десяти возможных (00111, 01011, 10011, 10101, 11001, 11010, 11100, где 1 означает искажение одноименного символа). Предлагаемое устройство дополнительно к известным комбинациям корректирует оставшиеся три из десяти (01101, 01110, 10110).

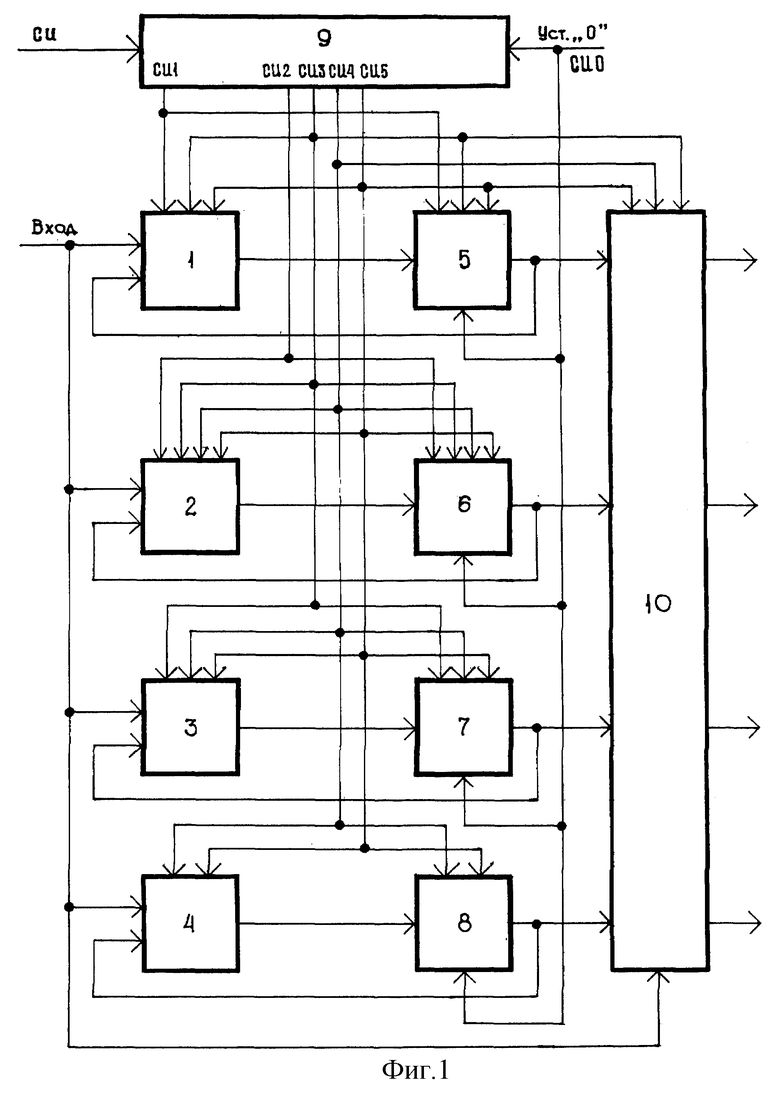

На фиг. 1 представлена структурная схема устройства коррекции ошибок с расширенным набором решающих правил. Устройство содержит переключатели 1-4, регистры cдвига 5-8, синхронизатор 9, решающий блок 10.

Переключатели 1-4 предназначены для коммутации информационных входов регистров сдвига 5-8. Выходы переключателей являются соответствующими входами регистров сдвига.

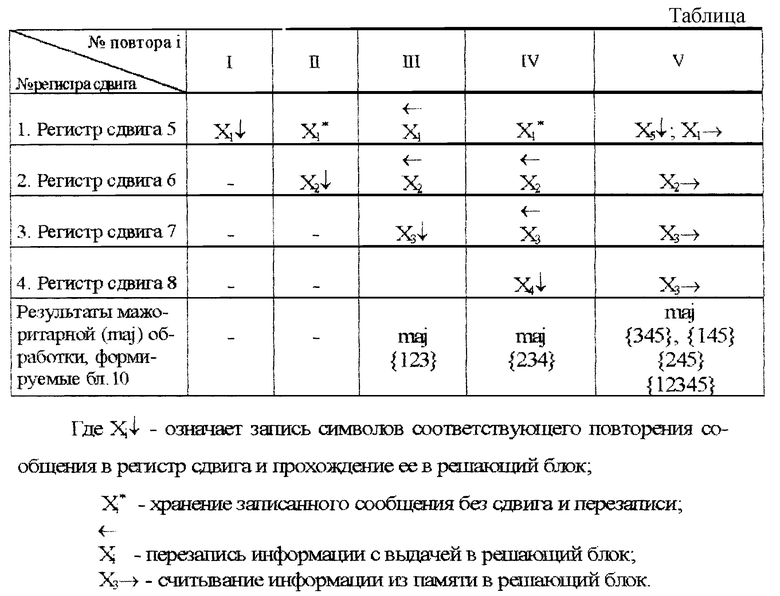

Регистры сдвига 5-8 являются стандартными элементами памяти и служат для хранения, перезаписи и выдачи информации, циркулирующей в устройстве. Распределение хранимой информации по регистрам сдвига может быть представлено таблицей.

Выход первого регистра сдвига 5 связан со вторым входом переключателя 1 и вторым входом решающего блока 10. Выход первого регистра сдвига 6 подключен к третьему входу решающего блока 10 и второму входу второго переключателя 2. Выход третьего регистра сдвига 7 подключен ко второму входу третьего переключателя 3 и четвертому входу решающего блока 10. Выход четвертого регистра сдвига 8 подключен ко второму входу четвертого переключателя 4 и пятому входу решающего блока 10.

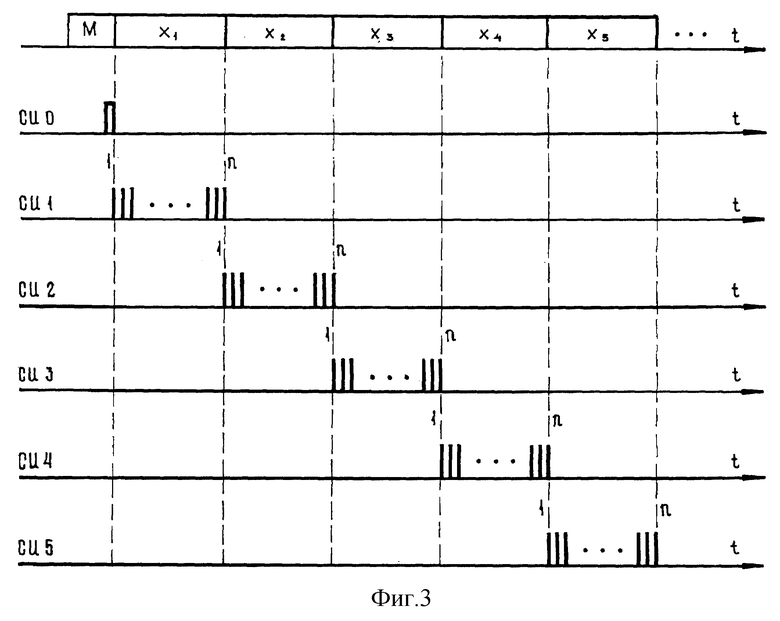

Синхронизатор 9 обеспечивает нормальное функционирование всех элементов устройства. На фиг. 3 представлена временная диаграмма работы синхронизатора. После выделения маркера цикловой синхронизации, определяющего начало кадра многократно повторенного сообщения выделяется импульс установки элементов памяти устройства в нулевое состояние (см. фиг. 3. "Уст. СИО"). После чего синхронизатор 9 обеспечивает пакетирование синхроимпульсов в последовательности СИ1 - СИ5 из импульсов тактовой синхронизации СИ, поступающих на его вход. Число импульсов соответствует в пакете количеству символов в одном повторе сообщения. Для выполнения функций такого блока уже существует ряд технических решений, описанных в технической литературе, например, в книге: Гуров В. С. , Емельянов А.Е., Етрухин Н.Н., Осипов В.Г. Передача дискретной информации и телеграфия. - М: Связь, 1974, с. 135.

При этом первый вход синхронизатора 9 является входом тактовой синхронизации. Первый выход этого блока одновременно соединен с первыми управляющими входами первого переключателя 1 и первого регистра сдвига 5. Второй выход синхронизатора 9 одновременно включен на первые управляющие входы второго переключателя 2 и второго регистра сдвига 6. Третий выход синхронизатора 9 одновременно подсоединен ко второму убавляющему входу регистра сдвига 6, ко второму управляющему входу переключателя 2, первому управляющему входу переключателя 3, первому управляющему входу третьего регистра сдвига 7, второму управляющему входу переключателя 1, регистра сдвига 5 и первому управляющему входу решающего блока 10. Четвертый выход синхронизатора 9 подключен к третьему управляющему входу переключателя 2, второму управляющему входу переключателя 3, первому управляющему входу переключателя 4, регистра сдвига 8, второму синхровходу регистра сдвига 7, третьему синхровходу регистра двига 6, второму управляющему входу решающего блока 10. Пятый выход синхронизатора 9 одновременно связан с третьими управляющими входами решающего блока 10 и 1, регистра сдвига 5, четвертым управляющим входом переключателя 2, регистра сдвига 6, третьим управляющим входом переключателя 3, регистра двига 7, вторым управляющим входом переключателя 4, регистра сдвига 8. Установочный вход синхронизатора 9 является установочными входами регистров сдвига 5, 6, 7, 8.

Решающий блок 10 предназначен для формирования расширенного набора решающих мажоритарных (maj) правил. По выходу 1 решающего блока 10 формируются разнесенные во времени результаты мажоритарной обработки первых трех повторов maj (X1X2 X3) сообщения в момент приема третьего X3 повтора и последних трех повторов maj (X3X4X5) в момент приема пятого X5 повторения.

Результат maj {X2X3X4} обработки второго, третьего, четвертого повторений выдается на второй выход решающего блока 10 в момент приема символов четвертого повтора X4. На этот же выход выдается результат maj {X1X4X5} обработки одноименных символов первого, четвертого, пятого повторов в момент приема символов пятого повторения X5.

На третий выход решающего блока 10 поступает результат мажоритарной обработки maj {X2Х4X5} по приходе символов пятого повтора X5.

По четвертому выходу выдается результат мажоритарной обработки в целом по пяти повторам сообщений maj {X1X2X3X4X5}.

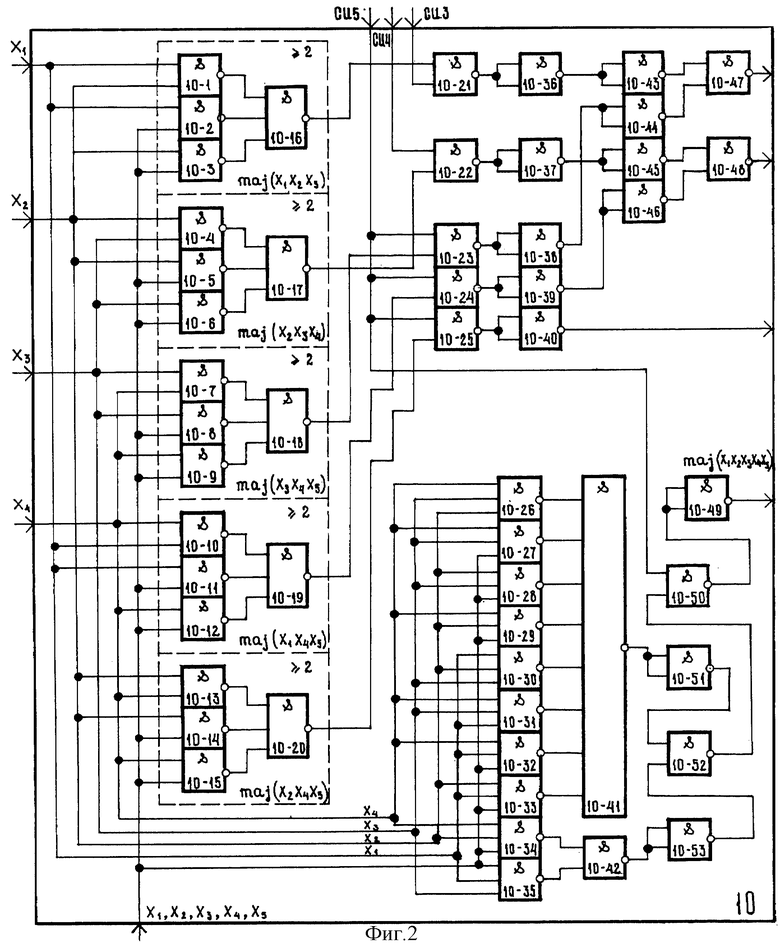

Возможный вариант функциональной схемы решающего блока 10 приведен на фиг. 2, которая содержит логические элементы в базисе "И - НЕ" 10-1 - 10-49. Решающий блок может быть реализован на типовой серии 133ЛА2, 133ЛАЗ, 133ЛА4.

При этом элементы 10-1 - 10-3, 10-16 реализуют первое решающее правило:

maj {X1X2X3}=X1X2+X1X3+ X2X3. (1)

Элементы 10-4 - 10-6,10-12 формируют второе правило:

maj {X2X3X4}=X2X3+X2X4+ X3X4. (2)

Элементы 10-7 - 10-9,10-18 опрецеляют мажоритарный результат последних трех повторов из пяти, третье правило:

maj {X3X4X5}=X3X4+X3X5+ X4X5. (3)

Элементы 10-10 - 10-12,10-19 реализуют четвертое правило:

maj {X1X4X5=X1X4+X1X5+ X4X5. (4)

Элементы 10-13 - 10-15,10-20 формируют пятое правило:

maj {X2X4X5}=X2X4+X2X5+X4X5. (5)

Группа элементов 10-26 - 10-35,10-41,10-42 позволяет провести мажоритарную обработку в целом по пяти повторам сообщения, шестое правило:

maj {X1X2X3X4X5}= X2X3X4+X3X4X5+ X2X3X5+X2X4X5+ X1X2X3+X1X3X4+ X1X4X5+X1X2X5+ X1X2X4+X1X3X5. (6)

Остальные элементы решающего блока 10 выполняют функции логических элементов "И", "ИЛИ".

Устройство работает следующим образом. Исходное состояние элементов памяти устройства нулевое, что обеспечивается установочным синхроимпульсом "СИ 0" (см. фиг. 3), выделенным по приему маркера цикловой кадровой синхронизации.

Символы первого повторения сообщения поступают на первый вход первого переключателя 1, который открывается синхроимпульсами СИ 1. Символы первого повторения, проходя через переключатель 1, записываются в регистр сдвига 5 с частотой следования синхроимпульсов СИ 1. Таким образом, по завершении приема первого повторения X1 оно оказывается записанным в первый регистр сдвига 5. Состояние регистров сдвига 6,7,8 - нулевое.

Синхронизатор 9, отсчитав n первых синхроимпульсов, выдает на втором выходе пачку синхроимпульсов СИ 2, которые обеспечивают прохождение через переключатель 2 и запись в регистр сдвига 6 символов второго повторения X2 сообщения. Состояние регистров сдвига 7, 8 - нулевое.

При приеме третьего повторения сообщения X3 синхроимпульсы СИ 3, выдаваемые с третьего выхода синхронизатора 9, обеспечивают коммутацию выходов регистров сдвига 5 и 6 через соответствующие переключатели 1 и 2, а также перезаписи, хранимых в них символов первого X1 и второго X2 повторений сообщения, с выдачей их на второй и третий входы решающего блока 10. Символы третьего повторения X3 через открытый переключатель 3 записываются в третий регистр сдвига 7, одновременно поступая на первый вход решающего блока 10. Поступающие через первый, второй, третий входы решающего блока 10 символы X1X2X3 повторений проходят через мажоритарный элемент, реализующий критерий "2 х 3", собранный на элементах "И-HE" (10 - 1 - 10-3,10-16), с выхода которого, через открытый синхроимпульсами СИ 3 элемент "И" (10-21, 10-36) и элемент "ИЛИ" (10-43, 10-44, 10-47), формируемый результат мажоритарной обработки первого решающего правила maj {X1X2X3} (1) выдается на первый выход устройства. Таким образом, после приема третьего повторения формируется результат мажоритарной обработки (1), а в регистрах сдвига 5, 6, 7 сохраняются символы X2X3X3 повторений соответственно (см. таблицу).

При приеме символов четвертого повторения X4 происходит выталкивание с перезаписью информации, хранимой в регистрах сдвига 6, 7, в решающий блок 10. Символы X4 через открытый синхроимпульсами СИ 4 переключатель 4 записываются в регистр сдвига 8, одновременно поступая на первый вход решающего блока 10. В работу включается мажоритарный элемент (10-4 - 10-6,10-17), реализующий правило (2) maj {X2X3X4}. Результат обработки через открытый СИ 4 элемент "И" (10-22, 10-37) и элемент "ИЛИ" (10-45, 10-46, 10-48) поступает на второй выход устройства. После приема X4 решающий блок 10 вьдал результат мажоритарной обработки по одноименным символам второго, третьего, четвертого повторений, а в регистрах сдвига 5, 6, 7, 8 соответственно сохранились символы X1X2X3X4 повторений.

При приеме символов пятого повторения X5, формируемых синхронизатором 9, импульсы СИ 5 выталкивают хранимую в регистрах сдвига 5, 6, 7, 8 информацию в решающий блок 10. При этом в регистр сдвига 5 записываются символы пятого повтора X5, проходя через переключатель 1, открытый СИ 5.

В то же время символы X5 поступают и в решающий блок 10 через первый вход.

В решающем блоке 10 реализуется оставшийся расширенный набор решающих правил.

Правило (3) maj {X3X4X5} реализуется на элементах (10-7 - 10-9, 10-18), а результат через элементы 10-23, 10-38, 10-44, 10-47 поступает на первый выход решающего блока 10.

Правило (4) maj {X1X4X5} формируется элементами 10-10 - 10-12, 10-19 и через 10-20, 10-39, 10-46, 10-48 результат мажоритарной обработки выдается на второй выход устройства.

Правило (5) maj {X2X4X5} реализуется на элементах "И-НЕ" (10-13 - 10-15). Результат мажоритарной обработки через 10- 25, 10-40, открытые СИ 5 выдается на третий выход устройства.

Правило (6) формируется совокупностью элементов "И-НЕ" 10-26 - 10-35, 10-41, 10-42, 10-51 - 10-53. Результат maj {X1-X5} через открытые СИ 5 элементы 10-50, 10-49 выдается на четвертый выход устройства.

Таким образом, после приема пяти повторов сообщения устройство реализует расширенный набор решающих правил. В регистре сдвига 5 сохраняются символы X5. Регистры сдвига 6, 7, 8 очищены и готовы к приему последующих повторов кадра сообщения. Это позволит продолжить обработку по изложенным правилам поступающих сообщений кадра, если кадр содержит более чем пять повторов сообщения.

Предлагаемое устройство обладает более высокой технико-экономической эффективностью, чем известное.

Известное устройство позволяет реализовать только четыре решающих мажоритарных правила (X1X2X3, X2 X3X4, X3X4X5, X1-X5).

Предлагаемое устройство расширяет функциональные возможности, увеличивая помехоустойчивость, т.к. позволяет провести дополнительную мажоритарную обработку еще двух наборов (X1X4X5, X2X4X5).

Известно, что при мажоритарной обработке одноименных символов (2m-l, m= 2, 3,...) кратно повторенному сообщению, эквивалентная вероятность искажения единичного символа в итоговой комбинации оценивается выражением

Pэ(m) ≅ C

т.е. при пятикратном повторении из 32 возможных комбинаций искажения одноименных символов 10 принадлежат к комбинациям, пораженным трехкратной ошибкой. Известное устройство из всей совокупности 10 комбинаций ошибок не исправляет три комбинации. Следовательно, эквивалентная вероятность искажения единичного символа в итоговой кодовой комбинации оценивается как Pэ1 = 3 P0 3.

Предлагаемое устройство исправляет все трехкратные ошибки, не исправляя 5 четырехкратных и пятикратную ошибки. Следовательно,

Pэ2=5P0 4+P0 5 ≈ 5P0 4

ввиду малого значения второго слагаемого уже при P0=10-2 (радиоканал).

Отсюда видно, что применение данного устройства при Р0=10-2

в 60 раз уменьшает эквивалентную вероятность искажения единичного символа в итоговой комбинации. Это ведет к увеличению помехоустойчивости, т.к. во столько же раз уменьшаются потери информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Модифицированное устройство коррекции ошибок | 2016 |

|

RU2635253C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК ПРИ МНОГОКРАТНОМ ПОВТОРЕНИИ СООБЩЕНИЙ | 1991 |

|

RU2023348C1 |

| Устройство для приема и мажоритарного декодирования информации | 1988 |

|

SU1562977A2 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК ПРИ МНОГОКРАТНОМ ПОВТОРЕНИИ СООБЩЕНИЙ | 1991 |

|

RU2012134C1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ СИГНАЛА СТИРАНИЯ | 2001 |

|

RU2208907C2 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1987 |

|

SU1453599A2 |

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Модифицированное устройство коррекции ошибок с учетом сигнала стирания | 2019 |

|

RU2711035C1 |

Изобретение относится к телемеханике и вычислительной технике и может быть использовано в системах передачи и обработки дискретной информации для исправления ошибок при многократном повторении сообщений. Технический результат заключается в повышении помехоустойчивости. Технический результат достигается за счет того, что в устройство, содержащее решающий блок, три переключателя, выходы которых соединены с информационными входами одноименных регистров, синхронизатор, дополнительно введен четвертый регистр. Этим достигается расширение набора решающих правил. Полностью исправляются все трехкратные ошибки в одноименных символах пятикратно повторенного сообщения. 3 ил., 1 табл.

Устройство коррекции ошибок с расширенным набором решающих правил, содержащее решающий блок, выходы которого являются выходами устройства, три переключателя, выходы которых соединены с информационными входами одноименных регистров сдвига, синхронизатор, тактовый вход которого является тактовым входом устройства, первый-третий выходы синхронизатора соединены соответственно с объединенными первыми управляющими входами первого переключателя и первого регистра сдвига, объединенными первыми управляющими входами второго переключателя и второго регистра сдвига, объединенными первыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока, вторыми управляющими входами первого и второго переключателей, первого и второго регистров сдвига, отличающееся тем, что введен четвертый регистр сдвига, вход которого является выходом четвертого переключателя, первый информационный вход которого объединен с первыми информационными входами переключателей, решающего блока и является информационным входом устройства, вторые информационные входы переключателей одновременно связаны с соответствующими выходами регистров сдвига и входами решающего блока, установочные входы регистров сдвига объединены с установочным входом устройства и установочным входом синхронизатора, четвертый выход которого соответственно соединен с объединенными третьими управляющими входами второго переключателя, второго регистра сдвига, вторыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока и первыми управляющими входами четвертого переключателя и четвертого регистра сдвига, при этом пятый выход синхронизатора одновременно подключен ко вторым управляющим входам четвертого переключателя и четвертого регистра сдвига, третьим управляющим входам третьего, первого переключателей, третьего, первого регистров сдвига, решающего блока и четвертым управляющим входам второго переключателя и второго регистра сдвига.

| Устройство для приема и мажоритарного декодирования информации | 1987 |

|

SU1439750A1 |

| Устройство для исправления ошибок | 1986 |

|

SU1367028A1 |

| Устройство для исправления ошибок в системе передачи дискретной информации | 1984 |

|

SU1177927A2 |

| Устройство для обнаружения ошибок | 1990 |

|

SU1743010A1 |

| US 3949208 А, 06.04.1976. | |||

Авторы

Даты

2000-06-27—Публикация

1998-07-20—Подача