Изобретение относится к телемеханике и вычислительной технике и может быть использовано в системах передачи и обработки дискретной информации для коррекции ошибок при семикратном повторении сообщения.

Известны устройства для мажоритарного декодирования (см. А.с. СССР №1345357 «Устройство для декодирования двоичных кодов при трехкратном повторении сообщений», №1562977 «Устройство для приема и мажоритарного декодирования информации», №677123 «Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации», №944129 «Устройство для декодирования двоичных кодов при трехкратном повторении сообщений», №980114 «Устройство для приема и мажоритарного декодирования информации», №1005151 «Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов», №1439750 «Устройство для приема и мажоритарного декодирования информации», Патенты РФ №2012134 «Устройство для исправления ошибок при многократном повторении сообщений», №2023348 «Устройство для исправления ошибок при многократном повторении сообщений»), содержащие регистры сдвига и логические элементы с соответствующими связями, позволяющие подвергать мажоритарной обработке три, пять и более повторений сообщения без потери промежуточных результатов. Недостатком этих устройств является ограниченность функциональных возможностей, проявляющаяся в том, что анализируются не все возможные сочетания одноименных символов повторений сообщения.

Из известных устройств наиболее близким по технической сущности является устройство коррекции ошибок с расширенным набором решающих правил, описанное в патенте РФ №2152129.

Это устройство содержит решающий блок, четыре переключателя, выходы которых соединены с информационными выходами одноименных регистров сдвига, синхронизатор и соответствующие связи.

Недостатком этого устройства является низкая помехоустойчивость, т.к. реализуя полный набор решающих правил на пяти повторениях сообщений, не исправляются четырехкратные и пятикратные ошибки в одноименных символах пяти повторений.

Техническим результатом настоящего изобретения является повышение помехоустойчивости, в условиях интенсивного воздействия помех, приводящих к значительному искажению одноименных символов повторений сообщения.

Указанный технический результат достигается тем, что в устройство, содержащее решающий блок, выходы которого являются выходами устройства, четыре переключателя, выходы которых соединены с информационными входами одноименных регистров сдвига, синхронизатор, тактовый вход которого является тактовым входом устройства, первый -третий выходы синхронизатора соединены соответственно с объединенными первыми управляющими входами первого переключателя и первого регистра сдвига, объединенными первыми управляющими входами второго переключателя и второго регистра сдвига, объединенными первыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока, вторыми управляющими входами первого и второго переключателей, первого и второго регистра сдвига, четвертый выход синхронизатора соединен с объединенными третьими управляющими входами второго переключателя, второго регистра сдвига, вторыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока и первыми управляющими входами четвертого регистра сдвига и четвертого переключателя, первый информационный вход которого объединен с первыми информационными входами первого-третьего переключателей, решающего блока и является информационным входом устройства, установочные входы первого-четвертого регистров сдвига объединены с установочным входом устройства и установочным входом синхронизатора, пятый выход которого одновременно подключен ко вторым управляющим входам четвертого переключателя и четвертого регистра сдвига, третьим управляющим входам третьего, первого переключателей, третьего, первого регистров сдвига, решающего блока, четвертым управляющим входам второго переключателя и второго регистра сдвига, при этом выходы первого-четвертого регистров сдвига соединены соответственно со вторым-пятым информационными входами решающего блока и вторыми информационными входами первого-четвертого переключателей, введены пятый переключатель, пятый регистр сдвига, формирователь результата, второй решающий блок, кодопреобразователь, при этом информационный вход пятого регистра сдвига является выходом пятого переключателя, первый информационный вход которого объединен с первыми информационными входами формирователя результата, второго решающего блока, информационным входом кодопреобразователя и информационным входом устройства, первый дополнительный вход кодопреобразователя связан со вторыми информационными входами решающего блока и формирователя результата, выходом первого регистра сдвига, второй дополнительный вход кодопреобразователя связан с третьими информационными входами решающего блока и формирователя результата, выходом второго регистра сдвига, третий дополнительный вход кодопреобразователя связан с четвертыми информационными входами решающего блока и формирователя результата, выходом третьего регистра сдвига, четвертый дополнительный вход кодопреобразователя связан с пятыми информационными входами решающего блока и формирователя результата, выходом четвертого регистра сдвига и вторым информационным входом второго решающего блока, выходы которого являются первым и вторым дополнительными выходами устройства, а третий информационный вход второго решающего блока одновременно связан со вторым информационным входом пятого переключателя и выходом пятого регистра сдвига, установочный вход которого объединен с установочным входом устройства и установочным входом кодопреобразователя, управляющий вход которого одновременно подключен к пятому выходу синхронизатора и первым управляющим входам пятого регистра сдвига, пятого переключателя, второй управляющий вход которого одновременно соединен с первым управляющим входом второго решающего блока, вторым управляющим входом пятого регистра сдвига, третьими управляющими входами четвертого переключателя, четвертого регистра сдвига и шестым выходом синхронизатора, седьмой выход которого одновременно подключен к четвертым управляющим входам первого регистра сдвига, первого переключателя, пятым управляющим входам второго регистра сдвига, второго переключателя, четвертым управляющим входам третьего регистра сдвига, третьего переключателя, четвертым управляющим входам четвертого регистра сдвига, четвертого переключателя, третьим управляющим входам пятого регистра сдвига, пятого переключателя, второму управляющему входу второго решающего блока и управляющему входу формирователя результата, выход которого является третьим дополнительным выходом устройства, при этом первый - третий выходы кодопреобразователя соединены с соответствующими третьими информационными входами первого-третьего переключателей.

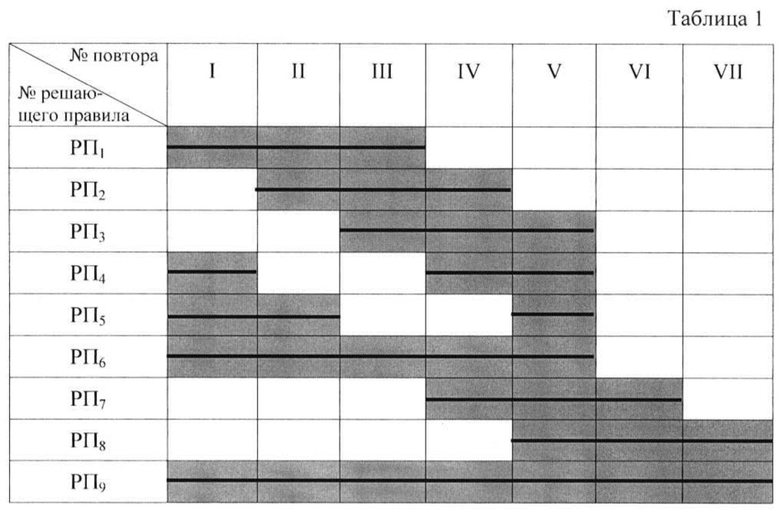

Этим достигается анализ и мажоритарная обработка одноименных символов всех групп, состоящих из трех повторений (X1 Х2 Х3), (Х2 Х3 Х4), (Х3 Х4 Х5), (X1 Х4 Х5), (X1 Х2 Х5) и пяти повторений (X1 Х2 Х3 Х4 Х5), где Xi - одноименные символы соответствующего i-го повтора, которые входят в кадр пятикратно повторенного сообщения. Кроме того, при минимальном увеличении объема памяти (пятый регистр сдвига, емкостью n разрядов), анализируются сочетания (Х4 Х5 Х6), (Х5 Х6 Х7) и (X1 Х2 Х3 Х4 Х5 Х6 Х7). Предлагаемый набор решающих правил представлен в таблице 1. Теперь появляется возможность исправить все трехкратные, четырехкратные и определенную долю пятикратных ошибок в одноименных символах семикратно повторенного сообщения. Известное устройство не позволяло исправлять уже четырехкратные ошибки.

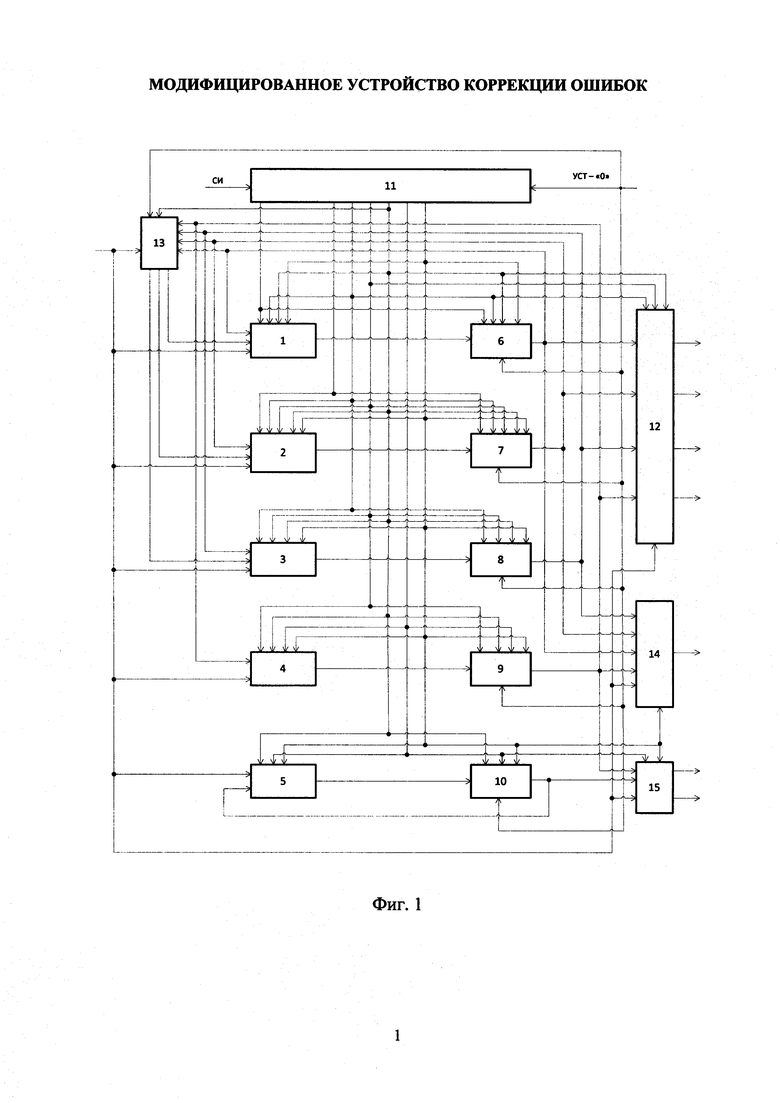

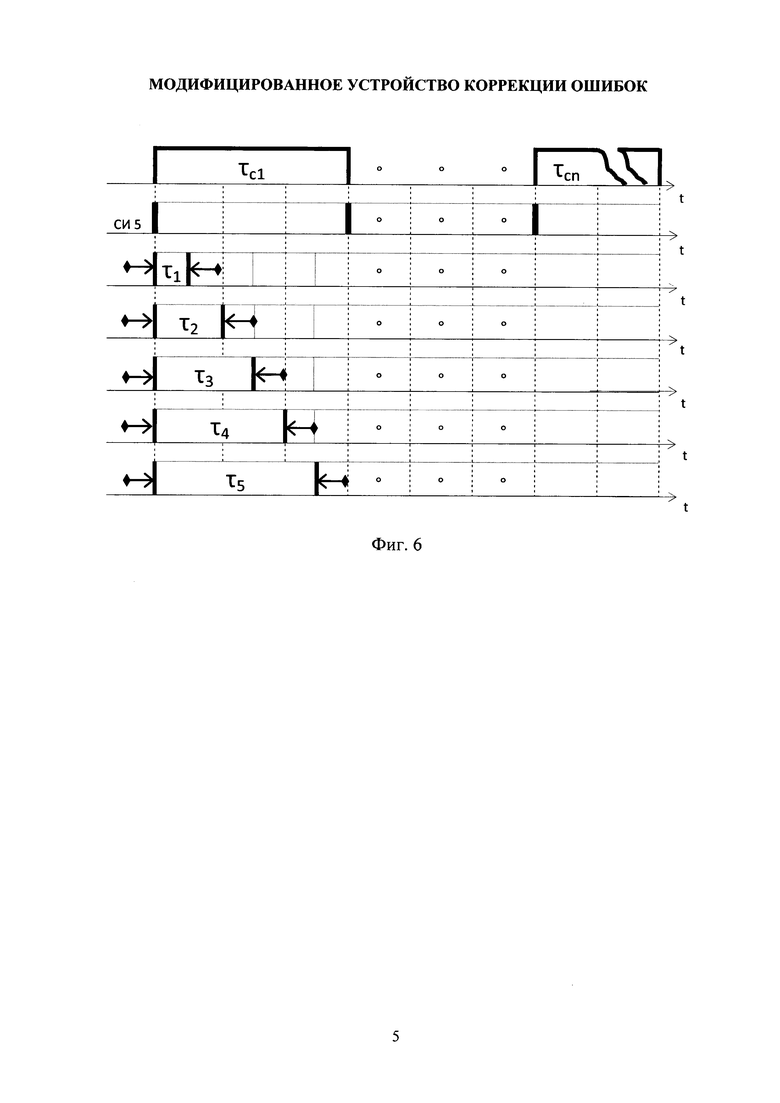

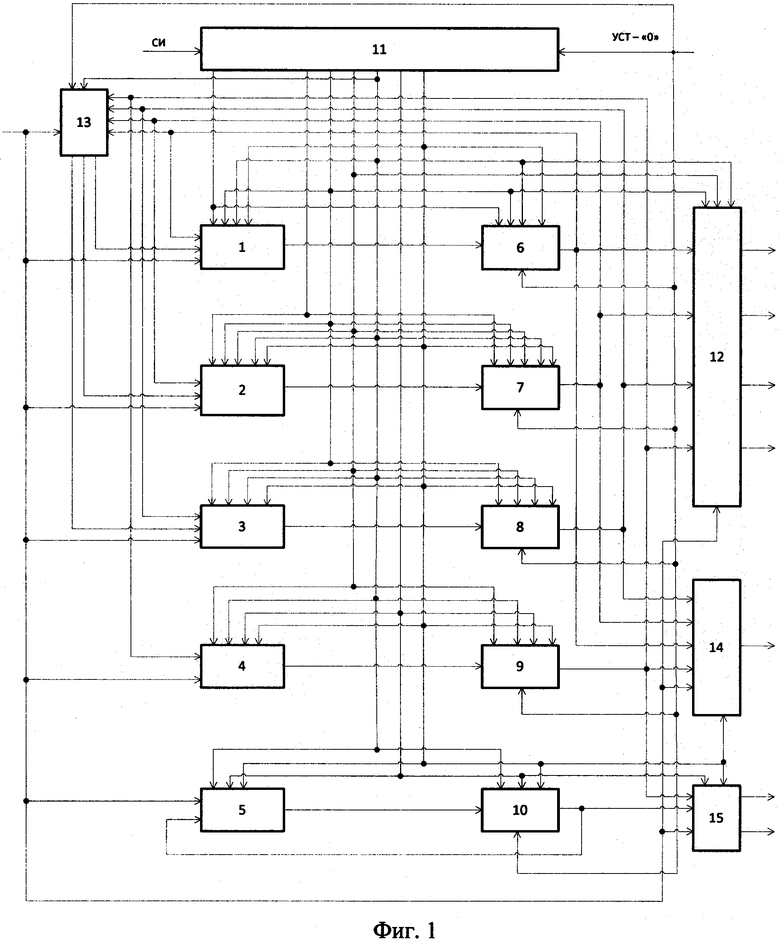

На фиг. 1 представлена структурная схема модифицированного устройства коррекции ошибок. Устройство содержит первый-пятый переключатели 1-5, первый-пятый регистры сдвига 6-10, синхронизатор 11, решающий блок 12, кодопреобразователь 13, формирователь результата 14, второй решающий блок 15.

Первый-пятый переключатели 1-5 предназначены для коммутации информационных входов первого-пятого регистров сдвига 6-10. Выходы первого-пятого переключателей 1-5 являются соответствующими информационными входами первого-пятого регистров сдвига 6-10.

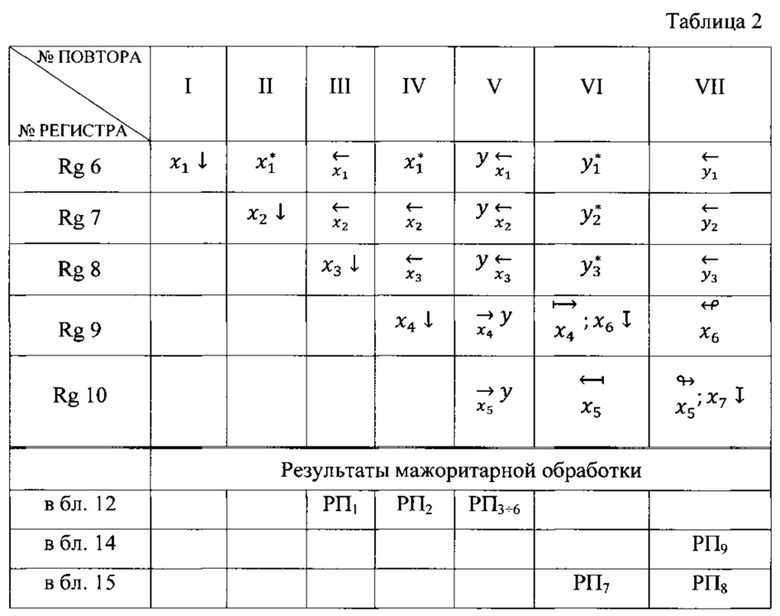

Первый-пятый регистры сдвига 6-10 являются стандартными элементами памяти и служат для хранения, перезаписи и выдачи информации, циркулирующей в устройстве. Распределение хранимой информации по регистрам сдвига представлено в таблице 2, где

xi ↓ - означает запись символов советующего повторения сообщения в регистр сдвига и прохождение ее в решающий блок;

- хранение записанного сообщения без сдвига и перезаписи;

- хранение записанного сообщения без сдвига и перезаписи;

- перезапись информации с выдачей в решающий блок;

- перезапись информации с выдачей в решающий блок;

- выдача хранимой информации в кодопреобразователь, с последующей записью результата обработки для хранения в соответствующем регистре сдвига, и в решающий блок;

- выдача хранимой информации в кодопреобразователь, с последующей записью результата обработки для хранения в соответствующем регистре сдвига, и в решающий блок;

- хранение результатов обработки кодопреобразователем;

- хранение результатов обработки кодопреобразователем;

- выдача информации в кодопреобразователь, решающий блок, сохранение ее в регистре сдвига;

- выдача информации в кодопреобразователь, решающий блок, сохранение ее в регистре сдвига;

- перезапись информации с выдачей во второй решающий блок;

- перезапись информации с выдачей во второй решающий блок;

- запись симоволов соответствующего повторения сообщения в регистр сдвига и прохождение ее во второй решающий блок и формирователь результата;

- запись симоволов соответствующего повторения сообщения в регистр сдвига и прохождение ее во второй решающий блок и формирователь результата;

- считывание информации во второй решающий блок;

- считывание информации во второй решающий блок;

- перезапись с выдачей во второй решающий блок и формирователь результата;

- перезапись с выдачей во второй решающий блок и формирователь результата;

- выдача информации во второй решающий блок и формирователь результата.

- выдача информации во второй решающий блок и формирователь результата.

Выход первого регистра сдвига 6 связан со вторыми информационными входами первого переключателя 1, решающего блока 12, формирователя результата 14 и первым дополнительным входом кодопреобразователя 13. Выход второго регистра сдвига 7 подключен к третьему информационному входу решающего блока 12, второму информационному входу второго переключателя 2, третьему информационному входу формирователя результата 14 и второму дополнительному входу кодопреобразователя 13.

Выход третьего регистра сдвига 8 подключен ко второму информационному входу третьего переключателя 3, четвертому информационному входу решающего блока 12, четвертому информационному входу формирователя результата 14 и третьему дополнительному входу кодопреобразователя 13. Выход четвертого регистра сдвига 9 подключен ко второму информационному входу четвертого переключателя 4, пятому информационному входу решающего блока 12, пятому информационному входу формирователя результата 14, второму информационному входу второго решающего блока 15 и четвертому дополнительному входу кодопреобразователя 13. Выход пятого регистра сдвига 10 соединен со вторым информационным входом пятого переключателя 5 и третьим информационным входом второго решающего блока 15. Информационные входы первого-пятого регистров сдвига 6-10 являются соответствующими выходами первого-пятого переключателей 1-5.

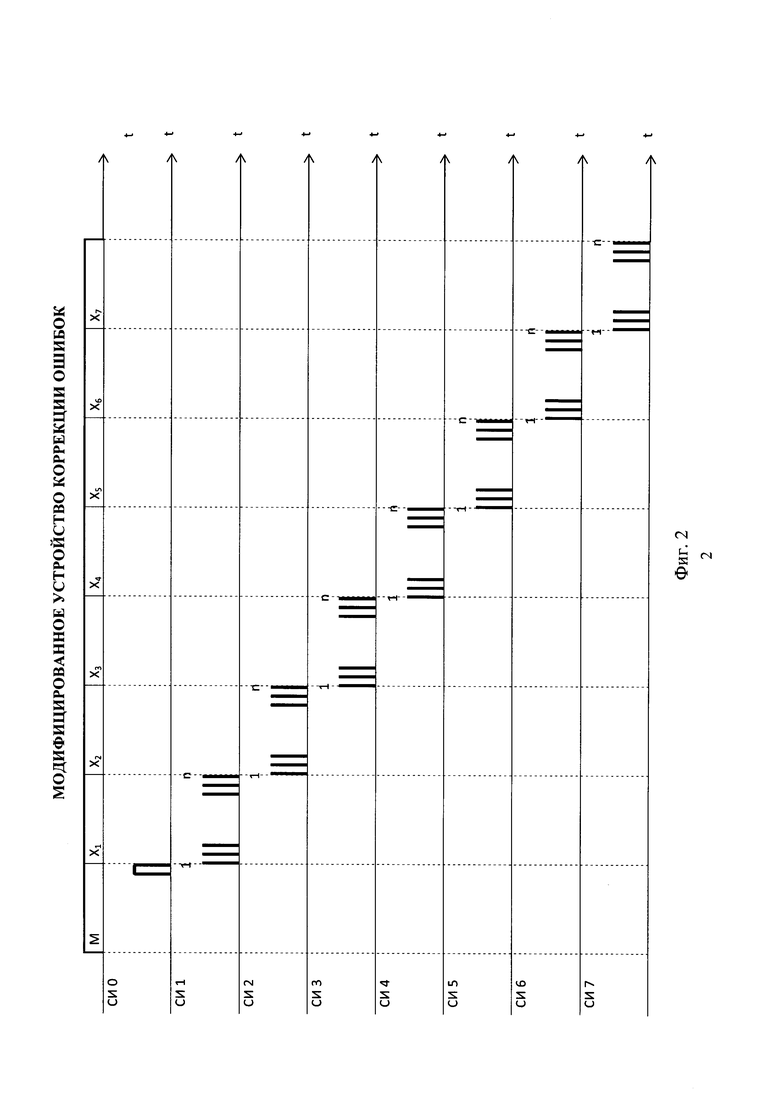

Синхронизатор 11 обеспечивает нормальное функционирование всех элементов устройства. На Фиг. 2. представлена временная диаграмма работы синхронизатора. После выделения маркера цикловой синхронизации, определяющего начало кадра многократно повторенного сообщения выделяется импульс установки элементов памяти устройства в нулевое состояние (см. Фиг. 2 «СИ 0»).

После чего синхронизатор 11 обеспечивает пакетирование синхроимпульсов в последовательности СИ 1 - СИ 7 из импульсов тактовой синхронизации СИ, поступающих на его вход. Число импульсов в пакете соответствует количеству символов в одном повторе сообщения.

При этом тактовый вход СИ синхронизатора 11 является тактовым входом устройства. Первый выход синхронизатора 11 одновременно соединен с первыми управляющими входами первого переключателя 1 и первого регистра сдвига 6. Второй выход синхронизатора 11 одновременно подключен к первым управляющим входам второго переключателя 2, второго регистра сдвига 7. Третий выход синхронизатора 11 одновременно подсоединен ко вторым управляющим входам первого переключателя 1, первого регистра сдвига 6, первому управляющему входу решающего блока 12, вторым управляющим входам второго переключателя 2, второго регистра сдвига 7 и первым управляющим входам третьего переключателя 3, третьего регистра сдвига 8. Четвертый выход синхронизатора 11 подключен ко второму управляющему входу решающего блока 12, третьим управляющим входам второго переключателя 2, регистра сдвига 7, вторым управляющим входам третьего переключателя 3, третьего регистра сдвига 8, первым управляющим входам четвертого переключателя 4, четвертого регистра сдвига 9. Пятый выход синхронизатора 11 одновременно связан с третьими управляющими входами первого переключателя 1, первого регистра сдвига 6, третьим управляющим входом решающего блока 12, четвертыми управляющими входами второго переключателя 2, второго регистра сдвига 7, третьими управляющими входами третьего переключателя 3, третьего регистра сдвига 8, вторыми управляющими входами четвертого переключателя 4, четвертого регистра сдвига 9, первыми управляющими входами пятого переключателя 5, пятого регистра сдвига 10, и управляющим входом кодопреобразователя 13. Шестой выход синхронизатора 11 одновременно соединен с третьими управляющими входами четвертого переключателя 4, четвертого регистра сдвига 9, вторыми управляющими входами пятого переключателя 5, пятого регистра сдвига 10 и первым управляющим входом второго решающего блока 15. Седьмой выход синхронизатора 11 одновременно подключен к четвертым управляющим входам первого переключателя 1, первого регистра сдвига 6, пятым управляющим входам второго переключателя 2, второго регистра сдвига 7, четвертым управляющим входам третьего переключателя 3, третьего регистра сдвига 8, четвертым управляющим входам четвертого переключателя 4, четвертого регистра сдвига 9, третьим управляющим входом пятого переключателя 5, пятого регистра сдвига 10, вторым управляющим входом второго решающего блока 15 и управляющим входом формирователя результата 14. Установочный вход синхронизатора 11 является и установочными входами первого 6, второго 7, третьего 8, четвертого 9, пятого 10 регистров сдвига, кодопреобразователя 13 и установочным входом устройства.

Решающий блок 12 предназначен для формирования расширенного набора решающих мажоритарных (maj) правил. На первом выходе решающего блока 12 формируется разнесенные во времени результаты мажоритарной обработки первых трех повторов РП1 maj(X1X2X3) сообщения в момент приема третьего Х3 повтора и РП3 maj(X3X4X5) в момент приема пятого Х5 повторения.

Результат РП2 maj(X2X3X4) обработки второго, третьего, четвертого повторения выдается на второй выход решающего блока 12 в момент приема символов четвертого повтора Х4. На этот же выход выдается результат РП4 maj(X1X4X5) обработки одноменных символов первого, четвертого, пятого повторов в момент приема символов пятого повторения Х5.

На третий выход решающего блока 12 поступает результат мажоритарной обработке РП5 maj(X1X2X5) по приходу символов пятого повтора Х5.

По четвертому выходу решающего блока 12 выдается результат мажоритарной обработке РП6 maj(X1X2X3X4X5) в целом по пяти повторам сообщения. Возможный вариант функциональной схемы решающего блока 12 аналогичен решающему блоку прототипа.

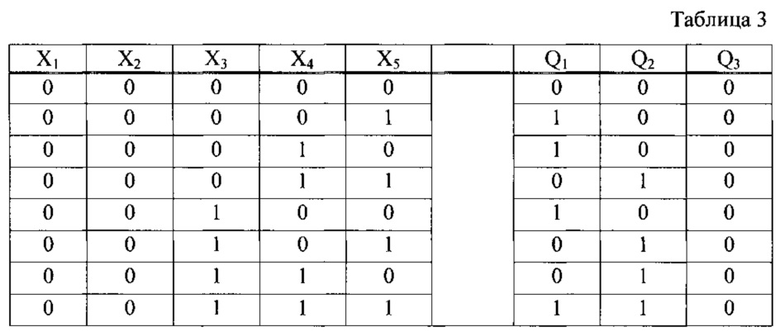

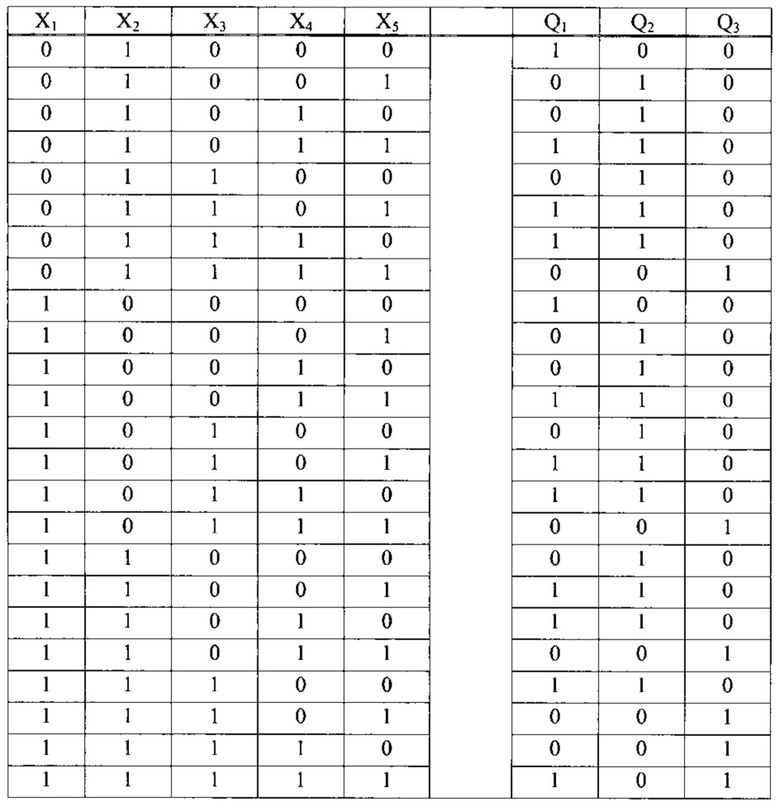

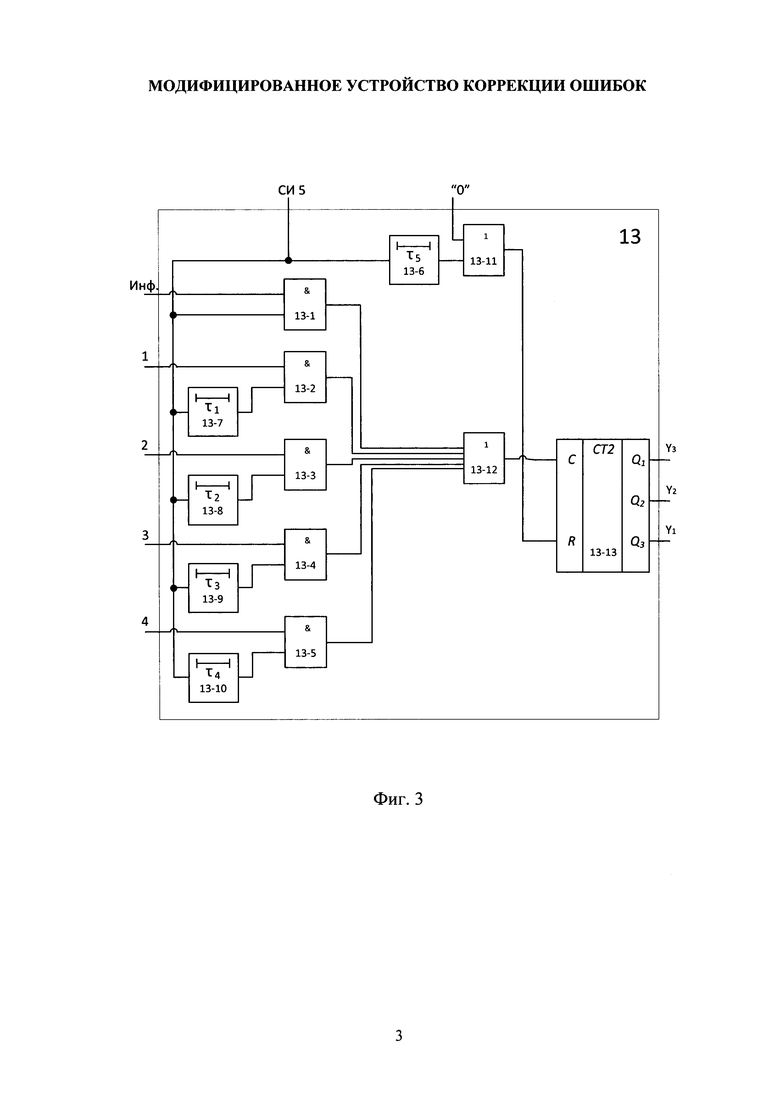

Кодопреобразователь 13 предназначен для формирования кода числа единиц в одноименных символах пяти повторений сообщений. Таблица 3 отражает формирование выходных сигналов yi, кодопреобразователя 13.

Возможный вариант функциональной схемы кодопреобразователя 13 приведен на фиг.3, которая содержит логические элементы «И» 13-1 - 13-5, элементы задержки с различным временем задержки τ 13-6 - 13-10 (τ1<τ2<τ3<τ4<τ5, смотри фиг. 6, где τci - длительность информационного символа, τi - временная задержка), элементы «ИЛИ» 13-11 - 13-12, трехразрядный двоичный счетчик 13-13.

При этом информационный вход кодопреобразователя 13 одновременно подключен ко входу устройства, к первым информационным входам первого-пятого переключателей 1-5, решающего блока 12, формирователя результата 14, второго решающего блока 15. Выходы кодопреобразователя 13 соединены с соответствующими третьими информационными входами первого-третьего переключателя 1-3. Установочный вход кодопреобразователя 13 подключен к установочному входу устройства.

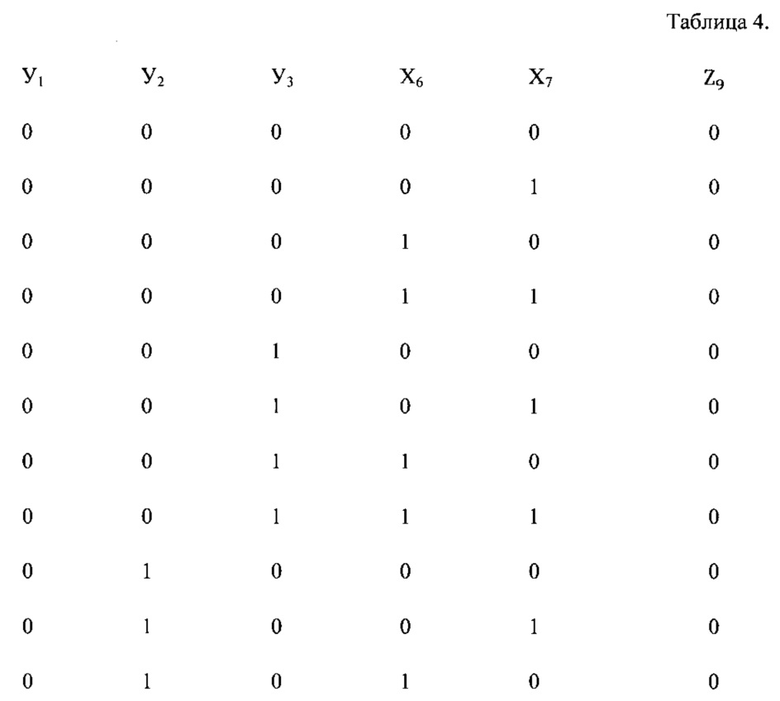

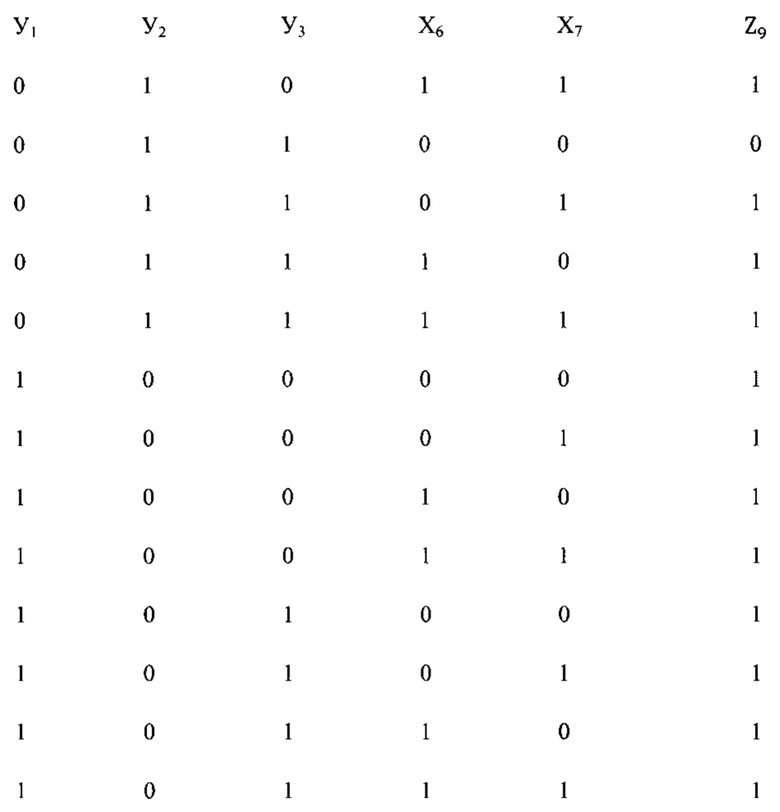

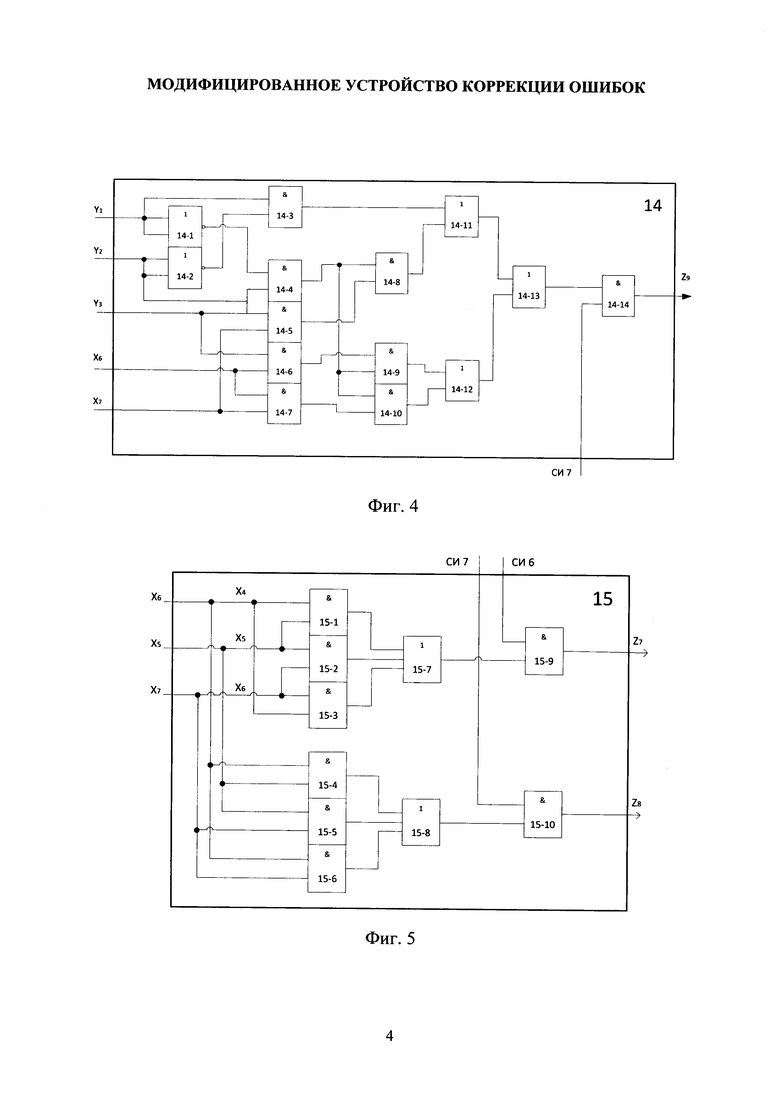

Формирователь результата 14 предназначен для получения мажоритарного результата обработки одноименных символов семи повторений сообщения РП9 maj(X1X2X3X4X5X6X7). Таблица 4 отражает формирование результата голосования по большинству Z9

Логическое выражение для Z9 имеет вид

Возможный вариант функциональной схемы формирователя результата 14 представлен на фиг. 4, которая содержит логические элементы «И» 14-3 - 14-10, 14-14, «ИЛИ» 14-1, 14-2, 14-11 - 14-13.

Выход формирователя результата 14 является третьим дополнительным выходом устройства.

Второй решающий блок 15, предназначен для формирования двух дополнительных решающих правил голосования по большинству РП7 maj(Х4Х5Х6), РП8 maj (Х5Х6Х7).

Результат РП7 maj (Х4Х5Х6) - Z7 выдается на первый дополнительный выход устройства в момент приема символов шестого повтора Х6. На второй дополнительный выход второго решающего блока 15, поступает результат РП8 maj (Х5Х6Х7) - Z8 обработки одноименных символов пятого, шестого, седьмого повторов сообщения.

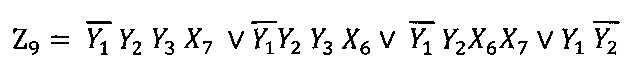

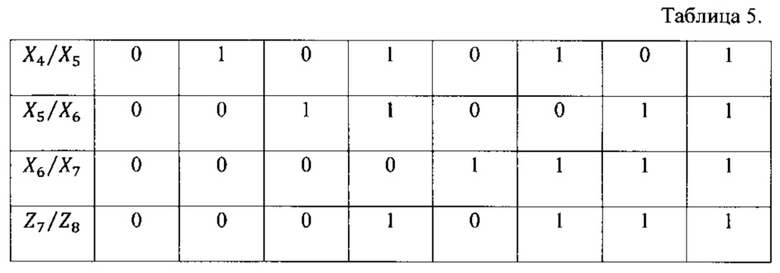

Сформулированным правилам соответствует таблица 5.

Логические выражения для Z7 и Z8 имеют вид

Z7=X4X5∨X5X6∨X4X6

Z8=X5X6∨X6X7∨X5X7

Возможный вариант функциональной схемы второго решающего блока 15 представлен на фиг.5, которая содержит логические элементы «И» 15-1 - 15-6, 15-9, 15-10; «ИЛИ» 15-7, 15-8.

Выходы второго решающего блока 15 являются первым и вторым дополнительными выходами устройства.

Устройство работает следующим образом. Исходное состояние элементов памяти устройства переводится в нулевое состояние, что обеспечивается установочным синхроимпульсом «СИ 0» (см. фиг. 2), выделенным по приему маркера цикловой кадровой синхронизации.

Символы первого повторения сообщения (Х1) поступают на первый информационный вход первого переключателя 1, который открывается синхроимпульсами СИ1, поступающими на первые управляющие входы первого переключателя 1 и первого регистра сдвига 6 с первого выхода синхронизатора 11.

Символы первого повторения, проходя через первый переключатель 1, записываются в первый регистр сдвига 6 (Х1 ↓) с частотой следования синхроимпульсов СИ1. Т.е., по окончанию приема символов первого повторения Х1 оно оказывается записанным в первый регистр сдвига 6. Состояние второго-пятого регистров сдвига 7-10 нулевое.

Синхронизатор 11, отсчитав n первых синхроимпульсов, выдает на втором выходе пачку синхроимпульсов СИ2, поступающих на первые управляющие входы второго переключателя 2 и второго регистра сдвига 7, которые обеспечивают прохождение через второй переключатель 2 и запись во второй регистр сдвига 7 символов второго повторения Х2 ↓ сообщения. Состояние третьего-пятого регистров сдвига 8-10 - нулевое.

При приеме третьего повторения Х3 сообщения, синхроимпульсы СИ 3, поступающие с третьего выхода синхронизатора 11 на первые управляющие входы третьего переключателя 3 и третьего регистра сдвига 8, вторые управляющие входы второго переключателя 2 и второго регистра сдвига 7, вторые управляющие входы первого переключателя 1, первого регистра сдвига 6, первый управляющий вход решающего блока 12, обеспечивают коммутацию выходов первого-второго регистров сдвига 6, 7 через соответствующие первый-второй переключатели 1 и 2, а так же перезапись хранимых в них символов первого  и второго

и второго  повторений сообщения, с выдачей их на второй и третий информационные входы решающего блока 12. Символы третьего повторения, через открытый синхроимпульсами СИ 3 третий переключатель 3, записываются Х3 ↓ в третий регистр сдвига 8, одновременно поступая на первый информационный вход решающего блока 12.

повторений сообщения, с выдачей их на второй и третий информационные входы решающего блока 12. Символы третьего повторения, через открытый синхроимпульсами СИ 3 третий переключатель 3, записываются Х3 ↓ в третий регистр сдвига 8, одновременно поступая на первый информационный вход решающего блока 12.

Поступающие через первый - третий информационные входы решающего блока 12 символы Х1Х2Х3 повторений проходят через мажоритарный элемент, реализующий критерий «2×3», формируя результат мажоритарной обработки РП1 maj (Х1Х2Х3), который выдается на первый выход устройства. Т.о., после приема Х3 третьего повторения формируется РП1 мажоритарный результат обработки трех первых повторов, а в первом-третьем регистрах сдвига 6, 7, 8 сохраняются символы Х1Х2Х3 повторов соответственно (см. табл. 2).

При приеме символов четвертого Х4 повторения синхроимпльсы СИ4 поступают на второй управляющий вход решающего блока 12, третьи управляющие входы второго переключателя 2 и второго регистра сдвига 7, вторые управляющие входы третьего переключателя 3, третьего регистра сдвига 8, первые управляющие входы четвертого переключателя 4, четвертого регистра сдвига 9. При этом происходит выталкивание с перезаписью информации, хранимой во втором-третьем регистрах сдвига 7, 8, в решающий блок 12.  . Символы Х4 через открытый синхроимпульсом СИ4 четвертый переключатель 4 записываются в четвертый регистр сдвига 9 Х4 ↓, одновременно поступая на первый информационный вход решающего блока 12, где в работу включается мажоритарный элемент, реализующий РП2 maj (Х2Х3Х4). Результат обработки поступает на второй выход устройства. После приема Х4 решающий блок 12 формирует результат мажоритарной обработки по одноименным символам второго, третьего, четвертого повторений, а в первом-четвертом регистрах сдвига 6-9 соответственно сохранились символы Х1Х2Х3Х4 повторений (см. табл. 2).

. Символы Х4 через открытый синхроимпульсом СИ4 четвертый переключатель 4 записываются в четвертый регистр сдвига 9 Х4 ↓, одновременно поступая на первый информационный вход решающего блока 12, где в работу включается мажоритарный элемент, реализующий РП2 maj (Х2Х3Х4). Результат обработки поступает на второй выход устройства. После приема Х4 решающий блок 12 формирует результат мажоритарной обработки по одноименным символам второго, третьего, четвертого повторений, а в первом-четвертом регистрах сдвига 6-9 соответственно сохранились символы Х1Х2Х3Х4 повторений (см. табл. 2).

При приеме символов пятого повтора Х5, фомируемые синхронизатором 11 синхроимпульсы СИ5 выталкивают, хранимую в первом-четвертом регистрах сдвига 6-9, информацию в решающий блок 12. При этом в пятый регистр сдвига 10 записываются символы пятого Х5 ↓ повтора, проходя через пятый переключатель 5, открытый СИ5, одновременно поступая на первый информационный вход решающего блока 12.

В решающем блоке 12 реализуется набор решающих правил:

РП3 maj (X3X4X5) результат поступает на первый выход блока 12, который является первым выходом устройства;

РП4 maj (X1X4X5) результат мажоритарной обработки выдается на второй выход устройства;

РП5 maj (Х1Х2Х5) результат выдается на третий выход устройства;

РП6 maj (Х1Х2Х3Х4Х5) выдается на четвертый выход устройства.

Кроме того выталкиваемые символы хранимые в первом-четвертом регистрах 6-9 поступают на соответствующие первый-четвертый дополнительные входы кодопреобразователя 13, на информационный вход которого подаются символы Х5. Информационные символы Х5 через открытый элемент «И» 13-1, «ИЛИ» 13-12, поступают на вход счетчика 13-13 изменяя его состояние. Если принятый символ был 1, то первый триггер счетчика 13-13 перейдет в единичное состояние, если символ 0, то состояние первого триггера не изменится. Возможные состояния выходов Q1Q2Q3 счетчика 13-13 следующие 000, 100. Выталкиваемый одноименный первый символ хранимой информации в первом регистре сдвига 6 через элемент «И» 13-2, на второй вход которого поступает СИ5 через элемент задержки 13-7 со временем задержки τ1 проходят далее через элемент «ИЛИ» 13-12, поступая на вход счетчика 13-13, где осуществляется подсчет числа единиц в одноименных первых символах первого и пятого повторений. Состояние выходов первого, второго и третьего триггеров Q1Q2Q3 счетчика 13-13 могут принимать значения 000, 100, 010. Выталкиваемые с помощью СИ5 символы второго повторения, хранимые во втором регистре сдвига 7 через элемент «И» 13-3 на второй вход которого поступают СИ5 через элемент задержки 13-8 с временем задержки τ2, проходят далее через элемент «ИЛИ» 13-12, поступая на вход счетчика 13-13, который подсчитывает число единиц в одноименных символах пятого, первого и второго повторений. Состояние выходов первого, второго и третьего триггеров Q1Q2Q3 счетчика 13-13 могут принимать значения 000, 100, 010, 110. Символы третьего повторения, хранимые в третьем регистре сдвига 8, поступающие на третий дополнительный вход кодопреобразователя 13 через элемент «И» 13-4 на второй вход которого поступают СИ5 через элемент задержки 13-9, с временем задержки т3, проходят далее через элемент «ИЛИ» 13-12 поступают на вход счетчика 13-13. На выходах Q1Q2Q3 счетчика 13-13 возможны следующие состояния 000, 100, 010, 110, 001. Выталкиваемые символы четвертого повторения с четвертого регистра сдвига 9 поступают на четвертый дополнительный вход кодопреобразователя 13, где через элемент «И» 13-5 на второй вход которого поступают СИ5 через элемент задержки 13-10 со временем задержки т4, проходят далее через элемент «ИЛИ» 13-12 и поступают на вход счетчика 13-13, тем самым подсчитывается код числа единиц в одноименных символах пяти повторений. Возможные состояния выходов Q1Q2Q3 счетчика 13-13 следующие 000, 100, 010, 110, 001, 101. Этим завершается операция подсчета числа единиц в одноименных первых символах пяти повторений. Для подсчета числа единиц в одноименных вторых символах пяти повторений счетчик 13-13 обнуляется синхроимпульсом СИ5, проходящим через элемент задержки 13-6 с временем задержки т5, элемент «ИЛИ» 13-11, который следует на вход R счетчика 13-13. Таким образом счетчик 13-13 готов к подсчету числа единиц в очередных одноименных символах пяти повторений.

С выхода кодопреобразователя 13, сформированные коды числа единиц по одноименным символам пяти повторений записываются в одноименные ячейки памяти первого-третьего регистров сдвига 6, 7, 8 в виде кода числа единиц (У1У2У3). Символы четвертого и пятого повторов сохраняются в четвертом-пятом регистрах сдвига 9, 10 соответственно.

Таким образом, после приема пяти повторов устройство реализовало решающие правила РП3 - РП6. В первом-третьем регистрах сдвига 6-8 хранится код числа единиц по одноименным символам пяти повторений сообщения. В четвертом регистре сдвига 9 сохранена информация четвертого повторения, а в пятом регистре сдвига 10 записаны символы пятого повторения.

При поступлении шестого повторения его символы поступают во второй решающий блок 15, куда выталкиваются так же символы четвертого повтора  из четвертого регистра сдвига 9 на место которых записываются символы

из четвертого регистра сдвига 9 на место которых записываются символы  шестого повтора.

шестого повтора.

В это же время во второй решающий блок 15 поступают символы пятого повтора  с перезаписью в пятый регистр сдвига 10. Коммутация, запись, сдвиг информации осуществляется синхроимпульсами СИ6.

с перезаписью в пятый регистр сдвига 10. Коммутация, запись, сдвиг информации осуществляется синхроимпульсами СИ6.

Во втором решающем блоке 15 при приеме шестого повтора формируется РП7 maj (Х4Х5Х6) (см. табл. 1) для чего задействованы логические элементы «И» 15-1 - 15-3, «ИЛИ» 15-7 и «И» 15-9, открываемый синхроимпульсами СИ6 для выдачи результата Z7 на выход устройства.

После приема шестого повтора в первом-третьем регистрах сдвига 6-8 хранится код числа единиц (У1У2У3) по одноименным символам пяти первых повторений сообщения. В четвертом регистре сдвига 9 записана информация  шестого повтора, а в пятом регистре сдвига 10 сохранены символы пятого повтора

шестого повтора, а в пятом регистре сдвига 10 сохранены символы пятого повтора  (см. табл. 2).

(см. табл. 2).

При приеме символов седьмого повторения оно записывается в пятый регистр сдвига 10, выталкивая символы  пятого повтора во второй решающий блок 15 и формирователь результата 14. Одновременно символы седьмого повтора

пятого повтора во второй решающий блок 15 и формирователь результата 14. Одновременно символы седьмого повтора  поступают в формирователь результата 14 и второй решающий блок 15. В формирователь результата 14 и второй решающий блок 15 также поступают символы

поступают в формирователь результата 14 и второй решающий блок 15. В формирователь результата 14 и второй решающий блок 15 также поступают символы  считываемые с четвертого регистра сдвига 9.

считываемые с четвертого регистра сдвига 9.

В то же время в формирователь результата 14 поступает, с перезаписью в первый-третий регистры сдвига 6-8, код числа единиц (У1У2У3) по одноименным символам пяти первых повторов. В результате чего в формирователь результата 14 через открытый синхроимпульсами СИ7 элемент «И» 14-14 выдается результат РП9 maj (Х1Х2Х3Х4Х5Х6Х7), а на выходе «И» 15-10 второго решающего блока 15, открытого синхроимпульсами СИ7, формируется результат Z8 - РП8 maj (X5X6X7).

Таким образом, после приема семи повторений сообщения устройство реализовало весь набор рассмотренных решающих правил (см. табл. 1). В первом-третьем регистрах сдвига 6-8 сохранен код числа единиц по одноименным символам первых пяти повторов. В четвертом регистре сдвига 9 хранятся символы шестого Х6 повтора, а в пятом регистре сдвига 10 символы седьмого Х7 повтора.

Предлагаемое устройство обладает более высокой технико-экономической эффективностью, чем известные.

Добавив минимальное количество элементов памяти на n символов в виде пятого регистра 10 с пятым переключателем 5 и введя формирователь результата 14, второй решающий блок 15, кодопреобразователь 13 был расширен набор решающих правил.

Известное устройство позволяет реализовать только шесть решающих правил (РП1 - РП6).

Ввод трех дополнительных правил РП7 - РП9 рассширяет функциональные возможности, увеличивая помехоустойчивость.

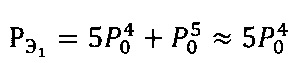

Известное устройство исправляет все трехкратные ошибки, не исправляя 5 четырехкратных и пятикратную ошибку. Следовательно

Такое допущение возможно ввиду малого значения второго слагаемого уже при Р0=10-2 (радиоканал)

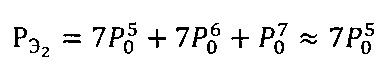

Предлагаемое устройство с предложенным набором решающих правил исправляет все 35 четырехкратных ошибок и 14 из 21 пятикратных ошибок не исправляя 7 шестикратных и одну семикратную. Следовательно

.

.

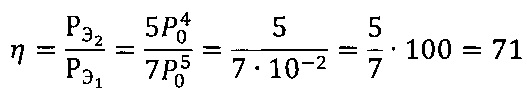

Отсюда видно, что применение данного устройства при Р0=10-2

в 71 раз уменьшает эквивалентную вероятность искажения единичного символа в итоговой комбинации. Это ведет к увеличению помехоустойчивости, т.к. во столько же раз уменьшаются потери информации.

Кроме того, разработанный набор решающих правил применим на пяти регистрах сдвига вместо шести у аналогичных устройствах.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ СИГНАЛА СТИРАНИЯ | 2001 |

|

RU2208907C2 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ | 1998 |

|

RU2152129C1 |

| Модифицированное устройство коррекции ошибок с учетом сигнала стирания | 2019 |

|

RU2711035C1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

| Устройство для приема и мажоритарного декодирования информации | 1987 |

|

SU1439750A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК ПРИ МНОГОКРАТНОМ ПОВТОРЕНИИ СООБЩЕНИЙ | 1991 |

|

RU2023348C1 |

| Устройство для приема и мажоритарного декодирования информации | 1988 |

|

SU1562977A2 |

| Устройство для приема и мажоритарного декодирования информации | 1981 |

|

SU980114A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК ПРИ МНОГОКРАТНОМ ПОВТОРЕНИИ СООБЩЕНИЙ | 1991 |

|

RU2012134C1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1981 |

|

SU1005151A2 |

Изобретение относится к телемеханике и вычислительной технике и может быть использовано в системах передачи и обработки дискретной информации для коррекции ошибок при повторении сообщения. Технический результат заключается в повышении помехоустойчивости в условиях интенсивного воздействия помех, приводящих к значительному искажению одноименных символов при повторении сообщения. В устройстве, содержащем четыре регистра сдвига с переключателями, решающий блок, синхронизатор с соответствующими связями, дополнительно введены пятый регистр сдвига с переключателем, кодопреобразователь, второй решающий блок, формирователь результата с соответствующими связями. Это позволило расширить набор решающих правил на ограниченном объеме памяти. Предложенный набор решающих правил исправляет ошибки в одноименных символах до четырехкратных включительно и пятикратных ошибок. Это ведет к увеличению помехоустойчивости, так как уменьшается эквивалентная вероятность искажения единичного символа в итоговой комбинации, что приводит к уменьшению потерь информации. 6 ил., 5 табл.

Модифицированное устройство коррекции ошибок, содержащее решающий блок, выходы которого являются выходами устройства, четыре переключателя, выходы которых соединены с информационными входами одноименных регистров сдвига, синхронизатор, тактовый вход которого является тактовым входом устройства, первый-третий выходы синхронизатора соединены соответственно с объединенными первыми управляющими входами первого переключателя и первого регистра сдвига, объединенными первыми управляющими входами второго переключателя и второго регистра сдвига, объединенными первыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока, вторыми управляющими входами первого и второго переключателей, первого и второго регистра сдвига, четвертый выход синхронизатора соединен с объединенными третьими управляющими входами второго переключателя, второго регистра сдвига, вторыми управляющими входами третьего переключателя, третьего регистра сдвига, решающего блока и первыми управляющими входами четвертого регистра сдвига и четвертого переключателя, первый информационный вход которого объединен с первыми информационными входами первого-третьего переключателей, решающего блока и является информационным входом устройства, установочные входы первого-четвертого регистров сдвига объединены с установочным входом устройства и установочным входом синхронизатора, пятый выход которого одновременно подключен ко вторым управляющим входам четвертого переключателя и четвертого регистра сдвига, третьим управляющим входам третьего, первого переключателей, третьего, первого регистров сдвига, решающего блока, четвертым управляющим входам второго переключателя и второго регистра сдвига, при этом выходы первого-четвертого регистров сдвига соединены соответственно со вторым-пятым информационными входами решающего блока и вторыми информационными входами первого-четвертого переключателей, отличающееся тем, что введены пятый переключатель, пятый регистр сдвига, формирователь результата, второй решающий блок, кодопреобразователь, при этом информационный вход пятого регистра сдвига является выходом пятого переключателя, первый информационный вход которого объединен с первыми информационными входами формирователя результата, второго решающего блока, информационным входом кодопреобразователя и информационным входом устройства, первый дополнительный вход кодопреобразователя связан со вторыми информационными входами решающего блока и формирователя результата, выходом первого регистра сдвига, второй дополнительный вход кодопреобразователя связан с третьими информационными входами решающего блока и формирователя результата, выходом второго регистра сдвига, третий дополнительный вход кодопреобразователя связан с четвертыми информационными входами решающего блока и формирователя результата, выходом третьего регистра сдвига, четвертый дополнительный вход кодопреобразователя связан с пятыми информационными входами решающего блока и формирователя результата, выходом четвертого регистра сдвига и вторым информационным входом второго решающего блока, выходы которого являются первым и вторым дополнительными выходами устройства, а третий информационный вход второго решающего блока одновременно связан со вторым информационным входом пятого переключателя и выходом пятого регистра сдвига, установочный вход которого объединен с установочным входом устройства и установочным входом кодопреобразователя, управляющий вход которого одновременно подключен к пятому выходу синхронизатора и первым управляющим входам пятого регистра сдвига, пятого переключателя, второй управляющий вход которого одновременно соединен с первым управляющим входом второго решающего блока, вторым управляющим входом пятого регистра сдвига, третьими управляющими входами четвертого переключателя, четвертого регистра сдвига и шестым выходом синхронизатора, седьмой выход которого одновременно подключен к четвертым управляющим входам первого регистра сдвига, первого переключателя, пятым управляющим входам второго регистра сдвига, второго переключателя, четвертым управляющим входам третьего регистра сдвига, третьего переключателя, четвертым управляющим входам четвертого регистра сдвига, четвертого переключателя, третьим управляющим входам пятого регистра сдвига, пятого переключателя, второму управляющему входу второго решающего блока и управляющему входу формирователя результата, выход которого является третьим дополнительным выходом устройства, при этом первый-третий выходы кодопреобразователя соединены с соответствующими третьими информационными входами первого-третьего переключателей.

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ | 1998 |

|

RU2152129C1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ СИГНАЛА СТИРАНИЯ | 2001 |

|

RU2208907C2 |

| US 6216189 B1, 10.04.2001. | |||

Авторы

Даты

2017-11-09—Публикация

2016-07-11—Подача