1

Изобретение .относится к вычислительной технике и может быть использовано в специализированных вычислительных комплексах.

Известны делительные устройства нестохастического типа, которые работают по алгоритмам операции суммирования и по алгоритмам приближенного деления fl . Такие устройства, сложны по структуре и не обеспечивают достаточной точности вычисления.

Известно устройство стахастического типа, содержащее генератор псевдослучайных чисел, две схемы сравнения, первые входы которых объединены и поключены к выходы генератора псевдослучайных случайных чисел, а выходы подключены к первым входам Четвертого и пятого ключевых элементов соответственно, при этом выход четвертого ключевого элемента подключен ко входу счетчика результата, выход которого подсоединен к первому входу третьего ключевого элемента, дополнительный счетчик делителя, вход которого подключен к первому входу устройства, а выход к вторым входам четвертого и пятого ключевых элементов, счетчик делителя, первый вход которого подключен ко второму входу устройства, а выход - к второму входу третьего ключевого элемента, выход которого является выходом устройства. Данное устройство обеспечивает более высокую точность вычисления за счет снижения автокорреляции в выходных потоках результатов сравнения Г2.

Недостатком этого устройства является то, что в случае, если делимое X больше делителя у, устройство не обеспечивает достаточной точности вычисления.

Наиболее близким техническим решением к предлагаемому изобретению является устройство, содержащее генератор псевдослучайных чисел, две схемы сравнения, первые входы которых объединены и подключены к выходу генератора псевдослучайных чисел, а выходы схем сравнения подключены к первым входам четвертого и пятого ключевых элементов соответственно, при этом выход четвертого ключевого элемента подключен к входу счетчика результата, выход которого подсоединен к первому входу третьего ключевого элемента, нительный счетчик делителя, вход

которого подключен к первому входу устройства, а выход - к вторьам входам четвертого и пятого ключевых элементов, первый счетчик делителя, первый вход которого подключен к второму входу устройства, а выход к второму входу третьего ключевого элемента, выход которого является выходом устройства, вторые входы первой и второй схем сравнения соединены с третьим и четвертым выходами устройства соответственно, шестой, седьмой и восьмой ключевые элементы, первые входы которых объединены и подключены к выходу пятого ключевого элемента, вторые входы седьмого и восьмого ключевых элементов подсоединены к нулевому и единичному выходам триггера соответственно, а второй вход шестого ключевого элемента соединен с выходом четвертого ключевого элемента, единичный и нулевой входы триггера соединены соответственно с шестым входом устройства и выходом шестого ключевого элемента, при этом выход седьмого ключевого элемента подключен к первому входу второго счетчика делителя, второй вход которого соединен с пятым входом устройства, а выход - с первым входом схемы ИЛИ, второй вход которой подключен к выходу восьмого ключевого элемента, а выход схемы ИЛИ соединен с вторым входом первого счетчика делителя. Кроме того, единичный выход триггера соединен с входом блока управления и первым входом блока элементов И, второй вход которого соединен со вторым выходом счетчика результата, а выход соединен с третьим входом первого счетчика делителя. Данное устройство обеспечивает более высокую точность вычисления в случае, если делимое х больше делителя у, за счет увеличения числа испытаний 3j .

Недостатком устройства является то, что увеличение точности при вычислении пропорции Х - 2 когда

делимое х больше делителя у, достигается за счет снижения быстродействия .

Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что д лительно-множительное устройство, содержащее первый и второй локи сравнения, генератор псевдослучайных чисел, выход которого соединен с первымивходами первого и второго блоков сравнения, первый, второй и третий ключевые элементы, первые входы первого и второго ключевых элементов соединены с выходами соответственно первого и второго блоков сравнения, счетчик результата, первый вход которого соединен с выходом первого ключевого элемента, а выход - с первым входом третьего ключевого элемента, первый счетчик делителя, первый вход которого соединен с входом генератора псевдослучайных чисел и является тактовым входом устройства, а первый выход соединен с вторыми входами первого и второго ключевых элементов второй счетчик делителя, первый вход которого является входом сомножителя устройства, второй вход соединен с выходом второго ключевого элемента, а выход соединен со вторым входом третьего ключевого элемента, выход третьего ключевого элемента является выходом устройства, дополнительно содержит первый и второй регистры, третий блок сравнения, первый, второй и третий дешифраторы, четвертый и пятый ключевые элементы, первые входы которых подключены к тактовому входу устройства, а выходы соединены с первыми входами соответственно первого и второго регистров, вторые входы первого и второго регистров соединены соответственно с вторыми входами первого счетчика делителя и счетчика результата, с третьим входом второго счетчика делителя и подключены к входу пуска устройства, третий вход первого регистра является входом делимого устройства а третий вход второго регистра является входом делителя устройства, выход первого регистра соединен с вторым входом первого блока сравнения, первым входом третьего блока сравнения и входом первого дешифратора, выход которого является выходом нулевого результата устройства, первый выход, второго регистра соединен со вторыми входами второго и третьего блоков сравнения и входом второго дешифратора, выход которого является выходом останова устройства, второй выход второго регистрасоединен с вторьми входами четвертого и пятого ключевых элементов, выход третьего блока сравнения соединен с третьими входами первого второго, четвертого и пятого ключевых элементов и первым входом третьего дешифратора, второй вход которого соединен с вторым выходом первого счетчика делителя, выход третьего дешифратора соединен с третьим входом счетчика результата.

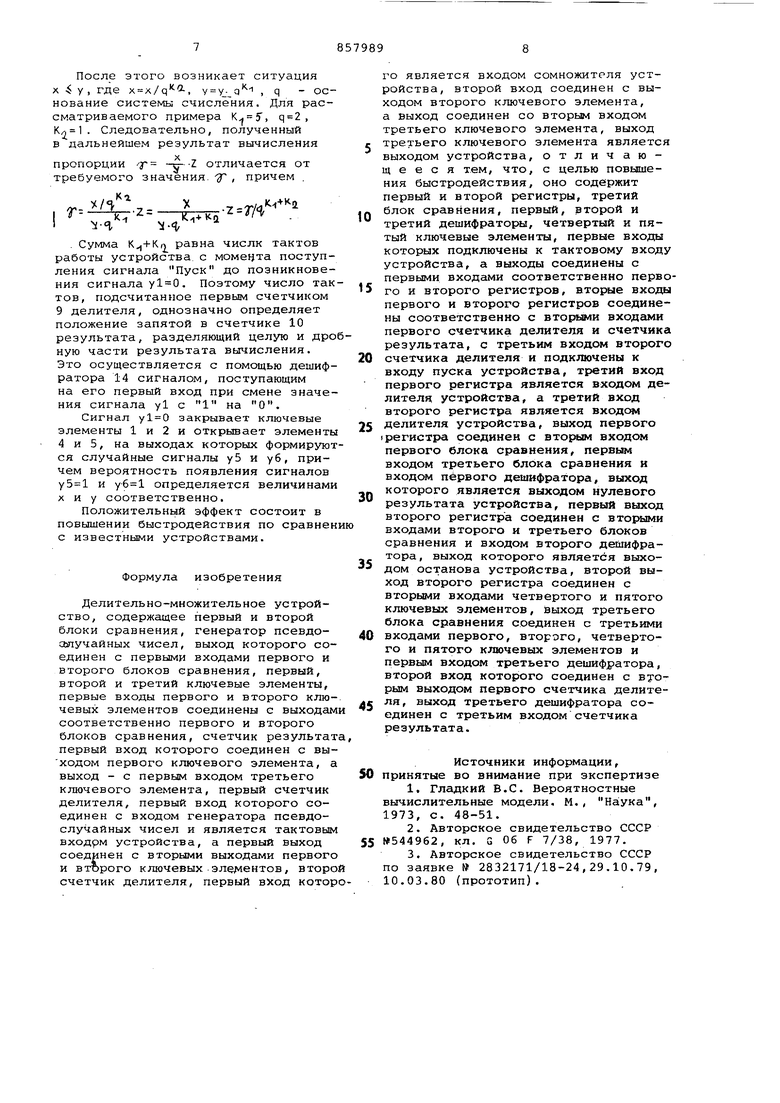

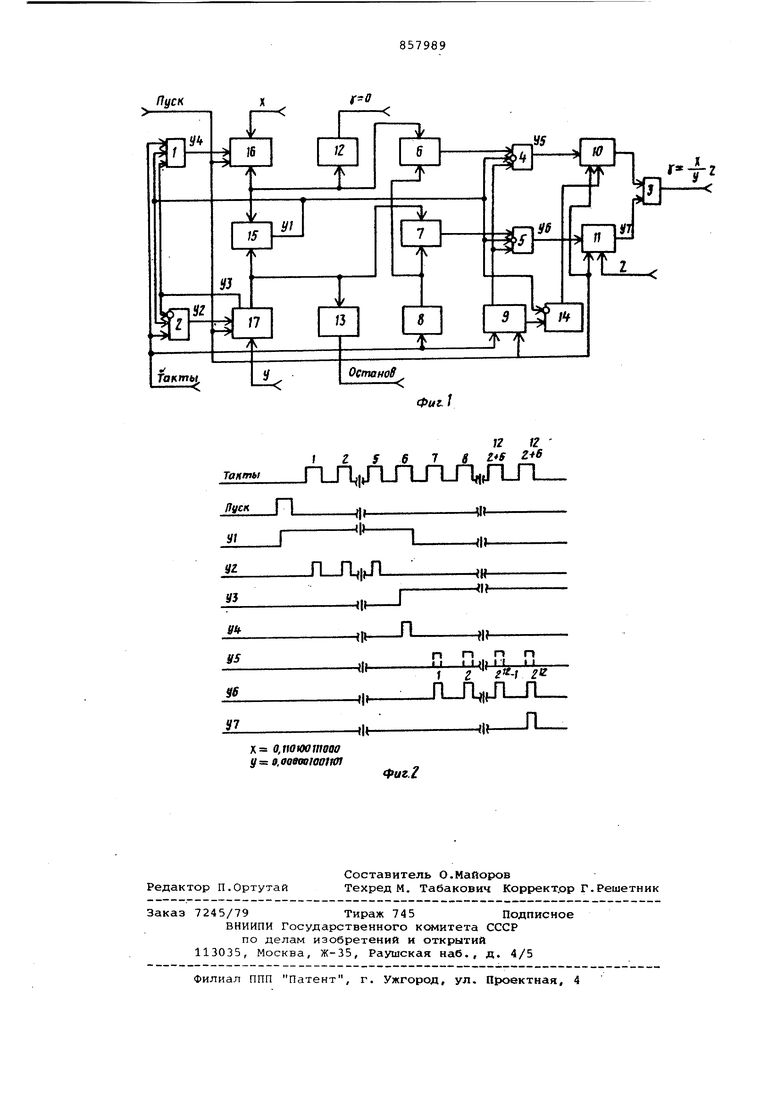

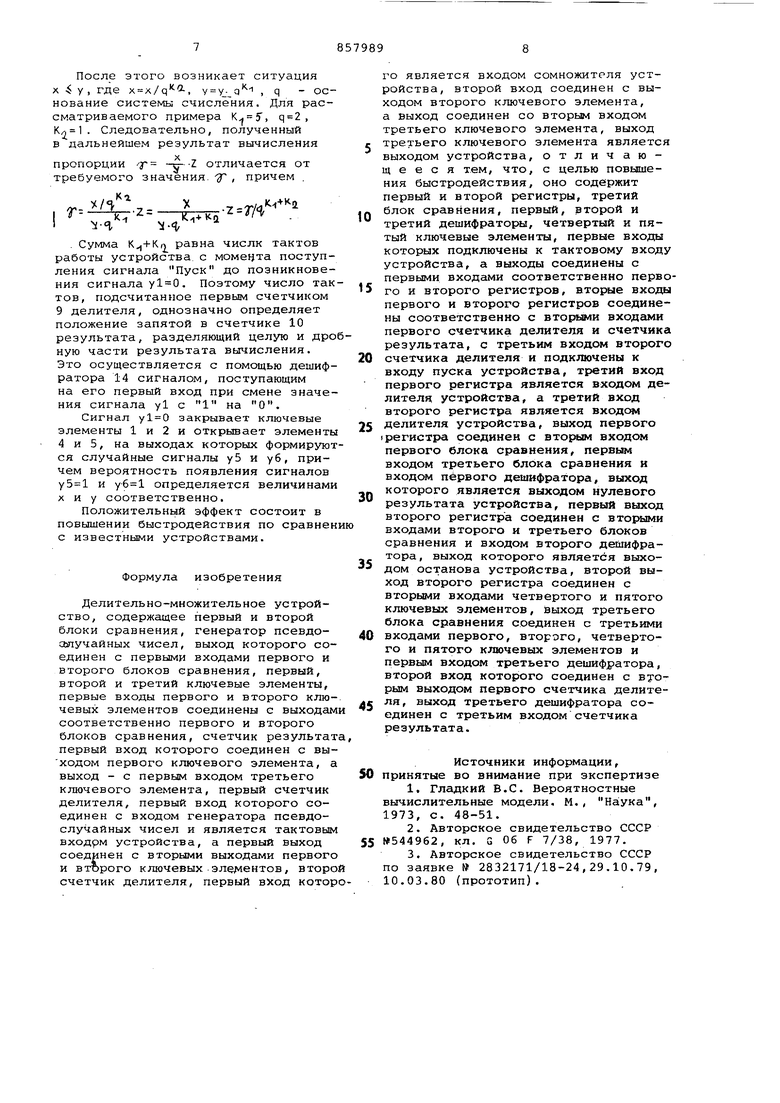

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - временные диаграммы его работы.

Устройство содержит четвертый 1, пятый 2, третий 3, первый 4 и второй 5 ключевые элементы, первый 6 и второй 7 блоки сравнения, генератор 8 псевдослучайных чисел, первый счетчик 9 делителя, счетчик 10 результата, второй счетчик 11 делителя, первый 12, второй 13 и третий 14 дешифраторы, третий блок 15 сравнекия, первый 16 и второй 17 регистры.

Выход генератора 8 псевдослучайных чисел подключен к объединенным первым входам первого 6 и второго 7 блоков сравнения, выходы которых подключены к первым входам первого

4и второго 5 ключевых элементов соответственно, при этом выход первого ключевого элемента подключен к первому входу счетчика 10 результата , выход которого соединен с первым входом третьего ключевого элемента 3, первый вход первого счетчика 9 делителя подключен к тактовому входу устройства и входу генератора 8 псевдослучайных чисел, а выход к вторым входам первого 4 и второго

5ключевых элементов. Первый вход второго счетчика 11 делителя подключен к входу сомножителя устройства, а второй вход подключен к выходу второго ключевого элемента 5. Выход второго счетчика 11 делителя подключен к второму входу третьего ключевого элемента 3, выход которого является выходом устройства. Вторые входы первого 6 и второго 7 блоков сравнения соединены с выходами соответственно первого 16 и второго 17 регистров, соответственно с входами первого 12 и второго 13 дешифраторов и соответственно с первым и вторым входами третьего блока 15 сравнения Первые входы первого 16 и второго 17 регистров подключены соответственно

к выходам четвертого 1 и пятого 2 ключевых элементов, первые входы которых объединены и подключены к тактовому входу устройства. Вторые входы четвертого 1 и пятого 2 ключевых элементов также объединены и подключены ко второму выходу второго регистра 17. Выход третьего блока 15 сравнения подключен к объединенным третьим входам первого 4, второго 5, четвертого 1 и пятого 2 ключевых элементов и первому входу третьего дешифратора 14, второй вход которого подключен ко второму выходу первого счетчика 9 делителя, а выход - к .третьему входу счетчика 10 результата. Второй вход счетчика 10 соединен с третьим входом второго счетчика 11 делителя, вторыми входами первого 16 и второго 17 регистров и подключен к входу пуска устройства в целом.

Устройство функционирует в соответствии с временной диаграммой (фиг.2). По сигналу Пуск устройство устанавливается я исходное положение: в регистр 16 заносится код числа X, в регистр 17 - код числа у , во второй счетчик 11 делителя код числа Z, а первый счетчик 9 делителя устанавливается в нулевое состояние. Тактовые сигналы, поступающие на тактовый вход устройства, синхронизируют работу генератора 8 псевдослучайных чисел, подсчитываются на первом счетчике 9 делителя и поступают на первые входы ключевых элементов 1 и 2. Блок 15 осуществляет сравнение величин х .и у, и в случае х у вырабатывает сигнал у 1 1, который закрывает ключевые элементы 4 и 5, а дешифратор 14 открывает по третьему входу ключевые элементы

0 1 и 2. Если же выполняется условие X у, блок 15 вырабатывает сигнал , который закрывает ключевые элементы 1 и 2, но открывает элементы 4 и 5, а также дешифратор 14.

5 Кроме того, в зависимости от кода числа у на выходе старшего разряда (второй выход) регистра 17 формируется сигнал , если в старшем разряде 1, либо сигнал , если

0 в старшем разряде О. Сигнал закрывает по второму входу ключевой элемент 2 и открывает по второму входу ключевой элемент 1. Сигнал открывает по второму входу ключевой элемент 2 и закрывает ключе5вой элемент 1.

Дешифратор 12 вырабатывает сигнал ТГ-О I если число . Дешифратор 13 вырабатывает сигнал Останов, если число (ситуация деления на ноль)

0 В рассматриваемом примере после занесения исходных данных на выходе блока 15 формируется сигнал , а на выходе старшего разряда (втором выходе) регистра 17 - . Поэтому

5 первый же тактовый сигнал проходит только через ключевой элемент 2, на выходе которого формируется импульсный сигнал (на выходах ключевых элементов 1, 4 и 5 сохраняются

0 сигналы , и соответственно) . Сигнал поступает на первый вход регистра 17 и осуществляет сдвиг кода числа у на один разряд влево (т.е. увеличивает делитель). Следующий тактовый импульс также

5 формирует сигнал и опять осуществляется увеличение делителя у. Так происходит (К тактов) до тех пор, пока в старшем разряде регистра 17 не окажется 1, при этом

0 . В рассматриваемом примере такая ситуация возникает только после пятого такта, т.е. . При этом асе еще , поэтому на следующем такте формируется сигнал

5 (, , ). Этот сигнал, поступая на первый в регистре 16, осуществляет сдвиг на один разряд кода числа вправо, т.е. уменьшает делимое х. Сигнал может быть

0 сформирован только один раз (К2. 0-1) при любых комбинациях значений (отличных от нуля) чисел х и у, тогда как в предельном случае формируется (п-1) раз, где п - разряд5ность регистра 17. После этого возникает ситуация X у, где x x/q2-, y y. , q - ос нование системы счисления. Для рассматриваемого примера , , . Следовательно, полученный в дальнейшем результат вычисления пропорции т отличается от требуемого значения. 3 , причем , . Сумма равна числк тактов работы устройства с момента поступления сигнала Пуск до позникновения сигнала . Поэтому число так тов, подсчитанное первым счетчиком 9 делителя, однозначно определяет положение запятой в счетчике 10 результата, разделяющий целую и др ную части результата вычисления. Это осуществляется с помощью дешиф ратора 14 сигналом, поступающим на его первый вход при смене значе ния сигнала у1 с 1 на О. Сигнал закрывает ключевые элементы 1 и 2 и открывает элемент 4 и 5, на выходах которых формирую ся случайные сигналы у5 и у6, причем вероятность появления сигналов и определяется величинам X и у соответственно. Положительный эффект состоит в повышении быстродействия по сравне с известными устройствами. Формула изобретения Делительно-множительное устройство, содержащее первый и второй блоки сравнения, генератор псевдосьлучайных чисел, выход которого со единен с первыми входами первого и второго блоков сравнения, первый, второй и третий ключевые элементы, первые входы первого и второго клю чевых элементов соединены с выхода соответственно первого и второго блоков сравнения, счетчик результа первый вход которого соединен с вы ходом первого ключевого элемента, выход - с первым входом третьего ключевого элемента, первый счетчик делителя, первый вход которого соединен с входом генератора псевдослучайных чисел и является тактовы входрм устройства, а первый выход соединен с вторыми выходами первог и второго ключевых элементов, втор счетчик делителя, первый вХод кото го является входом сомножителя устройства, второй вход соединен с выходом второго ключевого элемента, а выход соединен со вторым входом третьего ключевого элемента, выход третьего ключевого элемента является выходом устройства, отлич ающ е е с я тем, что, с целью повышения быстродействия, оно содержит первый и второй регистры, третий блок сравнения, первый, второй и третий дешифраторы, четвертый и пятый ключевые элементы, первые входы которых подключены к тактовому входу устройства, а выходы соединены с первыми входами соответственно первого и второго регистров, вторые входы первого и второго регистров соединены соответственно с вторьвли входами первого счетчика делителя и счетчика результата, с третьим входом второго счетчика делителя и подключены к входу пуска устройства, третий вход первого регистра является входом делителч устройства, а третий вход второго регистра является входсчм делителя устройства, выход первого Iрегистра соединен с вторым входом первого блока сравнения, первьш входом третьего блока сравнения и входом первого дешифратора, выход которого является выходом нулевого результата устройства, первый выход второго регистра соединен с вторыми входами второго и третьего блоков сравнения и входом второго дешифратора, выход которого является выходом останова устройства, второй выход второго регистра соединен с вторыми входс1ми четвертого и пятого ключевых элементов, выход третьего блока сравнения соединен с третьими входами первого, вторэго, четвертого и пятого ключевых элементов и первым входом третьего дешифратора, второй вход которого соединен с вторым выходом первого счетчика делителя, выход третьего дешифратора соединен с третьим входом счетчика результата. Источники информации, принятые во внимание при экспертизе 1.Гладкий B.C. Вероятностные вычислительные модели. М. , , 1973, с. 48-51. 2.Авторское свидетельство СССР №544962, кл. G 06 F 7/38, 1977. 3.Авторское свидетельство СССР по заявке 2832171/18-24,29.10.79, 10.03.80 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоканальной записи аналоговых процессов | 1985 |

|

SU1304070A1 |

| Устройство для формирования псевдослучайных сигналов | 1979 |

|

SU995292A1 |

| Генератор псевдослучайных чисел | 1984 |

|

SU1239844A1 |

| Вероятностный интегратор | 1980 |

|

SU900283A1 |

| Устройство синхронизации источников сейсмических сигналов | 1991 |

|

SU1787278A3 |

| Делительно-множительное устройство | 1980 |

|

SU868757A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Вероятностное делительно-множи-ТЕльНОЕ уСТРОйСТВО | 1979 |

|

SU834708A1 |

| Генератор псевдослучайных чисел | 1986 |

|

SU1324091A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1980 |

|

SU888119A1 |

12 12 г f 6 7 в

Авторы

Даты

1981-08-23—Публикация

1979-12-06—Подача