10 6

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения уравнения Кеплера | 1989 |

|

SU1615737A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для вычисления тригонометрического тангенса | 1986 |

|

SU1334144A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для потенцирования | 1990 |

|

SU1815635A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Множительно-делительное арифметическое устройство | 1986 |

|

SU1381491A1 |

| МАТРИЧНЫЙ СПЕЦПРОЦЕССОР | 1994 |

|

RU2079879C1 |

Изобретение относится к цифровой вычислительной технике и может быть применено в специализированных вычислительных устройствах, используемых в системах автоматического управления. Целью изобретения является повышение быстродействия работы устройства в следящем режиме. Устройство содержит входы 8, 9 первого и второго операндов устройства, входы 10 и 11 третьего и четвертого операндов устройства, вычитатели 1 и 2, накапливающий сумматор 7, сумматор 3 и умножители 5 и 6. Сущность изобретения состоит в создании быстродействующего цифрового устройства для выполнения множительно- делительной операции при одновременном выполнении операции суммирования с использованием итерационного метода реализации, позволяющего отслеживать изменения входных величин в процессе непрерывного формирования результата посредством организации структуры с отрицательной обратной связью для выработки компенсирующих воздействий при получении результата и с повышением благодаря этому быстродействия при отработке приращений. Цель изобретения достигнута за счет введения умножителей, сумматора и новых связей. 2 ил. СО С

V CLK

К о//о

w

Фиг.1

Изобретение относится к вычислительной технике и может быть применено в специализированных вычислительных устройствах, используемых в системах автоматического управления.

Известно устройство для умножения и деления, содержащее генератор, два делителя частоты, два счетчика и выполняющее операции умножения и деления одновременно. Начальная установка устройства сводится к вводу в первый счетчик дополнительного кода первого сомножителя А и установке кодов второго сомножителя В и делителя С в делители частоты в качестве коэффициентов деления. Результат множи- тельно-делительной операции устанавливается во втором счетчике за время t АВТ0 (где То - период следования импульсов генератора).

Недостатками устройства являются низкое быстродействие и малая помехоустойчивость, обусловленную отсутствием следящего режима работы.

Известно быстродействующее множи- тельно-делительное устройство, выполняющее операции умножения и деления одновременно и содержащее три регистра, три сумматора, блок управления. Устройство формирует результат преобразования с n-разрядными операндами за g шагов, где 1 д п.

Недостатком устройства является низкая помехоустойчивость, обусловленная отсутствием следящего режима работы.

Наиболее близким к предлагаемому является устройство, которое осуществляет множительно-делительные операции с использованием принципа слежения за изменением входных величин, что ускоряет процесс при работе в следящем режиме. Повышается помехоустойчивость устройства, поскольку оно одновременно выполняет дополнительную функцию суммирования.

Устройство-прототип осуществляет множительно-делительную операцию и one

X Y

рацию суммирования вида Z

V

+ We

-

использованием принципа слежения за изменением входных величин, т.е. производит операции не с самими входными величинами, а с их приращениями фиксированно, с запоминанием приращений всех аргументов вне зависимости от их величин.

Алгоритм функционирования определен при помощи вычисления конечно-разностного уравнения вида

Y + AY V + AV

ДХ +

X

V + AV

AY +

+ WAVAV + AWгде X, Y, V, W - величины операндов; 5АХ, AY, AV, AW - приращения операндов;

AZ - приращение результата. Множительно-делительная операция осуществляется за 4 такта. 10 Быстродействие устройства определяется следующим образом:

Греш 71 + Т2 + Тз

АХ

V +AV

+

AY

+

AV

V+AV V+AV

0

5

0

5

0

5

0

5

При максимальных приращениях входных величин, т.е. при предыдущих значениях V 0, и их приращениях АХ X макс, AY YMSKC , А V Умакс, AW WMaKc быстродействие характеризуется величиной греш 3 ед. времени, причем единица времени равна 2П периодам Тс тактовой частоты. Тогда Греш 3(2ПТ0), где п - разрядность операндов. Максимальное время решения определяется при Х Y V 1, AV О, АХ AY 2n - 2. В этом случае греш (2П+1 - 4) х х (2ПТ0). Например, если п 10, то греш 2093056Т0.

Недостатком прототипа является низкое быстродействие, вызванное необходимостью преобразования в процессе вычислений параллельного кода в частоту.

Цель изобретения - повышение быстродействия работы устройства в следящем режиме.

Поставленная цель достигается тем, что в цифровое множительно-делительное устройство, содержащее два вычитателя и сумматор, причем выход сумматора соединен с выходом результата устройства и входом уменьшаемого первого вычитателя, вход вычитаемого которого соединен с входом первого слагаемого сумматора, введены два умножителя и накапливающий сумматор, причем входы первого и второго операндов устройства соединены с входами первого и второго сомножителей соответственно первого умножителя, выход которого соединен с входом уменьшаемого второго вычитателя, вход вычитаемого которого соединен с выходом второго умножителя, входы первого и второго сомножителей которого соединены с входом третьего операнда устройства и выходом первого вычитателя устройства, выход второго вычитателя соединен с информационным входом накапливающего сумматора, выход которого соединен с входом второго слагаемого сумматора, вход первого слагаемого которого соединен с входом четвертого операнда устройства, вход синхронизации которого соединен с входом разрешения записи накапливающего сумматора.

Сущность изобретения состоит в создании быстродействующего цифрового устройства для выполнения множительно- делительной операции при одновременном выполнении операции суммирования с использованием итерационного метода реализации, позволяющего отслеживать изменения входных величин в процессе непрерывного формирования результата посредством организации структуры с отрицательной обратной связью для выработки компенсирующих воздействий при получении результата и с повышением благодаря этому быстродействия при отработке приращений.

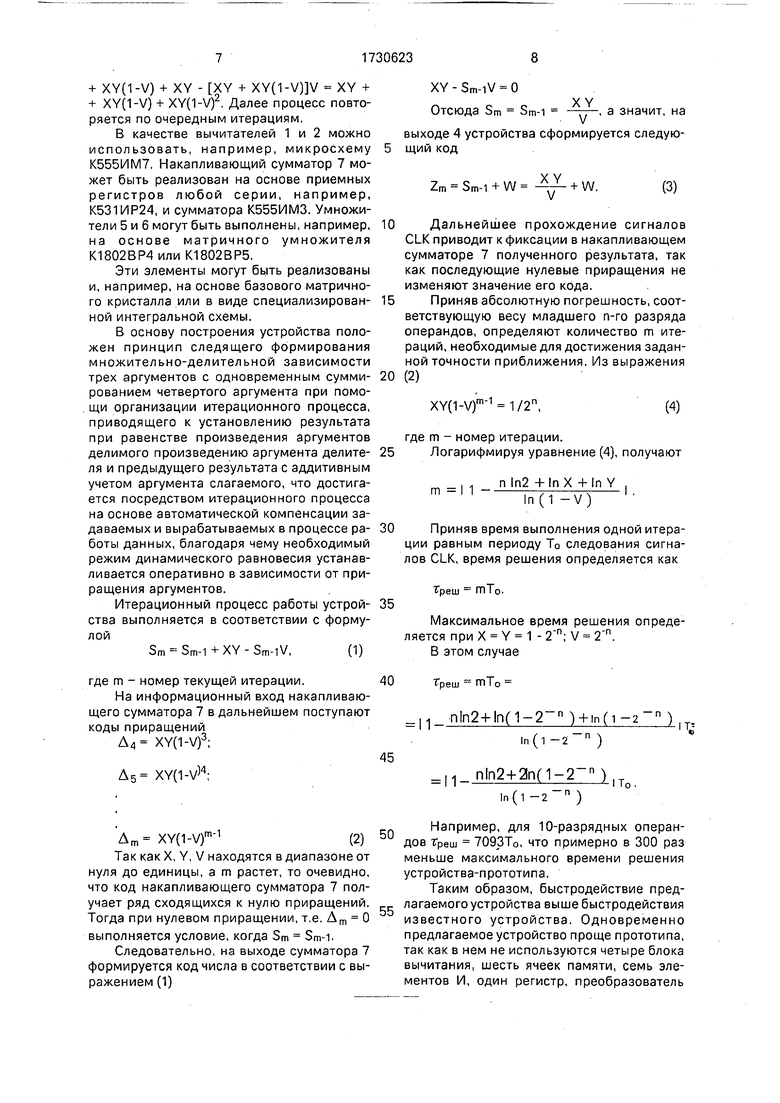

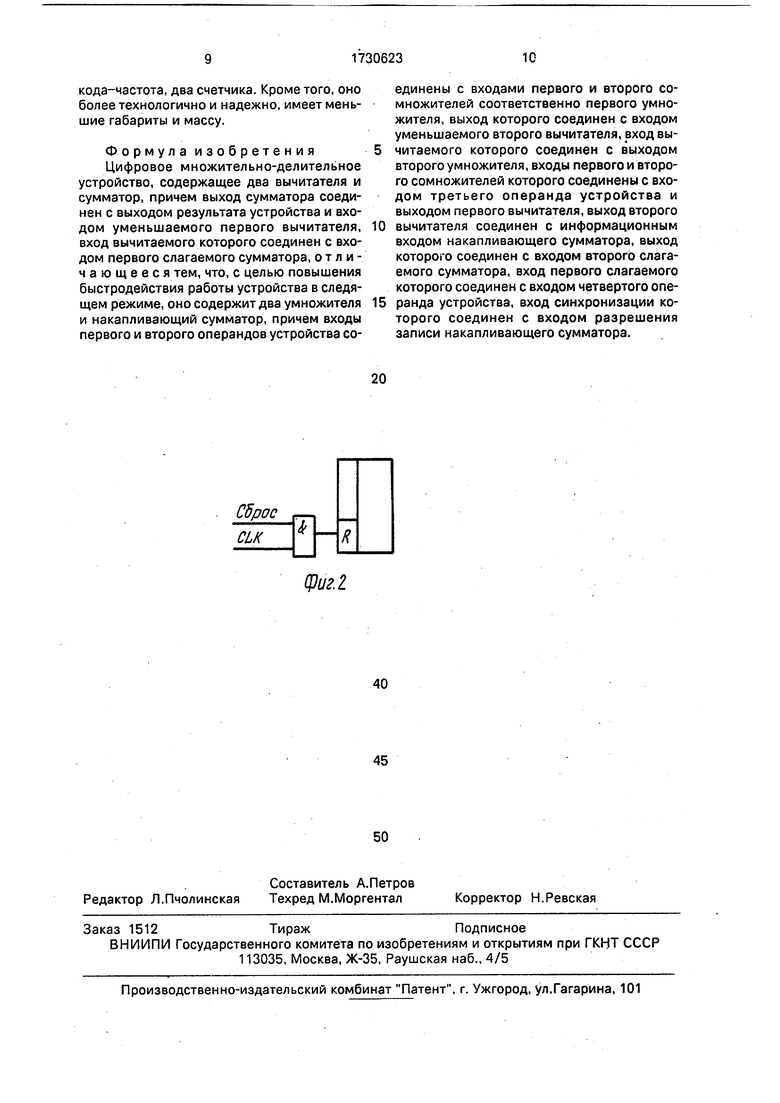

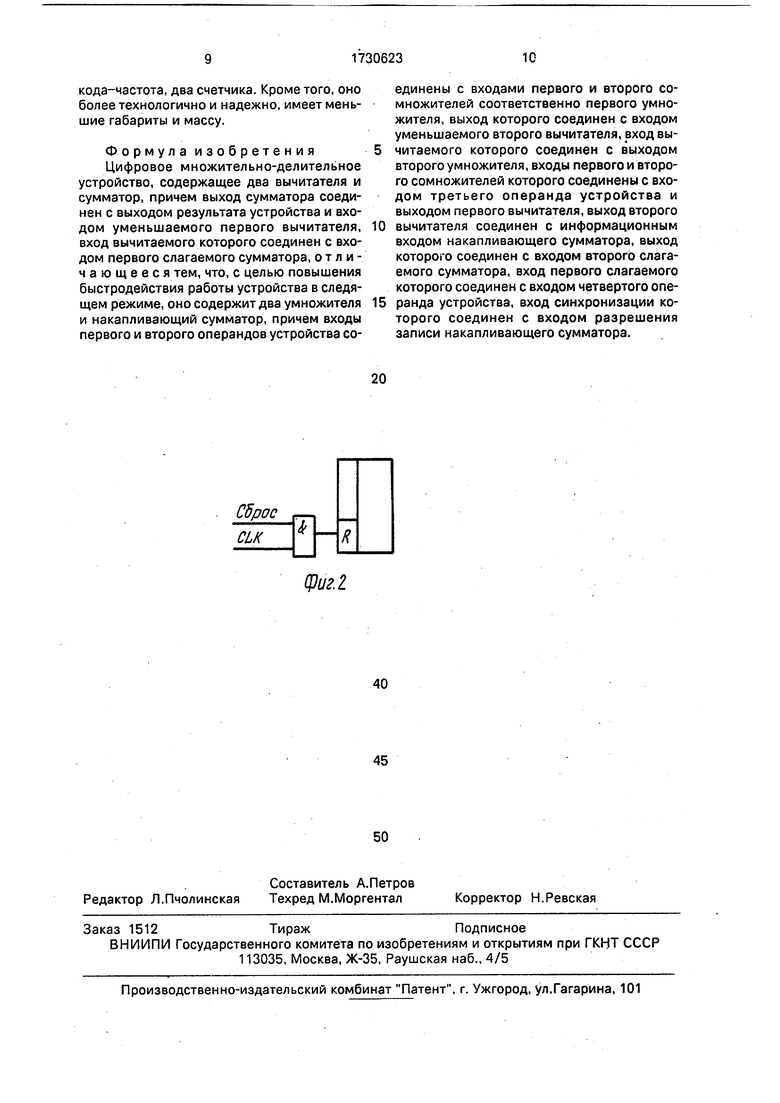

На фиг. 1 изображена схема предлагаемого устройства; на фиг. 2 - накапливающий сумматор.

Устройство содержит два вычитателя 1 и 2 и сумматор 3, причем выход сумматора 3 соединен с выходом 4 результата устройства и входом уменьшаемого вычитателя 1, вход вычитаемого которого соединен с входом первого слагаемого сумматора 1, два умножителя 5 и 6 и накапливающий сумматор 7, причем входы 8 и 9 первого и второго операндов устройства соединены с входами первого и второго сомножителей соответственно умножителя 5, выход которого соединен с входом уменьшаемого вычитателя 2, вход вычитаемого которого соединен с выходом умножителя 6, входы первого и второго сомножителей которого соединены с входом 10 третьего операнда устройства и выходом вычитателя 1 устройства, выход вычитателя 2 соединен с информационным входом накапливающего сумматора 7, выход которого соединен с входом второго слагаемого сумматора 3, вход первого слагаемого которого соединен с входом 11 четвертого операнда устройства, вход 12 синхронизации которого соединен с входом разрешения записи накапливающего сумматора 7.

Устройство работает следующим образом.

На входах 8-11 присутствуют п-разряд- ные коды типа 8-4-2-1 операндов X, Y, V, W соответственно, причем О Х 1;0 Y Y . С входа 12 на вход разрешения записи накапливающего сумматора 7 поступают сигналы синхронизации CLK.

Пусть в начальный момент времени разряды накапливающего сумматора 7 находятся в нулевом состоянии. При необходимости возможна, например, организация

процесса сброса накапливающего сумматора синхронно с сигналом CLK, так как показано на фиг. 2. Тогда на выходе сумматора 3, выполненного, например, в виде комбинационного сумматора, и выходе 4 устройства формируется код числа W, а на выходе вычитателя 1 - О. При этом с выхода умножителя б, выполненного, как и умножитель 5, например, на базе БИС матричного умножителя К1802ВР4 или К1802ВР5, на вход

вычитаемого вычитателя 2 поступит код О. На входе уменьшаемого вычитателя 2 присутствует код XY, причем с выходов умножителей 5 и 6 снимаются старшие п разрядов кодов произведений. При этом на информационном входе накапливающего сумматора 7 присутствует код числа AI XY и на его выходе сформируется код числа Si XY no переднему фронту сигнала CLK. Длительность сигнала CLK должна быть не меньше

времени задержки накапливающего сумматора 7, а период его следования - не меньше суммарной задержки элементов б, 2, 7, 3 и 1.

В результате первой итерации на выходе 4 устройства и выходе вычитателя 1 формируются коды чисел Zi XY + W и XY соответственно.

При этом с выхода умножителя б на вход вычитаемого вычитателя 2 поступает код

XYV, а на его выходе формируется код приращения Дг XY - XYV XY(1-V), поступающего на информационный вход накапливающего сумматора 7. Этот код суммируется с содержимым накапливающего сумматора 7 и с приходом сигнала CLK на выходе последнего устанавливается код S2 Si+ A2 XY + XY(1-V).

Таким образом, на выходе 4 устройства в результате второй итерации формируется

код Z2 S2 + W XY + XY - XYV + W XY + + XY(1-V) + W.

В процессе выполнения третьей итерации с выхода вычитателя 1 на вход второго сомножителя умножителя 6 поступает код

Z2 - W XY + XY(1-V). Тогда на входе вычитаемого вычитателя 2 появляется код числа (Z2-WJV XY + XY(1-V)V. В результате работы вычитателя 2 на информационный вход сумматора 7 поступает код приращения Дз XY - XY + XY(1-V)V XY(1-V)2 и суммируется с его кодом. По переднему фронту следующего сигнала CLK результат суммирования Зз появится на выходе накапливающего сумматора Зз $2 + Аз XY +

+ XY(1-V) + XY - XY + XY(1-V)V XY + + XY(1-V) + XY(1-V)2. Далее процесс повторяется по очередным итерациям.

В качестве вычитателей 1 и 2 можно использовать, например, микросхему К555ИМ7. Накапливающий сумматор 7 может быть реализован на основе приемных регистров любой серии, например, К531ИР24, и сумматора К555ИМЗ. Умножители 5 и 6 могут быть выполнены, например, на основе матричного умножителя К1802ВР4или К1802ВР5.

Эти элементы могут быть реализованы и, например, на основе базового матричного кристалла или в виде специализированной интегральной схемы.

В основу построения устройства положен принцип следящего формирования множительно-делительной зависимости трех аргументов с одновременным суммированием четвертого аргумента при помощи организации итерационного процесса, приводящего к установлению результата при равенстве произведения аргументов делимого произведению аргумента делителя и предыдущего результата с аддитивным учетом аргумента слагаемого, что достигается посредством итерационного процесса на основе автоматической компенсации задаваемых и вырабатываемых в процессе работы данных, благодаря чему необходимый режим динамического равновесия устанавливается оперативно в зависимости от приращения аргументов.

Итерационный процесс работы устройства выполняется в соответствии с формулой

Sm Sm-l+XY-Sm-lV,(1)

где m - номер текущей итерации.

На информационный вход накапливающего сумматора 7 в дальнейшем поступают коды приращений

Д4 XY(1-V)3;

А5 XY(1-V)4;

Дт XYO-Vf1(2)

Так как X, Y, V находятся в диапазоне от нуля до единицы, a m растет, то очевидно, что код накапливающего сумматора 7 получает ряд сходящихся к нулю приращений. Тогда при нулевом приращении, т.е. Ат О

выполняется условие, когда Sm Sm-1.

Следовательно, на выходе сумматора 7 формируется код числа в соответствии с выражением (1)

X Y

V

-, а значит, на

выходе 4 устройства сформируется следую- 5 щий код

Zm Sm-1 + W

.jX-X V

+ W.

(3)

Дальнейшее прохождение сигналов CLK приводит к фиксации в накапливающем сумматоре 7 полученного результата, так как последующие нулевые приращения не изменяют значение его кода.

Приняв абсолютную погрешность, соответствующую весу младшего n-го разряда операндов, определяют количество m итераций, необходимые для достижения заданной точности приближения. Из выражения

(2)

XY(1-V) 1/2n,

(4)

где m - номер итерации. 25 Логарифмируя уравнение (4), получают

m l 1

n In2 +lnX +ln Y

In (1 -V)

30Приняв время выполнения одной итерации равным периоду Т0 следования сигналов CLK, время решения определяется как

Треш тТо.

Максимальное время решения определяется при X Y 1 - V . В этом случае

Треш тТо

и nln2+ln( )+m( ) |Т.

,п(1-2-)

м nln2 + 2n( ) 1Т

| |i j Г Q .

1п(1-2-П)

Например, для 10-разрядных операндов Треш 7093Т0, что примерно в 300 раз меньше максимального времени решения устройства-прототипа.

Таким образом, быстродействие пред- латаемого устройства выше быстродействия известного устройства. Одновременно предлагаемое устройство проще прототипа, так как в нем не используются четыре блока вычитания, шесть ячеек памяти, семь элементов И, один регистр, преобразователь

кода-частота, два счетчика. Кроме того, оно более технологично и надежно, имеет меньшие габариты и массу.

Формула изобретения Цифровое множительно-делительное устройство, содержащее два вычитателя и сумматор, причем выход сумматора соединен с выходом результата устройства и входом уменьшаемого первого вычитателя, вход вычитаемого которого соединен с входом первого слагаемого сумматора, отличающееся тем, что, с целью повышения быстродействия работы устройства в следящем режиме, оно содержит два умножителя и накапливающий сумматор, причем входы первого и второго операндов устройства соСдрос JT

CLK

(Риг. 2

0

5

единены с входами первого и второго сомножителей соответственно первого умножителя, выход которого соединен с входом уменьшаемого второго вычитателя, вход вычитаемого которого соединен с выходом второго умножителя, входы первого и второго сомножителей которого соединены с входом третьего операнда устройства и выходом первого вычитателя, выход второго вычитателя соединен с информационным входом накапливающего сумматора, выход которого соединен с входом второго слагаемого сумматора, вход первого слагаемого которого соединен с входом четвертого операнда устройства, вход синхронизации которого соединен с входом разрешения записи накапливающего сумматора.

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ-ДЕЛЕНИЯ | 0 |

|

SU392495A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Множительно-делительное устройство | 1974 |

|

SU553614A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровое множительно-делительное устройство | 1978 |

|

SU742935A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-30—Публикация

1990-03-11—Подача