Область техники, к которой относится изобретение

Настоящее изобретение относится к тестированию больших интегральных схем (БИС), более точно, к конфигурации схемы и способу тестирования межсоединений БИС на уровне плат в реальных условиях эксплуатации.

Уровень техники

При производстве платы, на которой установлена специализированная интегральная микросхема (ASIC, от английского - Application Specific Integrated Circuit), разработанная и изготовленная для выполнения конкретной задачи, широко применяют периферийное сканирование с использованием системы отладки JTAG (Объединенная рабочая группа по автоматизации тестирования, от английского - Joint Test Automation Group), чтобы проверить, не является ли плата дефектной. В случае, когда межсоединения на уровне плат тестируют с использованием JTAG, тестирование проводят только с использованием схемы JTAG без использования схемы (далее - схема пользователя), которая обеспечивает предполагаемую работу ASIC. Это позволяет осуществлять тестирование в целом независимо от конфигурации схемы пользователя. Существует метод тестирования, известный как EXTEST, являющийся частью стандарта IEEE1149 (смотри, например, непатентный документ [1]: IEEE STD1149.1-1990, "IEEE Standard Test Access Port and Boundary-Scan Architecture", публикация IEEE, Inc., 345 East 47th Street, NY 10017, USA).

В настоящее время в качестве интерфейса ввода-вывода для высокоскоростной ASIC в основном используют интерфейс с быстродействующей памятью или интерфейс синхронного с источником типа. Синхронный с источником интерфейс (схема ввода-вывода) применим для высокоскоростной работы и используется в синхронных динамических оперативных запоминающих устройствах (SDRAM, от английского - Synchronous Dynamic Random Access Memories), таких как SDRAM с двойной скоростью (DDR, от английского - Double Data Rate) и SDRAM с четвертой скоростью (QDR, от английского - Quad Data Rate), и различных высокоскоростных шинах центрального процессора. Вместе с данными микросхемы этот интерфейс передает от микросхемы на передающей стороне микросхеме на принимающей стороне синхроимпульс для защелкивания данных микросхемы.

При тестировании такой схемы, работающей с высокой скоростью, считается важным также провести тест в реальных условиях эксплуатации (проверку на рабочей частоте), а также статический тест, такой как EXTEST, чтобы проверить, правильно ли работает логическая схема.

Тестирование на рабочей частоте синхронного с источником интерфейса на уровне плат традиционно проводят посредством теста системного уровня с использованием тестовой программы, разработанной разработчиком печатных плат, разработчиком системы и разработчиком микрокода для ASIC.

Раскрытие изобретения

Задачи изобретения

Как упомянуто выше, предпочтительно, чтобы тестирования на рабочей частоте осуществлялось на синхронном с источником интерфейсе ASIC, работающей с высокой скоростью. Тем не менее, традиционно отсутствует общий метод тестирования на рабочей частоте данного интерфейса на уровне плат.

Кроме того, хотя практическое тестирование на рабочей частоте осуществляют на уровне плат посредством теста системного уровня, как это упомянуто выше, в этом случае возникает следующая проблема. Если в результате теста системного уровня обнаружен отказ, необходимо произвести отладку. Вместе с тем, если проблема заключается в синхронном с источником интерфейсе, эту отладку нелегко осуществить. Это объясняется тем, что из-за неисправности интерфейса искажены только данные, а регистр состояния в микросхеме является нормальным. Иными словами, о наличии проблемы говорят только данные наблюдений, а управляющий сигнал действует должным образом. Из-за этого крайне сложно выявить причину проблемы.

С учетом перечисленных проблем задачей настоящего изобретения является создание общего алгоритма (конфигурации схемы и операционного метода) тестирования на уровне плат работы синхронного с источником интерфейса внутри ASIC на рабочей частоте без применения теста системного уровня.

Решение поставленной задачи

Для решения упомянутой задачи настоящее изобретение может быть реализовано в виде микрокомпьютера, имеющего следующую конфигурацию. В микрокомпьютере установлено множество интегральных схем (ИС), соединенных друг с другом синхронным с источником интерфейсом. ИС на стороне для передачи данных через синхронный с источником интерфейс включает: схему фазовой автоподстройки частоты (ФАПЧ) для передачи исполнительного синхроимпульса в процессе реальной работы, первый триггер для передачи тестовых данных в соответствии с исполнительным синхроимпульсом, передаваемым схемой ФАПЧ, и второй триггер для передачи синхронного с источником синхроимпульса в соответствии с исполнительным синхроимпульсом, передаваемым схемой ФАПЧ. ИС на стороне приема данных через синхронный с источником интерфейс имеет третий триггер для сбора тестовых данных, передаваемых первым триггером, в соответствии с синхроимпульсом, передаваемым вторым триггером.

Более точно, ИС на передающей стороне дополнительно включает схему генерирования сдвоенных импульсов для извлечения двухимпульсных сигналов из исполнительных синхроимпульсов, передаваемых схемой ФАПЧ. Кроме того, первый триггер передает тестовые данные в соответствии с двухимпульсными сигналами, извлеченными из схемы генерирования сдвоенных импульсов. Аналогичным образом второй триггер передает синхроимпульс в соответствии с двухимпульсными сигналами, извлеченными из схемы генерирования сдвоенных импульсов.

Еще точнее, первый триггер ИС на передающей стороне передает тестовые данные с задержкой, равной полупериоду двухимпульсных сигналов относительно синхроимпульса, передаваемого вторым триггером. В качестве альтернативы, первый триггер передает тестовые данные на фронте того же синхроимпульса, что и синхроимпульс, передаваемый вторым триггером. В последнем случае ИС на принимающей стороне имеет средство задержки, такое как схема DDL (цифровая линия задержки, от английского - digital delay line) для передачи принимаемого синхроимпульса третьему триггеру с задержкой π/2.

Первый триггер ИС на передающей стороне может состоять из триггера с раздельными входами (RS-триггера). В таком случае ИС на передающей стороне дополнительно включает РЕГИСТР ТЕСТОВЫХ ДАННЫХ (TDR, от английского - TEST DATA REGISTER) JTAG (далее - JTAG_TDR, смотри непатентный документ [1]) и обеспечивает сохранение тестовых данных первым триггером путем установки или сброса первого триггера в соответствии со значением, сохраненным этим JTAG_TDR. Возможна другая конфигурация, при которой тестовые данные вводят в первый триггер путем сканирования трактов данных со сдвигом через тракт сканирования, образованный первым триггером ИС на передающей стороне.

Кроме того, в настоящем изобретении также предложен способ тестирования микрокомпьютера. На тестируемом микрокомпьютере установлено множество ИС, соединенных друг с другом синхронным с источником интерфейсом. Способ включает стадию, на которой в ИС на стороне передачи данных через синхронный с источником интерфейс вводят исходные значения первого триггера для передачи данных и второго триггера для передачи синхроимпульса, и стадию, на которой передают синхросигнал схемы ФАПЧ для передачи исполнительного синхроимпульса в процессе реальной работы, после чего первый триггер и второй триггер соответственно передают данные исходных значений и синхроимпульс. Способ также включает стадию, на которой третий триггер для приема данных ИС на стороне приема данных через синхронный с источником интерфейс осуществляет сбор исходных значений, передаваемых первым триггером, в соответствии с синхроимпульсом, передаваемым вторым триггером.

В данном случае стадия ввода исходных значений в первый и второй триггеры включает стадию, на которой в каждом из JTAG_TDR, которые согласованы соответственно с первым и вторым триггерами, сохраняют заданное значение, и стадию, на которой JTAG_TDR в соответствии с сохраненными в них значениями осуществляют установку или сброс первого триггера и второго триггера для ввода исходных значений в первый и второй триггеры. В качестве альтернативы, на стадии ввода исходных значений в первый и второй триггеры исходные значения вводят путем сканирования трактов тестовых данных со сдвигом через тракт сканирования относительно первого и второго триггеров, образующих тракт сканирования.

Кроме того, в настоящем изобретении также предложен следующий способ тестирования микрокомпьютера, который включает множество ИС, соединенных синхронным с источником интерфейсом. Данный способ тестирования включает стадию, на которой триггер на стороне передачи данных через синхронный с источником интерфейс принимает и сохраняет тестовые данные, стадию, на которой передают синхросигнал схемы ФАПЧ для передачи исполнительного синхроимпульса в процессе реальной работы, после чего передают тестовые данные, сохраненные в триггере на передающей стороне, и синхронный с источником синхроимпульс и стадию, на которой триггер на стороне приема данных через синхронный с источником интерфейс осуществляет сбор тестовых данных в соответствии с синхроимпульсом.

В данном случае стадия приема тестовых данных триггером на передающей стороне включает стадию, на которой сохраняют заданное значение в JTAG_TDR, соответствующем триггеру на передающей стороне, и стадию, на которой в соответствии со значением, сохраненным в JTAG_TDR, осуществляют установку или сброс триггера на передающей стороне, которому соответствует JTAG_TDR, чтобы триггер на передающей стороне сохранил тестовые данные. В качестве альтернативы, на стадии приема тестовых данных триггером на передающей стороне триггер на передающей стороне сохраняет тестовые данные путем сканирования трактов тестовых данных со сдвигом через тракт сканирования относительно триггера на передающей стороне, образующего тракт сканирования.

Технические результаты изобретения

Согласно настоящему изобретению с описанной выше конфигурацией обмен данными между микросхемами, соединенными синхронным с источником интерфейсом внутри ASIC, может осуществляться в соответствии с тем же синхросигналом, что и в процессе реальной работы. Затем получают результат обмена данными и оценивают с использованием JTAG_TDR для изучения в микросхеме на принимающей стороне. Это позволяет проводить тестирование на рабочей частоте на уровне плат без применения теста системного уровня.

Кроме того, данный способ тестирования позволяет отдельно оценивать данные, которые передают по каждому каналу передачи. Соответственно, в отличие от теста системного уровня при обнаружении проблемы можно легко установить ее причину.

Краткое описание чертежей

Далее подробно описаны предпочтительные варианты осуществления настоящего изобретения со ссылкой на приложенные чертежи, на которых показано:

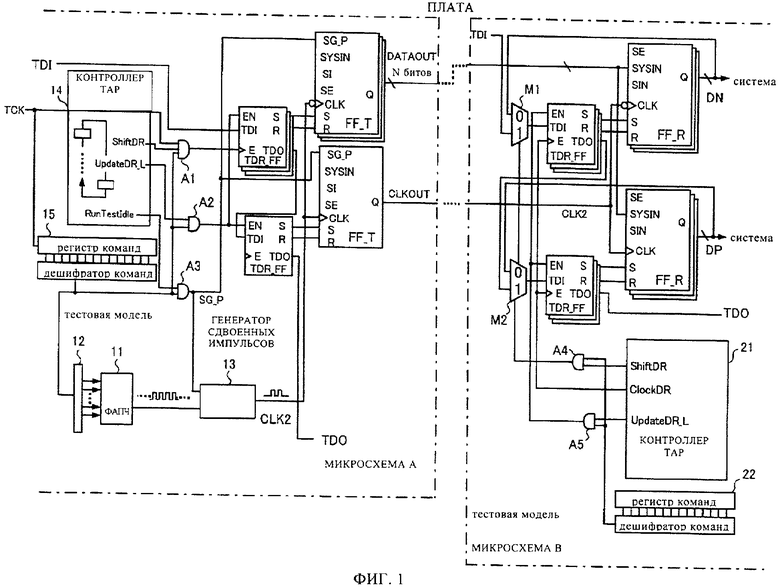

на фиг.1 - полная конфигурация синхронной с источником схемы, к которой применим первый вариант осуществления настоящего изобретения,

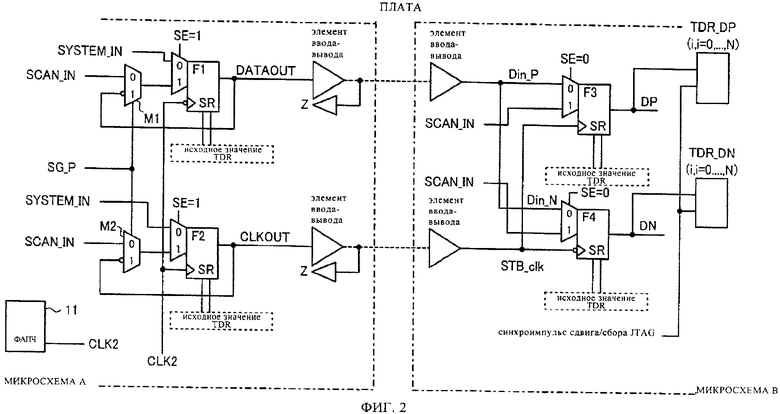

на фиг.2 - основные базовые элементы показанной на фиг.1 схемы для синхронизации с источником, являющиеся предметом варианта осуществления,

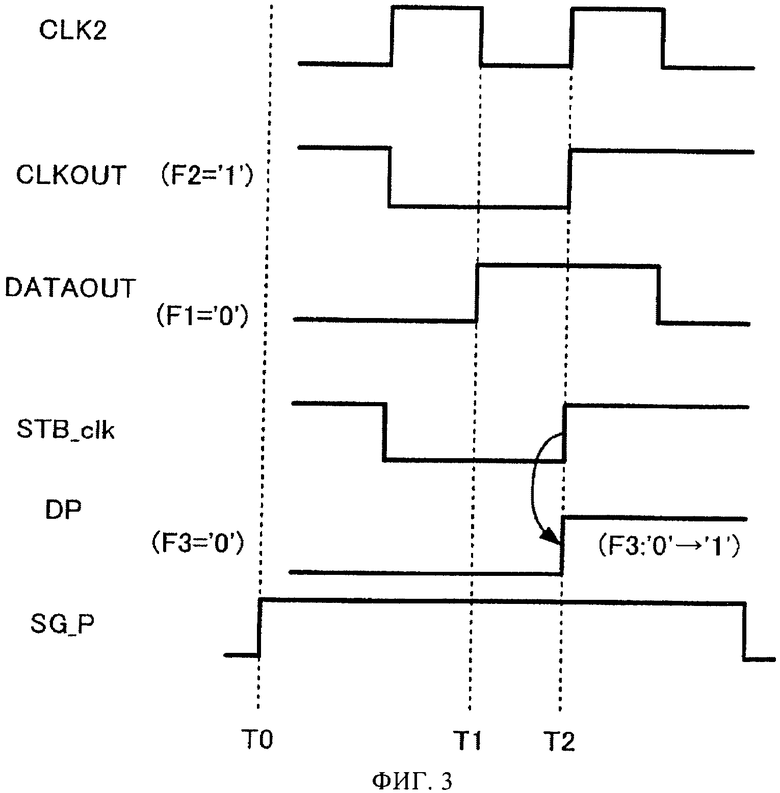

на фиг.3 - диаграмма, иллюстрирующая формы сигнала в триггере F3, показанном на фиг.2,

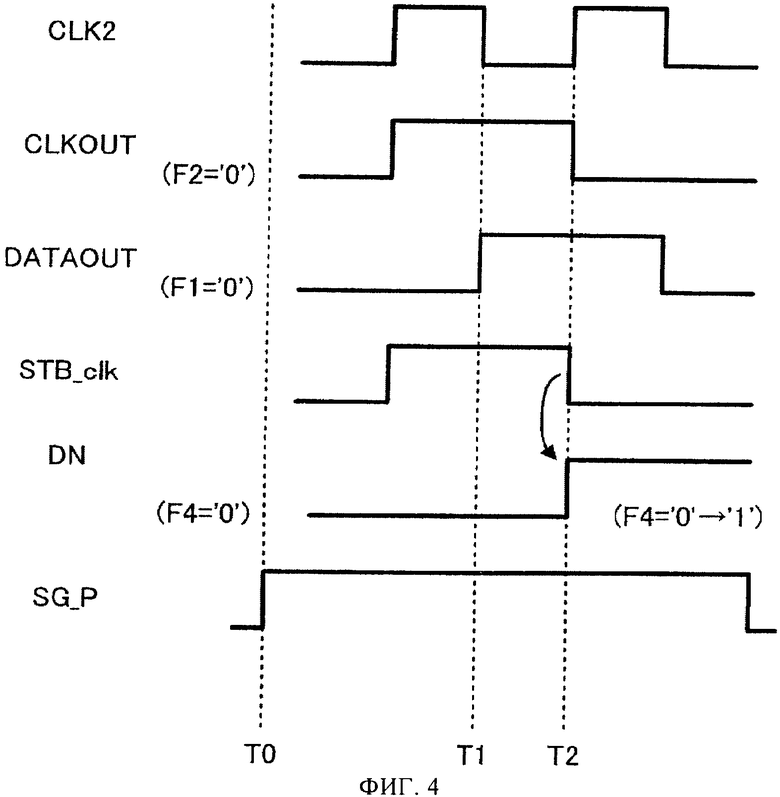

на фиг.4 - диаграмма, иллюстрирующая формы сигнала в триггере F4, показанном на фиг.2,

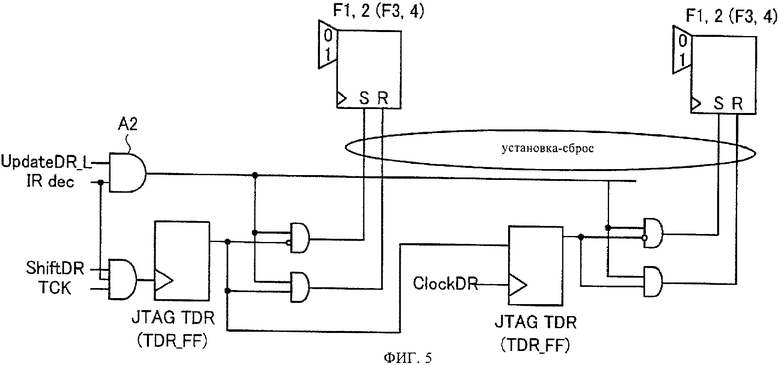

на фиг.5 - диаграмма, иллюстрирующая конфигурацию схемы инициализации триггеров микросхемы согласно варианту осуществления,

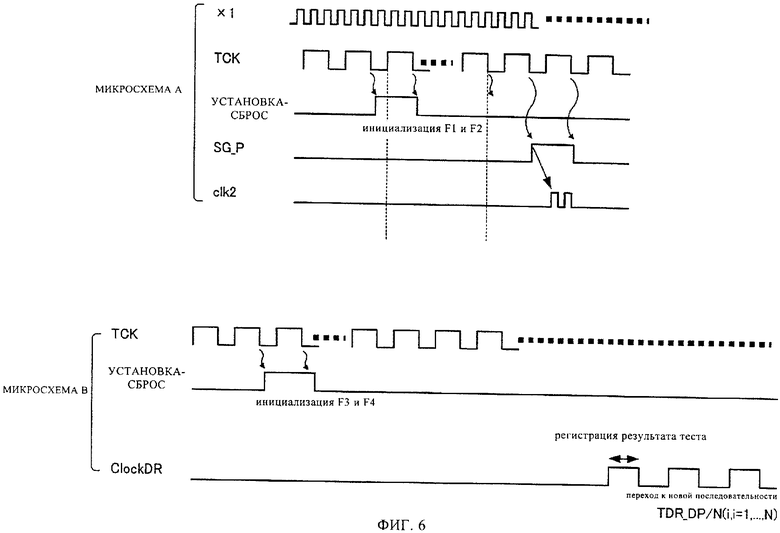

на фиг.6 - диаграмма, иллюстрирующая формы сигнала во время тестирования согласно варианту осуществления,

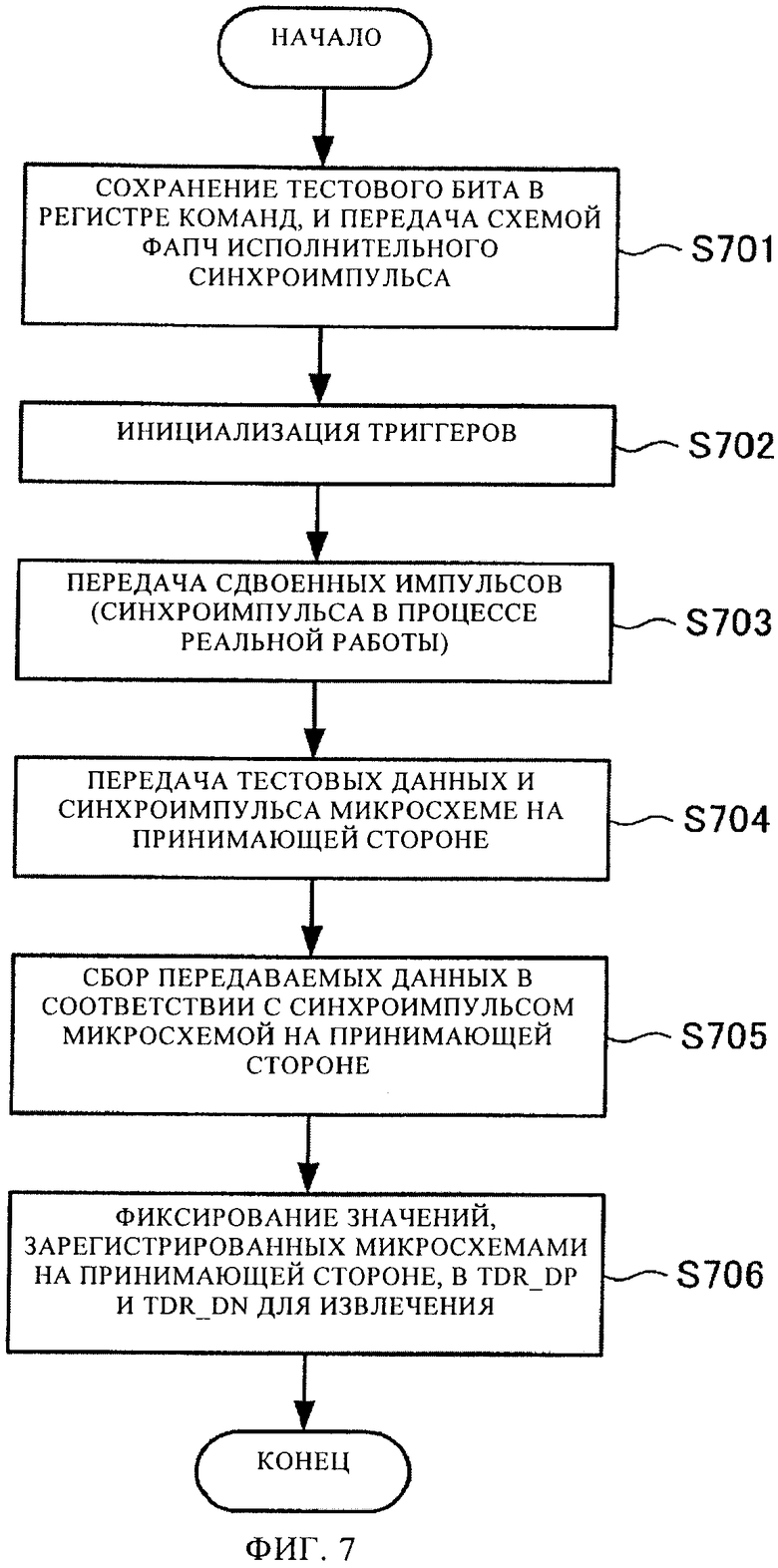

на фиг.7 - блок-схема, иллюстрирующая последовательность тестирования согласно варианту осуществления,

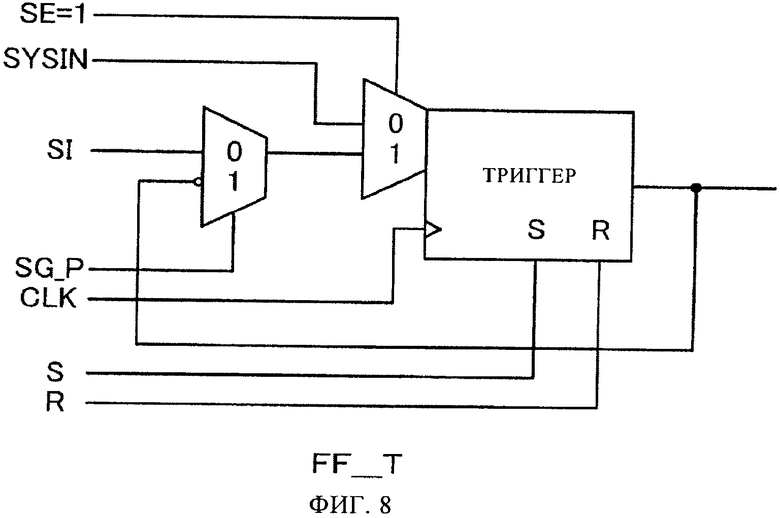

на фиг.8 - диаграмма, иллюстрирующая конфигурацию триггера на передающей стороне, применяемого в варианте осуществления,

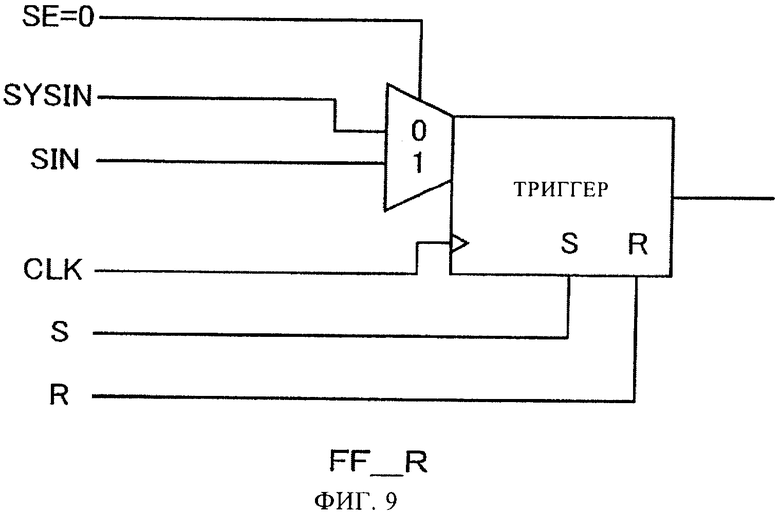

на фиг.9 - диаграмма, иллюстрирующая конфигурацию триггера на принимающей стороне, применяемого в варианте осуществления,

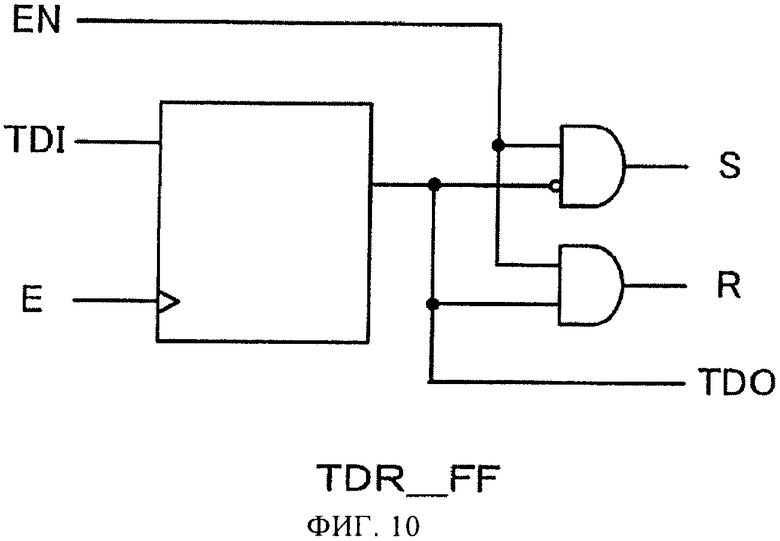

на фиг.10 диаграмма, иллюстрирующая конфигурацию схемы JTAG_TDR, применяемого в варианте осуществления,

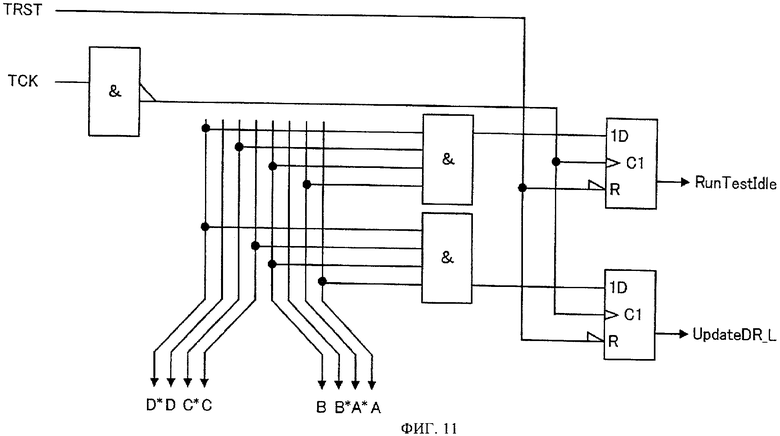

на фиг.11 - диаграмма, иллюстрирующая сигналы UpdateDR_L и RunTestIdle, применяемые в варианте осуществления,

на фиг.12 - диаграмма, иллюстрирующая полную конфигурацию синхронной с источником схемы, к которой применим второй вариант осуществления настоящего изобретения,

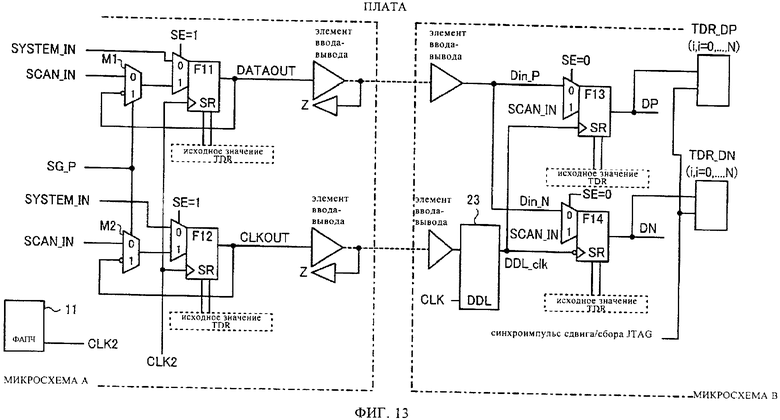

на фиг.13 - диаграмма, иллюстрирующая основные базовые элементы показанной на фиг.12 схемы для синхронизации с источником, являющиеся предметом варианта осуществления,

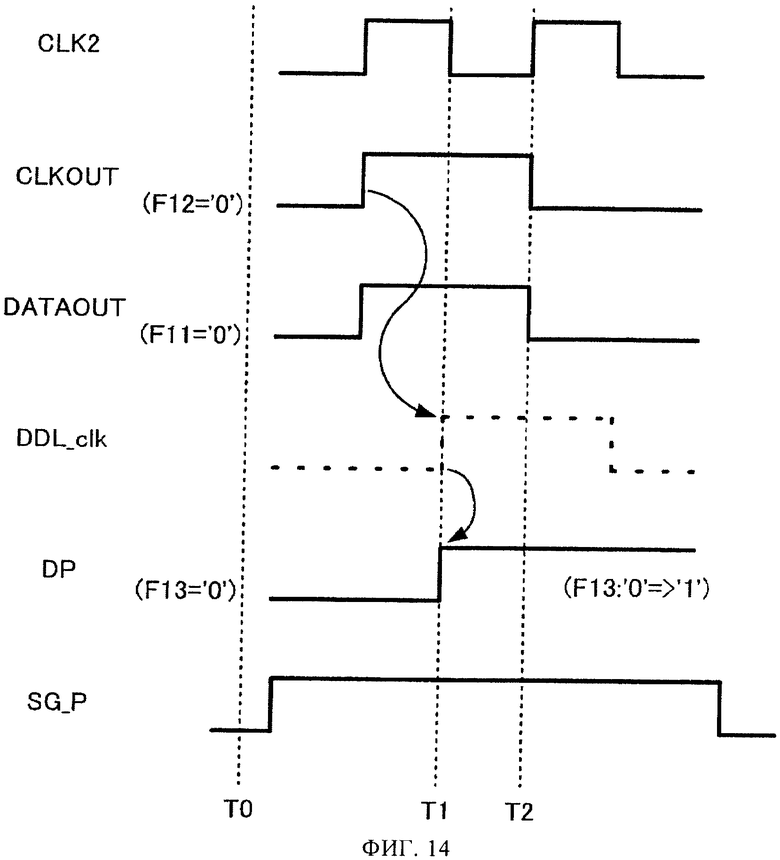

на фиг.14 - диаграмма, иллюстрирующая формы сигнала в триггере F13, показанном на фиг.13,

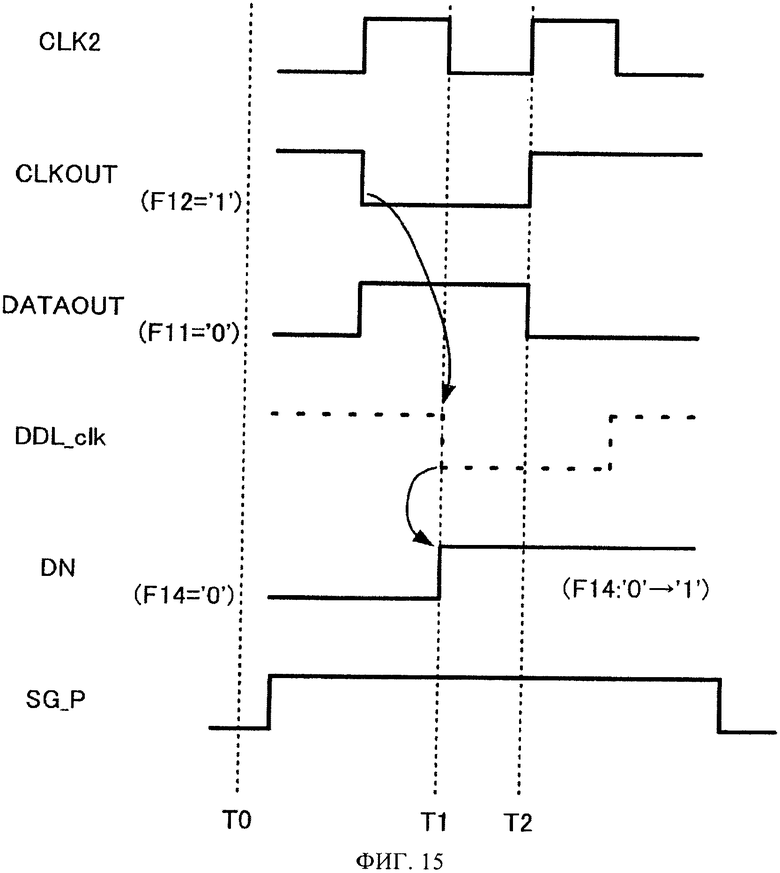

на фиг.15 - диаграмма, иллюстрирующая формы сигнала в триггере F14, показанном на фиг.13,

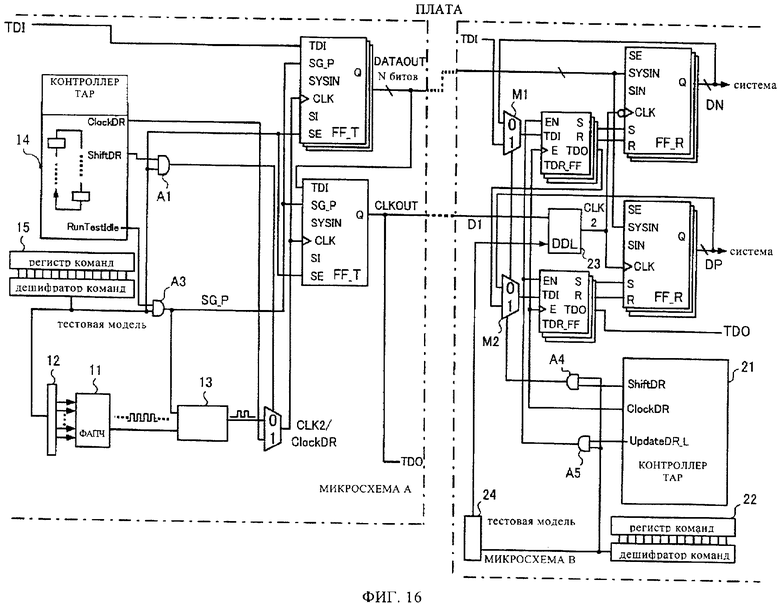

на фиг.16 - диаграмма, иллюстрирующая полную конфигурацию синхронной с источником схемы, к которой применим третий вариант осуществления настоящего изобретения,

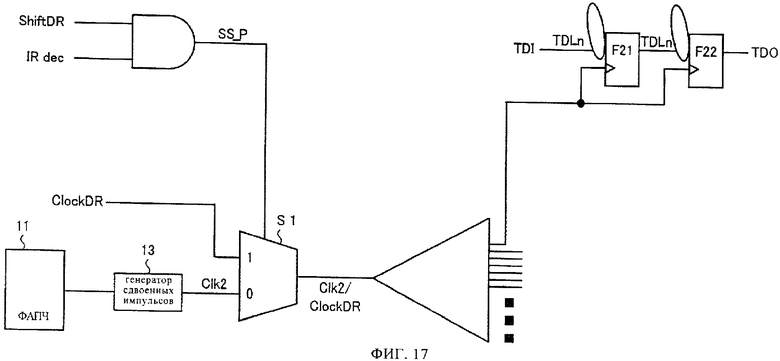

на фиг.17 - диаграмма, иллюстрирующая конфигурация схемы триггеров на передающей стороне, применяемых в варианте осуществления,

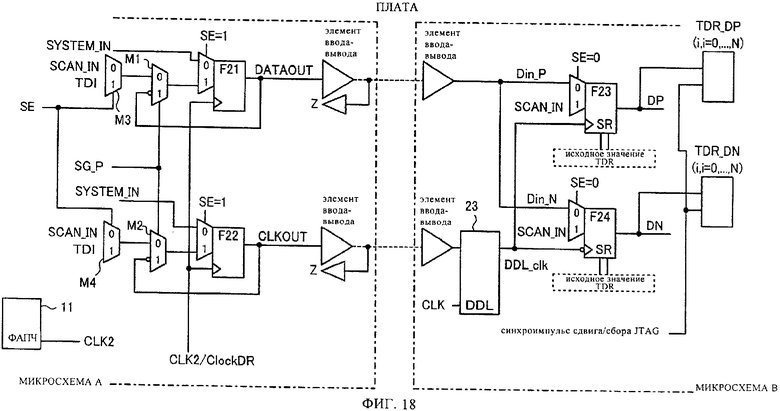

на фиг.18 - диаграмма, иллюстрирующая основные базовые элементы показанной на фиг.16 схемы для синхронизации с источником, являющиеся предметом варианта осуществления,

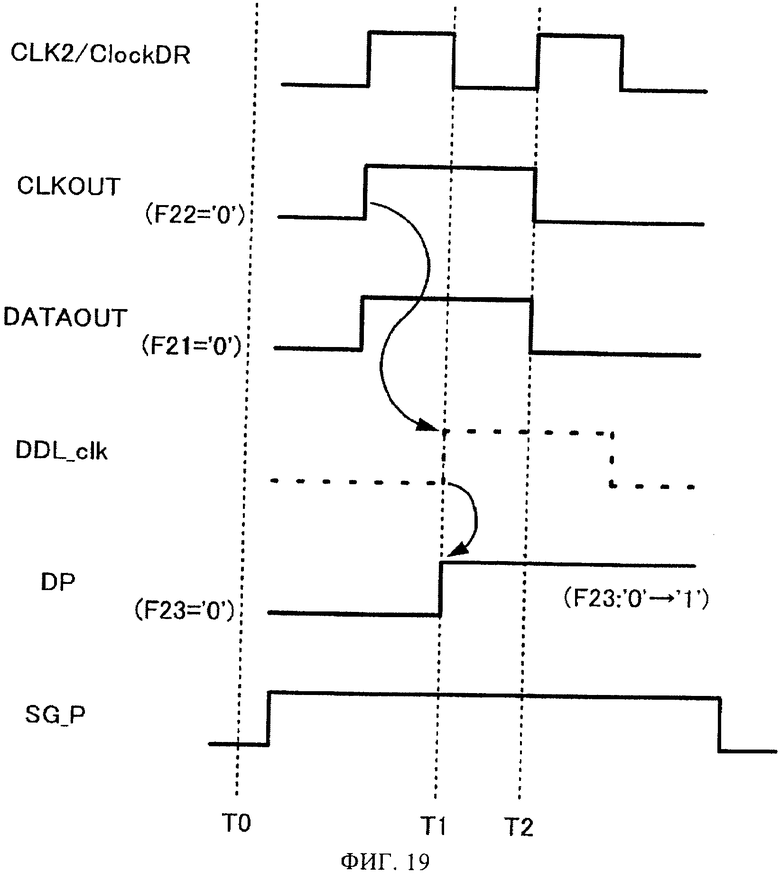

на фиг.19 - диаграмма, иллюстрирующая формы сигнала в триггере F23, показанном на фиг.18,

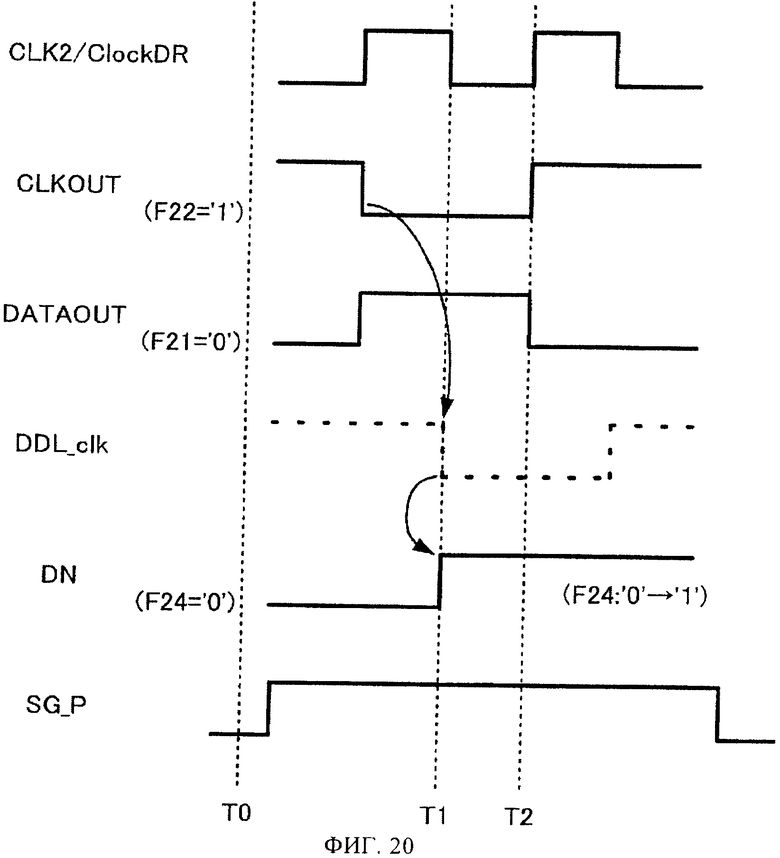

на фиг.20 - диаграмма, иллюстрирующая формы сигнала в триггере F24, показанном на фиг.18,

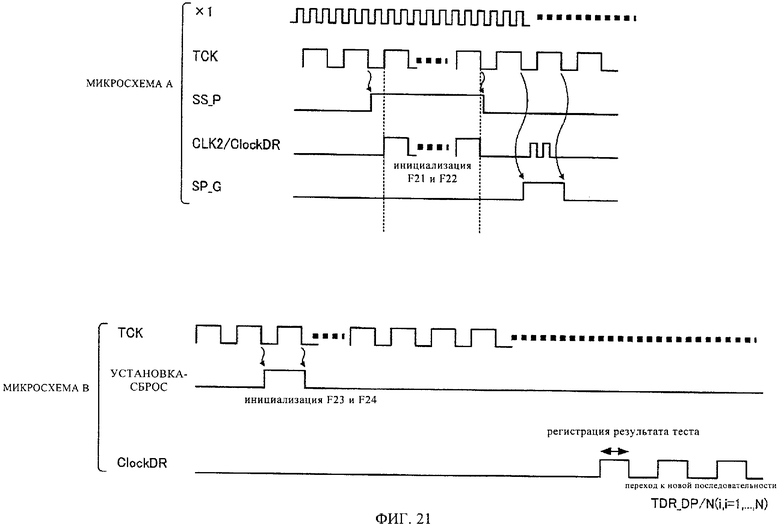

на фиг.21 - диаграмма, иллюстрирующая формы сигнала во время тестирования согласно варианту осуществления.

На представленных схемах под F1-F4, F11-F14, F21-F24 обозначен триггер, 11 - схема ФАПЧ, 12 - контроллер ФАПЧ, 13 - генератор сдвоенных импульсов, 14, 21 - контроллер ТАР, 15, 22 - регистр команд, 23 - схема DDL, 24 - контроллер синхроимпульсов

Предпочтительные варианты осуществления изобретения

Сначала кратко изложим общие принципы изобретения. Для тестирования согласно настоящему изобретению в каждой паре из двух микросхем (для синхронизации с источником), между которыми происходит обмен данными, сосредоточивают передачу, которую осуществляет микросхема на передающей стороне микросхеме на принимающей стороне из множества входящих в ASIC микросхем (схем). Для этого сначала приводят в действие триггеры для синхронизации с источником как в микросхеме на передающей стороне, так и в микросхеме на принимающей стороны для получения соответствующих заданных значений. Затем в соответствии с синхроимпульсом приводят в действие синхронный с источником интерфейс с той же скоростью, что и в процессе реальной работы, для передачи значения (тестовых данных) триггера на передающей стороне триггеру на принимающей стороне. После этого отображают результат, сохраненный в триггере на принимающей стороне, и затем изучают его.

Как описано выше, в настоящем изобретении тестовые данные передают через синхронный с источником интерфейс с той же скоростью, что и в процессе реальной работы, за счет чего осуществляют тестирование на рабочей частоте. В некоторых случаях, когда в тесте необходимо использовать триггеры для синхронизации с источником, может применяться способ, в котором JTAG_TDR является общим.

Способами синхронизации с источником являются: (а) способ, в котором с передающей стороны передают данные и синхроимпульс с равным полупериоду интервалом между ними, и (б) способ, в котором с передающей стороны передают данные и синхроимпульс на фронте одного синхроимпульса. Из этих способов в способе (б) во многих случаях используют отличающиеся друг от друга периоды повторения фронта синхроимпульса и передачи данных, чтобы задерживать синхроимпульс на π/2 (90°) с помощью средства задержки, такого как схема DDL (цифровая линия задержки) (далее - механизм задержки синхроимпульса на π/2 именуется DDL) в микросхеме на принимающей стороне, за счет чего данные защелкивают в триггере в соответствии с этим синхроимпульсом.

В качестве способа ввода исходных значений (тестовых данных) в триггеры для синхронизации с источником применяют способ ввода исходного значения в соответствии с сигналом установки-сброса путем использования триггеров с раздельными входами в качестве триггеров для синхронизации с источником. Кроме того, когда синхронизацию с источником осуществляют упомянутым способом (б), может применяться способ, в котором триггер на передающей стороне также используют в качестве JTAG_TDR (то есть, в котором исходное значение вводят в триггер на передающей стороне с использованием алгоритма сдвига данных в соответствии с JTAG). Следовательно, для осуществления теста согласно настоящему изобретению предположительно может применяться конфигурация схемы трех типов. Далее настоящее изобретение описано на примере с первого по третий вариантов осуществления, которые соответствуют этим конфигурациям схемы.

Первый вариант осуществления

В первом варианте осуществления описан следующий случай. В частности, в качестве способа синхронизации с источником применяют способ, в котором с передающей стороны передают данные и синхроимпульс с равным полупериоду интервалом между ними.

На фиг.1 показана полная конфигурация синхронной с источником схемы, к которой применим рассматриваемый вариант осуществления. Как показано на фиг.1, микросхема А является микросхемой на передающей стороне, а микросхема В является микросхемой на принимающей стороне. Хотя на фиг.1 показаны только синхронные с источником участки схемы, подразумевается, что обе микросхемы А и В соответственно имеют системные схемы. Следует отметить, что показанные на фиг.1 различия между микросхемами А и В лишь показывают, является ли каждая из микросхем А и В микросхемой на передающей стороне или микросхемой на принимающей стороне. Иными словами, каждая микросхема в ASIC служит микросхемой А или микросхемой В в зависимости от состояния (передающая сторона или принимающая сторона) микросхемы в синхронном с источником интерфейсе.

В микросхеме А под FF_T обозначается триггер на передающей стороне. В данном варианте осуществления триггер на передающей стороне является триггером с раздельными входами, конфигурация которого показана на фиг.8. В микросхеме В FF_R обозначает триггер на принимающей стороне. Триггер на принимающей стороне также является триггером с раздельными входами, конфигурация которого показана на фиг.9. TDR_FF в микросхемах А и В обозначает JTAG_TDR, конфигурация которого показана на фиг.10.

На фиг.2 проиллюстрированы основные базовые элементы схемы для синхронизации с источником, являющиеся предметом данного варианта осуществления. Как показано на фиг.2, триггерами для синхронизации с источником в микросхеме А (передающая сторона) являются триггер F1 для передачи данных и триггер F2 для передачи синхроимпульса, а в микросхеме В (принимающая сторона) - триггеры F3 и F4 для приема данных. Из триггеров F3 и F4 на принимающей стороне триггер F3 осуществляет сбор данных, передаваемых триггером F1 на переднем фронте синхроимпульса, передаваемого триггером F2. Триггер F4 осуществляет сбор данных, передаваемых триггером F1 на заднем фронте синхроимпульса, передаваемого триггером F2.

Как показано на фиг.2, одиночный триггер F2 для передачи синхроимпульса имеет одиночный триггер F1, одиночный триггер F3 и одиночный триггер F4. Вместе с тем, в реальной схеме одиночный триггер F2 для передачи синхроимпульса имеет несколько триггеров F1, а число триггеров F3 и число триггеров F4 в микросхеме В в каждом случае соответствует числу триггеров F1 (смотри фиг.1). Кроме того, в микросхемах А и В предусмотрено несколько комплектов таких триггеров F1-F4. Например, допустим, что микросхемы А и В имеют четыре комплекта триггеров F1-F4, при этом в каждом комплекте одиночный триггер F2 имеет восемь триггеров F1, восемь триггеров F3 и восемь триггеров F4. В таком случае скорость обмена данными между микросхемами А и В составляет 32 бита (=8 бит×4)/фронт синхроимпульса.

Кроме того, в микросхеме А множество триггеров F1 и F2 на передающей стороне образует тракт сканирования для производственных испытаний, при этом каждый из них соединен с терминалом ввода данных (ввод данных в сканирующий регистр) и терминалом вывода данных (вывод данных из сканирующего регистра) в микросхеме А. Аналогичным образом, в микросхеме В триггеры F3 и F4 на принимающей стороне образуют тракт сканирования, при этом каждый из них соединен с терминалом ввода данных (ввод данных в сканирующий регистр) и терминалом вывода данных (вывод данных из сканирующего регистра) в микросхеме В. Каждый из триггеров F1, F2, F3 и F4 устанавливают/сбрасывают в ответ на выходной сигнал соответствующего TDR_FF, каждый из которых является JTAG_TDR (смотри фиг.1). Помимо этого, F1, F2, F3 и F4 являются триггерами MUXSCAN (мультиплексорное сканирование, от английского - multiplexer scan). Во время тестирования в F1 и F2 поступает избирательный сигнал SE="1", а в F3 и F4 поступает избирательный сигнал SE="0". Это также относится к фиг.13-18, на которых проиллюстрированы другие варианты осуществления, описанные далее.

Далее описаны триггеры F1 и F2 микросхемы.

В триггер F1 на передающей стороне для передачи данных вводят значение (тестовые данные) из соответствующего TDR_F. Затем в ответ на управляющий сигнал SG_P="1", введенный мультиплексором M1, триггер F1 инвертирует собственный выходной сигнал и снова вводит инвертированный выходной сигнал, после чего выводит сохраненное значение (DATAOUT) на заднем фронте синхросигнала CLK2 из схемы 11 ФАПЧ.

В отличие от этого в триггер F2 на передающей стороне для передачи синхроимпульса вводят исходное значение из соответствующего TDR_FF. Затем в ответ на управляющий сигнал SG_P="1", введенный мультиплексором М2, триггер F2 инвертирует собственный выходной сигнал и снова вводит инвертированный выходной сигнал, после чего выводит сохраненное значение в виде синхроимпульса (CLKOUT) путем ввода синхросигнала CLK2 из схемы 11 ФАПЧ без его инвертирования. При данной конфигурации получают DATAOUT на выходе триггера F1 и CLKOUT на выходе триггера F2 с равным полупериоду интервалом между ними.

В данном случае синхросигнал CLK2, выводимый из схемы 11 ФАПЧ, является синхросигналом, имеющим такую же частоту, что и исполнительный синхроимпульс, управляющий микросхемой А в процессе реальной работы.

Далее описаны триггеры F3 и F4 микросхемы В.

В триггер F3 на принимающей стороне для приема данных вводят исходное значение из соответствующего TDR_FF. После этого синхроимпульс CLKOUT, поступающий из микросхемы А, вводят в триггер F3 в качестве исполнительного синхроимпульса STB_clk без инвертирования. В соответствии с этим исполнительным синхроимпульсом STB_clk триггер F3 осуществляет сбор DATAOUT, поступающих из микросхемы А. Тем самым значение (тестовые данные) DATAOUT выводят из триггера F3 (DP) и затем защелкивают в TDR_DP для изучения.

В отличие от этого в триггер F4, являющийся другим триггером на принимающей стороне для приема данных, вводят исходное значение из соответствующего TDR_FF. После этого синхроимпульс CLKOUT, поступающий из микросхемы А, вводят в триггер F4 в качестве исполнительного синхроимпульса STB_clk с инвертированием. В соответствии с этим исполнительным синхроимпульсом STB_clk триггер F4 осуществляет сбор данных DATAOUT, поступающих из микросхемы А. Тем самым значение (тестовые данные) DATAOUT выводят из триггера F4 (DN) и затем защелкивают в TDR_DN для изучения.

На фиг.3 показана диаграмма, иллюстрирующая формы сигнала в триггере F3.

Рассмотрим фиг.3. На переднем фронте первого из двух синхросигналов CLK2 из схемы 11 ФАПЧ микросхемы А из триггера F2 выводят синхроимпульс (CLKOUT), a STB_clk спадает. Затем на заднем фронте этого первого синхросигнала CLK2 из триггера F1 выводят тестовые данные (DATAOUT). В дальнейшем на переднем фронте второго синхросигнала CLK2 завершают вывод синхроимпульса, a STB_clk нарастает, за счет чего триггер F3 микросхемы В (DP) регистрирует значение тестовых данных. В данном случае (Fl="0") на чертежах обозначает, что триггер F1 установлен на "0" соответствующим TDR_FF. Это также относится к последующему описанию.

На фиг.4 показана диаграмма, иллюстрирующая формы сигнала в триггере F4.

Рассмотрим фиг.4. На переднем фронте первого из двух синхросигналов CLK2 из схемы 11 ФАПЧ микросхемы А из триггера F2 выводят синхроимпульс (CLKOUT), a STB_clk нарастает. Затем на заднем фронте этого первого синхросигнала CLK2 из триггера F1 выводят тестовые данные (DATAOUT). В дальнейшем на переднем фронте второго синхросигнала CLK2 завершают вывод синхроимпульса, a STB_clk спадает, за счет чего триггер F4 микросхемы В (DN) регистрирует значение тестовых данных.

Далее описан способ ввода исходных значений в триггеры F1-F4 для синхронизации с источником, который используют в рассматриваемом варианте осуществления.

На фиг.5 показана конфигурация схемы инициализации триггеров F1 и F2 микросхемы А. Показанный триггер с раздельными входами является триггером F1 или триггером F2 микросхемы А, показанной на фиг.2. Как показано на фиг.5, сначала в TDR_FF сохраняют какое-либо значение. Затем, когда UpdateDR_L="1", триггеры F1 и F2 устанавливают или сбрасывают в соответствии со значением, сохраненным в TDR_FF. Сигнал UpdateDR_L генерируют, как это показано на фиг.11. Это также относится к последующему описанию. В показанном на чертежах примере, когда значение в соответствующем TDR_FF равно "1", осуществляют сброс каждого из триггеров F1 и F2, а когда значение в соответствующем TDR_FF равно "0", осуществляют их установку. В частности, фиг.11 основана на фиг.5-5 упомянутого выше непатентного документа [1], а для генерирования сигналов А, В, С и D и в показанной на чертежах схеме использована система обозначений, соответствующая фиг.5-5.

Выше описан способ инициализации триггеров F1 и F2 микросхемы А. Тем не менее, поскольку в данном варианте осуществления триггеры F3 и F4 микросхемы В имеют аналогичную конфигурацию, каждый из триггеров F3 и F4 устанавливают или сбрасывают с помощью соответствующего TDR_FF микросхемы В. Соответственно, на чертежах используются обозначения F1, F2 (F3, F4).

Далее снова со ссылкой на фиг.1 описана зависимость соединения на уровне микросхем, включая триггеры для синхронизации с источником, которую тестируют в рассматриваемом варианте осуществления.

Сначала рассмотрим микросхему А на передающей стороне. Помимо упомянутых выше FF_T и TDR_FF, микросхема А включает схему 11 ФАПЧ и контроллер 12 ФАПЧ для данного теста в качестве устройства для передачи исполнительных синхроимпульсов, генератор 13 сдвоенных импульсов для извлечения сдвоенных импульсов из исполнительных синхроимпульсов, передаваемых схемой 11 ФАПЧ, и затем вывода импульсов, контроллер 14 ТАР (порт доступа к средствам тестирования, от английского - Test Access Port) для управления JTAG и регистр 15 команд (IR, от английского - Instruction Register). Выходы контроллера 14 ТАР и регистра 15 команд через дешифратор команд, а также логические элементы A1, A2 и A3 подают в TDR_FF, FF_T, генератор 13 сдвоенных импульсов и т.п.

Контроллер 12 ФАПЧ управляет схемой 11 ФАПЧ таким образом, чтобы схема 11 ФАПЧ осуществляла передачу на той же частоте, что и в процессе реальной работы, после сохранения в регистре 15 команд битовой строки (далее - тестовый бит) из команды JTAG, которая соответствует данному тесту.

Логический элемент И A1 подает синхросигнал тестирования ТСК (от английского - Test Clock) в соответствующий TDR_FF, когда тестовый бит сохранен в регистре 15 команд, и параллельно, когда ShiftDR="1".

Логический элемент И A2 через соответствующий TDR_FF подает в каждый FF_T управляющий сигнал для установки или сброса FF_T, когда тестовый бит сохранен в регистре 15 команд, и параллельно, когда UpdateDR_L="1". От значений, введенных в соответствующие TDR_FF, как это описано выше, зависит, должны ли быть установлены или сброшены FF_T. Таким способом определяют исходные значения FF_T.

Логический элемент И A3 подает в каждый FF_T управляющий сигнал SG_P для установки внутри FF_T циклического состояния, а также подает в генератор 13 сдвоенных импульсов запускающий сигнал для извлечения сдвоенных импульсов из выходного сигнала схемы 11 ФАПЧ, когда тестовый бит сохранен в регистре 15 команд, и параллельно, когда RunTestIdle="1" (смотри фиг.11).

Далее рассмотрим микросхему В на принимающей стороне. Помимо упомянутых выше FF_R и TDR_FF микросхема В включает контроллер 21 ТАР для управления JTAG и регистр 22 команд. Выходные сигналы контроллера 21 ТАР и регистра 22 команд через дешифратор команд и логические элементы И А4 и А5 поступают в TDR_FF и т.п.

Логический элемент И А4 подает в мультиплексоры M1 и М2 управляющий сигнал, согласно которому мультиплексоры M1 и М2 выбирают данные, отображающие "1", когда тестовый бит сохранен в регистре 22 команд, и затем, когда ShiftDR="1". За счет того что мультиплексоры M1 и М2 выбирают данные, отображающие "1", осуществляют сканирование тракта TDI (тестовые данные на входе) - TDO (тестовые данные на выходе) в соответствии с синхросигналом тестирования ТСК и вводят значение в каждый из TDR_FF.

Логический элемент И А5 подает в TDR_FF управляющий сигнал для установки или сброса FF_R, когда тестовый бит сохранен в регистре 22 команд, и параллельно, когда UpdateDR_L="1". От значений, введенных в соответствующие TDR_FF, как это описано выше, зависит, должны ли быть установлены или сброшены FF_R. Таким способом определяют исходные значения FF_R. Кроме того, контроллер 21 ТАР подает в TDR_FF синхросигнал ClockDR для управления работой TDR_FF.

Далее описаны операции, осуществляемые при тестировании с использованием схемы с описанной выше конфигурацией.

На фиг.6 показана диаграмма, иллюстрирующая формы сигналов в микросхемах А и В во время тестирования, а на фиг.7 показана блок-схема, иллюстрирующая последовательность тестирования.

Согласно данному варианту осуществления тест состоит из трех основных этапов: этапа ввода исходных значений в триггеры (как на передающей, так и на принимающей стороне) для синхронизации с источником, этапа приведения в действие синхронного с источником интерфейса с такой же скоростью, что и при реальной работе, и этап получения результата теста.

Как показано на фиг.7, при проведении теста согласно данному варианту осуществления сначала в каждом из регистров 15 и 22 команд микросхем А и В сохраняют тестовый бит. Тем самым приводят в действие схемы 11 ФАПЧ микросхем А и В для передачи исполнительного синхроимпульса (шаг 701). Затем согласно произвольному значению инициируют каждый из триггеров для синхронизации с источником (FF_T и FF_R на фиг.1 и F1-F4 на фиг.2) (шаг 702). Эта инициализация триггеров может быть осуществлена способом, который соответствует стандарту JTAG 1149, как это описано выше. Как показано на фиг.6, каждый из триггеров F1 и F2 в микросхеме А инициирован в соответствии со значением, введенным в соответствующий TDR_FF, а каждый из триггеров F3 и F4 в микросхеме В аналогичным образом инициирован в соответствии со значением, введенным в соответствующий TDR_FF.

В дальнейшем генератор 13 сдвоенных импульсов, приведенный в действие RunTestIdle="1" микросхемы А на передающей стороне, передает сдвоенные импульсы, извлеченные из выходного сигнала схемы 11 ФАПЧ, при этом сдвоенные импульсы имеют такую же скорость, что и синхроимпульс в процессе реальной работы (шаг 703). Как показано на фиг.6, выводят управляющий сигнал SG_P для установки циклического состояния FF_T и одновременно выводят синхросигналы CLK2 сдвоенных импульсов. Следует отметить, что RunTestIdle генерируют, как показано на фиг.11.

Затем в соответствии со сдвоенными импульсами триггеры F1 и F2 соответственно передают тестовые данные, сохраненные в триггере F1, и синхроимпульс микросхеме В на принимающей стороне (шаг 704). Триггеры F3 и F4 микросхемы В осуществляют сбор данных, передаваемых триггером F1 микросхемы А, в соответствии с синхроимпульсом, передаваемым триггером F2 (шаг 705).

После этого в ответ на clockDR в микросхеме В на принимающей стороне защелкивают значения, зарегистрированные триггерами F3 и F4 соответственно в TDR_DP и TDR_DN. Затем значения в защелке извлекают из изучаемых TDO (тестовые данные на выходе, от английского - Test Data Out) (шаг 706). Эти данные могут быть извлечены из TDO в соответствии с сигналом ClockDR, поступающим из контроллера 14 ТАР, способом, который соответствует стандарту JTAG 1149.

Таким способом осуществляют обмен тестовыми данными между триггерами на передающей стороне и триггерами на принимающей стороне, во всех случаях для синхронизации с источником с той же скоростью, что и в процессе реальной работы. Путем оценки значений (результата теста), зарегистрированных на принимающей стороне, может быть проведено тестирование на уровне плат синхронного с источником интерфейса на рабочей частоте.

Второй вариант осуществления

Во втором варианте осуществления описан следующий случай. В частности, для синхронизации с источником применяют способ, в котором передающая сторона передает данные и синхроимпульс на фронте одного синхроимпульса, и параллельно осуществляют установку или сброс триггеров на передающей стороне в соответствии со значениями инициируемых TDR_FF.

На фиг.12 показана полная конфигурация синхронной с источником схемы, к которой применим данный вариант осуществления. Как показано на фиг.12, микросхема А является микросхемой на передающей стороне, а микросхема В является микросхемой на принимающей стороне. Хотя на фиг.12 показаны только синхронные с источником участки схемы, подразумевается, что обе микросхемы А и В соответственно имеют системные схемы. Следует отметить, что показанные на фиг.1 различия между микросхемами А и В лишь показывают, является ли каждая из микросхем А и В микросхемой на передающей стороне или микросхемой на принимающей стороне. Иными словами, каждая микросхема в ASIC служит микросхемой А или микросхемой В в зависимости от состояния (передающая сторона или принимающая сторона) микросхемы в синхронном с источником интерфейсе. В микросхемах А и В FF_T обозначает триггер на передающей стороне, FF_R обозначает триггер на принимающей стороне, a TDR_FF обозначает JTAG_TDR. Их конфигурации аналогичны конфигурациям из первого варианта осуществления, соответственно показанным на фиг.8, 9 и 10.

На фиг.13 проиллюстрированы основные базовые элементы схемы для синхронизации с источником, являющиеся предметом данного варианта осуществления. Как показано на фиг.13, триггерами для синхронизации с источником в микросхеме А (передающая сторона) являются триггер F11 для передачи данных и триггер F12 для передачи синхроимпульса, а в микросхеме В (принимающая сторона) - триггеры F13 и F14 для приема данных. Из триггеров F13 и F14 на принимающей стороне триггер F13 осуществляет сбор данных, передаваемых триггером F11 на переднем фронте синхроимпульса, передаваемого триггером F12. Триггер F14 осуществляет сбор данных, передаваемых триггером F11 на заднем фронте синхроимпульса, передаваемого триггером F12.

Как показано на фиг.12, одиночный триггер F12 для передачи синхроимпульса имеет одиночный триггер F11, одиночный триггер F13 и одиночный триггер F14. Вместе с тем, в реальной схеме одиночный триггер F12 для передачи синхроимпульса имеет несколько триггеров F11, а число триггеров F13 и число триггеров F14 в микросхеме В в каждом случае соответствует числу триггеров F11 (смотри фиг.12). Кроме того, в микросхемах А и В предусмотрено несколько комплектов таких триггеров F11-F14.

Помимо этого, в микросхеме А множество триггеров F11 и F12 на передающей стороне образует тракт сканирования для производственных испытаний, при этом каждый из них соединен с терминалом ввода данных (ввод данных в сканирующий регистр) и терминалом вывода данных (вывод данных из сканирующего регистра) в микросхеме А. Аналогичным образом, в микросхеме В триггеры F13 и F14 на принимающей стороне образуют тракт сканирования, при этом каждый из них соединен с терминалом ввода данных (ввод данных в сканирующий регистр) и терминалом вывода данных (вывод данных из сканирующего регистра) в микросхеме В. Каждый из триггеров F11, F12, F13 и F14 устанавливают/сбрасывают в ответ на выходной сигнал соответствующего TDR_FF (смотри фиг.12).

Далее описаны триггеры F11 и F12 микросхемы А.

В триггер F11 на передающей стороне для передачи данных вводят значение (тестовые данные) из соответствующего TDR_FF. Затем в ответ на управляющий сигнал SG_P="1", введенный мультиплексором M1, триггер F11 инвертирует собственный выходной сигнал и снова вводит инвертированный выходной сигнал, после чего выводит сохраненное значение (DATAOUT) путем ввода синхросигнала CLK2 из схемы 11 ФАПЧ без его инвертирования.

В отличие от этого в триггер F12 на передающей стороне для передачи синхроимпульса вводят исходное значение из соответствующего TDR_FF. Затем в ответ на управляющий сигнал SG_P="1", введенный мультиплексором М2, триггер F12 инвертирует собственный выходной сигнал и снова вводит инвертированный выходной сигнал, после чего выводит сохраненное значение в виде синхроимпульса (CLKOUT) путем ввода синхросигнала CLK2 из схемы 11 ФАПЧ без его инвертирования. При данной конфигурации получают DATAOUT на выходе триггера F11 и CLKOUT на выходе триггера F12 на фронте одного синхроимпульса.

В данном случае синхросигнал CLK2, выводимый из схемы 11 ФАПЧ, является исполнительным синхроимпульсом для управления микросхемой А в процессе реальной работы.

Далее описаны триггеры F13 и F14 микросхемы В.

В триггер F13 на принимающей стороне для приема данных вводят исходное значение из соответствующего TDR_FF. После этого в схеме 23 DLL задерживают на π/2 продолжительность периода CLKOUT, поступающего из микросхемы А, а затем задержанный CLKOUT вводят в триггер F13 в качестве исполнительного синхроимпульса DDL_clk без инвертирования. В соответствии с этим исполнительным синхроимпульсом DDL_clk триггер F13 осуществляет сбор DATAOUT, поступающих из микросхемы А. Тем самым значение (тестовые данные) DATAOUT выводят из триггера F13 (DP) и затем защелкивают в TDR_DP для изучения.

В отличие от этого в триггер F14, являющийся другим триггером на принимающей стороне для приема данных, вводят исходное значение из соответствующего TDR_FF. После этого в схеме 23 DLL задерживают на π/2 продолжительность периода CLKOUT, поступающего из микросхемы А, и вводят синхроимпульс CLKOUT в качестве исполнительного синхроимпульса DDL_clk. Затем исполнительный синхроимпульс DDL_clk вводят в триггер F14 с инвертированием. В соответствии с этим исполнительным синхроимпульсом DDL_clk триггер F14 осуществляет сбор DATAOUT, поступающих из микросхемы А. Тем самым значение (тестовые данные) DATAOUT выводят из триггера F14 (DN) и затем защелкивают в TDR_DN для изучения.

На фиг.14 показана диаграмма, иллюстрирующая формы сигнала в триггере F13.

Рассмотрим фиг.14. На переднем фронте первого из двух синхросигналов CLK2, поступающих из схемы 11 ФАПЧ микросхемы А, одновременно выводят тестовые данные (DATAOUT) триггера F11 и синхроимпульс (CLKOUT) триггера F12. Затем DDL_clk нарастает с задержкой на π/2 относительно этого синхроимпульса. В результате период нарастания DDL_clk сдвигается в середину тестовых данных. В ответ на это нарастание DLL_clk триггер F13 микросхемы В (DP) регистрирует значение тестовых данных.

На фиг.15 показана диаграмма, иллюстрирующая формы сигнала в триггере F14.

Рассмотрим фиг.15. На переднем фронте первого из двух синхросигналов CLK2, поступающих из схемы 11 ФАПЧ микросхемы А, одновременно выводят тестовые данные (DAT AOUT) триггера F11 и синхроимпульс (CLKOUT) триггера F12. Затем DDL_clk спадает с задержкой на π/2 относительно этого синхроимпульса. В результате период спада DDL_clk сдвигается в середину тестовых данных. В ответ на этот спад DLL_clk триггер F14 микросхемы В (DN) регистрирует значение тестовых данных.

В данном варианте осуществления триггеры F11-F14 для синхронизации с источником, как и триггеры F1-F4 из первого варианта осуществления, устанавливают/сбрасывают в соответствии с выходными сигналами соответствующих TDR_FF, как это описано выше. Следовательно, при конфигурации схемы, показанной на фиг.5, в каждый из триггеров F11-F14 вводят исходное значение способом, аналогичным способу, применяемому в первом варианте осуществления.

Далее снова со ссылкой на фиг.12 описана зависимость соединения на уровне микросхем, включая триггеры для синхронизации с источником, которую тестируют в рассматриваемом варианте осуществления.

Сначала рассмотрим микросхему А на передающей стороне. Помимо упомянутых выше FF_T и TDR_FF, микросхема А включает схему 11 ФАПЧ и контроллер 12 ФАПЧ в качестве устройства для передачи исполнительных синхроимпульсов, генератор 13 сдвоенных импульсов для извлечения сдвоенных импульсов из исполнительных синхроимпульсов, передаваемых схемой 11 ФАПЧ, и затем вывода импульсов, контроллер 14 ТАР для управления JTAG и регистр 15 команд (IR). Выходы контроллера 14 ТАР и регистра 15 команд через логические элементы A1, A2 и A3 подают в TDR_FF, FF_T, генератор 13 сдвоенных импульсов и т.п.

Контроллер 12 ФАПЧ управляет схемой 11 ФАПЧ таким образом, чтобы схема 11 ФАПЧ осуществляла передачу на той же частоте, что и в процессе реальной работы, после сохранения тестового бита в регистре 15 команд.

Логический элемент И А1 подает ТСК в соответствующий TDR_FF, когда тестовый бит сохранен в регистре 15 команд, и параллельно, когда ShiftDR="1".

Логический элемент И А2 через соответствующий TDR_FF подает в каждый FF_T управляющий сигнал для установки или сброса FF_T, когда тестовый бит сохранен в регистре 15 команд, и параллельно, когда UpdateDR_L="1". От значений, введенных в соответствующие TDR_FF, как это описано выше, зависит, должны ли быть установлены или сброшены FF_T. Таким способом определяют исходные значения FF_T. При этом в качестве тестовых данных вводят исходное значение FF_T, включая триггер F1, показанный на фиг.13.

Логический элемент И A3 подает в каждый FF_T управляющий сигнал SG_P для установки внутри FF_T циклического состояния, а также подает в генератор 13 сдвоенных импульсов запускающий сигнал для извлечения сдвоенных импульсов из выходного сигнала схемы 11 ФАПЧ, когда тестовый бит сохранен в регистре 15 команд, и параллельно, когда RunTestIdle="1".

Далее рассмотрим микросхему В на принимающей стороне. Помимо упомянутых выше FF_R и TDR_FF, микросхема В включает контроллер 21 ТАР для управления JTAG, регистр 22 команд, схему 23 DDL для задержки синхроимпульса и контроллер 24 синхроимпульсов для управления схемой 23 DDL и непоказанной схемой ФАПЧ. Выходные сигналы контроллера 21 ТАР и регистра 22 команд через логические элементы И А4 и А5 поступают в TDR_FF и т.п.

Контроллер 24 синхроимпульсов управляет схемой 23 DDL и схемой ФАПЧ таким образом, чтобы схема 23 DDL и непоказанная схема ФАПЧ могли осуществлять передачу на той же частоте, что и в процессе реальной работы после сохранения тестового бита в регистре 22 команд.

Логический элемент И А4 подает в мультиплексоры M1 и М2 управляющий сигнал, согласно которому мультиплексоры М1 и М2 выбирают данные, отображающие "1", когда тестовый бит сохранен в регистре 22 команд, и затем, когда ShiftDR="1". За счет того что мультиплексоры M1 и М2 выбирают данные, отображающие "1", осуществляют сканирование тракта TDI (тестовые данные на входе) - TDO (тестовые данные на выходе) в соответствии с синхросигналом тестирования ТСК и вводят значение в каждый из TDR_FF.

Логический элемент И А5 через соответствующий TDR_FF подает в каждый FF_R управляющий сигнал для установки или сброса FF_R, когда тестовый бит сохранен в регистре 22 команд, и параллельно, когда UpdateDR_L="1". От значений, введенных в соответствующие TDR_FF, как это описано выше, зависит, должны ли быть установлены или сброшены FF_R. Таким способом определяют исходные значения FF_R.

ClockDR контроллера 21 ТАР подает синхросигнал тестирования ТСК в TDR_FF, когда ShiftDR="1" или когда CaptureDR="1". В соответствии с поступившим синхросигналом тестирования ТСК осуществляют сканирование тракта TDI-TDO, а также, например, TDR_FF осуществляет сбор данных, хранящихся в FF_R.

При тестировании схемы с описанной выше конфигурацией осуществляют приблизительно такие же операции, что в первом варианте осуществления, описанном со ссылкой на фиг.6 и 7.

Операции согласно второму варианту осуществления отличаются следующими особенностями от операций согласно первому варианту осуществления.

Во-первых, в первом варианте осуществления период вывода тестовых данных из триггера F1 и период вывода синхроимпульса из триггера F2 разделены временным интервалом, равным половине периода. В отличие от этого во втором варианте осуществления вывод тестовых данных из триггера F11 и вывод синхроимпульса из триггера F12 осуществляют на фронте одного синхроимпульса.

Кроме того, в первом варианте осуществления на шаге 705, показанном на фиг.7, триггеры F3 и F4 осуществляют сбор тестовых данных, передаваемых триггером F1, в соответствии с синхроимпульсом, передаваемым триггером F2. В отличие от этого, поскольку во втором варианте осуществления фронт синхроимпульса, на котором выводят тестовые данные из триггера F11, и фронт синхроимпульса, на котором выводят синхроимпульс из триггера F12, имеют одинаковый период, синхроимпульс задерживают на π/2 в схеме 23 DLL. Затем триггеры F13 и F14 осуществляют сбор тестовых данных в соответствии с этим задержанным синхроимпульсом.

Третий вариант осуществления

Как и во втором варианте осуществления, в третьем варианте осуществления для синхронизации с источником применяют способ, в котором передающая сторона передает данные и синхроимпульс на фронте одного синхроимпульса. Вместе с тем в третьем варианте осуществления описан случай, когда для инициализации применяют способ, в котором в JTAG_TDR вводят значение, позволяя триггеру на передающей стороне играть роль JTAG_TDR.

На фиг.16 показана полная конфигурация синхронной с источником схемы, к которой применим данный вариант осуществления. Как показано на фиг.16, микросхема А является микросхемой на передающей стороне, а микросхема В является микросхемой на принимающей стороне. Хотя на фиг.16 показаны только синхронные с источником участки схемы, подразумевается, что обе микросхемы А и В соответственно имеют системные схемы. Следует отметить, что показанные на фиг.16 различия между микросхемами А и В лишь показывают, является ли каждая из микросхем А и В микросхемой на передающей стороне или микросхемой на принимающей стороне. Иными словами, каждая микросхема в ASIC служит микросхемой А или микросхемой В в зависимости от состояния (передающая сторона или принимающая сторона) микросхемы в синхронном с источником интерфейсе.

В микросхемах А и В FF_T обозначает триггер на передающей стороне, FF_R обозначает триггер на принимающей стороне, a TDR_FF обозначает JTAG_TDR. Поскольку в данном варианте осуществления FF_T также служат TDR_FF, в микросхеме А отсутствует TDR_FF. Конфигурация одного из этих триггеров FF_T на передающей стороне показана на фиг.17. Конфигурации FF_R и TDR_FF микросхемы В аналогичны конфигурациям из первого варианта осуществления, показанным на фиг.9 и 10.

На фиг.18 проиллюстрированы основные базовые элементы схемы для синхронизации с источником, являющиеся предметом данного варианта осуществления. Как показано на фиг.18, триггерами для синхронизации с источником в микросхеме А (передающая сторона) являются триггер F21 для передачи данных и триггер F22 для передачи синхроимпульса, а в микросхеме В (принимающая сторона) - триггеры F13 и F14 для приема данных. Из триггеров F23 и F24 на принимающей стороне триггер F23 осуществляет сбор данных, передаваемых триггером F21 на переднем фронте синхроимпульса, передаваемого триггером F22. Триггер F24 осуществляет сбор данных, передаваемых триггером F21 на заднем фронте синхроимпульса, передаваемого триггером F22.

Как показано на фиг.18, одиночный триггер F22 для передачи синхроимпульса имеет одиночный триггер F21, одиночный триггер F23 и одиночный триггер F24. Вместе с тем в реальной схеме одиночный триггер F22 для передачи синхроимпульса имеет несколько триггеров F21, а число триггеров F23 и число триггеров F24 в микросхеме В в каждом случае соответствует числу триггеров F21 (смотри фиг.16). Кроме того, в микросхемах А и В предусмотрено несколько комплектов таких триггеров F21-F24.

Кроме того, в микросхеме А множество триггеров F21 и F22 на передающей стороне образуют тракт сканирования для производственных испытаний, при этом каждый из них соединен с терминалом ввода данных (ввод данных в сканирующий регистр) и терминалом вывода данных (вывод данных из сканирующего регистра) в микросхеме А. Аналогичным образом, в микросхеме В триггеры F23 и F24 на принимающей стороне образуют тракт сканирования, при этом каждый из них соединен с терминалом ввода данных (ввод данных в сканирующий регистр) и терминалом вывода данных (вывод данных из сканирующего регистра) в микросхеме В.

В данном варианте осуществления в каждый из триггеров F21 и F22 вводят исходное значение путем сканирования трактов данных со сдвигом через соответствующий тракт сканирования. В то же время каждый из триггеров F21, F22, F23 и F24 устанавливают/сбрасывают в ответ на выходной сигнал соответствующего TDR_FF (смотри фиг.16). Далее описаны триггеры F21 и F22 микросхемы А.

В триггер F21 на передающей стороне для передачи данных вводят значение (тестовые данные) через тракт сканирования JTAG_TDR, проходящий через выводы 1 и 0 соответственно мультиплексоров М3 и M1. Затем в ответ на управляющий сигнал SG_P, введенный мультиплексором M1, триггер F21 инвертирует собственный выходной сигнал и снова вводит инвертированный выходной сигнал, при этом он вводит синхросигнал CLK2 из схемы 11 ФАПЧ без его инвертирования и тем самым выводит сохраненное значение (DATAOUT).

В отличие от этого в триггер F22 на передающей стороне для передачи данных вводят исходное значение через тракт сканирования JTAG_TDR, проходящий через выводы 1 и 0 соответственно мультиплексоров М4 и М2. Затем в ответ на управляющий сигнал SG_P, введенный мультиплексором М2, триггер F22 инвертирует собственный выходной сигнал и снова вводит инвертированный выходной сигнал, при этом он вводит синхросигнал CLK2 из схемы 11 ФАПЧ без его инвертирования и тем самым выводит сохраненное значение в виде синхроимпульса (CLKOUT). При данной конфигурации получают DATAOUT на выходе триггера F21 и CLKOUT на выходе триггера F22 на фронте одного синхроимпульса.

В данном случае синхросигнал CLK2, выводимый из схемы 11 ФАПЧ, является исполнительным синхроимпульсом для управления микросхемой А в процессе реальной работы.

Далее описаны триггеры F23 и F24 микросхемы В.

В триггер F23 на принимающей стороне для приема данных вводят исходное значение из соответствующего TDR_FF. После этого в схеме 23 DLL задерживают на π/2 продолжительность периода CLKOUT, поступающего из микросхемы А, а затем задержанный CLKOUT вводят в триггер F23 в качестве исполнительного синхроимпульса DDL_clk без инвертирования. В соответствии с этим исполнительным синхроимпульсом DDL_clk триггер F23 осуществляет сбор DATAOUT, поступающих из микросхемы А. Тем самым значение (тестовые данные) DATAOUT выводят из триггера F23 (DP) и затем защелкивают в TDR_DP для изучения.

В отличие от этого в триггер F24, являющийся другим триггером на принимающей стороне для приема данных, вводят исходное значение из соответствующего TDR_FF. После этого в схеме 23 DLL задерживают на π/2 продолжительность периода CLKOUT, поступающего из микросхемы А, и вводят синхроимпульс CLKOUT в качестве исполнительного синхроимпульса DDL_clk. Затем исполнительный синхроимпульс DDL_clk вводят в триггер F24 с инвертированием. В соответствии с этим исполнительным синхроимпульсом DDL_clk триггер F24 осуществляет сбор DATAOUT, поступающих из микросхемы А. Тем самым значение (тестовые данные) DATAOUT выводят из триггера F24 (DN) и затем защелкивают в TDR_DN для изучения.

На фиг.19 показана диаграмма, иллюстрирующая формы сигнала в триггере F23.

Рассмотрим фиг.19. На переднем фронте первого из двух синхросигналов CLK2, поступающих из схемы 11 ФАПЧ микросхемы А, одновременно выводят тестовые данные (DATAOUT) триггера F21 и синхроимпульс (CLKOUT) триггера F22. Затем DDL_clk нарастает с задержкой на π/2 относительно этого синхроимпульса. В результате период нарастания DDL_clk сдвигается в середину тестовых данных. В ответ на это нарастание DLL_clk триггер F23 микросхемы В (DP) регистрирует значение тестовых данных.

На фиг.20 показана диаграмма, иллюстрирующая формы сигнала в триггере F24.

Рассмотрим фиг.20. На переднем фронте первого из двух синхросигналов CLK2, поступающих из схемы 11 ФАПЧ микросхемы А, одновременно выводят тестовые данные (DATAOUT) триггера F21 и синхроимпульс (CLKOUT) триггера F22. Затем DDL_clk спадает с задержкой на π/2 относительно этого синхроимпульса. В результате период спада DDL_clk сдвигается в середину тестовых данных. В ответ на этот спад DLL_clk триггер F24 микросхемы В (DN) регистрирует значение тестовых данных.

Далее в данном варианте осуществления описан способ ввода исходных значений в триггеры F21-F24 для синхронизации с источником.

На фиг.17 показана конфигурация схемы инициализации триггеров F21 и F22 микросхемы А. Как показано на фиг.17, когда ShiftDR="1", в мультиплексор S1 поступает управляющий сигнал SS_P, чтобы был выбран ClockDR для подачи в триггеры F21 и F22. В соответствии с этим сигналом ClockDR в триггеры F21 и F22 вводят данные из TDI (тестовых данных на входе) JATG, чтобы инициировать триггеры F21 и F22.

В отличие от этого триггеры F23 и F24 микросхемы В устанавливают/сбрасывают, как и в случае с триггерами F1-F4 для синхронизации с источником в первом варианте осуществления, в соответствии с выходными сигналами TDR_FF. Следовательно, при конфигурации схемы, показанной на фиг.5, исходные значения вводят в триггеры F23 и F24 таким же способом, что и в первом варианте осуществления.

Далее снова со ссылкой на фиг.16 описана зависимость соединения на уровне микросхем, включая триггеры для синхронизации с источником, которую тестируют в рассматриваемом варианте осуществления.

Сначала рассмотрим микросхему А на передающей стороне. Помимо упомянутых выше FF_T, микросхема А включает схему 11 ФАПЧ и контроллер 12 ФАПЧ в качестве устройства для передачи исполнительных синхроимпульсов, генератор 13 сдвоенных импульсов для извлечения сдвоенных импульсов из исполнительных синхроимпульсов, передаваемых схемой 11 ФАПЧ, и затем вывода импульсов, контроллер 14 ТАР для управления JTAG и регистр 15 команд (IR). Выходы контроллера 14 ТАР и регистра 15 команд через логические элементы А1 и A3 подают в FF_T, генератор 13 сдвоенных импульсов и т.п.

Контроллер 12 ФАПЧ управляет схемой 11 ФАПЧ таким образом, чтобы схема 11 ФАПЧ осуществляла передачу на той же частоте, что и в процессе реальной работы, после сохранения тестового бита в регистре 15 команд.

Логический элемент И А1 подает синхросигнал ClockDR в TDR_FF, когда тестовый бит сохранен в регистре 15 команд, и параллельно, когда ShiftDR="1". В результате непосредственно инициируют FF_T.

Логический элемент И A3 подает в FF_T управляющий сигнал SG_P для установки внутри каждого из FF_T циклического состояния, а также подает в генератор 13 сдвоенных импульсов запускающий сигнал для извлечения сдвоенных импульсов из выходного сигнала схемы 11 ФАПЧ, когда тестовый бит сохранен в регистре 15 команд, и параллельно, когда RunTestIdle="1".

Далее рассмотрим микросхему В на принимающей стороне. Помимо упомянутых выше FF_R и TDR_FF, микросхема В включает контроллер 21 ТАР для управления JTAG, регистр 22 команд, схему 23 DDL для задержки синхроимпульса и контроллер 24 синхроимпульсов для управления схемой 23 DDL и непоказанной схемой ФАПЧ. Выходные сигналы контроллера 21 ТАР и регистра 22 команд через логические элементы И А4 и А5 поступают в TDR_FF и т.п.

Контроллер 24 синхроимпульсов управляет схемой 23 DDL и схемой ФАПЧ таким образом, чтобы схема 23 DDL и непоказанная схема ФАПЧ могли осуществлять передачу на той же частоте, что и в процессе реальной работы после сохранения тестового бита в регистре 22 команд.

Логический элемент И А4 подает в мультиплексоры M1 и М2 управляющий сигнал, согласно которому мультиплексоры M1 и М2 выбирают данные, отображающие "1", когда тестовый бит сохранен в регистре 22 команд, и параллельно, когда ShiftDR="1". За счет того, что мультиплексоры M1 и М2 выбирают данные, отображающие "1", осуществляют сканирование тракта TDI (тестовые данные на входе) - TDO (тестовые данные на выходе) в соответствии с синхросигналом тестирования ТСК и вводят значение в каждый из TDR_FF.

Логический элемент И А5 подает через TDR_FF управляющий сигнал для установки или сброса FF_R, когда тестовый бит сохранен в регистре 22 команд, и параллельно, когда UpdateDR_L="1". От значений, введенных в соответствующие TDR_FF, как это описано выше, зависит, должны ли быть установлены или сброшены FF_R. Таким способом определяют исходные значения FF_R.

ClockDR контроллера 21 ТАР подает синхросигнал тестирования ТСК в TDR_FF, когда ShiftDR="1" или когда CaptureDR="1". В соответствии с синхросигналом тестирования ТСК осуществляют сканирование тракта TDI-TDO, a TDR_FF осуществляют сбор данных, хранящихся в FF_R.

Далее описаны операции, осуществляемые при тестировании с использованием схемы, имеющей описанную выше конфигурацию.

На фиг.21 показана диаграмма, иллюстрирующая формы сигналов в микросхемах А и В во время тестирования. Поскольку последовательность тестирования аналогична последовательности согласно первому варианту осуществления, которая описана со ссылкой на фиг.7, далее она также описана со ссылкой на фиг.7.

Сначала в каждом из регистров 15 и 22 команд соответственно микросхем А и В сохраняют тестовый бит. Тем самым приводят в действие схемы 11 ФАПЧ микросхем А и В (схема ФАПЧ микросхемы В не показана) для передачи каждой из них исполнительного синхроимпульса (шаг 701). Затем согласно произвольному значению инициируют каждый из триггеров для синхронизации с источником (FF_T и FF_R на фиг.16 и F21-F24 на фиг.18) (шаг 702).

В данном варианте осуществления каждый из триггеров также инициируют способом, который соответствует стандарту JTAG 1149. Тем не менее, рассмотрим фиг.21. Показанный на фиг.17 мультиплексор S1 выбирает синхросигнал ClockDR на выходе контроллера 14 ТАР в соответствии с сигналом SS_P, за счет чего осуществляют сканирование трактов данных со сдвигом в соответствии с этим синхросигналом ClockDR. В результате происходит непосредственная инициализация триггеров F21 и F22, в которые вводят тестовые данные. В то же время, как и в первом варианте осуществления, триггеры F23 и F24 микросхемы инициируют в соответствии с хранящимися в TDR_FF значениями, которые соответствуют триггерам F21 и F22, как это показано ниже на временной диаграмме сигналов (следует отметить, что эту инициализацию осуществляют раньше по времени, чем инициализацию триггеров F21 и F22 микросхемы А).

В дальнейшем генератор 13 сдвоенных импульсов, приведенный в действие RunTestIdle="1" микросхемы А на передающей стороне, передает сдвоенные импульсы из выходного сигнала схемы 11 ФАПЧ (шаг 703). В данном варианте осуществления выходной сигнал CLK2 генератора 13 сдвоенных импульсов выбирают в показанном на фиг.17 мультиплексоре S 1, когда ShiftDR="0". Как показано на фиг.6, выводят управляющий сигнал SG_P для установки внутри FF_T циклического состояния, а затем выводят синхросигналы CLK2 для получения сдвоенных импульсов.

Затем в соответствии со сдвоенными импульсами триггеры F1 и F22 соответственно передают тестовые данные, сохраненные в триггере F1, и синхроимпульс микросхеме В на принимающей стороне (шаг 704). Триггеры F23 и F24 микросхемы В осуществляют сбор данных, передаваемых триггером F21 микросхемы А, в соответствии с синхроимпульсом, передаваемым триггером F22 (шаг 705). После этого в микросхеме В на принимающей стороне защелкивают значения, зарегистрированные триггерами F23 и F24 соответственно в TDR_DP и TDR_DN. Затем значения в защелке извлекают из изучаемых TDO (шаг 706).

В изложенном выше описании с первого по третий варианты осуществления примерами служили случаи, в каждом из которых в качестве триггеров для синхронизации с источником используют триггеры, образующие тракт сканирования JTAG. Вместе с тем, очевидно, что возможны иные конфигурации при условии, что они соответствуют сущности и объему настоящего изобретения. В частности, ввод исходных значений и изучение результатов можно легко осуществить с использованием тракта сканирования помимо тракта сканирования JTAG. В современных ASIC обычно применяют конфигурацию для тестирования методом сканирования с использованием JTAG. Соответственно, предпочтительно, чтобы тест проводился с использованием таких триггеров, образующих тракт сканирования. Вместе с тем не исключен случай, когда для тестирования межсоединений согласно рассмотренным вариантам осуществления в ASIC применяется отдельная конфигурация схемы.

Изобретение относится к средствам тестирования взаимосвязанных больших интегральных микросхем (БИС) на уровне плат в реальных условиях эксплуатации. Техническим результатом является обеспечение тестирования на рабочей частоте на уровне плат без применения теста системного уровня, а также оценки данных, передаваемых по каждому каналу передачи. Микрокомпьютер (ASIC) включает множество ИС, которые соединены друг с другом синхронными с источниками данных интерфейсами. Сначала в триггер для передачи данных (F1) и триггер для передачи синхроимпульса (F2) в ИС на стороне передачи данных вводят тестовые данные. Затем схема (11) ФАПЧ генерирует синхросигнал, в ответ на который первый и второй триггеры передают тестовые данные и синхроимпульс. Триггеры (F3, F4) для приема данных ИС на стороне приема данных регистрируют тестовые данные, поступающие из первого триггера (F1) в соответствии с синхроимпульсом, поступающим из триггера (F2). 3 н. и 9 з.п. ф-лы, 21 ил.

1. Микрокомпьютер, в котором установлено несколько интегральных схем (ИС), соединенных друг с другом синхронным с источником интерфейсом, отличающийся тем, что

имеется ИС на стороне для передачи данных через синхронный с источником интерфейс, включающая

схему фазовой автоподстройки частоты (ФАПЧ) для передачи исполнительного синхроимпульса в процессе реальной работы,

первый триггер для передачи тестовых данных в соответствии с исполнительным синхроимпульсом, передаваемым схемой ФАПЧ, и

второй триггер для передачи синхронного с источником синхроимпульса в соответствии с исполнительным синхроимпульсом, передаваемым схемой ФАПЧ, и

имеется ИС на стороне приема данных через синхронный с источником интерфейс, включающая

третий триггер для сбора тестовых данных, передаваемых первым триггером, в соответствии с синхроимпульсом, передаваемым вторым триггером.

2. Микрокомпьютер по п.1, отличающийся тем, что ИС на передающей стороне дополнительно включает схему генерирования сдвоенных импульсов для извлечения двухимпульсных сигналов из исполнительных синхроимпульсов, передаваемых схемой ФАПЧ, первый триггер способен передавать тестовые данные в соответствии с двухимпульсными сигналами, извлеченными из схемы генерирования сдвоенных импульсов, а

второй триггер способен передавать синхроимпульс в соответствии с двухимпульсными сигналами, извлеченными из схемы генерирования сдвоенных импульсов.

3. Микрокомпьютер по п.1, отличающийся тем, что первый триггер ИС на передающей стороне способен передавать тестовые данные с задержкой, равной полупериоду двухимпульсных сигналов, относительно синхроимпульса, передаваемого вторым триггером.

4. Микрокомпьютер по п.1, отличающийся тем, что

первый триггер ИС на передающей стороне способен передавать тестовые данные на фронте того же синхроимпульса, что и синхроимпульс, передаваемый вторым триггером, а

ИС на принимающей стороне имеет средство задержки для передачи принимаемого синхроимпульса третьему триггеру с задержкой π/2.

5. Микрокомпьютер по п.1, отличающийся тем, что первый триггер ИС на передающей стороне является триггером с раздельными входами, а

ИС на передающей стороне дополнительно включает регистр тестовых данных для сохранения тестовых данных в первом триггере путем установки или сброса первого триггера в соответствии с сохраненным значением.

6. Микрокомпьютер по п.1, отличающийся тем, что первый триггер ИС на передающей стороне образует тракт сканирования, а тестовые данные вводят в первый триггер путем сканирования трактов данных со сдвигом через тракт сканирования.

7. Способ тестирования микрокомпьютера, в котором установлено несколько интегральных схем (ИС), соединенных друг с другом синхронным с источником интерфейсом, включающий:

стадию, на которой в ИС на стороне передачи данных через синхронный с источником интерфейс вводят исходные значения первого триггера для передачи данных и второго триггера для передачи синхроимпульса,

стадию, на которой передают синхросигнал схемы ФАПЧ для передачи исполнительного синхроимпульса в процессе реальной работы, после чего первый триггер и второй триггер соответственно передают данные исходных значений и синхроимпульс, и

стадию, на которой в ИС на стороне приема данных через синхронный с источником интерфейс посредством третьего триггера для приема данных осуществляют сбор исходных значений, передаваемых первым триггером, в соответствии с синхроимпульсом, передаваемым вторым триггером.

8. Способ тестирования по п.7, отличающийся тем, что стадия ввода исходных значений в первый и второй триггеры включает:

шаг, на котором каждый из регистров тестирования, согласованных соответственно с первым и вторым триггерами, сохраняет заданное значение, и

шаг, на котором посредством регистров тестирования в соответствии с сохраненными в них значениями осуществляют установку или сброс первого триггера и второго триггера для ввода исходных значений в первый триггер и второй триггер.

9. Способ тестирования по п.7, отличающийся тем, что на стадии ввода исходных значений в первый триггер и второй триггер исходные значения вводят путем сканирования трактов данных со сдвигом через тракт сканирования относительно первого триггера и второго триггера, образующих тракт сканирования.

10. Способ тестирования микрокомпьютера, в котором установлено несколько интегральных схем (ИС), соединенных друг с другом синхронным с источником интерфейсом, включающий:

стадию, на которой посредством триггера на стороне передачи данных через синхронный с источником интерфейс принимают и сохраняют тестовые данные,

стадию, на которой передают синхросигнал схемы ФАПЧ для передачи исполнительного синхроимпульса в процессе реальной работы, после чего передают тестовые данные, сохраненные в триггере на передающей стороне, и синхронный с источником синхроимпульс и

стадию, на которой посредством триггера на стороне приема данных через синхронный с источником интерфейс осуществляют сбор тестовых данных в соответствии с синхроимпульсом.

11. Способ тестирования по п.10, отличающийся тем, что стадия приема тестовых данных триггером на передающей стороне включает:

шаг, на котором сохраняют заданное значение в регистре тестовых данных, соответствующем триггеру на передающей стороне, и

шаг, на котором в соответствии со значением, сохраненным в регистре тестовых данных, осуществляют установку или сброс триггера на передающей стороне, которому соответствует регистр тестовых данных, чтобы триггер на передающей стороне сохранил тестовые данные.

12. Способ тестирования по п.10, отличающийся тем, что на стадии приема тестовых данных триггером на передающей стороне посредством триггера на передающей стороне сохраняют тестовые данные путем сканирования трактов тестовых данных со сдвигом через тракт сканирования относительно триггера на передающей стороне, образующего тракт сканирования.

| JP, 2004-294424, А, 21.10.2004 | |||

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Статор многоступенчатого центробежного компрессора | 1986 |

|

SU1377465A1 |

| JP, 8-240645, A, 17.09.1996 | |||

| JP, 6-289099, A, 18.10.1994. | |||

Авторы

Даты

2009-11-27—Публикация

2006-06-08—Подача