Изобретение относится к защищенной памяти. Более конкретно, настоящее изобретение относится к защищенной памяти, которая обеспечивает множество уровней защиты для зон приложений.

Пластиковые карточки используются для платежей с 1950-х годов с началом введения международной кредитной карточки, выдававшейся членам Дайнерз клуба. Масштабы их использования с того времени расширились феноменальным образом. В настоящее время миллионы карточек используются ежегодно различными организациями, так что их использование для платежей и для записей информации в настоящее время стало практически повсеместным.

Первоначально такие пластиковые карточки выполнялись тиснеными с рельефным изображением и имели строку подписи, которая должна была использоваться для обеспечения защищенности. Однако можно себе представить, что это в весьма малой степени способствовало предотвращению подделок и мошенничества. Первым важным усовершенствованием в направлении обеспечения защищенности было введение магнитной полосы на обратной стороне тисненой карточки. Пластиковые карточки с магнитной полосой представляют собой, вероятно, наиболее популярную форму платежных и информационных карточек, доступных для использования в настоящее время. Память, обеспечиваемая магнитной полосой, также позволила записывать намного больше информации, чем это могло быть выполнено тиснением на поверхности карточки. Хотя такие карточки обеспечивают некоторый уровень защиты, однако данные, хранящиеся на магнитной полосе, могут быть без труда считаны, удалены и перезаписаны любым лицом, имеющим доступ к соответствующему устройству записи/считывания. Соответственно, такие карточки менее чем пригодны для хранения данных конфиденциального характера или для хранения стоимости, используемой вместо наличных.

Для решения этих проблем была разработана пластиковая карточка с защищенной памятью. Такие карточки известны в промышленности как "интеллектуальные карточки". Область хранения защищенной памяти часто подразделяется на блоки памяти. Целью обеспечения защищенности памяти является защита от несанкционированного доступа и неправомочного манипулирования с этими блоками. Защищенность в типовом случае обеспечивается некоторой комбинацией аппаратных средств и программного обеспечения. С использованием защищенной памяти можно записывать данные конфиденциального характера, которые невозможно считать или стереть, и предотвращать запись данных путем контролирования процессов считывания, записи и стирания с помощью комбинации аппаратных средств и программного обеспечения, которая зависит от конкретных условий, которые должны возникнуть перед выполнением этих операций.

Примером интеллектуальной карточки с защищенной памятью, которая находит широкое применение, является телефонная карточка с памятью. Такие карточки являются предварительно оплачиваемыми (дебетовыми) карточками, причем стоимость, хранящаяся с помощью электронных средств в памяти, изменяется в процессе использования карточки путем уменьшения на соответствующую сумму. Разумеется, для предотвращения неправомочного использования необходимо предотвратить возможность пользователя манипулировать с карточкой таким образом, чтобы увеличить хранящуюся стоимость. В случае карточки с магнитной полосой перезапись новой стоимости на карточку могло выполняться без особого труда.

Один из известных способов предотвращения неправомочного манипулирования с защищенной карточкой для увеличения хранящейся стоимости является использование кода защиты, который известен только эмитенту карточки. Систематические попытки определить код защиты пресекаются за счет использования счетчика попыток доступа, который предотвращает дальнейшее использование карточки, если число попыток представления действительного секретного кода превышает предварительно определенное их число. Если действительный код защиты представлен до достижения предельного числа попыток, то счетчик попыток доступа сбрасывается в нуль. Каждый из этих блоков дополнительно защищается кодом стирания, который должен быть представлен, прежде чем хранящийся блок можно будет стереть. К сожалению, такие коды стирания являются уязвимыми по отношению к регулярным попыткам определения кода.

Другим способом предотвращения неправомочных попыток манипулирования с телефонными карточками было обеспечение по существу невозможности стирания ячейки памяти после того, как она записана. Для данного типа карточек в типовом случае предусматривается пережигание предохранительной перемычки, что делает недоступной функцию стирания. Соответственно, после того как путем записи в память осуществлено уменьшение стоимости на карточке, дополнительная стоимость не может быть добавлена в память путем стирания. Хотя данный метод в достаточной мере адекватен для предотвращения неправомочного манипулирования с карточками, однако он не вполне привлекателен для использования по той причине, что если стоимость на карточке удалена, то карточка не может быть повторно использована путем добавления дополнительной стоимости на карточку.

Соответственно задачей изобретения является обеспечить дополнительную защищенность для памяти, встраиваемой в устройства, требующие применения защищенной памяти, такие как интеллектуальные карточки.

Кроме того, задачей изобретения является обеспечение защищенности для памяти, встраиваемой в устройства с защищенной памятью, такие как интеллектуальные карточки, таким образом, чтобы не препятствовать повторному использованию интеллектуальной карточки в процессе обращения с ней пользователем.

В соответствии с настоящим изобретением защищенная память содержит зону первого уровня защищенности, имеющую код доступа, контролирующий доступ к упомянутой защищенной памяти до пережигания предохранительной перемычки, предусмотренной эмитентом карточки, счетчик попыток ввода кода защиты для предотвращения доступа к упомянутой защищенной памяти, если предварительно определенное число попыток совпадения с упомянутым кодом доступа сделано до сброса счетчика попыток ввода кода защиты, множество зон приложений, каждая из которых включает в себя зону хранения, зону защиты приложения, имеющую код доступа к зоне приложения, контролирующий доступ к зоне хранения после пережигания предохранительной перемычки, счетчик попыток ввода кода защиты зоны приложения, предотвращающий доступ к зоне приложения, если предварительно определенное число попыток совпадения с кодом доступа к зоне приложения сделано до сброса счетчика попыток ввода кода защиты зоны приложения, участок ключа стирания, имеющий код ключа стирания, контролирующий доступ стирания к зоне хранения после пережигания предохранительной перемычки, предусмотренной эмитентом карточки, и счетчик попыток ввода ключа стирания, предотвращающий доступ стирания к зоне приложения, если предварительно определенное число попыток совпадения с кодом ключа стирания было сделано до сброса счетчика попыток ввода ключа стирания.

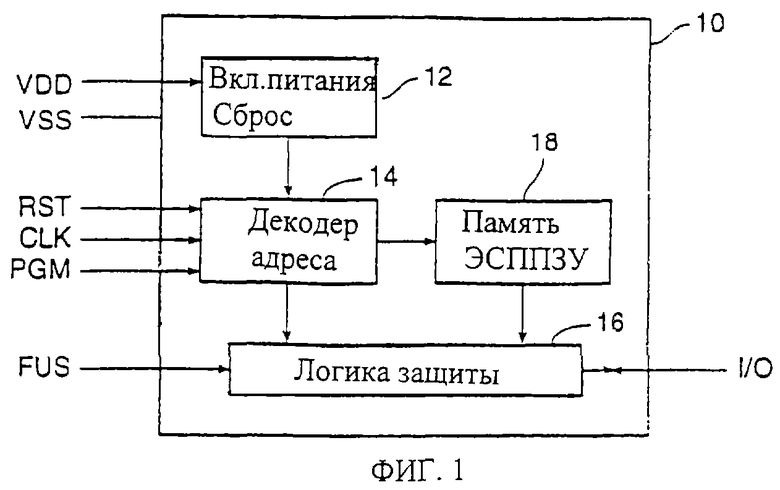

Фиг. 1 иллюстрирует обобщенную архитектуру в виде блок-схемы защищенной памяти согласно настоящему изобретению.

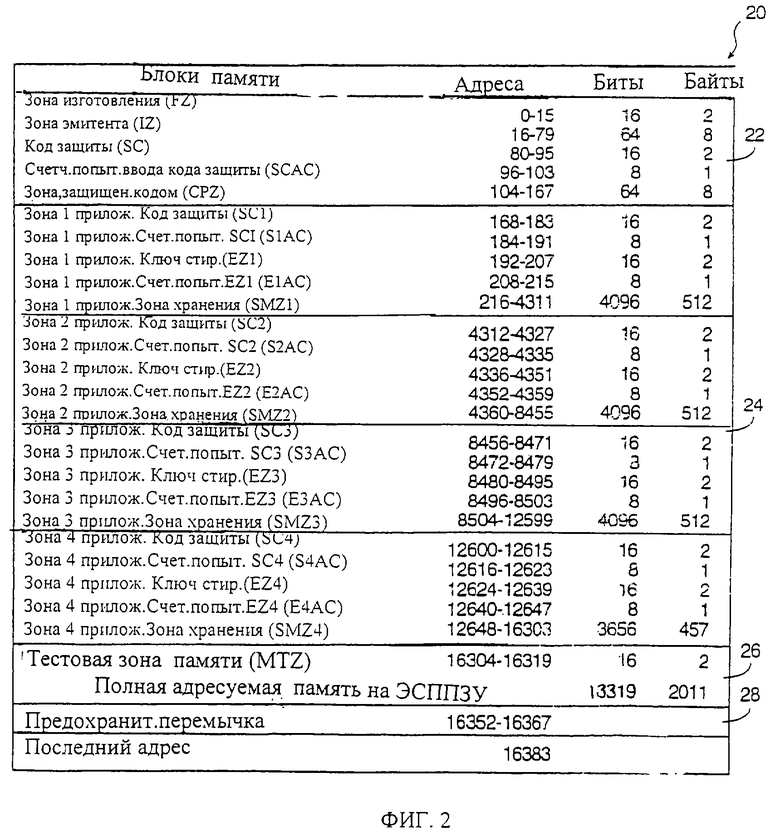

Фиг.2 отображает карту памяти электронно-стираемого программируемого постоянного запоминающего устройства (ЭСППЗУ), подразделенной в соответствии с настоящим изобретением.

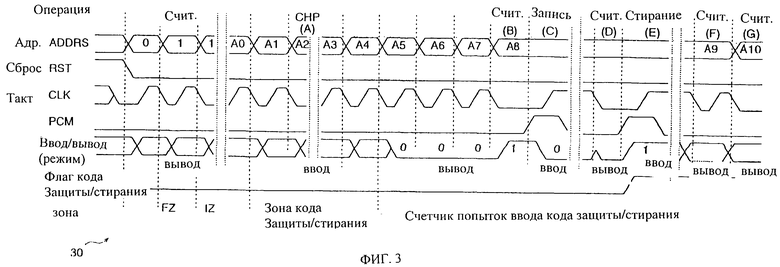

Фиг. 3 - временная диаграмма сравнения кода защиты и проверки правильности в соответствии с изобретением.

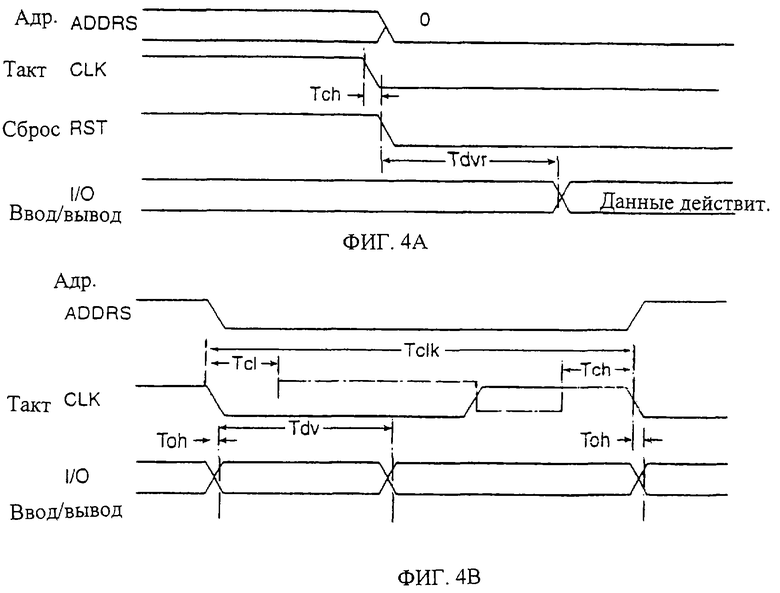

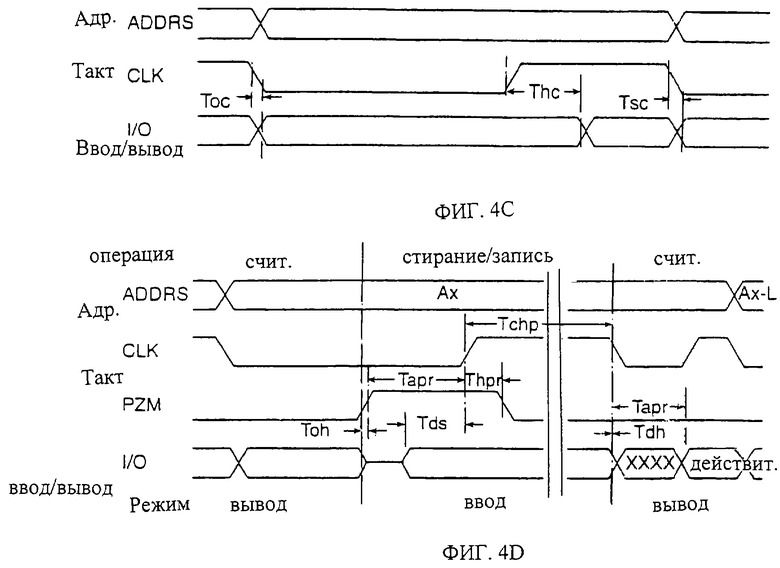

Фиг. 4А - временная диаграмма операции установки в исходное состояние, пригодной для использования в настоящем изобретении.

Фиг.4В - временная диаграмма операции считывания, пригодной для использования в настоящем изобретении.

Фиг.4С - временная диаграмма операции сравнения, пригодной для использования в настоящем изобретении.

Фиг.4D - временная диаграмма операции стирания/записи, пригодной для использования в настоящем изобретении.

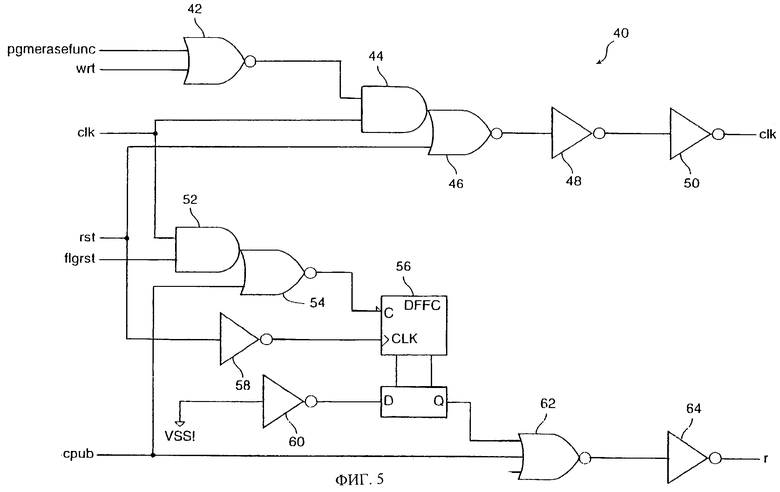

Фиг. 5 - схема контроля местоположения адреса в памяти ЭСППЗУ, которая может быть использована в настоящем изобретении.

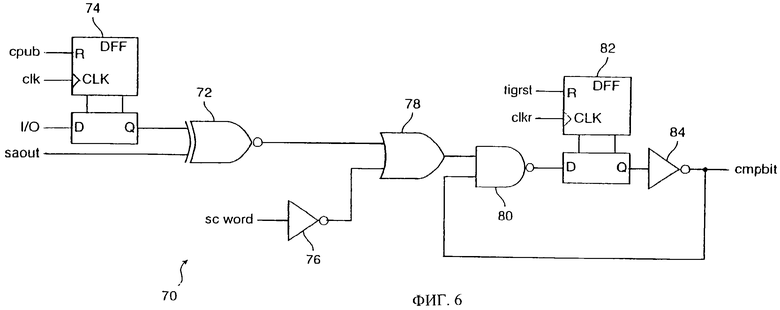

Фиг. 6 - схема сравнения кода защиты, которая может быть использована в настоящем изобретении.

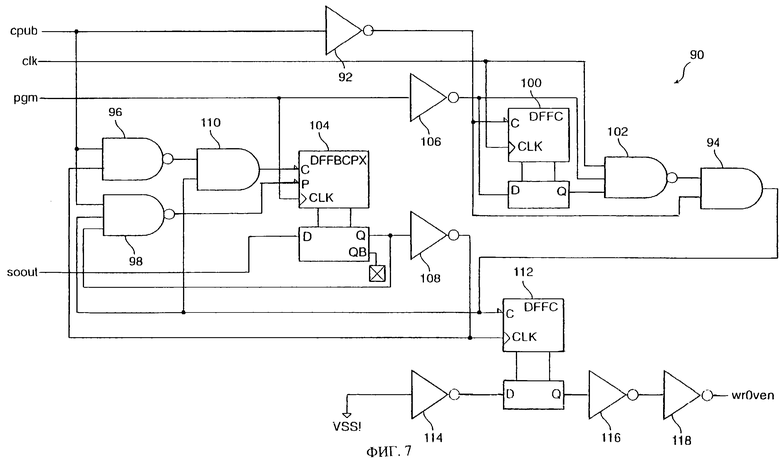

Фиг. 7 - схема проверки правильности записи нуля, которая может быть использована в настоящем изобретении.

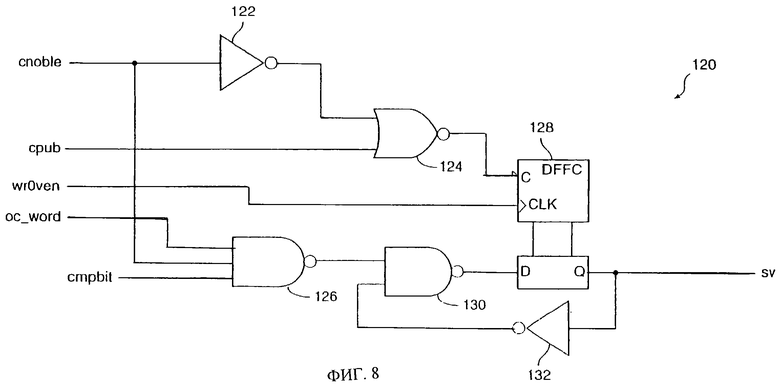

Фиг. 8 - схема установки флага защищенности, которая может быть использована в настоящем изобретении.

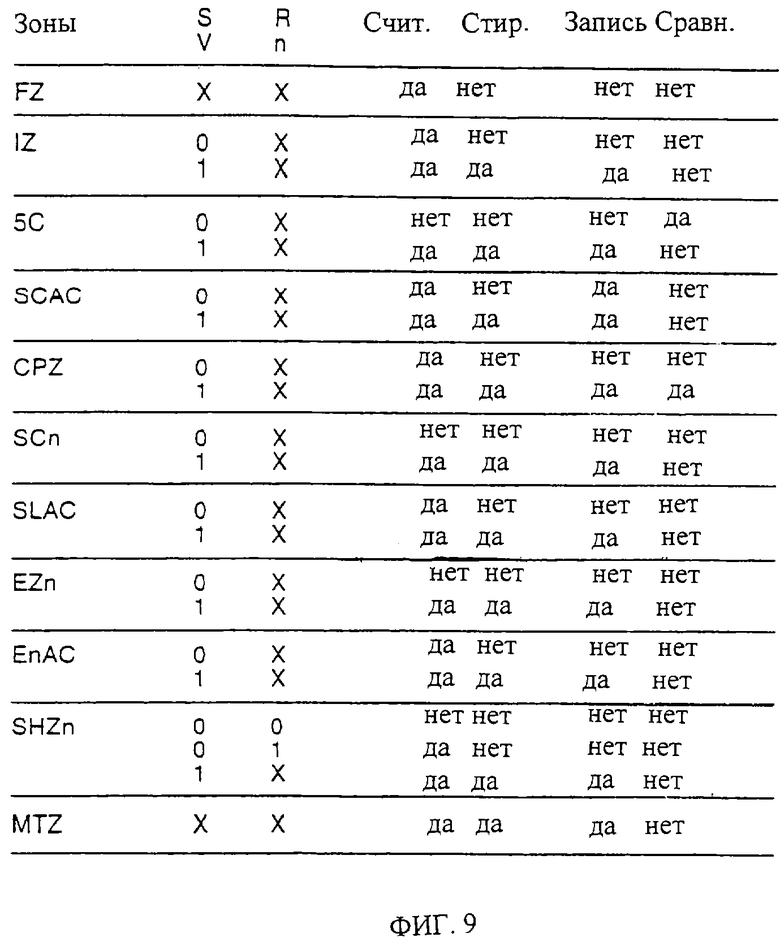

Фиг.9 - таблица условий доступа для персонализации защищенной памяти перед установкой предохранительной перемычки в состояние логического "0" в соответствии с настоящим изобретением.

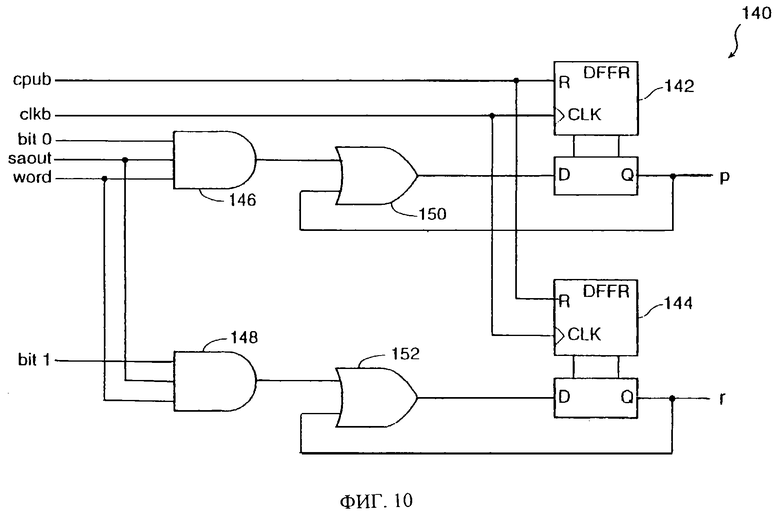

Фиг.10 - схема установки флагов Rn и Рn, которая может быть использована в настоящем изобретении.

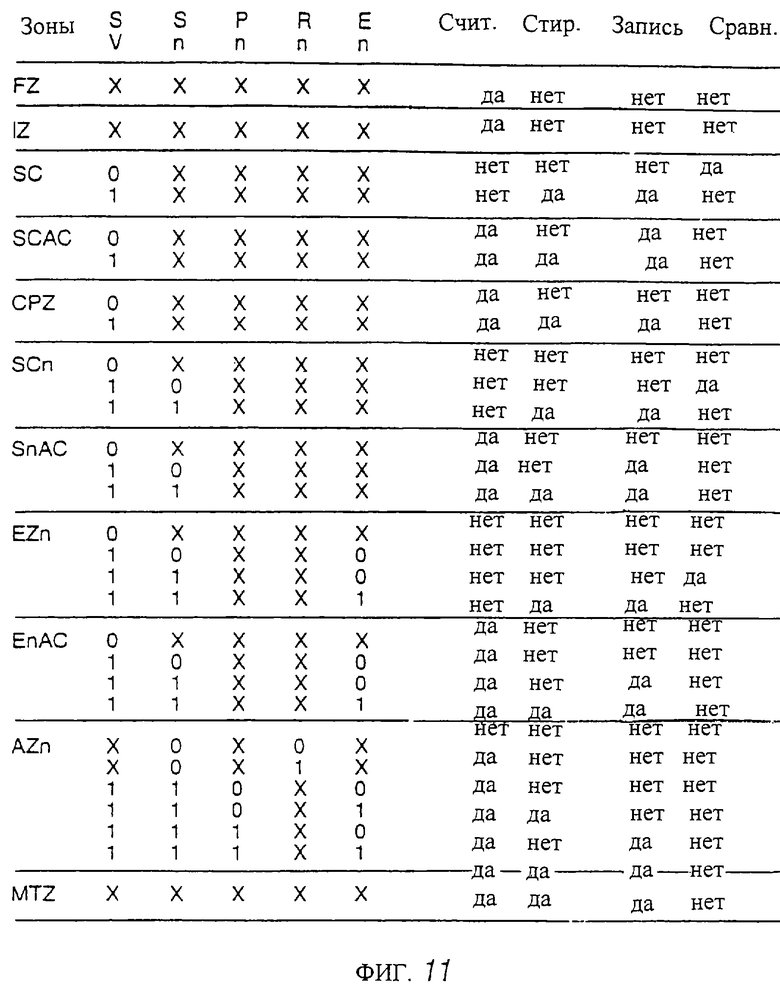

Фиг. 11 - таблица условий доступа для персонализации защищенной памяти после установки предохранительной перемычки в состояние логического "0" в соответствии с настоящим изобретением.

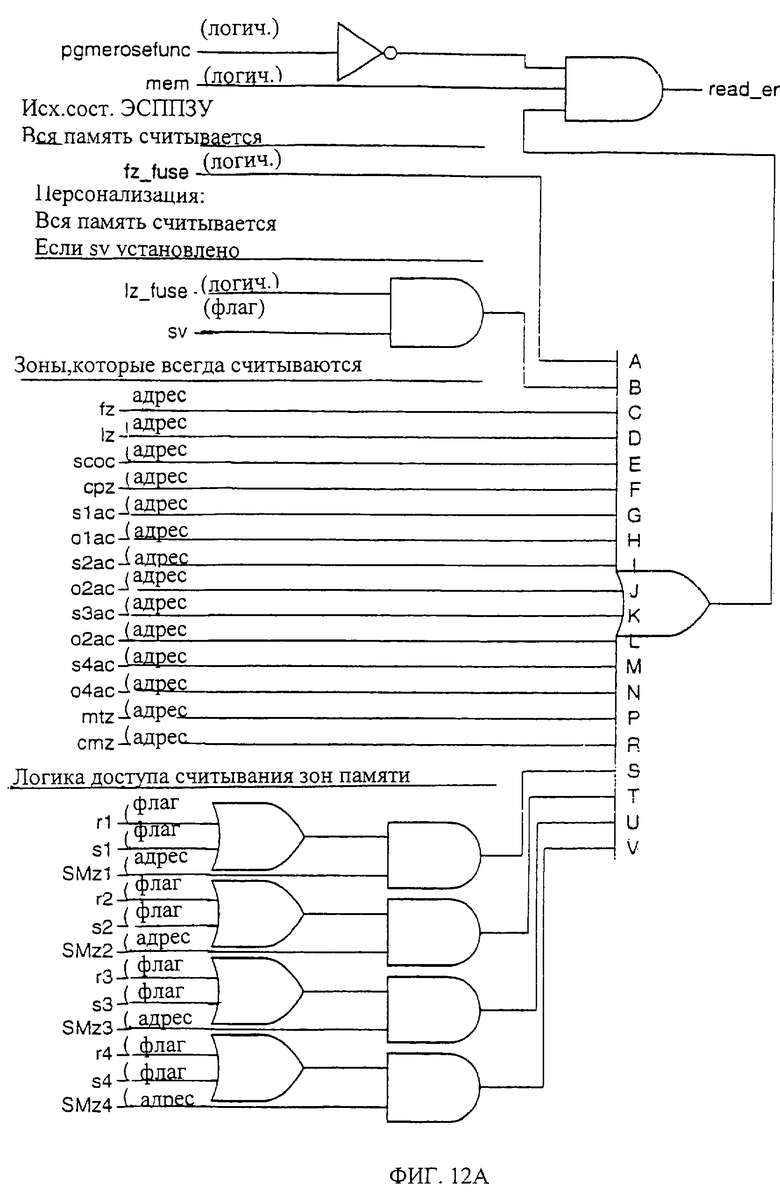

Фиг. 12А - схема генерирования сигнала разрешения считывания, соответствующая настоящему изобретению.

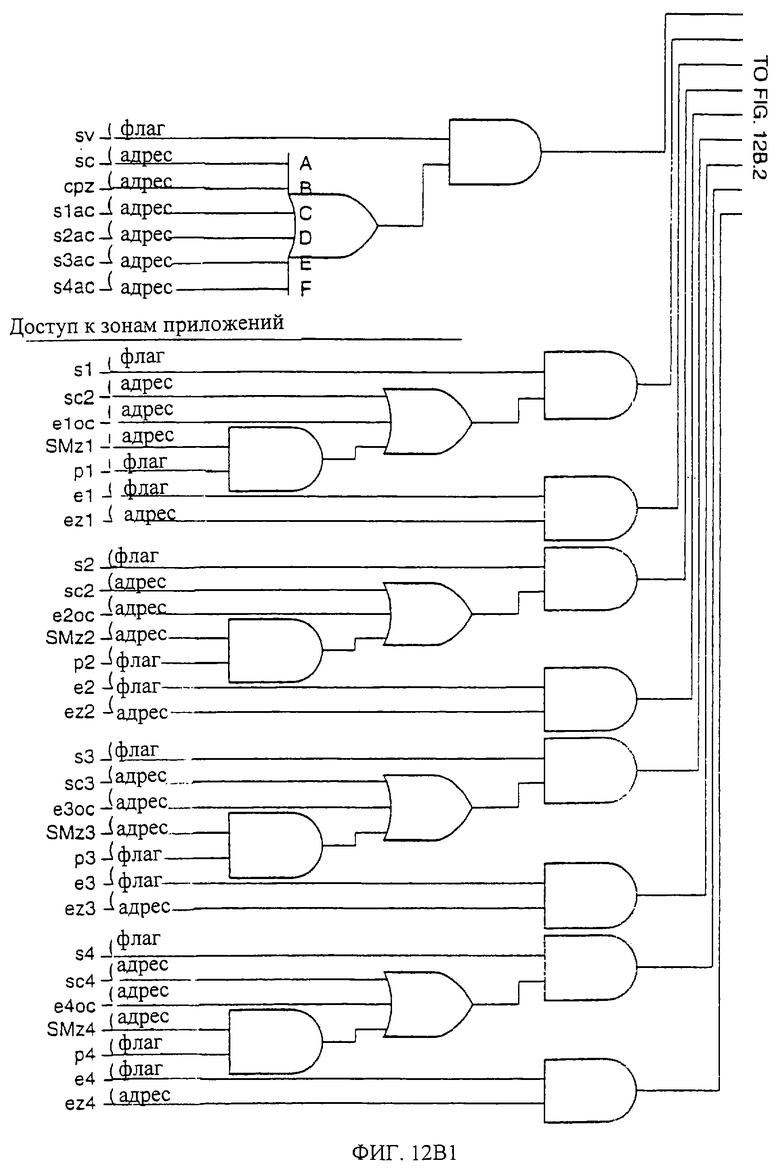

Фиг. 12В1 - схема генерирования сигнала управления записью предохранительной перемычки и сигнала управления записью, соответствующая настоящему изобретению.

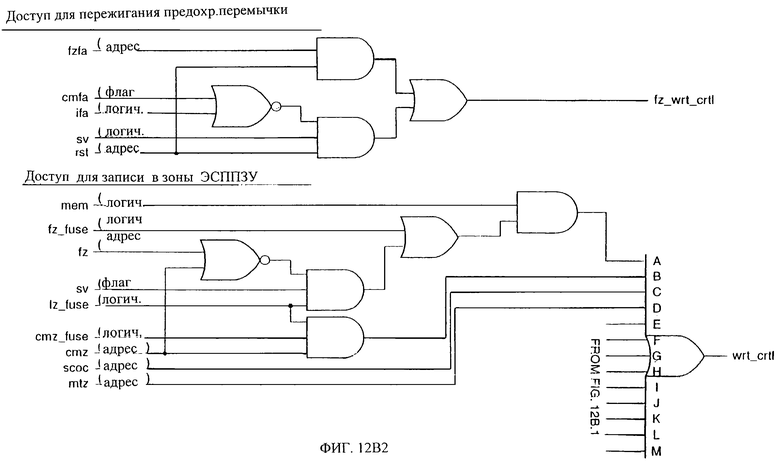

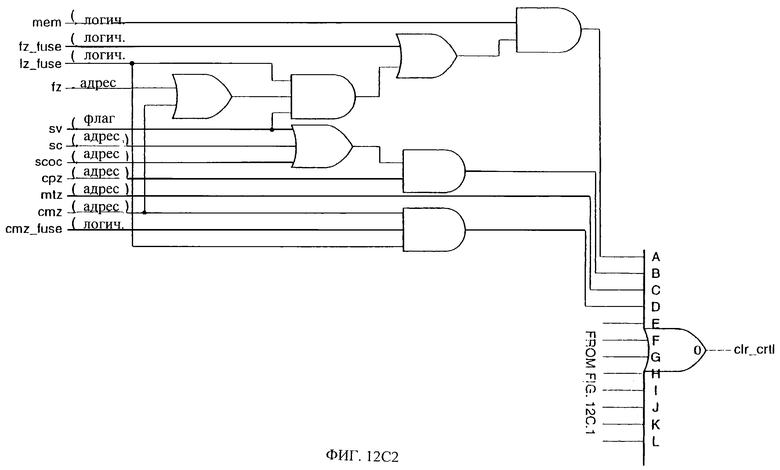

Фиг.12В2 - схема генерирования сигнала управления стиранием, соответствующая настоящему изобретению.

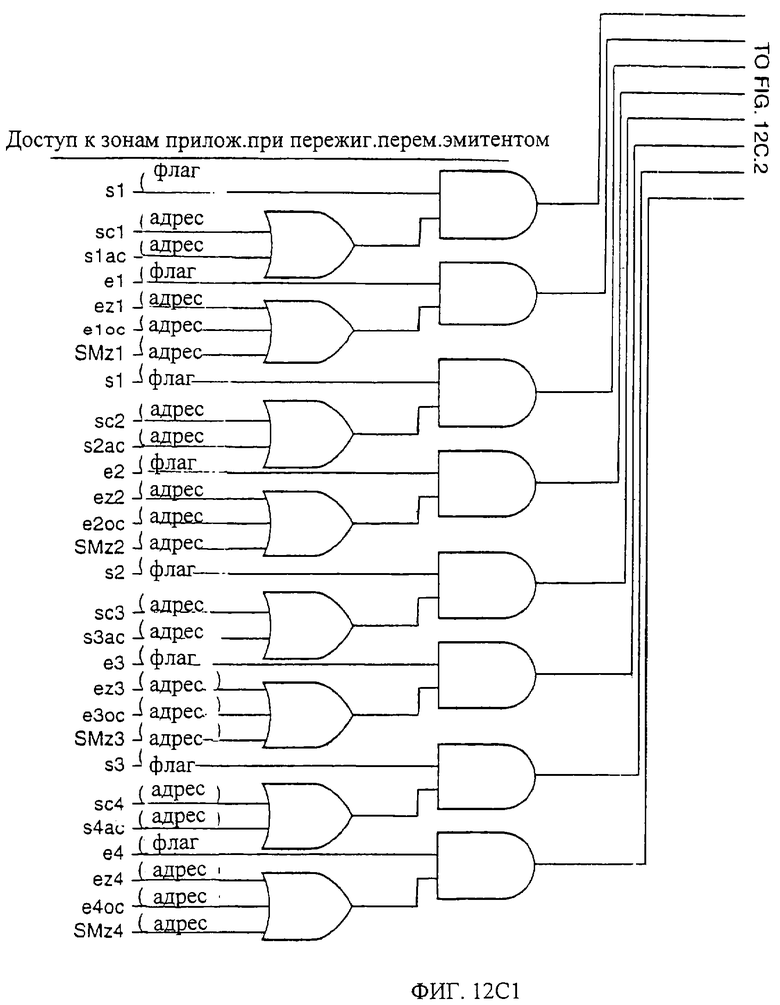

Фиг. 13 - схема генерирования сигналов записи предохранительной перемычки, записи и разрешения стирания, соответствующая настоящему изобретению.

Специалистам в данной области техники должно быть понятно, что последующее описание настоящего изобретения является иллюстративным, но не ограничительным. Специалисты в данной области техники смогут легко предложить другие варианты осуществления настоящего изобретения.

В типовом случае по меньшей мере три группы специалистов участвуют в манипулировании защищенной памятью, которая введена в интеллектуальную карточку. Первую группу представляет изготовитель защищенной памяти. Вторую группу представляет изготовитель карточек, который вводит защищенную память в интеллектуальную карточку и затем распространяет интеллектуальные карточки среди конечных пользователей. (Часто функции изготовления карточек и эмитента карточек или дистрибьютора выполняются различными группами специалистов.) Третью группу составляют пользователи защищенной памятью, которые получили данный продукт от эмитента или дистрибьютора. В соответствии с настоящим изобретением обеспечивается более высокая степень защищенности, чем это имело место согласно предшествующему уровню техники, для предотвращения несанкционированного использования защищенной памяти конечными пользователями или лицами, непосредственно не участвующими в процедурах с использованием защищенной памяти.

Блок-схема обобщенной архитектуры защищенной памяти 10 согласно настоящему изобретению показана на фиг.1. Защищенная память 10 содержит следующие блоки: блок 12 включения/сброса питания, декодер 14 адреса, блок 16 логики защиты, память 18 на ЭСППЗУ. Защищенная память 10 имеет восемь выводов, а именно: VDD, VSS, RST, CLK, PGM, FUS, I/O, соединенные с различными блоками в составе защищенной памяти, как показано на чертеже. Как будет пояснено ниже, память 18 на ЭСППЗУ подразделена на области, и санкционированный доступ к различным областям памяти для выполнения операций СЧИТЫВАНИЕ, ЗАПИСЬ, СРАВНЕНИЕ и СТИРАНИЕ контролируется средствами обеспечения защищенности, предусмотренными в соответствии с настоящим изобретением.

Для предотвращения несанкционированного доступа к памяти 18 на ЭСППЗУ следует учитывать два потенциально возможных случая несанкционированного доступа. Первый случай может возникнуть при передаче защищенной памяти 10 от изготовителя защищенной памяти 10 к эмитенту защищенной памяти 10. Для предотвращения несанкционированного использования защищенной памяти 10 лицами, которые могут перехватить защищенную память от эмитента, код защиты, определенный изготовителем и переданный эмитенту, должен использоваться эмитентом для получения доступа к защищенной памяти. В соответствии с настоящим изобретением защищенность обеспечивается для предотвращения несанкционированного использования лицом иным, чем конечный пользователь, и для предотвращения возможности неправомочного манипулирования памятью или ее использования лицами иными, чем эмитент, таким способом, который запрещен эмитентом.

На фиг. 2 представлена карта 20 памяти, показывающая различные области памяти, реализованные в памяти 18 на ЭСППЗУ. В карте 20 памяти адрес каждой области памяти в памяти 18 на ЭСППЗУ идентифицирован вместе с числом битов для каждой из областей памяти. Например, область, обозначенная как Зона Изготовления, как будет пояснено ниже, находится по адресам от 0 до 15 в карте 20 памяти и ей выделено 16 битов. Биты в памяти 18 на ЭСППЗУ сгруппированы вместе в виде 8-битовых слов. Карта 20 памяти 18 на ЭСППЗУ разделена на четыре секции 22, 24, 26 и 28 для более четкого понимания каждой из областей подразделения памяти.

Секция 22 карты 20 памяти содержит области для изготовителя и эмитента. Областями в секции 22 являются следующие: Зона Изготовления, Зона Эмитента, Код Защиты, Счетчик Попыток Доступа к Коду Защиты и Защищенная Кодом Зона. Защищенная Кодом Зона также доступна для конечного пользователя.

Зона Изготовления и Зона Эмитента содержат каждая информацию, относящуюся к изготовителю и эмитенту соответственно. Зона Изготовления программируется изготовителем защищенной памяти и является неизменяемой. Доступ к Зоне Эмитента контролируется с помощью флага кода защиты, который устанавливается, когда защищенная память 10 распознает действительный код защиты.

Область для Кода Защиты содержит код защиты, для которого должно быть обеспечено совпадение эмитентом для получения доступа к памяти 18 на ЭСППЗУ и тем самым персонализации различных областей в памяти 18 на ЭСППЗУ. Код защиты обеспечивает защиту пересылки между изготовителем и эмитентом, и, как будет более подробно описано ниже, после того как память 18 на ЭСППЗУ будет персонализирована эмитентом, код защиты препятствует несанкционированному доступу к зонам прикладных программ (приложений) памяти 18 на ЭСППЗУ. Как таковой, код защиты представляет собой глобальный контроль доступа для всей памяти 18 на ЭСППЗУ.

Счетчик попыток ввода кода защиты подсчитывает число попыток, осуществленных при представлении кода защиты. Защищенная память остается блокированной, если счетчик попыток ввода кода защиты регистрирует восемь неправильных представлений кода защиты. Защищенная кодом зона представляет собой область, которая может быть использована как сверхоперативная память, в которой разрешен доступ для считывания, и операции ЗАПИСЬ/СТИРАНИЕ контролируются флагом кода защиты.

Секция 24 карты 20 памяти содержит четыре зоны приложений, которые включают в себя области как для защиты, так и для хранения. Каждая из четырех зон приложений, показанных в карте 20 памяти, включает в себя области для кода защиты, счетчика попыток ввода кода защиты, ключа стирания, счетчика попыток ввода ключа стирания и зону хранения. Как только память 18 на ЭСППЗУ персонализирована эмитентом, области для кода защиты и счетчика попыток ввода кода защиты в каждой из зон приложений контролируют доступ считывания и записи, в комбинации с другими мерами защиты, к связанным с ними зонам хранения, а области для ключа стирания и счетчика попыток ввода ключа стирания в каждой из зон приложений контролируют доступ стирания, вместе с другими мерами защиты, к связанной с ними зоне хранения. Следует иметь в виду, что для специалистов в данной области техники запись в ЭСППЗУ представляет собой процесс установки логического "0" для бита памяти на ЭСППЗУ, а стирание - процесс установки логической "1" для бита памяти на ЭСППЗУ.

Секция 26 в зоне тестирования памяти предусмотрена для тестирования всех операций защищенной памяти 10 без необходимости защищенного доступа.

Секция 28 представляет собой область для предохранительной перемычки. Как только защищенная память 10 персонализирована эмитентом, область 28 предохранительной перемычки постоянно находится в состоянии "пережигания" путем установки ее в логический "0". Следует иметь в виду, что бит, соответствующий "пережиганию предохранительной перемычки" представляет собой одиночный бит памяти на ЭСППЗУ, который постоянно установлен в состояние логического "0".

Как описано выше, если защищенная память 10 передается от изготовителя к эмитенту, код защиты, определенный изготовителем, передается изготовителем эмитенту. Для того чтобы обеспечить доступ к защищенной памяти 10 эмитенту для персонализации защищенной памяти 10 для пользователя, эмитент должен ввести код защиты, переданный изготовителем, для сравнения с кодом защиты, запрограммированным изготовителем защищенной памяти в области кода защиты в секции 22 карты 20 памяти. Для того чтобы эмитент получил доступ к памяти 18 на ЭСППЗУ, должно иметь место точное совпадение кода защиты, введенного эмитентом, с кодом защиты, запрограммированным изготовителем.

Для предотвращения систематических попыток нарушения защиты защищенной памяти 10 несанкционированным лицом каждая попытка доступа к защищенной памяти 10 путем ввода кода защиты для сравнения с кодом защиты, запрограммированным изготовителем, подсчитывается счетчиком попыток ввода кода защиты в секции 22. Если сделано восемь безуспешных попыток согласования кода защиты с запрограммированным кодом защиты, то возможность установки флагов защиты блокируется. Всякий раз, когда введенный код защиты сравнивается с запрограммированным кодом защиты и устанавливается их совпадение, счетчик попыток ввода кода защиты сбрасывается в нуль.

На фиг.3 представлена временная диаграмма 30 для успешного сравнения кода защиты и установки флага кода защиты. Согласно диаграмме 30 выполняются операции СБРОС, СЧИТЫВАНИЕ, СРАВНЕНИЕ, ЗАПИСЬ и СТИРАНИЕ. Временные диаграммы для операций СБРОС, СЧИТЫВАНИЕ, СРАВНЕНИЕ и СТИРАНИЕ/ЗАПИСЬ представлены дальше на фиг. 4А - 4D соответственно. Как показано на временной диаграмме 30, для сравнения кода защиты с кодом защиты, запрограммированным изготовителем, сначала на вывод RST (сброс) защищенной памяти 10 подается сигнал сброса. В процессе выполнения операции СБРОС счетчик адреса в декодере 14 адреса устанавливается в нуль и после заднего фронта сигнала сброса на вывод I/O (ввода/вывода) подается первый бит из памяти 18 на ЭСППЗУ. Затем счетчик адреса получает приращение сигналом, выдаваемым на вывод CLK (такт), пока сигнал, подаваемый на вывод PGM (программирование/стирание) защищенной памяти 10, удерживается на низком логическом уровне до тех пор, пока не будет получен адрес области кода защиты. Это представляет собой операцию ЗАПИСЬ.

Счетчик адреса для памяти 18 на ЭСППЗУ управляется схемой 40 управления счетом адреса, показанной на фиг.5. Два сигнала CLKR и R формируются схемой 40 управления счетом адреса для управления многокаскадным счетчиком, который используется для формирования желательного адреса памяти 18 на ЭСППЗУ. Сигнал CLKR является внутренним тактовым сигналом для обеспечения приращения счетчика адреса, а сигнал R является внутренним сигналом, используемым для установки счетчика адреса на нуль.

Схема 40 управления счетом адреса имеет следующие входные сигналы: PGMERASEFUNC, WRT, CLK, RST, FLGRST и CPUB. В схеме управления счетом адреса сигналы PGMERASEFUNC и WRT подаются на входы логической схемы 42 ИЛИ-НЕ. Выходной сигнал логической схемы 42 ИЛИ-НЕ и сигнал CLK подаются на входы логической схемы 44 И. Выходной сигнал логической схемы 44 И и сигнал RST подаются на входы логической схемы 46 ИЛИ-НЕ, а выходной сигнал логической схемы 46 ИЛИ-НЕ проходит через инверторы 48 и 50 для формирования сигнала CLKR. Сигнал CLK и сигнал FLGRST подаются на входы логической схемы 52 И. Выходной сигнал логической схемы И и сигнал CPUB подаются на входы логической схемы 54 ИЛИ-НЕ, выход которой соединен с запускаемым отрицательным фронтом входом очистки D-триггера 56. Сигнал RST также подается через инвертор 58 на тактовый вход D-триггера 56. Вход данных D-триггера 56 поддерживается на высоком логическом уровне с помощью инвертора 60, соединенного с входом Vss. Выходной сигнал данных D-триггера 56 и сигнал CPUB подаются на входы логической схемы 62 ИЛИ-НЕ, а выходной сигнал логической схемы 62 ИЛИ-НЕ проходит через инвертор 64 для формирования сигнала R.

Сигнал PGMERASEFUNC генерируется внутренним образом в схеме, описанной ниже. Он генерируется для того, чтобы перевести в состояние ожидания счетчик адреса путем блокировки пропускания сигнала CLK через схему 42 И при ее переключении, что можно ожидать исходя из анализа схемы 40 управления счетом адреса, когда выполняется цикл стирания или записи. Сигнал RST генерируется внешним образом для сброса счетчика адреса на нуль. Когда сигнал RST осуществляет переход от высокого логического уровня к низкому логическому уровню, D-триггер тактируется и выходной сигнал данных D-триггера 56 переходит на высокий логический уровень. В результате этого сигнал R переходит на высокий логический уровень, а счетчик адреса устанавливается на нуль. Сигнал FLGRST устанавливает сигнал R на низкий логический уровень, после того как счетчик адреса установлен на нуль, когда сигнал R перешел на высокий логический уровень. Сигнал FLGRST генерируется счетчиком адреса, когда адрес в памяти 18 на ЭСППЗУ равен нулю, или когда память 18 на ЭСППЗУ установлена в исходное состояние, или счетчик адреса установлен на нуль. Сигнал CPUB генерируется при подаче питания на защищенную память 10.

Выходной сигнал счетчика адреса подается на идентификатор слова управления, который используется для формирования сигналов слова управления для индикации достижения конкретных адресов в памяти 18 на ЭСППЗУ. Идентификатор слова управления также генерирует сигнал для первого бита, второго бита и восьмого (последнего) бита каждого слова в памяти 18 на ЭСППЗУ. Как будет более подробно описано ниже, сигналы, генерируемые идентификатором слова управления, используются логикой защиты для идентификации того, к какой области памяти 18 на ЭСППЗУ получен доступ, а также того, какой из битов - первый, второй или последний - слова адресован.

Затем осуществляется побитовое сравнение запрограммированного кода защиты с кодом защиты, представленным на выводе I/O (ввода/вывода), по мере того как тактовый сигнал обуславливает приращение адреса запрограммированного кода защиты. Сравнение осуществляется схемой 70 сравнения битов, показанной на фиг.6. В схеме 70 сравнения битов данные, считанные из памяти 18 на ЭСППЗУ по биту в каждый данный момент времени считывающим усилителем в линию SAOUT, сравниваются логической схемой 72 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ с кодом защиты, введенным в линию I/O, тактируемую посредством D-триггера 74. При осуществлении операции СРАВНЕНИЕ счетчик адреса получает приращение по спадающему фронту тактового сигнала, и входные данные фиксируются по нарастающему фронту тактового сигнала. Сравнение осуществляется по следующему спадающему фронту тактового сигнала.

Сравнение выполняется в момент тактирования D-триггера 82. При осуществлении сравнения сигнал CMPBIT должен оставаться на высоком логическом уровне для сравнения, чтобы иметь возможность индикации совпадения. Для того чтобы сигнал CMPBIT находился на высоком логическом уровне, оба входных сигнала логической схемы 80 И-НЕ должны оставаться на высоком логическом уровне. Если один из входных сигналов перейдет на низкий логический уровень, то сигнал CMPBIT будет оставаться на низком логическом уровне. Поскольку один из входов логической схемы 80 И-НЕ соединен с выходом логической схемы 78 ИЛИ, выходной сигнал логической схемы 78 ИЛИ должен удерживаться на высоком логическом уровне, чтобы сигнал CMPBIT сохранял высокий логический уровень. Входными сигналами логической схемы 78 ИЛИ являются выходной сигнал результата сравнения с логической схемы 72 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и сигнал SC WORD, подаваемый через инвертор 76. Если счетчик адреса находится в пределах области, содержащей код защиты, то сигнал SC WORD находится на высоком логическом уровне, и в результате выходной сигнал логической схемы 78 ИЛИ может не переводиться на высокий логический уровень сигналом SC WORD, пока счетчик адреса находится в пределах области кода защиты. Напротив, когда сравниваемые биты совпадают, выходной сигнал логической схемы 72 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ находится на высоком логическом уровне для обеспечения выходного сигнала высокого логического уровня с логической схемы 78 ИЛИ, так что сигнал CMPBIT остается на высоком логическом уровне. Если в процессе сравнения выходной сигнал логической схемы ИЛИ 78 переходит на низкий логический уровень, то сигнал CMPBIT перейдет на низкий логический уровень и останется на этом уровне. Следует отметить, что если в процессе сравнения будет выключено питание, то операция СРАВНЕНИЕ будет завершена, так как D-триггер сбрасывается сигналом CPUB. Сигнал FLGRST будет устанавливать D-триггер 82 в исходное состояние, обеспечивая возможность проведения другой операции СРАВНЕНИЕ.

После того как установлено совпадение запрограммированного кода защиты с введенным кодом защиты, должна выполняться операция проверки правильности. В процессе выполнения операции проверки правильности счетчик попыток ввода кода защиты получает приращения, и операция СЧИТЫВАНИЕ выполняется до тех пор, пока в счетчике попыток ввода кода защиты не будет найдена логическая "1". В процессе операции СЧИТЫВАНИЕ счетчик адреса получает приращения. При этом, когда счетчик адреса получает приращение, на выводе I/O (ввода/вывода) первый бит появляется после спадающего фронта тактового сигнала. Следует иметь в виду, что то обстоятельство, что счетчик попыток ввода кода защиты имеет все логические "1", указывает, что не имелось безуспешных попыток ввода кода защиты с момента установки на нуль счетчика попыток ввода кода защиты. По адресу, при котором найдены все логические "1", выполняется операция ЗАПИСЬ для установки логического "0" по данному адресу.

Схема 90 проверки правильности записи нуля показана на фиг.7. Входными сигналами для схемы 90 проверки правильности записи нуля являются CPUB, CLK, PGM, SAOUT. Сигнал CPUB подается через инвертор 92 на вход логической схемы 94 И и на вход очистки "С" D-триггера 100. Сигнал CLK подается на вход первой логической схемы 96 И-НЕ, второй логической схемы 98 И-НЕ, на тактовый вход D-триггера 100 и на вход третьей логической схемы 102 И-НЕ. Сигнал PGM подается на тактовый вход D-триггера 104 и через инвертор 106 на вход данных D-триггера 100 и на вход третьей логической схемы 102 И-НЕ. Выход данных D-триггера 100 также соединен с входом третьей логической схемы 102 И-НЕ. Выход третьей логической схемы 102 И-НЕ соединен с входом логической схемы 94 И. Сигнал SAOUT подается на вход данных D-триггера 104. Второй вход первой логической схемы 96 И-НЕ соединен с выходом данных D-триггера 104 через инвертор 108. Выход первой логической схемы 96 И-НЕ соединен с одним из входов логической схемы 110 И, в то время как другой вход логической схемы 110 И соединен с выходом логической схемы 94 И. Вход логической схемы 94 И также соединен с запускаемым отрицательным фронтом входом очистки "С" D-триггера 112 и с входом логической схемы 98 И-НЕ. Выход данных D-триггера 104 также соединен с логической схемой 98 И-НЕ, а инверсный выход D-триггера 104 соединен с тактовым входом D-триггера 112. Вход Vss соединен с входом данных D-триггера 112 через инвертор 114, а на выходе данных D-триггера 112 образуется выходной сигнал схемы 90 проверки правильности записи нуля после прохождения через инверторы 116 и 118.

Операция проверки правильности описана ниже со ссылками на фиг.7. Если после операции СРАВНЕНИЕ со счетчика попыток ввода кода защиты считана логическая "1", как описано выше, сигнал SAOUT будет представлять собой логическую "1". Когда сигнал PGM переходит на высокий логический уровень для запуска операции ЗАПИСЬ "0" по адресу в счетчике попыток ввода кода защиты, с которого была считана логическая "1", логическая "1" должна фиксироваться на Q-выходе D-триггера 104. В этот момент выходной сигнал WR0VEN находится на низком логическом уровне. Если операция ЗАПИСЬ "0" реализована, то сигнал SAOUT будет фиксироваться по следующему нарастающему фронту сигнала PGM.

Затем выполняется операция СТИРАНИЕ для счетчика попыток ввода кода защиты. Это приведет к фиксации логической "1" на выходе D-триггера 112 по нарастающему фронту тактового сигнала на входе D-триггера 112. Следует иметь в виду, что когда выполняется операция ЗАПИСЬ, изменяется только один бит, а когда выполняется операция СТИРАНИЕ, изменяется весь байт. Затем выполняется операция СЧИТЫВАНИЕ для индикации того, что флаг кода защиты был установлен, так как разрешается стирание счетчика попыток ввода кода защиты. Операция СЧИТЫВАНИЕ логической "1" указывает, что флаг кода защиты был установлен, поскольку произошло стирание счетчика попыток ввода кода защиты. Операция СЧИТЫВАНИЕ логического "0" указывает, что флаг кода защиты не был установлен, поскольку не произошло стирания счетчика попыток ввода кода защиты. D-триггер 100, логическая схема 102 И-НЕ и логическая схема 94 И обеспечивают то, что сигнал WR0VEN будет принудительно переведен на логический "0" при сбросе питания или при приращении адреса.

После успешного осуществления операции СРАВНЕНИЕ и выполнения операции ЗАПИСЬ будет устанавливаться флаг кода защиты с помощью схемы 120 флага защиты, показанной на фиг.8. Входными сигналами схемы 120 флага защиты являются ENABLE, CPUB, WR0VEN, ACWORD и CMPBIT, а ее выходным сигналом является сигнал SV. Сигнал ENABLE подается через инвертор 122 на вход логической схемы 124 ИЛИ-НЕ, а также на вход логической схемы 126 И-НЕ. На два других входа логической схемы 126 И-НЕ подаются сигналы ACWORD и CMPBIT. Сигнал CPUB подается на другой вход логической схемы 124 ИЛИ-НЕ, а выход логической схемы 124 ИЛИ-НЕ соединен с запускаемым отрицательным фронтом входом очистки "С" D-триггера 128. Сигнал WR0VEN подается на тактовый вход D-триггера 128. Вход данных D-триггера 128 соединен с выходом логической схемы 130 И-НЕ, первый вход которой соединен с выходом логической схемы 126 И-НЕ, а второй вход соединен с выходом данных D-триггера 128 через инвертор 132.

При условии, что входной сигнал CMPBIT логической схемы 126 И-НЕ продолжает оставаться на высоком логическом уровне после сравнения кодов, когда сигнал WR0VEN нарастает, D-триггер 128 будет фиксировать выходной сигнал SV на высоком логическом уровне (при условии, что сигналы ENABLE и ACWORD также находятся на высоком логическом уровне). Сигнал SV будет сохранять высокий логический уровень, пока питание подано на защищенную память 10 и сигнал ENABLE имеет высокий логический уровень, поскольку логическая "1" в сигнале SV подается через инвертор на логическую схему 130 И-НЕ для ввода логического "0" в логическую схему 130 И-НЕ. Входной сигнал D-триггера 128 будет сохранять высокий логический уровень вследствие такой обратной связи.

Как только флаг кода защиты установлен, эмитент защищенной памяти 10 получает доступ для персонализации зон приложений для конечного пользователя. После персонализации желательных областей защищенной памяти 10, к которой эмитент имеет доступ, значение для предохранительной перемычки в секции 28 записывается на логический "0". В таблице на фиг.9 приведены условия доступа для персонализации защищенной памяти 10 перед установкой логического "0" для предохранительной перемычки. Для персонализации защищенной памяти 10 эмитент записывает или стирает требуемые данные в защищенной памяти 10, как это обеспечено условиями доступа. В таблице на фиг.9 код SV представляет флаг кода защиты, который установлен на логическую "1", код Rn является флагом считывания для зон приложений, где n=1, 2, 3 или 4 соответственно четырем зонам приложений, а символ "X" обозначает безразличное состояние.

В качестве первого примера, в области для счетчика попыток ввода кода защиты (SCAC), если сигнал SV=0, т.е. флаг кода защиты не установлен, то разрешается только доступ для считывания и записи, а если сигнал SV=1, т.е. установлен флаг кода, то разрешен доступ для записи и стирания. В качестве второго примера, в области для первой зоны хранения (SMZ1), если сигнал SV=0 и R1= 0, то доступ не разрешен, если сигнал SV=0 и R1=1, то разрешен доступ для считывания, и если сигнал SV=1, то разрешен доступ для считывания, записи и стирания. В предпочтительном варианте осуществления флаг Rn установлен значением во втором бите в каждой из четырех зон хранения. Флаг Rn будет оставаться установленным до тех пор, пока от защищенной памяти не будет отключено питание, даже если второй бит в конкретной зоне хранения последующей операцией может быть записан как логический "0".

На фиг. 10 представлена схема 140 установки флага Р и R, которая устанавливает флаг Rn. Схема 140 установки флага Р и R также устанавливает флаг Рn, как описано ниже. Схема 140 установки флага Р и R имеет следующие входные сигналы: CPUB, CLKB, BIT0, SAOUT, WORD, BIT1. Сигнал CPUB подается на вход сброса "R" D-триггеров 142 и 144. Сигнал CLKB подается на тактовый вход D-триггеров 142 и 144. Сигналы SAOUT и WORD подаются на первый и второй входы логических схем 146 и 148 И, и сигналы BIT0 и BIT1 подаются на первые входы логических схем 146 и 148 И соответственно. Выходы логических схем 146 и 148 И соединены с первым входом логических схем 150 и 152 ИЛИ-НЕ соответственно. Выходы логических схем 150 и 152 ИЛИ-НЕ соединены с входами данных D-триггеров 142 и 144 соответственно. Выходные сигналы данных D-триггеров 142 и 144 подаются назад на вторые входы логических схем 150 и 152 ИЛИ-НЕ соответственно и таким образом формируют флаги Рn и Rn.

В процессе работы схемы 140 установки флага Р и R сигналы BIT0, BIT1 и WORD устанавливаются схемой идентификатора слова управления. При установке конкретного флага Rn адрес находится в области памяти, из которой должен считываться флаг Rn, сигнал WORD и сигнал BIT1 этого слова будет иметь высокий логический уровень, и если значение BIT1, считанное из линии SAOUT, также находится на высоком логическом уровне, то устанавливается флаг Rn. Флаг Rn будет сохраняться до тех пор, пока сигналом CPUB не будет отключено питание с защищенной памяти. Это имеет силу, даже если второй бит в конкретной зоне хранения последующей операцией может быть записан как логический "0", тем самым переводя выходной сигнал логической схемы 148 И в состояние логического "0", так как выходной сигнал D-триггера 144, подаваемый назад через логическую схему 152 ИЛИ, будет поддерживать выходной сигнал логической схемы 152 ИЛИ в состоянии логической "1". Операция установки флага Рn аналогична операции установки флага Rn, за исключением того, что вместо сигнала BIT1 используется сигнал BIT0.

Специалистам в данной области техники легко понять из фиг.9, какие флаги должны устанавливаться для считывания, записи, стирания или сравнения данных в областях защищенной памяти 10. Считывание, запись, стирание и сравнение данных в защищенной памяти 10 выполняется путем приложения соответствующей последовательности сигналов к выводам защищенной памяти 10, как поясняется с помощью временных диаграмм на фиг.4А-4D.

Например, для записи в область для кода защиты в первой зоне приложения вначале адрес памяти 18 на ЭСППЗУ устанавливается на нуль путем выполнения операции СБРОС. Специалистам в данной области техники должно быть ясно, что операция СБРОС может быть выполнена путем приложения сигналов к выводам защищенной памяти в порядке, предписываемом временной диаграммой для операции СБРОС, представленной на фиг.4А. Затем выполняется операция СЧИТЫВАНИЕ по тех пор, пока адрес в счетчике адреса не получит приращение до исходного адреса в область для кода защиты в первой зоне приложения. Наконец, операция ЗАПИСЬ выполняется для записи желательных данных по адресу кода защиты в первой зоне приложения. Как указано выше, как только эмитент закончил персонализацию защищенной памяти 10 для конечного пользователя, область для предохранительной перемычки постоянно устанавливается на логический "0" для эмулирования состояния пережигания предохранительной перемычки.

После пережигания предохранительной перемычки доступ к защищенной памяти определяется в соответствии с условиями адреса, представленными в таблице на фиг. 11. В таблице на фиг.11 имеются три дополнительных кода, не представленных в таблице на фиг.9. Этими кодами являются Sn, Pn, и En. Код Sn представляет флаг кода защиты для четырех зон приложения, где n=1, 2, 3 или 4 в соответствии с четырьмя зонами приложений.

Если установлен флаг защиты для конкретной зоны приложения, то код Sn имеет значение логической "1". Для установки флага Sn в конкретной зоне приложения должен быть представлен код защиты, который совпадает с кодом защиты, хранящимся в области для кода защиты конкретной зоны приложения. Операции сравнения и проверки правильности проводятся аналогично тому, как описано выше для кода защиты, найденного в области для кода защиты области в секции 22. Единственная разница состоит в том, что, разумеется, сравнение начинается по адресу области для кода защиты, связанной с выбранной зоной приложения.

Код Pn представляет собой флаг записи для каждой из четырех зон приложений. В предпочтительном варианте осуществления флаг Pn установлен на значение в первом бите в каждой из четырех зон приложений. Флаг Pn, если он установлен на логическую "1", будет сохраняться установленным, пока питание не будет отключено от защищенной памяти, даже если первый бит в конкретной зоне приложения последующей операцией может быть записан на логический "0". Установка флага Pn выполняется как описано со ссылками на фиг.10.

Код En представляет флаг кода стирания для четырех зон приложений. Если флаг кода стирания для конкретной зоны приложения установлен, то код En имеет значение логической "1". Для установки флага En в конкретной зоне приложения должен быть представлен код стирания, который совпадает с кодом стирания, хранящимся в области для ключа стирания конкретной зоны приложения. Операции сравнения и проверки правильности проводятся аналогично тому, как описано выше для кода защиты, найденного в области для кода защиты области в секции 22. Единственная разница состоит в том, что, разумеется, сравнение начинается по адресу области для ключа стирания, связанной с выбранной зоной приложения.

Для того чтобы конечный пользователь получил доступ к различным областям памяти 18 на ЭСППЗУ для считывания, записи, стирания и сравнения, должны быть установлены корректные комбинации флагов SV, Sn, Pn, Rn и En. В качестве примеров ниже описаны требуемые комбинации флагов SV, Sn, Pn, Rn и En, которые должны быть установлены для считывания, записи, стирания и сравнения в одной из зон хранения.

Доступ, обеспечиваемый различными комбинациями флагов в зонах хранения, можно легко понять путем подразделения различных комбинаций флагов на три группы. В первой группе Sn=0, и единственный разрешенный доступ к зоне хранения представляет собой операцию СЧИТЫВАНИЕ, которая может иметь место при Rn=1. Во второй группе SV=1, Sn=1 и Рn=0. Если установлен этот набор флагов, то доступ к зоне хранения зависит от флага En. Если Еn=0, то разрешена только операция СЧИТЫВАНИЕ. В противном случае, если Еn=1, то разрешены операции СЧИТЫВАНИЕ и СТИРАНИЕ. В третьей группе SV=1, Sn=1 и Рn=1. Если установлен этот набор флагов, то доступ к зоне хранения зависит от флага En. Если Еn=0, то разрешены операции СЧИТЫВАНИЕ и ЗАПИСЬ. В противном случае, если Еn=1, то разрешены операции СЧИТЫВАНИЕ, ЗАПИСЬ и СТИРАНИЕ.

Соответственно, должны осуществляться следующие операции. Во-первых, единственным случаем, когда не разрешено СЧИТЫВАНИЕ из зоны хранения, является случай, когда Sn=0 и Rn=0. Во-вторых, единственным случаем, когда разрешена ЗАПИСЬ, является случай, когда SV= 1, Sn= 1 и Рn=1. В-третьих, единственным случаем, когда разрешено СТИРАНИЕ, является случай, когда SV=1, Sn=1 и Еn=1.

Блок-схема комбинаторной логики для генерирования разрешающих сигналов, передаваемых в память 18 на ЭСППЗУ, чтобы выполнить операции СЧИТЫВАНИЕ, ЗАПИСЬ, СТИРАНИЕ данных в памяти 18 на ЭСППЗУ, а также разрешающих сигналов для пережигания предохранительных перемычек для персонализации, как описано выше, представлена на фиг. 12А-12С. Специалисту в данной области техники легко понять из фиг.12А-12С, что флаги должны быть установлены как описано выше, чтобы обеспечить получение желательных выходных разрешающих сигналов согласно фиг. 12А-12С. Например, схема, показанная на фиг.12А, генерирует сигнал разрешения считывания, который имеет высокий логический уровень, когда сигнал PGMERASEFUNC имеет низкий логический уровень, сигнал MEM имеет высокий логический уровень, и флаги для выбранной области доступа также имеют высокий логический уровень. Чтобы не загромождать описание изобретения ненужными подробностями, каждый из этих флагов, которые были описаны выше, здесь дополнительно не описывается.

Схемы по фиг.12В и 12С генерируют сигнал управления записью (WRT CTRL), сигнал управления записью для предохранительной перемычки (FZ WRT CTRL) и сигнал управления очисткой или стиранием (CLR CTRL) соответственно из набора флагов, установленных, как описано выше. Сигналы WRT CTRL, FZ WRT CTRL, CLR CTRL затем подаются в схему управления записью и стиранием, показанную на фиг. 13, генерирующую сигналы WRTEN, CLREN, WRT, используемые памятью 18 на ЭСППЗУ для записи и стирания данных, а также разрешающий сигнал для управления сигналом программирования FZ WRTEN для предохранительных перемычек. Специалистам в данной области техники понятна работа схем, представленных на фиг. 12А-12С, 13, обеспечивающих генерирование разрешающих сигналов для считывания, записи и программирования предохранительной перемычки в соответствии с флагами, описанными выше.

Выше представлены и описаны варианты осуществления и применения настоящего изобретения. Однако специалистам в данной области техники должно быть ясно, что возможны и другие модификации, помимо упомянутых выше, без отклонения от принципов изобретения. Изобретение, следовательно, ограничивается только сущностью, представленной в формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАЩИЩЕННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, ИМЕЮЩЕЕ ЗАЩИТУ ОТ ПЕРЕХВАТА | 1998 |

|

RU2224288C2 |

| УСТРОЙСТВО И СПОСОБ УПРОЩЕННОЙ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ АНАЛОГОВОГО СИГНАЛА | 1998 |

|

RU2204176C2 |

| МАТРИЦА ФЛЭШ-ПАМЯТИ С ВНУТРЕННИМ ОБНОВЛЕНИЕМ | 1999 |

|

RU2224303C2 |

| НОСИТЕЛЬ ЗАПИСИ, ЗАПИСЫВАЮЩЕЕ УСТРОЙСТВО И СИСТЕМА ЗАПИСИ/ВОСПРОИЗВЕДЕНИЯ | 2000 |

|

RU2268505C2 |

| ВОСПРОИЗВОДЯЩЕЕ УСТРОЙСТВО И СПОСОБ ВОСПРОИЗВЕДЕНИЯ | 2000 |

|

RU2253146C2 |

| УСТРОЙСТВО И СПОСОБ РЕДАКТИРОВАНИЯ | 2000 |

|

RU2252448C2 |

| МЕЖДУНАРОДНЫЙ НОСИМЫЙ ИНДЕНТИФИКАТОР ЛИЧНОСТИ (МНИЛ) ЛИТВИНОВА-СОБОЛЕНКО-МЕДВЕДЕВА (ЛСМ) | 2004 |

|

RU2319206C2 |

| УСТРОЙСТВО ОГРАНИЧЕНИЯ ДОСТУПА К СЕКТОРАМ ЖЕСТКОГО ДИСКА | 2007 |

|

RU2359317C2 |

| СИСТЕМА ИНДИВИДУАЛЬНОГО УЧЕТА И СОРТИРОВКИ РАНЕНЫХ | 1994 |

|

RU2105350C1 |

| БЕЗОПАСНОЕ ХРАНЕНИЕ ДАННЫХ С ЗАЩИТОЙ ЦЕЛОСТНОСТИ | 2006 |

|

RU2399087C2 |

Изобретение относится к защищенной памяти, в частности к памяти, обеспечивающей множество уровней защиты для зон приложений. Техническим результатом является защита памяти при многократном ее использовании в том случае, когда она является частью интеллектуальной карточки. Память содержит зону первого уровня защищенности, счетчик попыток ввода кода защиты, множество зон приложений, каждая из которых включает в себя зону хранения, зону защиты приложения, счетчик попыток ввода кода защиты зоны приложения, участок ключа стирания, счетчик попыток ввода ключа стирания. 20 ил.

Защищенная память, содержащая зону первого уровня защищенности, имеющую код доступа, контролирующий доступ к упомянутой защищенной памяти, до пережигания предохранительной перемычки, предусмотренной эмитентом, счетчик попыток ввода кода защиты для предотвращения доступа к упомянутой защищенной памяти, если предварительно определенное число попыток совпадения с упомянутым кодом доступа сделано перед сбросом счетчика попыток ввода кода защиты, множество зон приложений, каждая из которых включает в себя зону хранения, зону защиты приложения, имеющую код доступа к зоне приложения, контролирующий доступ к зоне хранения после пережигания предохранительной перемычки, предусмотренной эмитентом, счетчик попыток ввода кода защиты зоны приложения, предотвращающий доступ к зоне приложения, если предварительно определенное число попыток совпадения с кодом доступа к зоне приложения сделано до сброса счетчика попыток ввода кода защиты зоны приложения, участок ключа стирания, имеющий код ключа стирания, контролирующий доступ стирания к упомянутой зоне хранения после пережигания предохранительной перемычки, предусмотренной эмитентом, и счетчик попыток ввода ключа стирания, предотвращающий доступ стирания к зоне приложения, если предварительно определенное число попыток совпадения с кодом ключа стирания было сделано до сброса счетчика попыток ввода ключа стирания.

| US 4758718 А, 19.07.1988 | |||

| УСТРОЙСТВО ЗАЩИТЫ ПАМЯТИ | 1991 |

|

RU2006923C1 |

| US 5606315 А, 25.02.1997 | |||

| US 5508691 А, 16.04.1996 | |||

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2036547C1 |

Авторы

Даты

2003-10-10—Публикация

1998-09-23—Подача