Изобретение относится к импульсной технике и может быть использовано в вычислительной технике и системах управления.

Известна энергонезависимая ячейка памяти (св.СССР N 845287, кл. Н 03 К 19/16, 1979), содержащая сердечник с прямоугольной петлей гистерезиса (ППГ) и обмоткой, логические элементы, резистор и триггер. Логические элементы выполнены на элементах И-НЕ. Средняя точка обмотки сердечника подключена через резистор к источнику питания. Конец обмотки подключен к выходу первого элемента И-НЕ, начало к выходу второго элемента И-НЕ и к одному из входов третьего элемента И-НЕ, второй вход которого подключен к шине разрешения, а выход к единичному входу триггера, нулевой вход которого подключен к шине сброса, счетный вход к информационной шине. Прямой и инверсный выходы триггера подключены к входам первого и второго элементов И-НЕ соответственно, вторые входы которых подключены к шине перемагничивания.

Недостатком указанной ячейки памяти является сложность схемы, связанная с необходимостью использования элементов И-НЕ с открытым стоком при построении ячейки памяти на основе КМОП интегральных схем, в одном корпусе которых расположены два элемента И-НЕ с открытым стоком вместо четырех обычных элементов И-НЕ (Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. Л: Энергоатомиздат, 1986, с. 81).

Необходимо отметить также отсутствие в схеме ячейки памяти входа установки в "единицу", организация которого требует дополнительного усложнения схемы. Отсутствие указанного входа ограничивает функциональные возможности указанной ячейки памяти.

Для установки ячейки памяти в "единицу" может использоваться счетный вход триггера. Но перед установкой триггера в "единицу" по счетному входу необходимо быть уверенным, что триггер находится в состоянии логического "0", что затрудняет эту операцию. Кроме того, установка триггера в "единицу" по счетному входу возможна только при автономном использовании триггера, когда его счетный вход свободен.

Наиболее близкой к заявляемому объекту по технической сущности является энергонезависимая ячейка памяти, содержащая сердечник с прямоугольной петлей гистерезиса и двумя обмотками, RS-триггер, три логических элемента, резистор, выходную шину и шины опроса, разрешения и установки в "ноль" и "единицу". Конец первой обмотки сердечника подключен к выходу первого логического элемента, один вход которого подключен к выходной шине и прямому выходу RS-триггера. Выход второго логического элемента соединен с одним из входов третьего логического элемента. Другой вход первого логического элемента подключен к шине установки в "единицу". Начало первой обмотки сердечника через резистор соединено с выходом третьего логического элемента, другой вход которого подключен к шине установки в "ноль". Один из входов второго логического элемента соединен с прямым выходом RS-триггера, другой вход с шиной опроса. Шина разрешения соединена с R-входом RS-триггера, S-вход которого подключен к началу второй обмотки сердечника, конец которой соединен с общей шиной. Первый и третий логические элементы выполнены в виде элементов Исключающее ИЛИ, а второй логический элемент в виде элемента ИЛИ-НЕ

В прототипе устранены недостатки аналога.

Недостатком указанной ячейки памяти являются узкие функциональные возможности, связанные с отсутствием возможности постоянного съема информации.

В режиме хранения информации RS-триггер принудительно удерживается в состоянии логического "0". Информация о состоянии энергонезависимой ячейки памяти записана в магнитный сердечник. Для опроса состояния необходимо подать импульсы по двум входным шинам, причем импульс по шине разрешения должен быть подан с задержкой относительной импульса по шине опроса. При этом поступление опросных импульсов во время действия установочных импульсов не допускается.

Цель изобретения расширение функциональных возможностей путем обеспечения возможности постоянного съема информации о состоянии энергонезависимой ячейки памяти.

Поставленная цель достигается тем, что в энергонезависимую ячейку памяти, содержащую RS-триггер, прямой выход которого соединен с выходной шиной, три логических элемента, первые входы первого и третьего из которых подключены к шинам установки в "единицу" и "ноль" соответственно, сердечник с прямоугольной петлей гистерезиса и первой и второй обмотками, концы которых подключены к выходу первого логического элемента и общей шине соответственно, первый резистор и шину питания, введены второй сердечник с прямоугольной петлей гистерезиса и двумя обмотками, второй, третий и четвертый резисторы, второй логический элемент снабжен третьим входом, вторым и третьим выходами и выполнен в виде четырехканального коммутатора, а первый и третий логические элементы выполнены в виде, соответственно, первого и второго двунаправленных ключей, управляющие входы которых являются первыми входами этих логических элементов, причем первый и второй адресные входы четырехканального коммутатора соединены с шинами установки в "единицу" и "ноль" соответственно, информационный вход с информационными входами двунаправленных ключей и с шиной питания, первый выход с началами первых обмоток сердечников, второй выход с S-входом RS-триггера и через первый резистор с началом второй обмотки первого сердечника, третий выход с R-входом RS-триггера и через второй резистор с началом второй обмотки второго сердечника, конец которой соединен с общей шиной, прямой и инверсный выходы RS-триггера через третий и четвертый резисторы соответственно соединены с концами первых обмоток, соответственно первого и второго сердечников, а выход второго двунаправленного ключа соединен с концом первой обмотки второго сердечника.

Указанная совокупность признаков позволяет расширить функциональные возможности энергонезависимой ячейки памяти путем обеспечения возможности постоянного съема информации о состоянии ячейки памяти за счет исключения принудительного удержания RS-триггера в состоянии логического "0" в режиме хранения информации.

Не обнаружены известные технические решения, содержащие отличительные от прототипа существенные признаки. Это позволяет сделать вывод о соответствии заявляемого технического решения критерию "существенные отличия".

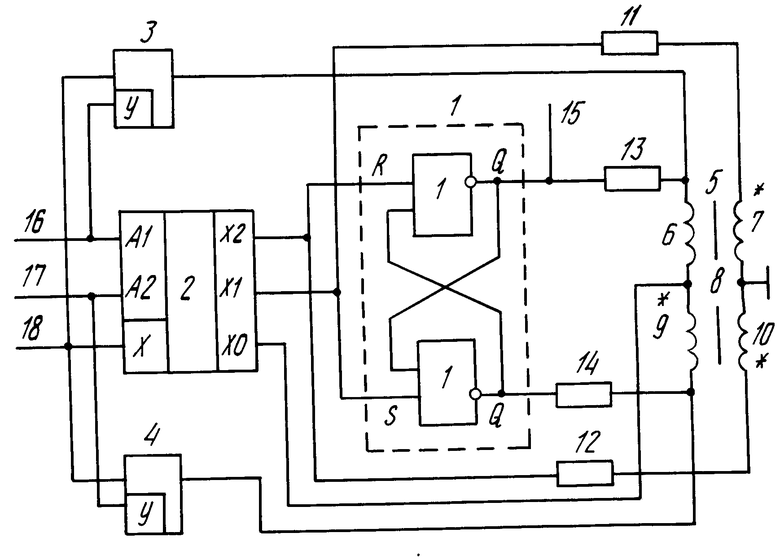

На чертеже приведена схема энергонезависимой ячейки памяти.

Энергонезависимая ячейка памяти содержит RS-триггер 1, четырехканальный коммутатор 2, первый 3 и второй 4 двунаправленные ключи, первый сердечник 5 с первой 6 и второй 7 обмотками, второй сердечник 8 с первой 9 и второй 10 обмотками, первый 11, второй 12, третий 13 и четвертый 14 резисторы, выходную шину 15, шины 16 и 17 установки в "единицу" и "ноль" соответственно, шину 18 питания.

Шина 16 установки в "единицу" соединена с первым адресным входом коммутатора 2 и с управляющим входом двунаправленного ключа 3. Шина 17 установки в "ноль" соединена с вторым адресным входом коммутатора 2 и с управляющим входом двунаправленного ключа 4. Информационные входы коммутатора 2 и двунаправленных ключей 3 и 4 соединены с шиной 18 питания. Первый выход коммутатора 2 соединен с началами обмоток 6 и 9 сердечников 5 и 8 соответственно, концы которых соединены с выходами двунаправленных ключей 3 и 4 соответственно и через резисторы 13 и 14 с прямым и инверсным выходами RS-триггера 1, прямой выход которого соединен с выходной шиной 15. Второй выход коммутатора 2 соединен с S-входом RS-триггера 1 и через резистор 11 с началом обмотки 7 сердечника 5, конец которой соединен с общей шиной. Третий выход коммутатора 2 соединен с R-входом RS-триггера 1 и через резистор 12 с началом обмотки 10 сердечника 8, конец которой соединен с общей шиной.

RS-триггер 1 построен на элементах ИЛИ-НЕ микросхемы 564ЛЕ5 по известной схеме (Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. Л. Энергоатомиздат, Л. 1986, с. 163, рис. 10.1). Четырехканальный коммутатор 2 выполнен на микросхеме 564КП1. Двунаправленные ключи 3, 4 выполнены на микросхеме 564КТ3. В качестве сердечников 5, 8 использованы сердечники ленточные кольцевые М2,5-3/2,5-45 де 4.804.004ТУ, число витков первых обмоток 6 и 9-100, число витков вторых обмоток 7 и 10-200. В качестве резисторов 11, 12 использованы резисторы С2-33Н-0,125-100 кОм ± 5% в качестве резисторов 13, 14 резисторы С2-33Н-0,125-1 кОм ± 5%

Элементы 1-4 могут быть выполнены на КМОП микросхемах других серий, например серий К561, 1526. В качестве сердечников 5, 8 могут быть использованы сердечники зМч-3/2,5-60 де4.804.005ТУ, в качестве резисторов 11-14 резисторы типа С2-23 и др.

Энергонезависимая ячейка памяти работает следующим образом.

В исходном состоянии на шинах 16, 17 присутствует уровень логического "0". Напряжение питания с шины 18 через коммутатор 2 поступает на начало первых обмоток 6 и 9 сердечников 5 и 8 соответственно. Двунаправленные ключи 3 и 4 разомкнуты.

Допустим, что RS-триггер 1 и сердечник 5 находятся в состоянии логического "0", сердечник 8 в состоянии логической "1". За состояние логического "0" сердечников 5, 8 принимается состояние, в которое перемагничивается сердечник током, втекающим в первую обмотку со стороны начала.

Поэтому через обмотку 6 протекает ток, ограничиваемый резистором 13, подтверждающий состояние логического "0" сердечника 5. Ток в обмотке 9 сердечника 8 отсутствует. На выходной шине 15, а также на входах R и S RS-триггера 1 присутствует уровень логического "0".

При поступлении импульса положительной полярности на шину 16 установки в "единицу" напряжение питания с шины 18 поступает на второй выход коммутатора 2 и далее на S-вход RS-триггера 1, устанавливая RS-триггер 1 в состояние логической "1". Одновременно открывается двунаправленный ключ 3 и напряжение питания с шины 18 поступает на конец обмотки 6.

Через последовательно включенные обмотки 6 и 9 начинает протекать ток, ограничиваемый резистором 14, перемагничивающий сердечник 5 в состояние логической "1", а сердечник 8 в состояние логического "0". На обмотке 7 формируется импульс отрицательной полярности, вызывающий протекание тока через резистор 11 и диод схемы защиты S-входа RS-триггера 1 (Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. Л. Энергоатомиздат, 1986, с. 65, рис.6-4), но не влияющий на состояние RS-триггера 1.

На обмотке 10 формируется импульс положительной полярности, поступающий через резистор 12 на R-вход RS-триггера 1, устанавливающий уровень логического "0" на прямом выходе RS-триггера 1 и вызывающий протекание тока через резисторы 13.

После перемагничивания сердечников 5 и 8 импульсы на обмотках 7 и 10 заканчиваются, RS-триггер 1 остается в состоянии логической "1". Импульс положительной полярности на шине 16 заканчивается. Двунаправленный ключ 3 размыкается. Напряжение питания с шины 18 поступает на первый выход коммутатора 2. Через обмотку 9 протекает ток, ограничиваемый резистором 14, подтверждающий состояние логического "0" сердечника 8. На выходной шине 18 присутствует уровень логической "1".

Переключение энергонезависимой ячейки памяти в состояние логического "0" производится аналогичным образом с задействованием двунаправленного ключа 4 при поступлении импульса положительной полярности на шину 17.

При поступлении на шину 16 установки в "единицу" помехи, длительность которой не превышает времени перемагничивания сердечников 5 и 8, процессы в энергонезависимой ячейке памяти во время ее действия аналогичны описанным выше. После окончания помехи двухнаправленный ключ 3 размыкается, напряжение питания с шины 18 поступает на начала обмоток 6 и 9, на прямом и инверсном выходах RS-триггера 1 присутствует уровень логического "0". Оба сердечника 5 и 8 перемагничиваются в состояние логического "0". На обмотках 7 и 10 формируются импульсы положительной полярности, поддерживающие RS-триггер 1 в указанном состоянии. Состояние, в которое установится RS-триггер 1, зависит от длительности помехи. Если длительность помехи меньше половины времени перемагничивания сердечников 5 и 8, то импульс положительной полярности на обмотке 7 закончится раньше, чем на обмотке 9, и RS-триггер 1 возвратится в исходное состояние логического "0". Если длительность помехи больше половины времени перемагничивания сердечников 5 и 8, то произойдет переключение RS-триггера 1 в состояние логической "1".

Аналогичным образом протекают процессы при поступлении помехи на шину 17 установки в "ноль", а также при переключении RS-триггера 1 под действием помех по питанию.

Таким образом, описание работы подтверждает нормальное функционирование энергонезависимой ячейки памяти при поступлении импульсов установки в "единицу" и в "ноль" на соответствующие шины.

При этом на выходной шине 15 постоянно присутствует логический уровень, соответствующий состоянию энергонезависимой ячейки памяти, что расширяет функциональные возможности путем обеспечения возможности постоянного вывода информации на внешние устройства без использования буферных регистров памяти и упрощает вывод информации.

В прототипе RS-триггер в режиме хранения информации принудительно удерживается в состоянии логического "0". Информация о состоянии энергонезависимой ячейки памяти записана в магнитном сердечнике. Для вывода указанной информации необходимо подать импульсы по двум входным шинам, причем импульс по шине разрешения должен быть подан с задержкой относительно импульса по шине опроса. При этом поступление опросных импульсов по время действия установочных импульсов не допускается. Необходимо отметить, что в режиме опроса состояния помехоустойчивость ячейки памяти сохраняется только для состояния логической "1". В состоянии логического "0" RS-триггер может сбиваться внешними помехами.

В институте изготовлен лабораторный макет энергонезависимой ячейки памяти, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта. Время перемагничивания сердечников при напряжении питания 10 В составило 12-13 мкс, допустимая длительность помехи по входу около 6 мкс.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 2002 |

|

RU2230427C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1990 |

|

SU1753919A1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1811353A1 |

| СЧЕТЧИК ИМПУЛЬСОВ, СОХРАНЯЮЩИЙ ИНФОРМАЦИЮ ПРИ ПЕРЕРЫВАХ ПИТАНИЯ | 1991 |

|

RU2047271C1 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1780487A1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2034397C1 |

| ЯЧЕЙКА ПАМЯТИ | 2001 |

|

RU2214037C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

Использование: изобретение относится к импульсной технике и может быть использовано в вычислительтной технике и системах управления. Устройство содержит RS-триггер 1, четырехканальный коммутатор 2, два двунаправленных ключа 3,4, два сердечника 5,8 с прямоугольной петлей гистерезиса, четыре резистора 11 - 14. 1 ил.

ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ, содержащая RS-триггер, прямой выход которого соединен с выходной шиной, три логических элемента, первые входы первого и третьего из которых подключены к шинам установки в "1" и в "0", соответственно, сердечник с прямоугольной петлей гистерезиса и первой и второй обмотками, концы которых подключены к выходу первого логического элемента и общей шине соответственно, первый резистор и шину питания, отличающаяся тем, что, с целью расширения области применения путем обеспечения постоянного съема информации о состоянии энергонезависимой ячейки памяти, в нее введены второй сердечник с прямоугольной петлей гистерезиса и двумя обмотками, второй - четвертый резисторы, второй логический элемент снабжен третьим входом, вторым и третьим выходами и выполнен в виде четырехканального коммутатора, а первый и третий логические элементы в виде соответственно первого и второго двунаправленных ключей, управляющие входы которых являются первыми входами этих логических элементов, причем первый и второй адресные входы четырехканального коммутатора соединены с шинами установки в "1" и в "0" соответственно, информационный вход с информационными входами двунаправленных ключей и шиной питания, первый вход с началами первых обмоток сердечников, второй выход с S-входом RS-триггера и через первый резистор с началом второй обмотки первого сердечника, третий выход с R-входом RS-триггера и через второй резистор с началом второй обмотки второго сердечника, конец которой соединен с общей шиной, прямой и инверсный выходы RS-триггера через третий и четвертый резисторы соответственно соединены с концами первых обмоток соответственно первого и второго сердечников, а выход второго двунаправленного ключа соединен с концом первой обмотки второго сердечника.

| Энергонезависимая ячейка памяти | 1979 |

|

SU845287A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-05-27—Публикация

1991-04-04—Подача