Предпосылки создания изобретения

1. Область техники, к которой относится изобретение

Настоящее изобретение относится к матрицам флэш-памяти. В частности, настоящее изобретение относится к режиму внутреннего обновления матрицы флэш-памяти.

2. Уровень техники

В типичной матрице флэш-памяти ячейки памяти размещены в прямоугольной матрице из строк и столбцов. Участки обычной матрицы 10 флэш-памяти изображены на фиг.1. В матрице 10 флэш-памяти словарные шины 12 и разрядные шины 14 организованы в виде сетки и образуют точки пересечения, в которых расположены ячейки 16 флэш-памяти. Известная ячейка флэш-памяти, которую можно использовать согласно настоящему изобретению, описана в патенте США 4783766, опубликованном 30 мая 1986, права на который принадлежат настоящему заявителю и который упомянут здесь в качестве ссылки.

Каждая словарная шина 12 матрицы 10 флэш-памяти представляет одну из М строк, где каждая строка содержит N слов. Каждая из М строк матрицы 10 флэш-памяти в типичном случае называется страницей памяти. Число разрядных шин 14 в матрице 10 флэш-памяти приблизительно равно числу N слов в строке, умноженному на число бит в каждом слове. Например, в матрице емкостью 4 Мбит с последовательной выборкой 4-Megabit Serial DataFlashТМ, номер изделия AT45DB041, производимой компанией Atmel Corporation, Сан-Хосе, Калифорния, каждая строка известной матрицы 10 флэш-памяти емкостью 4 Мбит содержит 264 слова по 8 бит каждое.

Для каждого элемента флэш-памяти, расположенного в точке пересечения словарной шины 12 и разрядной шины 14, сток элемента 16 флэш-памяти соединен с разрядной шиной 14, к каждому истоку элемента 16 флэш-памяти подведено напряжение питания матрицы при помощи шины 20 питания матрицы, а затвор элемента 16 флэш-памяти соединен со словарной шиной 12. Для каждой словарной шины 12 между схемами доступа к словарным шинам (не показаны) и первым элементом 16 флэш-памяти, расположенным в точке пересечения словарной шины 12 и разрядной шины 14, с последовательным соединением установлен обеспечивающий блокировку/пропускание р-МОП-транзистор 22. С участком каждой словарной шины 12, расположенным между обеспечивающим блокировку/пропускание р-МОП-транзистором 22 и затвором первого элемента 16 флэш-памяти каждой строки, связан генератор 24 накачки словарной шины, который при помощи шины 26 для отрицательной накачки словарной шины соединен с источником отрицательного напряжения, которое во время стирания составляет от приблизительно -15 В до приблизительно -4 В и предпочтительно -10 В.

Операциями, которые могут быть выполнены над ячейками памяти в матрице флэш-памяти, являются ПРОГРАММИРОВАНИЕ (PROGRAM), СТИРАНИЕ (ERASE) и ЧТЕНИЕ (READ). Операция ПРОГРАММИРОВАНИЕ часто выполняется путем подачи на выбранные разрядные шины 14, соединенные с областью стока ячеек 16 флэш-памяти, первого напряжения и подачи на затворы ячеек 16 флэш-памяти, соединенные с выбранными словарными шинами 12 второго, более высокого напряжения с целью осуществления интенсивной инжекции электронов способом, который хорошо известен работающим в данной области техники специалистам обычной квалификации.

Операция СТИРАНИЕ выполняется путем подачи на затвор ячейки 16 флэш-памяти напряжения, которое существенно ниже напряжения, имеющегося на разрядной шине 14. При этом электроны в результате туннельного эффекта мигрируют от плавающего затвора ячейки 16 флэш-памяти способом, который хорошо известен специалистам данной отрасли техники. Для обычной матрицы 10 флэш-памяти известно, что операция СТИРАНИЕ может представлять собой ОБЩЕЕ СТИРАНИЕ (BULK ERASE), когда матрица 10 флэш-памяти стирается полностью, СТИРАНИЕ СЕКТОРА (SECTOR ERASE), когда в матрице 10 флэш-памяти стирается сектор, или СТИРАНИЕ СТРАНИЦЫ (PAGE ERASE), когда стирание может быть выполнено применительно к отдельной строке сектора. Путем ограничения операции СТИРАНИЕ операцией СТИРАНИЕ СЕКТОРА или ОБЩЕЕ СТИРАНИЕ может быть уменьшен эффект появления помех, связанный с возникновением произвольного туннелирования в оставшихся невыбранными строках.

Хотя эффект появления помех при стирании может быть уменьшен путем выбора способа выполнения операции СТИРАНИЕ, при появлении помех, вызванных как операцией стирания, так и операцией программирования, может быть выполнено внешнее обновление ячеек памяти, как это описано в листе технических данных для матрицы 4-Megabit Serial DataFlashТМ, номер изделия AT45DB041. При внешнем обновлении пользователем данных флэш-памяти может быть выполнена команда Auto Page Rewrite (Автоматическая Перезапись Страницы) для обновления строки в матрице флэш-памяти путем считывания в буфер хранящихся в строке данных и последующей записи хранящихся в буфере данных обратно в ту же строку. Команда Auto Page Rewrite, задающая операцию записи в буфер, более подробно описана в заявке на патент США с серийным 08/824175, авторами которой являются Гупта (Gupta) и др., которая подана 26 марта 1997 и озаглавлена "Архитектура флэш-памяти с двумя буферами и несколькими режимами функционирования", права на которую принадлежат настоящему заявителю и которая упомянута здесь в качестве ссылки. Выполнение внешнего обновления с использованием команды Auto Page Rewrite требует от пользователя матрицы флэш-памяти предоставить инструкции для ее выполнения, а также предоставить получивший последовательное приращение страничный адрес для строки, которая должна быть обновлена. Выполнение пользователем матрицы флэш-памяти требования предоставить упомянутые инструкции может иногда оказаться для него обременительным.

Таким образом, задачей настоящего изобретения является внутреннее обновление строк для матрицы флэш-памяти, которое автоматически просматривает строки матрицы флэш-памяти для обновления ячеек памяти в матрице.

Другой задачей настоящего изобретения является внутреннее обновление строк для матрицы флэш-памяти, которое пользователь может программировать для автоматического просмотра строк в матрице с целью обновления одной строки ячеек памяти после каждой N-й операции стирания и программирования, выполняемой для матрицы флэш-памяти.

Сущность изобретения

Согласно настоящему изобретению внутреннее обновление периодически перезаписывает информацию, хранящуюся в каждой из строк ячеек памяти, имеющихся во флэш-памяти. Матрица флэш-памяти включает разрядную шину указателя обновления, которая указывает строку, которая должна быть обновлена. По первому варианту реализации настоящего изобретения внутреннее обновление выполняется автоматически после каждого осуществляемого пользователем цикла стирания/программирования. По второму и третьему вариантам реализации настоящего изобретения пользователь матрицы флэш-памяти сам выбирает, когда выполняется внутреннее обновление, но адрес строки, которая должна быть обновлена, определяется внутри. В каждом из трех вариантов внутреннее обновление включает четыре операции: ПОИСК (SCAN), СТИРАНИЕ ПРИ ОБНОВЛЕНИИ (REFRESH ERASE), ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ (REFRESH PROGRAM) и ПРИРАЩЕНИЕ (INCREMENT).

По первому варианту реализации настоящего изобретения, за относящейся к внутреннему обновлению операцией ПОИСК следует пользовательский цикл стирания/программирования, после которого операция внутреннего обновления продолжается путем выполнения операций СТИРАНИЕ ПРИ ОБНОВЛЕНИИ, ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ и ПРИРАЩЕНИЕ.

По второму варианту реализации настоящего изобретения пользовательский цикл стирания/программирования включает операции ЧТЕНИЕ УКАЗАТЕЛЯ (POINTER READ) и ПРОГРАММИРОВАНИЕ УКАЗАТЕЛЯ (POINTER PROGRAM). Эти операции проверяют, является ли строка, к которой должно быть произведено обращение в пользовательском цикле стирания/программирования, также и следующей строкой, которая должна пройти внутреннее обновление, и, если это так, поддерживают прежним состояние ячейки памяти на разрядной шине указателя обновления после пользовательского цикла стирания/программирования. После выполнения выбранного пользователем матрицы флэш-памяти пользовательского цикла стирания/программирования, с использованием операций ПОИСК, СТИРАНИЕ ПРИ ОБНОВЛЕНИИ, ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ и ПРИРАЩЕНИЕ выполняется внутреннее обновление.

По третьему варианту реализации настоящего изобретения в состав матрицы флэш-памяти включается схема выбора обновления. При включении схемы выбора обновления операции ЧТЕНИЕ УКАЗАТЕЛЯ и ПРОГРАММИРОВАНИЕ УКАЗАТЕЛЯ не выполняются в каждом пользовательском цикле стирания/программирования. После выполнения выбранного пользователем матрицы флэш-памяти пользовательского цикла стирания/программирования, с использованием операций ПОИСК, СТИРАНИЕ ПРИ ОБНОВЛЕНИИ, ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ и ПРИРАЩЕНИЕ выполняется внутреннее обновление.

Краткое описание чертежей

На фиг.1 изображен участок известной матрицы флэш-памяти, которую можно использовать согласно настоящему изобретению.

На фиг. 2 изображена схема декодера разрядных шин для матрицы флэш-памяти, который можно использовать согласно настоящему изобретению.

Фиг. 3А-3С представляют собой принципиальные схемы цепей для генерации сигналов ПОИСК YA (YASCAN) и ПОИСК YB (YBSCAN), используемых схемой декодера разрядных шин, изображенной на фиг.2, согласно настоящему изобретению.

На фиг.4 изображены таблицы I, II и III, указывающие сигналы, используемые соответственно по первому, второму и третьему вариантам реализации настоящего изобретения.

Фиг. 5 представляет собой принципиальную схему цепи выбора обновления, которую можно использовать в матрице флэш-памяти согласно настоящему изобретению.

Фиг.6 представляет собой принципиальную схему цепи прохождения затворов, предназначенной для генерации сигналов ПРОХОД ЗАТВОРА (PASSGATE) и РАЗГРУЗКА (PULLDOWN), используемых схемой выбора обновления, изображенной на фиг.5, согласно третьему варианту реализации настоящего изобретения.

На фиг. 7 изображены таблицы, иллюстрирующие сигналы, используемые согласно третьему варианту реализации настоящего изобретения.

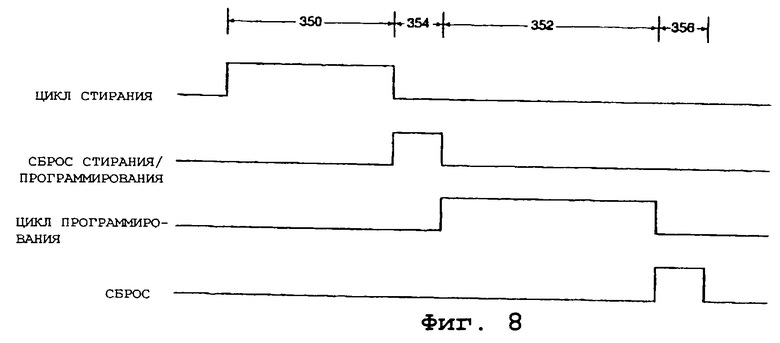

Фиг.8 представляет собой временную диаграмму сигналов, используемых согласно третьему варианту реализации настоящего изобретения.

Подробное описание предпочтительного варианта реализации настоящего изобретения

Специалистам в данной области техники будет понятно, что нижеследующее описание настоящего изобретения является только иллюстративным и ни в коем случае не ограничивает объем изобретения. Для таких специалистов достаточно очевидны и другие варианты реализации настоящего изобретения.

Согласно настоящему изобретению внутреннее обновление периодически перезаписывает информацию, хранящуюся в каждой из строк ячеек памяти, имеющихся во флэш-памяти. Предлагаемое настоящим изобретением обновление называется "внутренним", так как в отличие от существующего уровня техники адрес страницы, которая должна быть перезаписана, не вводится "извне" пользователем матрицы флэш-памяти.

Соответственно, согласно настоящему изобретению, в изображенной на фиг.1 матрице 10 памяти имеется разрядная шина, которая является специальным указателем адреса или обновления. Использование разрядной шины указателя обновления ниже будет описано более подробно. На участке матрицы 10 флэш-памяти, изображенном на фиг.1, разрядная шина указателя обновления обозначена ссылочным номером 18. Понятно, что изображенная на фиг.1 матрица 10 флэш-памяти может представлять собой матрицу флэш-памяти полностью или просто сектор матрицы флэш-памяти, как хорошо представляют себе работающие в данной области специалисты обычной квалификации.

По первому варианту реализации настоящего изобретения периодичность внутреннего обновления такова, что внутреннее обновление выполняется после каждого пользовательского цикла стирания/программирования. По альтернативным второму и третьему вариантам реализации настоящего изобретения периодичность внутреннего обновления устанавливается пользователем матрицы флэш-памяти таким образом, что внутреннее обновление выполняется в ответ на введенную пользователем команду после выбранного пользователем пользовательского цикла стирания/программирования. Для каждого из данных вариантов внутреннее обновление включает четыре операции: ПОИСК, СТИРАНИЕ ПРИ ОБНОВЛЕНИИ, ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ и ПРИРАЩЕНИЕ.

При выполнении операции ПОИСК производится чтение ячеек 16 памяти, расположенных на разрядной шине 18 указателя обновления в каждой строке, до тех пор, пока не будет обнаружено значение "0". Для строки матрицы 10 флэш-памяти, которая в ячейке 16 памяти, расположенной на разрядной шине 18 указателя обновления, имеет значение "0", путем перезаписи будет производиться обновление хранящихся в строке данных. Также, как часть операции ПОИСК, адрес строки, которая должна быть обновлена, сохраняется в регистре поиска. Перед выполнением операций СТИРАНИЕ ПРИ ОБНОВЛЕНИИ и ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ, данные в обновляемой строке записываются в буфер (не показан). Затем строка стирается при помощи операции СТИРАНИЕ ПРИ ОБНОВЛЕНИИ, и хранящиеся в буфере данные записываются обратно в строку при помощи операции ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ. При выполнении операции ПРИРАЩЕНИЕ адрес строки в регистре поиска получает приращение, чтобы указывать адрес следующей строки, которая должна быть обновлена, и в соответствующую ячейку 16, расположенную на разрядной шине 18 указателя обновления, для следующей обновляемой строки операцией ПРОГРАММИРОВАНИЕ (PROGRAM) записывается значение "0".

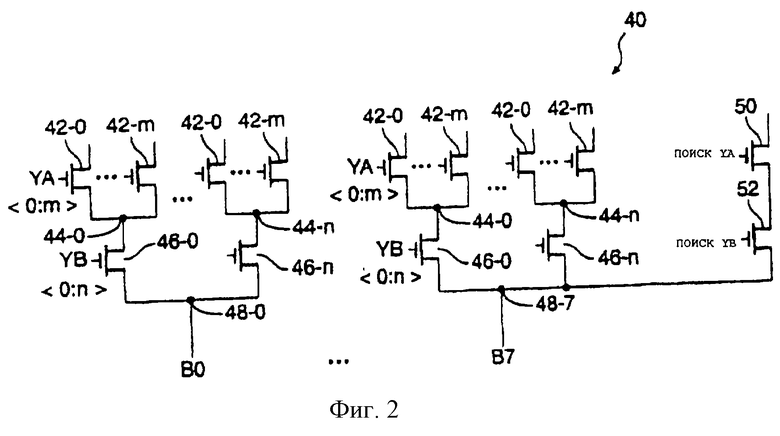

На фиг. 2 изображен приведенный в качестве примера декодер 40 разрядных шин, который декодирует разрядные шины матрицы 10 флэш-памяти, подобной изображенной на фиг.1, и который можно использовать согласно настоящему изобретению. Для специалистов в данной области техники понятно, что без выхода за пределы объема описанного здесь изобретения могут быть использованы и другие варианты реализации декодера 40 разрядных шин. Декодер 40 разрядных шин выбирает слово из выбранной строки в матрице 10 флэш-памяти, для которого нужно выполнить требуемую операцию, такую, например, как ЧТЕНИЕ (READ) или ПРОГРАММИРОВАНИЕ. Для примера, изображенного на фиг.2, ширина выбранного слова составляет восемь бит (В0-В7).

В декодере 40 разрядных шин каждая из изображенных на фиг.1 разрядных шин соединена с первым истоком/стоком отдельного пропускного n-МОП-элемента 42. Пропускные n-МОП-элементы 42 сгруппированы таким образом, что вторые истоки/стоки пропускных n-МОП-элементов 42 из одной и той же группы соединены вместе с образованием общего узла 44. Затворы пропускных n-МОП-транзисторов 42 подключены к сигналам декодирования YA<0:m>.

Каждый общий узел 44 соединен с первым истоком/стоком пропускного n-МОП-транзистора 46. Пропускные n-МОП-транзисторы 46 сгруппированы таким образом, что вторые истоки/стоки пропускных n-МОП-элементов 46 из одной и той же группы соединены вместе с образованием общего узла 48. Пропускные n-МОП-транзисторы 46 объединены по сигналам декодирования YB<0:n>. Общие узлы с 48-0 по 48-7 обеспечивают ввод/вывод слова, над которым выполняется операция в матрице флэш-памяти.

В процессе функционирования матрицы 10 флэш-памяти, когда должна быть выполнена требуемая операция, сигналы YA<0:m> и YB<0:n> выбирают слово в выбранной строке. В процессе выбора один из сигналов YA<0:m> будет иметь логический уровень ВЫСОКИЙ (HIGH), чтобы отпереть один из n-МОП-транзисторов с 42-0 по 42-m в каждой из N групп. Из схемы декодера разрядных шин понятно, что будет иметься восемь наборов из N групп (одна группа для каждого бита в декодируемом слове размером восемь бит). Логический уровень ВЫСОКИЙ одного из сигналов YA<0:n> будет одновременно отпирать один из n-МОП-транзисторов с 46-0 по 46-n, чтобы обеспечить проход через один из n-МОП-транзисторов с 42-0 по 42-m, который был выбран сигналами YA<0:m>.

Изображенная на фиг.1 разрядная шина 18 указателя обновления соединена с первым истоком/стоком пропускного n-МОП-транзистора 50, второй исток/сток которого соединен с первым истоком/стоком пропускного n-МОП-транзистора 52. Второй исток/сток пропускного n-МОП-транзистора 52 соединен с общим узлом 48-7. Затворы пропускных n-МОП-транзисторов 50 и 52 подключены к сигналам ПОИСК YA и ПОИСК YB соответственно, генерируемым в ответ на управляющие сигналы, которые будут описаны ниже. Когда над ячейкой 16 памяти, расположенной в выбранной строке на разрядной шине 18, должна быть выполнена операция, сигналы ПОИСК YA и ПОИСК YB устанавливают на затворах пропускных n-МОП-транзисторов 50 и 52 логический уровень ВЫСОКИЙ, чтобы их отпереть.

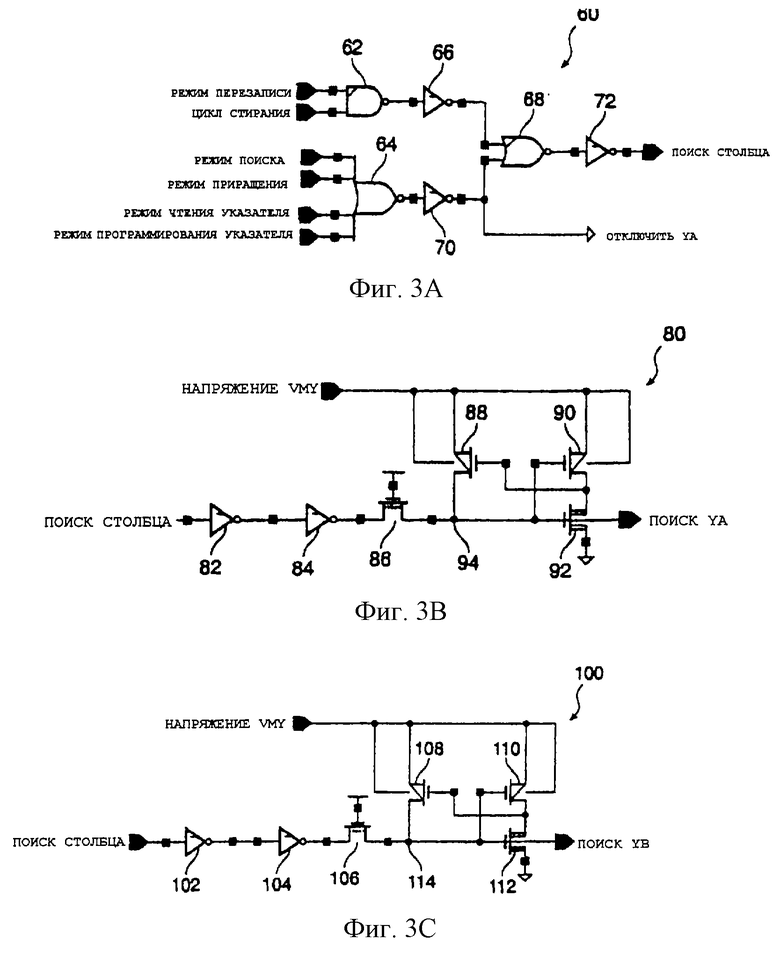

На фиг.3А, 3В и 3С в общем виде изображены соответственно схема 60 ПОИСК СТОЛБЦА, схема 80 ПОИСК YA и схема 100 ПОИСК YB, предназначенные для генерации сигналов ПОИСК СТОЛБЦА (COLUMN SCAN), ПОИСК YA и ПОИСК YB в ответ на управляющие сигналы РЕЖИМ ПЕРЕЗАПИСИ (REWRITE MODE), ЦИКЛ СТИРАНИЯ (ERASE CYCLE), РЕЖИМ ПОИСКА (SCAN MODE), РЕЖИМ ПРИРАЩЕНИЯ (INCREMENT MODE), РЕЖИМ ЧТЕНИЯ УКАЗАТЕЛЯ (POINTER READ MODE) и РЕЖИМ ПРОГРАММИРОВАНИЯ УКАЗАТЕЛЯ (POINTER PROGRAM MODE). В схеме 60 ПОИСК СТОЛБЦА первый вход логического элемента "И НЕ" 62 подключен к управляющему сигналу РЕЖИМ ПЕРЕЗАПИСИ, а его второй вход подключен к управляющему сигналу ЦИКЛ СТИРАНИЯ, далее первый вход логического элемента "ИЛИ НЕ" 64 подключен к управляющему сигналу РЕЖИМ ПОИСКА, второй вход этого элемента подключен к управляющему сигналу РЕЖИМ ПРИРАЩЕНИЯ, третий вход этого элемента подключен к управляющему сигналу РЕЖИМ ЧТЕНИЯ УКАЗАТЕЛЯ и четвертый вход этого элемента подключен к управляющему сигналу РЕЖИМ ПРОГРАММИРОВАНИЯ УКАЗАТЕЛЯ.

Выход логического элемента "И НЕ" 62 через инвертор 66 соединен с первым входом логического элемента "ИЛИ НЕ" 68, а выход логического элемента "ИЛИ НЕ" 64 через инвертор 70 соединен со вторым входом логического элемента "ИЛИ НЕ" 68. На выходе инвертора 70 также формируется сигнал ОТКЛЮЧИТЬ YA (YADISABLE). Выходной сигнал логического элемента "ИЛИ НЕ" 68 подается через инвертор 72 и формирует сигнал ПОИСК СТОЛБЦА. Сигнал ПОИСК СТОЛБЦА поступает как в схему 80 ПОИСК YA, так и в схему 100 ПОИСК YB.

В изображенной на фиг.3В схеме 80 ПОИСК YA сигнал ПОИСК СТОЛБЦА подается через первый и второй инверторы 82 и 84 на сток n-МОП-транзистора 86. Исток n-МОП-транзистора 86 соединен с истоком р-МОП-транзистора 88 затвором р-МОП-транзистора 90 и затвором n-МОП-транзистора 92 с образованием общего узла 94. Затвор n-МОП-транзистора 86 соединен с источником напряжения Vdd (drain voltage - напряжение стока). Источник переменного напряжения VMY соединен с затвором и подложкой (нижним затвором) р-МОП-транзисторов 88 и 90. Затвор р-МОП-транзистора 88 соединен с общим выводом между истоком р-МОП-транзистора 90 и стоком n-МОП-транзистора 92. Исток n-МОП-транзистора 92 соединен с заземлением. Сигнал ПОИСК YA, подведенный к затвору изображенного на фиг.2 n-МОП-транзистора 50, образуется в общем узле 94.

Изображенная на фиг.3С схема 100 ПОИСК YB идентична изображенной на фиг. 3В схеме ПОИСК YA. Соответственно, в схеме 100 ПОИСК YB сигнал ПОИСК СТОЛБЦА подается через первый и второй инверторы 102 и 104 на сток n-МОП-транзистора 106. Исток n-МОП-транзистора 106 соединен с истоком р-МОП-транзистора 108, затвором р-МОП-транзистора 110 и затвором n-МОП-транзистора 112 с образованием общего узла 114. Затвор n-МОП-транзистора 106 соединен с источником напряжения Vdd. Источник переменного напряжения VMY соединен с затвором и подложкой (нижним затвором) р-МОП-транзисторов 108 и 110. Затвор р-МОП-транзистора 108 соединен с общим выводом между истоком р-МОП-транзистора 110 и стоком n-МОП-транзистора 112. Исток n-МОП-транзистора 112 соединен с заземлением. Сигнал ПОИСК YB, подведенный к затвору изображенного на фиг.2 n-МОП-транзистора 52, образуется в общем узле 114.

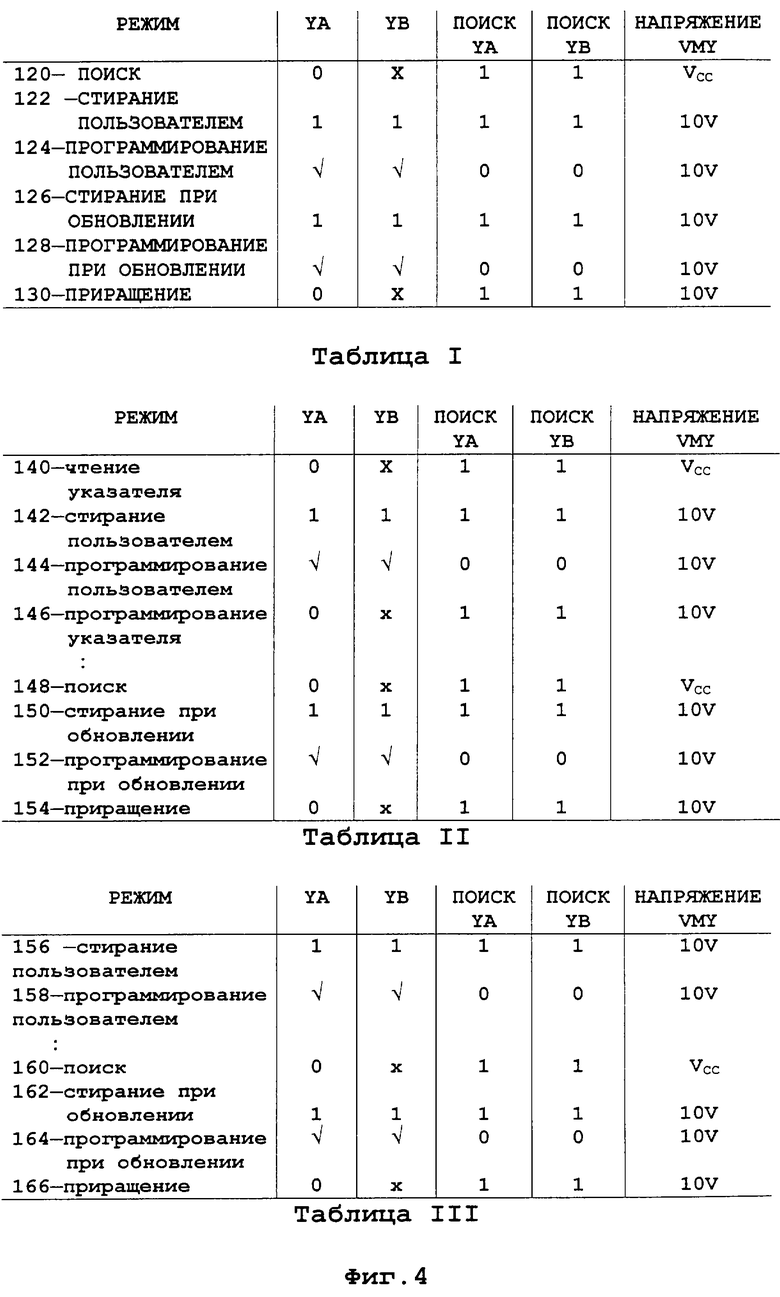

Теперь со ссылкой на изображенную на фиг.4 таблицу I будет описана работа схемы 60 ПОИСК СТОЛБЦА, схемы 80 ПОИСК YA и схемы 100 ПОИСК YB в соответствии с первым вариантом реализации настоящего изобретения. Приведенные в таблице I сигналы ПОИСК YA и ПОИСК YB генерируются в ответ на управляющие сигналы ЦИКЛ СТИРАНИЯ, РЕЖИМ ПОИСКА и РЕЖИМ ПРИРАЩЕНИЯ и подачу уровня VMY переменного напряжения. Управляющие сигналы РЕЖИМ ПЕРЕЗАПИСИ, РЕЖИМ ЧТЕНИЯ УКАЗАТЕЛЯ и РЕЖИМ ПРОГРАММИРОВАНИЯ УКАЗАТЕЛЯ в первом варианте реализации настоящего изобретения не используются и как таковые могут либо отсутствовать, либо управляющий сигнал РЕЖИМ ПЕРЕЗАПИСИ может иметь постоянный уровень ВЫСОКИЙ, а управляющие сигналы РЕЖИМ ЧТЕНИЯ УКАЗАТЕЛЯ и РЕЖИМ ПРОГРАММИРОВАНИЯ УКАЗАТЕЛЯ могут иметь постоянный уровень НИЗКИЙ.

Согласно таблице I, в операции внутреннего обновления, выполняемой согласно первому варианту реализации настоящего изобретения вместе с каждым пользовательским циклом стирания/программирования, сначала на этапе 120 выполняется операция ПОИСК, которая предшествует выполнению в пользовательском цикле стирания/программирования операций СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ (USER ERASE) и ПРОГРАММИРОВАНИЕ ПОЛЬЗОВАТЕЛЕМ (USER PROGRAM), показанных на этапах 122 и 124. При выполнении операции ПОИСК сигнал РЕЖИМ ПОИСКА с логическим уровнем ВЫСОКИЙ подается на первый вход логического элемента "ИЛИ НЕ" 64. Соответственно, сигнал ПОИСК СТОЛБЦА с логическим уровнем ВЫСОКИЙ подается из схемы 60 ПОИСК СТОЛБЦА как в схему 80 ПОИСК YA, так и в схему 100 ПОИСК YB.

Согласно фиг.3В логический уровень ВЫСОКИЙ сигнала ПОИСК СТОЛБЦА пропускается пропускным n-МОП-транзистором 86, чтобы отпереть n-МОП-транзистор 92. В результате на затвор р-МОП-транзистора 88 подается напряжение заземления, чтобы его отпереть и подать переменное напряжение VMY, которое во время операции ПОИСК равно Vcc (collector voltage - напряжение коллектора), на общий узел 94, чтобы на затвор n-МОП-транзистора 50 поступил сигнал ПОИСК YA, в результате чего данный транзистор отпирается. Работа изображенной на фиг.3С схемы 100 ПОИСК YB по подаче сигнала ПОИСК YB на затвор n-МОП-транзистора 52 с результирующим его отпиранием является аналогичной только что описанной работе схемы 80 ПОИСК YA.

Во время операции ПОИСК логический уровень ВЫСОКИЙ сигнала РЕЖИМ ПОИСКА также приводит к появлению сигнала ОТКЛЮЧИТЬ YA с логическим уровнем ВЫСОКИЙ. Когда сигнал ОТКЛЮЧИТЬ YA имеет уровень ВЫСОКИЙ, на затворы n-МОП-транзисторов с 42-0 по 42-m, изображенных на фиг.2, подается сигнал с логическим уровнем НИЗКИЙ, чтобы предотвратить чтение любой другой ячейки 16 памяти, расположенной в матрице 10 флэш-памяти. Сигнал, подающийся на затворы n-МОП-транзисторов 46, не имеет значения. Как только из ячейки 16 памяти, расположенной в столбце 18 указателя обновления, считано значение "0", адрес строки, в которой расположена ячейка 16, сохраняется в регистре поиска. Регистр поиска, который можно использовать для сохранения адреса строки, находится в пределах уровня знаний работающих в данной области специалистов обычной квалификации и не будет здесь рассмотрен, чтобы чрезмерно не усложнять описание и, таким образом, не затруднять понимание настоящего изобретения.

На этапах 122 и 124 для выбранной пользователем строки выполняются, соответственно, операции СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ и ПРОГРАММИРОВАНИЕ ПОЛЬЗОВАТЕЛЕМ. Для этого на этапе 122 сигнал РЕЖИМ ПОИСКА переводится на уровень НИЗКИЙ, а сигнал ЦИКЛ СТИРАНИЯ переводится на уровень ВЫСОКИЙ. Как упомянуто выше, в описываемом здесь первом варианте реализации настоящего изобретения, сигнал РЕЖИМ ПЕРЕЗАПИСИ не требуется. Как следствие, сигнал ПОИСК СТОЛБЦА имеет уровень ВЫСОКИЙ, и, как и на этапе 120, на общих узлах 94 и 114 схемы 80 ПОИСК YA и схемы 100 ПОИСК YB, соответственно, возникает уровень VMY переменного напряжения. Однако в отличие от этапа 120, уровень VMY переменного напряжения составляет 10 В, а не Vcc, чтобы соответствующим образом отпереть n-МОП-транзисторы 50 и 52 во время операции СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ. Также, во время выполнения операции СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ каждый из n-МОП-транзисторов 42 и 46 отпирается, в результате чего стирается вся выбранная строка.

На этапе 124 сигнал ЦИКЛ СТИРАНИЯ переходит с уровня ВЫСОКИЙ на уровень НИЗКИЙ, а сигналы РЕЖИМ ПОИСКА и РЕЖИМ ПРИРАЩЕНИЯ поддерживаются на уровне НИЗКИЙ. Как упомянуто выше, в описываемом здесь первом варианте реализации настоящего изобретения, управляющие сигналы РЕЖИМ ЧТЕНИЯ УКАЗАТЕЛЯ и РЕЖИМ ПРОГРАММИРОВАНИЯ УКАЗАТЕЛЯ не требуются. В результате на выходах как логического элемента "И НЕ" 62, так и логического элемента "ИЛИ НЕ" 64 существует уровень ВЫСОКИЙ. Эти сигналы уровня ВЫСОКИЙ подаются соответственно через инверторы 66 и 70 на первый и второй входы логического элемента "ИЛИ НЕ" 68. Выходной сигнал ВЫСОКИЙ логического элемента "ИЛИ НЕ" 68 подается через инвертор 72, в результате чего сигнал ПОИСК СТОЛБЦА имеет уровень НИЗКИЙ.

В схеме 80 ПОИСК YA сигнал ПОИСК СТОЛБЦА с уровнем НИЗКИЙ подается через инверторы 82 и 84 и пропускается n-МОП-транзистором 86 в узел 94, где он фиксируется р-МОП-транзисторами 88 и 90 и n-МОП-транзистором 92. Работа схемы 100 ПОИСК YB аналогична только что описанной работе схемы 80 ПОИСК YB. Когда сигналы ПОИСК YA и ПОИСК YB оба имеют уровень НИЗКИЙ, n-МОП-транзисторы 50 и 52 оба запираются. В результате ячейка 16 памяти, расположенная на разрядной шине 18 указателя обновления, содержимое которой было стерто на этапе 122, не может теперь быть запрограммирована. Сигналы YA и YB, которые соответствующим образом декодируют участки строки, которую пользователь хочет запрограммировать в матрицу 10 флэш-памяти, также поступают на этапе 124.

На этапах 126 и 128 продолжается операция внутреннего обновления, которая началась с выполнения операции ПОИСК на этапе 120. Операции СТИРАНИЕ ПРИ ОБНОВЛЕНИИ и ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ, выполняемые на этапах 126 и 128, похожи на операции СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ и ПРОГРАММИРОВАНИЕ ПОЛЬЗОВАТЕЛЕМ этапов 122 и 124, за исключением того, что строка, над которой выполняются эти операции, имеет адрес, сохраненный в регистре поиска во время

выполнения операции ПОИСК этапа 120. Перед выполнением операции СТИРАНИЕ ПРИ ОБНОВЛЕНИИ на этапе 126, строка, которая должна быть обновлена, сначала записывается в буфер. На этапе 126 сигнал ЦИКЛ СТИРАНИЯ переводится на уровень ВЫСОКИЙ. Как описано ранее, в результате этого сигнал ПОИСК СТОЛБЦА перейдет на уровень ВЫСОКИЙ.

При сигнале ПОИСК СТОЛБЦА на уровне ВЫСОКИЙ и переменном напряжении VMY, составляющем 10 В, напряжения на узлах 94 и 114 соответственно схемы 80 ПОИСК YA и схемы 100 ПОИСК YB, формирующих сигналы ПОИСК YA и ПОИСК YB, также составляют 10 В. Кроме того, сигналы декодирования YA и YB отпирают все n-МОП-транзисторы 42 и 46. Так как все транзисторы в изображенном на фиг.2 декодере 40 отперты, строка по выбранному адресу полностью стирается. На этапе 128 сигнал ЦИКЛ СТИРАНИЯ переводится на уровень НИЗКИЙ. В результате данные, хранящиеся в буфере, перезаписываются в выбранную строку таким же образом, как и в операции ПРОГРАММИРОВАНИЕ ПОЛЬЗОВАТЕЛЕМ, которая имела место на этапе 124.

На этапе 130 цикл внутреннего обновления завершается операцией ПРИРАЩЕНИЕ. При выполнении операции ПРИРАЩЕНИЕ адрес строки, хранящийся в регистре поиска, получает приращение, и в ячейку 16 памяти, расположенную на разрядной шине 18 указателя обновления, которая соответствует получившему приращение адресу строки, программируется значение "0". На этапе 130 сигнал РЕЖИМ ПРИРАЩЕНИЯ переводится на уровень ВЫСОКИЙ, в результате чего сигнал ПОИСК СТОЛБЦА также имеет уровень ВЫСОКИЙ. При сигнале ПОИСК СТОЛБЦА на уровне ВЫСОКИЙ и переменном напряжении VMY, составляющем 10 В, соответственно в схеме 80 ПОИСК YA и схеме 100 ПОИСК YB на общих узлах 94 и 114, формирующих сигналы ПОИСК YA и ПОИСК YB и соединенных с n-МОП-транзисторами 50 и 52, устанавливаются напряжения 10 В для выполнения операции программирования. Сигналы YA, подаваемые в изображенную на фиг.2 схему 40 декодирования разрядных шин, все имеют уровень напряжения НИЗКИЙ, в результате чего ни один другой бит в выбранной строке не программируется.

Согласно второму и третьему вариантам реализации настоящего изобретения, пользователь матрицы 10 флэш-памяти может установить периодичность внутреннего обновления таким образом, что внутреннее обновление будет выполняться после пользовательского цикла стирания/программирования по желанию, путем подачи "команды внутреннего обновления" в матрицу 10 флэш-памяти. В отличие от существующего уровня техники, адрес строки, которая должна быть обновлена, не предоставляется пользователем, а отслеживается матрицей 10 флэш-памяти и предоставляется матрицей "изнутри".

По второму варианту реализации настоящего изобретения операции внутреннего обновления ПОИСК, СТИРАНИЕ ПРИ ОБНОВЛЕНИИ, ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ и ПРИРАЩЕНИЕ, выполняются схемой 60 ПОИСК СТОЛБЦА, схемой 80 ПОИСК YA, схемой 100 ПОИСК YB в ответ на управляющие сигналы ЦИКЛ СТИРАНИЯ, РЕЖИМ ПОИСКА, РЕЖИМ ПРИРАЩЕНИЯ, РЕЖИМ ЧТЕНИЯ УКАЗАТЕЛЯ и РЕЖИМ ПРОГРАММИРОВАНИЯ УКАЗАТЕЛЯ. Сигналы YA, YB, ПОИСК YA и ПОИСК YB, а также переменное напряжение VMY, связанные со вторым вариантом реализации настоящего изобретения, приведены в таблице II, изображенной на фиг.4.

В таблице II на этапах 140, 142, 144 и 146 изображен пользовательский цикл стирания/программирования, включающий операции ЧТЕНИЕ УКАЗАТЕЛЯ, СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ, ПРОГРАММИРОВАНИЕ ПОЛЬЗОВАТЕЛЕМ и ПРОГРАММИРОВАНИЕ УКАЗАТЕЛЯ, а на этапах 148, 150, 152 и 154 изображено выполняемое после выбранного пользовательского цикла стирания/программирования внутреннее обновление, включающее операции ПОИСК, СТИРАНИЕ ПРИ ОБНОВЛЕНИИ, ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ и ПРИРАЩЕНИЕ.

По второму варианту реализации настоящего изобретения на этапе 140 во время каждого пользовательского цикла стирания/программирования для ячейки 16 памяти, расположенной на разрядной шине 18 указателя обновления в строке, которая должна быть стерта и запрограммирована, выполняется ЧТЕНИЕ УКАЗАТЕЛЯ. При выполнении операции ЧТЕНИЕ УКАЗАТЕЛЯ на третий вход логического элемента "ИЛИ НЕ" 64 подается сигнал РЕЖИМ ЧТЕНИЯ УКАЗАТЕЛЯ с логическим уровнем ВЫСОКИЙ. Соответственно, из схемы 60 ПОИСК СТОЛБЦА как в схему 80 ПОИСК YA, так и в схему 100 ПОИСК YB подается сигнал ПОИСК СТОЛБЦА с логическим уровнем ВЫСОКИЙ.

Согласно фиг.3В, логический уровень ВЫСОКИЙ сигнала ПОИСК СТОЛБЦА пропускается пропускным n-МОП-транзистором 86, чтобы отпереть n-МОП-транзистор 92. В результате на затвор р-МОП-транзистора 88 подается напряжение заземления, чтобы его отпереть и подать переменное напряжение VMY, которое во время операции ЧТЕНИЕ УКАЗАТЕЛЯ равно Vcc, на общий узел 94, чтобы на затвор n-МОП-транзистора 50 поступил сигнал ПОИСК YA, в результате чего данный транзистор отпирается. Работа изображенной на фиг.3С схемы 100 ПОИСК YB по подаче сигнала ПОИСК YB на затвор n-МОП-транзистора 52 с результирующим его отпиранием является аналогичной только что описанной работе схемы 80 ПОИСК YA.

Во время операции ЧТЕНИЕ УКАЗАТЕЛЯ логический уровень ВЫСОКИЙ сигнала РЕЖИМ ЧТЕНИЯ УКАЗАТЕЛЯ также приводит к возникновению логического уровня ВЫСОКИЙ у сигнала ОТКЛЮЧИТЬ YA. Когда сигнал ОТКЛЮЧИТЬ YA имеет уровень ВЫСОКИЙ, на затворы n-МОП-транзисторов с 42-0 по 42-m, изображенных на фиг.2, подается сигнал с логическим уровнем НИЗКИЙ, чтобы предотвратить чтение любой другой ячейки 16 памяти, расположенной в матрице 10 флэш-памяти. Сигнал, подающийся на затворы n-МОП-транзисторов 46, не имеет значения. Когда содержимое считываемой во время операции ЧТЕНИЕ УКАЗАТЕЛЯ ячейки 16 памяти находится в запрограммированном состоянии, обычно "0", в матрице памяти устанавливается внутренний ФЛАГ ЧТЕНИЯ УКАЗАТЕЛЯ. Установка флагов хорошо известна работающим в данной области специалистам обычной квалификации и не будет описана здесь более подробно.

На этапах 142 и 144, как описано выше для этапов 122 и 124 по первому варианту реализации настоящего изобретения, создаются управляющие сигналы, предназначенные для выполнения операций СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ и ПРОГРАММИРОВАНИЕ ПОЛЬЗОВАТЕЛЕМ, в результате чего требуемая строка стирается и программируется. После завершения этапов 142 и 144, когда ФЛАГ ЧТЕНИЯ УКАЗАТЕЛЯ находится в установленном состоянии, на этапе 146 выполняется операция ПРОГРАММИРОВАНИЕ УКАЗАТЕЛЯ. При выполнении операции ПРОГРАММИРОВАНИЕ УКАЗАТЕЛЯ в ячейку 16 памяти, расположенную на разрядной шине 18 указателя обновления и соответствующую либо только что считанной и запрограммированной пользователем строке, либо строке, полученной в результате выполнения приращения (которая выбирается согласно избранному пользователем строению программы), программируется значение "0".

На этапе 146, в ходе операции ПРОГРАММИРОВАНИЕ УКАЗАТЕЛЯ, на четвертый вход логического элемента "ИЛИ НЕ" 64 подается сигнал РЕЖИМ ПРОГРАММИРОВАНИЯ УКАЗАТЕЛЯ с логическим уровнем ВЫСОКИЙ, и в результате этого сигнал ПОИСК СТОЛБЦА также имеет уровень ВЫСОКИЙ. При сигнале ПОИСК СТОЛБЦА на уровне ВЫСОКИЙ и переменном напряжении VMY, составляющем 10 В, соответственно в схеме 80 ПОИСК YA и схеме 100 ПОИСК YB на общих узлах 94 и 114, формирующих сигналы ПОИСК YA и ПОИСК YB и соединенных с n-МОП-транзисторами 50 и 52, устанавливаются напряжения 10 В для выполнения операции программирования. Сигналы YA, подаваемые в изображенную на фиг.2 схему 40 декодирования разрядных шин, все имеют уровень напряжения НИЗКИЙ, в результате чего ни один другой бит в выбранной строке не программируется.

Этапы внутреннего обновления 148, 150, 152 и 154 по второму варианту реализации настоящего изобретения выполняются таким же образом, что и этапы внутреннего обновления 120, 126, 128 и 130 по первому варианту реализации настоящего изобретения.

По третьему варианту реализации настоящего изобретения операции внутреннего обновления ПОИСК, СТИРАНИЕ ПРИ ОБНОВЛЕНИИ, ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ и ПРИРАЩЕНИЕ, выполняются схемой 60 ПОИСК СТОЛБЦА, схемой 80 ПОИСК YA, схемой 100 ПОИСК YB в ответ на управляющие сигналы РЕЖИМ ПЕРЕЗАПИСИ, ЦИКЛ СТИРАНИЯ, РЕЖИМ ПОИСКА и РЕЖИМ ПРИРАЩЕНИЯ и подачу переменного напряжения VMY. Сигналы YA, YB, ПОИСК YA и ПОИСК YB, а также переменное напряжение VMY, связанные с третьим вариантом реализации настоящего изобретения, приведены в таблице III, изображенной на фиг.4.

В таблице III на этапах 156 и 158 изображен пользовательский цикл стирания/программирования, включающий операции СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ и ПРОГРАММИРОВАНИЕ ПОЛЬЗОВАТЕЛЕМ, а на этапах 160, 162, 164 и 166 изображено выполняемое после выбранного пользовательского цикла стирания/программирования внутреннее обновление, включающее операции ПОИСК, СТИРАНИЕ ПРИ ОБНОВЛЕНИИ, ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ и ПРИРАЩЕНИЕ. Можно видеть, что этап 158 ПРОГРАММИРОВАНИЕ ПОЛЬЗОВАТЕЛЕМ аналогичен этапу 144 ПРОГРАММИРОВАНИЕ ПОЛЬЗОВАТЕЛЕМ, но этап 156 СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ отличается от этапа 142 СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ.

По третьему варианту реализации настоящего изобретения не используются операции ЧТЕНИЕ УКАЗАТЕЛЯ и ПРОГРАММИРОВАНИЕ УКАЗАТЕЛЯ, выполняемые в пользовательском цикле стирания/программирования второго варианта реализации настоящего изобретения, но используется управляющий сигнал РЕЖИМ ПЕРЕЗАПИСИ. При выполнении на этапе 156 операции СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ управляющий сигнал РЕЖИМ ПЕРЕЗАПИСИ, поступающий на первый вход логического элемента "И НЕ" 62, поддерживается на уровне НИЗКИЙ. При сигналах РЕЖИМ ПОИСКА и РЕЖИМ ПРИРАЩЕНИЯ, также имеющих уровень НИЗКИЙ, сигнал ПОИСК СТОЛБЦА тоже имеет уровень НИЗКИЙ. В результате сигналы ПОИСК YA и ПОИСК YB также имеют уровень НИЗКИЙ.

Операции этапов внутреннего обновления 160, 162, 164 и 166 по третьему варианту реализации настоящего изобретения похожи на операции этапов внутреннего обновления 120, 126, 128 и 130 по первому варианту реализации настоящего изобретения за исключением того, что во время выполнения операций СТИРАНИЕ ПРИ ОБНОВЛЕНИИ и ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ создается управляющий сигнал РЕЖИМ ПЕРЕЗАПИСИ.

Понятно, что в каждом из трех вариантов, когда соответственно сигналами YA и YB на затворы n-МОП-транзисторов 42 и 46 подается уровень ВЫСОКИЙ, напряжение на затворах n-МОП-транзисторов 42 и 46 представляет собой переменное напряжение VMY.

По третьему варианту реализации настоящего изобретения структура изображенной на фиг.1 матрицы 10 флэш-памяти модифицируется включением схемы выбора обновления. Схема выбора обновления включается в состав матрицы таким образом, что внутреннее обновление может выполняться после пользовательского цикла стирания/программирования как требуется, без применения в пользовательском цикле стирания/программирования по третьему варианту реализации настоящего изобретения операций ЧТЕНИЕ УКАЗАТЕЛЯ и ПРОГРАММИРОВАНИЕ УКАЗАТЕЛЯ.

На фиг.5 изображена используемая в третьем варианте реализации настоящего изобретения схема 170 выбора обновления. В схеме 170 выбора обновления в каждой из приведенных в качестве примера первой и второй словарных шин 12-1 и 12-2, между ячейками 16 памяти, расположенными на последней разрядной шине 14 матрицы 10 флэш-памяти, и ячейками 16 памяти, расположенными на разрядной шине 18 указателя обновления, находятся пропускной р-МОП-транзистор 172 и разгрузочный р-МОП-транзистор 174. Понятно, что пропускной р-МОП-транзистор 172 и разгрузочный р-МОП-транзистор 174 таким же образом установлены в каждой строке матрицы 10 флэш-памяти.

В каждой строке сток пропускного р-МОП-транзистора 172 соединен со словарной шиной 12, а исток пропускного р-МОП-транзистора 172 соединен с ячейкой 16 памяти, расположенной на разрядной шине 18 указателя обновления. Сигнал ПРОХОД ЗАТВОРА, генерируемый схемой прохождения затворов, которая будет описана ниже, подведен к затвору каждого пропускного р-МОП-транзистора 172. Исток пропускного р-МОП-транзистора 172 также соединен со стоком разгрузочного р-МОП-транзистора 174. Исток разгрузочного р-МОП-транзистора 174 соединен с заземлением, а затвор каждого разгрузочного р-МОП-транзистора 174 подключен к сигналу РАЗГРУЗКА, генерируемому схемой прохождения затворов, которая описана ниже.

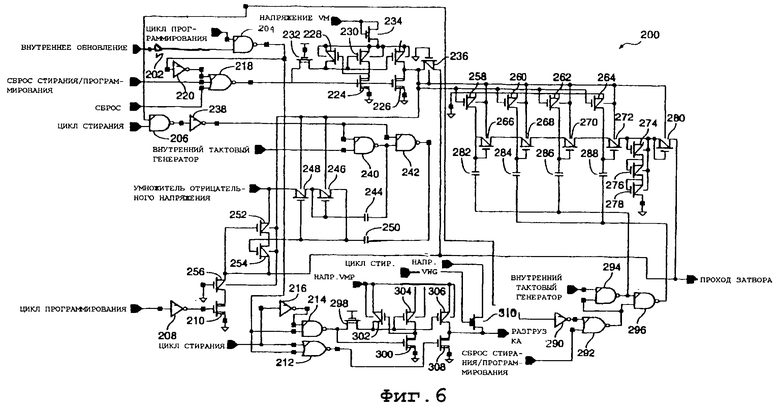

На фиг. 6 изображена схема 200 прохождения затворов, которая генерирует сигналы ПРОХОД ЗАТВОРА и РАЗГРУЗКА в ответ на управляющие сигналы ВНУТРЕННЕЕ ОБНОВЛЕНИЕ (INTERNAL REFRESH), ЦИКЛ ПРОГРАММИРОВАНИЯ (PROGRAM CYCLE), ЦИКЛ СТИРАНИЯ, СБРОС СТИРАНИЯ/ПРОГРАММИРОВАНИЯ (ERASE/PROGRAM RESET) и СБРОС (RESET), а также подачу напряжений смещения VM, VMP, NVM и VWG. В схеме 200 прохождения затворов управляющий сигнал ВНУТРЕННЕЕ ОБНОВЛЕНИЕ подведен через инвертор 202 к первому входу логического элемента "И НЕ" 204, а также к первому входу логического элемента "И НЕ" 206. Второй вход логического элемента "И НЕ" 204 подключен к управляющему сигналу ЦИКЛ ПРОГРАММИРОВАНИЯ, а второй вход логического элемента "И НЕ" 206 подключен к управляющему сигналу ЦИКЛ СТИРАНИЯ. Управляющий сигнал ЦИКЛ ПРОГРАММИРОВАНИЯ также подведен через инвертор 208 к затвору n-МОП-транзистора 210, а управляющий сигнал ЦИКЛ СТИРАНИЯ также подведен к первому входу логического элемента "ИЛИ НЕ" 212 и через инвертор 216 к первому входу логического элемента "И НЕ" 214. Управляющий сигнал СБРОС СТИРАНИЯ/ПРОГРАММИРОВАНИЯ подведен к первому входу логического элемента "ИЛИ НЕ" 218, а управляющий сигнал СБРОС подведен ко второму входу логического элемента "ИЛИ НЕ" 218. Выход логического элемента "И НЕ" 204 соединен через инвертор 220 с третьим входом логического элемента "ИЛИ НЕ" 218, а также со вторым входом логического элемента "ИЛИ НЕ" 212 и вторым входом логического элемента "И НЕ" 214.

Выход логического элемента "ИЛИ НЕ" 218 соединен со стоком пропускного n-МОП-транзистора 222 и затворами n-МОП-транзисторов 224 и 226. Затвор пропускного n-МОП-транзистора 222 соединен с источником напряжения Vdd. Исток пропускного n-МОП-транзистора 222 соединен с истоком р-МОП-транзистора 228, затвором р-МОП-транзистора 230 и затвором р-МОП-транзистора 232. Стоки и подложки (нижние затворы) р-МОП-транзисторов 228, 230 и 232 соединены с истоком n-МОП-транзистора 234 в диодном включении. Затвор и сток n-МОП-транзистора 234 соединены с источником переменного напряжения VM. Затвор р-МОП-транзистора 228 и исток р-МОП-транзистора 230 соединены со стоком n-МОП-транзистора 224. Исток р-МОП-транзистора 232 соединен со стоком n-МОП-транзистора 226. Истоки n-МОП-транзисторов 224 и 226 соединены с заземлением. Общий вывод истока р-МОП-транзистора 232 и стока n-МОП-транзистора 226 соединен со стоком пропускного элемента 236 из р-МОП-транзистора. Затвор р-МОП-транзистора 236 соединен с заземлением.

Выход логического элемента "И НЕ" 206 через инвертор 238 соединен с первым входом логических элементов "И НЕ" 240 и 242. Второй вход логического элемента "И НЕ" 240 подключен к сигналу ВНУТРЕННИЙ ТАКТОВЫЙ ГЕНЕРАТОР (INTERNAL CLOCK OSCILLATOR), выход логического элемента "И НЕ" 240 соединен со вторым входом логического элемента "И НЕ" 242, а через конденсатор 244 - с затвором и стоком р-МОП-транзистора 246 и истоком р-МОП-транзистора 248. Выход логического элемента "И НЕ" 242 соединен через конденсатор 250 с истоком р-МОП-транзистора 246, затвором р-МОП-транзистора 248, истоком р-МОП-транзистора 252, а также затвором и стоком р-МОП-транзистора 254. Напряжение смещения УМНОЖИТЕЛЬ ОТРИЦАТЕЛЬНОГО НАПРЯЖЕНИЯ (NEGATIVE VOLTAGE MULTIPLIER, NVM) подведено к стокам р-МОП-транзисторов 248 и 252.

Сток n-МОП-транзистора 210 соединен с истоком р-МОП-транзистора 256. Исток n-МОП-транзистора 210 и затвор р-МОП-транзистора 256 оба соединены с заземлением. Нижние затворы р-МОП-транзисторов 256, 254, 252, 248, 246 и 236 все соединены с общим выводом истока р-МОП-транзистора 232, стока n-МОП-транзистора 226 и стока пропускного элемента 236 из р-МОП-транзистора. Также с этим общим выводом соединены затворы и нижние затворы р-МОП-транзисторов 258, 260, 262 и 264, а также нижние затворы р-МОП-транзисторов 266, 268, 270, 272, 274, 276, 278 и 280.

Стоки р-МОП-транзисторов 258, 260, 262 и 264 соединены с заземлением, а истоки р-МОП-транзисторов 258, 260, 262 и 264 соединены со стоками и затворами соответственно р-МОП-транзисторов 266, 268, 270 и 272, а также с первой обкладкой соответственно конденсаторов 282, 284, 286 и 288. Истоки р-МОП-транзисторов 260, 262 и 264 также соединены с истоками соответственно р-МОП-транзисторов 266, 268 и 270. Исток р-МОП-транзистора 272 соединен со стоками и затворами р-МОП-транзисторов 274 и 280. Исток р-МОП-транзистора 274 соединен с затвором и стоком р-МОП-транзистора 276, исток р-МОП-транзистора 276 соединен с затвором и стоком р-МОП-транзистора 278, а исток р-МОП-транзистора 278 соединен с заземлением.

Управляющий сигнал ВНУТРЕННЕЕ ОБНОВЛЕНИЕ также подведен через инвертор 290 к первому входу логического элемента "ИЛИ НЕ" 292. Второй вход логического элемента "ИЛИ НЕ" 292 подключен к управляющему сигналу СБРОС СТИРАНИЯ/ПРОГРАММИРОВАНИЯ, а выход логического элемента "ИЛИ НЕ" 292 соединен с первым входом логического элемента "И НЕ" 294 и первым входом логического элемента "И НЕ" 296. Второй вход логического элемента "И НЕ" 294 подключен к сигналу ВНУТРЕННИЙ ТАКТОВЫЙ ГЕНЕРАТОР, а выход логического элемента "И НЕ" 294 соединен со вторым входом логического элемента "И НЕ" 296 и второй обкладкой конденсаторов 282 и 286. Выход логического элемента "И НЕ" 296 соединен со второй обкладкой конденсаторов 284 и 288.

Исток р-МОП-транзистора 236, затвор р-МОП-транзистора 252, исток р-МОП-транзистора 254, сток р-МОП-транзистора 256 и исток р-МОП-транзистора 280 соединены в общий узел, который формирует сигнал ПРОХОД ЗАТВОРА схемы 200 прохождения затворов.

Выход логического элемента "И НЕ" 214 соединен со стоком n-МОП-транзистора 298 и затвором n-МОП-транзистора 300. Исток n-МОП-транзистора 293 соединен с истоком р-МОП-транзистора 302, затвором р-МОП-транзистора 304 и затвором р-МОП-транзистора 306. Источник переменного напряжения VMP соединен со стоком и подложкой (нижним затвором) р-МОП-транзисторов 302, 304 и 306. Затвор р-МОП-транзистора 302, исток р-МОП-транзистора 304 и сток n-МОП-транзистора 300 образуют общий вывод. Исток n-МОП-транзистора 300 соединен с заземлением.

Выход логического элемента "ИЛИ НЕ" 212 соединен с затвором n-МОП-транзистора 308. Исток n-МОП-транзистора 308 соединен с заземлением, а сток n-МОП-транзистора 308 соединен с истоком р-МОП-транзистора 306. Затвор n-МОП-транзистора 310 подключен к управляющему сигналу ЦИКЛ СТИРАНИЯ, а сток n-МОП-транзистора 310 соединен с переменным напряжением смещения VWG. Общий вывод, образуемый стоком n-МОП-транзистора 308, истоком n-МОП-транзистора 310 и истоком р-МОП-транзистора 306, формирует сигнал РАЗГРУЗКА схемы 200 прохождения затворов.

В изображенной на фиг.7 таблице IV приведены напряжения сигналов ПРОХОД ЗАТВОРА и РАЗГРУЗКА для различных режимов, соответствующих настоящему изобретению, а в таблице V приведены напряжения источников напряжения VM, VMP, VWG и NVM для различных режимов, соответствующих настоящему изобретению.

Что касается изображенной на фиг.7 схемы 200 прохождения затворов, при функционировании по третьему варианту реализации настоящего изобретения, когда выполняется операция внутреннего обновления, как показано на приведенных в таблице III (фиг.4) этапах 160, 162, 164 и 166 с операциями ПОИСК, СТИРАНИЕ ПРИ ОБНОВЛЕНИИ, ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ и ПРИРАЩЕНИЕ, управляющий сигнал ВНУТРЕННЕЕ ОБНОВЛЕНИЕ, поданный в схему 200 прохождения затворов, будет иметь уровень ВЫСОКИЙ, а когда выполняются операции пользовательского цикла "СТИРАНИЕ и ПРОГРАММИРОВАНИЕ", как показано на приведенных в таблице III (фиг.4) этапах 156 и 158 с операциями СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ и ПРОГРАММИРОВАНИЕ ПОЛЬЗОВАТЕЛЕМ, управляющий сигнал ВНУТРЕННЕЕ ОБНОВЛЕНИЕ, поданный в схему 200 прохождения затворов, будет иметь уровень НИЗКИЙ.

Во время операции ПОИСК управляющие сигналы ЦИКЛ СТИРАНИЯ и ЦИКЛ ПРОГРАММИРОВАНИЯ оба будут находиться на логическом уровне НИЗКИЙ. В результате сигнал ПРОХОД ЗАТВОРА, подаваемый на затворы изображенных на фиг.5 пропускных р-МОП-транзисторов 172, будет иметь значение -2 В, а сигнал РАЗГРУЗКА, подаваемый на затворы изображенных на фиг.5 разгрузочных р-МОП-транзисторов 174, будет иметь значение приблизительно 5 В (напряжение VMP).

Во время операции СТИРАНИЕ ПРИ ОБНОВЛЕНИИ управляющий сигнал ЦИКЛ СТИРАНИЯ будет иметь уровень ВЫСОКИЙ, а управляющий сигнал ЦИКЛ ПРОГРАММИРОВАНИЯ будет находиться на уровне НИЗКИЙ, как показано ссылочным номером 350 на фиг.8. В результате сигнал ПРОХОД ЗАТВОРА, подаваемый на затворы изображенных на фиг.5 пропускных р-МОП-транзисторов 172, будет иметь значение приблизительно -10 В, а сигнал РАЗГРУЗКА, подаваемый на затворы изображенных на фиг.5 разгрузочных р-МОП-транзисторов 174, будет иметь значение приблизительно 1,5 В (напряжение VWG).

Во время операции ПРОГРАММИРОВАНИЕ ПРИ ОБНОВЛЕНИИ управляющий сигнал ЦИКЛ СТИРАНИЯ будет иметь уровень НИЗКИЙ, а управляющий сигнал ЦИКЛ ПРОГРАММИРОВАНИЯ будет иметь уровень ВЫСОКИЙ, как показано ссылочным номером 352 на фиг. 8. Управляющий сигнал СБРОС СТИРАНИЯ/ПРОГРАММИРОВАНИЯ также в течение короткого импульса будет иметь уровень ВЫСОКИЙ, как показано ссылочным номером 354. В результате сигнал ПРОХОД ЗАТВОРА, подаваемый на затворы изображенных на фиг.5 пропускных р-МОП-транзисторов 172, будет иметь значение -2 В, а сигнал РАЗГРУЗКА, подаваемый на затворы изображенных на фиг.5 разгрузочных р-МОП-транзисторов 174, будет иметь значение приблизительно 10 В (напряжение VMP).

Во время операции ПРИРАЩЕНИЕ управляющий сигнал ЦИКЛ СТИРАНИЯ будет иметь уровень НИЗКИЙ, а управляющий сигнал ЦИКЛ ПРОГРАММИРОВАНИЯ будет иметь уровень ВЫСОКИЙ. В результате сигнал ПРОХОД ЗАТВОРА, подаваемый на затворы изображенных на фиг.5 пропускных р-МОП-транзисторов 172, будет иметь значение -2 В, а сигнал РАЗГРУЗКА, подаваемый на затворы изображенных на фиг.5 разгрузочных р-МОП-транзисторов 174, будет иметь значение приблизительно 10 В (напряжение VMP). В конце операции ПРИРАЩЕНИЕ управляющий сигнал СБРОС в течение короткого импульса будет иметь уровень ВЫСОКИЙ, как показано ссылочным номером 356, чтобы перевести в исходное состояние схему 200 прохождения затворов.

Во время операции СТИРАНИЕ ПОЛЬЗОВАТЕЛЕМ с управляющим сигналом ВНУТРЕННЕЕ ОБНОВЛЕНИЕ на уровне ВЫСОКИЙ, управляющий сигнал ЦИКЛ СТИРАНИЯ будет иметь уровень ВЫСОКИЙ, а управляющий сигнал ЦИКЛ ПРОГРАММИРОВАНИЯ будет находиться на уровне НИЗКИЙ, как показано ссылочным номером 350 на фиг.8. В результате сигнал ПРОХОД ЗАТВОРА, подаваемый на затворы изображенных на фиг. 5 пропускных р-МОП-транзисторов 172, будет иметь значение менее 1 В, а сигнал РАЗГРУЗКА, подаваемый на затворы изображенных на фиг.5 разгрузочных р-МОП-транзисторов 174, будет иметь значение приблизительно 1,5 В (напряжение VWG).

Во время операции ПРОГРАММИРОВАНИЕ ПОЛЬЗОВАТЕЛЕМ с управляющим сигналом ВНУТРЕННЕЕ ОБНОВЛЕНИЕ на уровне НИЗКИЙ, управляющий сигнал ЦИКЛ СТИРАНИЯ будет иметь уровень НИЗКИЙ, а управляющий сигнал ЦИКЛ ПРОГРАММИРОВАНИЯ будет иметь уровень ВЫСОКИЙ, как показано ссылочным номером 352 на фиг.8. Управляющий сигнал СБРОС СТИРАНИЯ/ПРОГРАММИРОВАНИЯ также в течение короткого импульса будет иметь уровень ВЫСОКИЙ, как показано ссылочным номером 354. В результате сигнал ПРОХОД ЗАТВОРА, подаваемый на затворы изображенных на фиг. 5 пропускных р-МОП-транзисторов 172, будет иметь значение приблизительно 10 В, а сигнал РАЗГРУЗКА, подаваемый на затворы изображенных на фиг.5 разгрузочных р-МОП-транзисторов 174, будет иметь значение приблизительно 0 В.

Хотя здесь приведены и рассмотрены некоторые варианты реализации и применения данного изобретения, для специалистов в данной области техники должно быть очевидно, что без выхода за пределы указанных здесь новаторских концепций может быть осуществлено гораздо большее, чем упомянутые выше и приведенное в качестве примера. Таким образом, данное изобретение ограничивается только пунктами приложенной формулы изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЖИМ СТИРАНИЯ СТРАНИЦЫ В МАТРИЦЕ ФЛЭШ-ПАМЯТИ | 1999 |

|

RU2222058C2 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО НЕРАЗРУШАЕМОЙ ПАМЯТИ | 1992 |

|

RU2097842C1 |

| СХЕМА УПРАВЛЕНИЯ ДЛЯ ЭНЕРГОНЕЗАВИСИМОГО ПОЛУПРОВОДНИКОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1998 |

|

RU2221286C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1999 |

|

RU2249262C2 |

| Логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2643650C1 |

| Многослойная логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2682548C2 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| САМОПРОГРАММИРУЮЩИЙСЯ ГЕНЕРАТОР НАПРЯЖЕНИЯ В ЭНЕРГОНЕЗАВИСИМОМ ПОЛУПРОВОДНИКОВОМ ЗУ, ЭНЕРГОНЕЗАВИСИМОЕ ПОЛУПРОВОДНИКОВОЕ ЗУ И СПОСОБ САМОПРОГРАММИРУЮЩЕЙСЯ ГЕНЕРАЦИИ НАПРЯЖЕНИЯ В НЕМ | 1995 |

|

RU2146398C1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| ЭЛЕКТРИЧЕСКИ СТИРАЕМАЯ И ПРОГРАММИРУЕМАЯ ЭНЕРГОНЕЗАВИСИМАЯ НАКОПИТЕЛЬНАЯ ЯЧЕЙКА | 1996 |

|

RU2168242C2 |

Изобретение относится к матрице флэш-памяти, в частности к режиму внутреннего обновления матрицы флэш-памяти. Техническим результатом является возможность обновления одной строки ячеек памяти после каждой N-операции стирания и программирования, выполняемой для матрицы флэш-памяти. Способ функционирования матрицы флэш-памяти содержит операции выбора в матрице флэш-памяти строки, которая должна быть обновлена, стирания этой строки, программирования этой строки, создания приращения адреса упомянутой строки, которая должна быть обновлена, в матрице флэш-памяти. Другой вариант способа содержит операции считывания выбранной строки в матрице флэш-памяти и сохранения состояния выбранного бита из упомянутой выбранной строки, стирания этой строки в матрице флэш-памяти, программировании этой строки в матрице флэш-памяти и установки упомянутого выбранного бита в первое состояние, если его состояние, сохраненное на перовой операции, является первым состоянием. 2 с. и 4 з.п. ф-лы, 18 ил.

| US 5365486 А, 15.09.1994 | |||

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 1996 |

|

RU2111556C1 |

| СПОСОБ ПРОГРАММИРОВАНИЯ ЯЧЕЙКИ ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ | 1996 |

|

RU2111555C1 |

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| US 5347486 A, 13.09.1994. | |||

Авторы

Даты

2004-02-20—Публикация

1999-09-14—Подача