Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известен многоканальный таймер (см. авторское свидетельство СССР 1345326 от 07.04.86, МКИ Н 03 К 5/13 "Многоканальный таймер", Г.А. Пыко и Г.Г. Кравцов. Опубликовано 15.10.87. Бюл. 38), содержащий дискретную линию задержки (ДЛЗ), запоминающее устройство (ЗУ), счетчик управления, N JK-триггеров, (N+3) логических элемента И, логический элемент ИЛИ, вход тактовых импульсов, вход старта, шину управления и N выходов, причем вход тактовых импульсов подключен к тактовому входу ДЗЛ и тактовым входам JK-триггеров, выходы которых являются выходами устройства, вход старта соединен с первым входом элемента ИЛИ, выход которого соединен с тактовым входом счетчика управления и со входом управления ДЗЛ, информационный вход которой соединен с выходом ЗУ, а выход соединен с первыми входами элементов И, вторые входы которых соединены с выходами ЗУ, выходы N элементов И соединены с J-входами соответствующих JK-триггеров, К-входы которых соединены с выходом (N+1) элемента И, выход (N+3) элемента И соединен со вторым входом элемента ИЛИ, выход (N+2) элемента И соединен с R-входом счетчика управления, выходы которого соединены с адресными входами ЗУ, управляющий вход которого подключен к шине управления.

Недостатком данного таймера является сложность его реализации в случае, когда необходимо формировать несколько интервалов, лежащих в широком временном диапазоне.

Известно устройство для программного управления (см. авторское свидетельство СССР 1080120 от 16.12.84, МКИ G 05 В 19/08 "Устройство для программного управления", В. А. Сечкин и В.И. Юлдашев. Опубликовано 15.03.84. Бюл. 10), взятое в качестве прототипа, содержащее генератор импульсов, выход которого соединен с входом счетчика импульсов, выходы каждого разряда которого соединены с первыми входами блока сравнения, выход которого подключен к первому входу первого логического элемента И, выход которого соединен с входом блока команд, выходы которого подключены ко второму выходу устройства и к входу блока формирования данных, соединенного первым и вторым выходами с входами соответственно первого и второго задатчиков времени, выходы которых соединены с первыми входами соответственно второго и третьего блоков логических элементов И, соединенных выходами к входам блока логических элементов ИЛИ, выходы которого соединены со вторыми входами блока сравнения, вторые входы второго блока элементов И соединены с инверсным выходом RS-триггера, S-вход которого соединен с выходом блока сравнения, а прямой выход RS-триггера соединен со вторыми входами третьего блока элементов И, с вторым входом первого элемента И и с первым выходом устройства.

Недостатком данного устройства является сложность его реализации в случае, когда необходимо формировать несколько интервалов, лежащих в широком временном диапазоне.

Техническим результатом заявляемого устройства является упрощение схемы при последовательном формировании временных интервалов, длительности которых находятся в широком диапазоне. Это достигается тем, что таймер содержит последовательно соединенные генератор импульсов и счетчик, выходы которого соединены с первыми входами блока сравнения, выход которого соединен с первым входом логического элемента И, выход которого соединен с входом блока формирования команд, выходы которого соединены с входами блока формирования данных и являются выходами устройства. Новым является то, что дополнительно введен логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй логический элемент И, один вход которого инверсный, и второй счетчик, вход которого соединен с выходом второго логического элемента И, прямой вход которого соединен с выходом блока сравнения, вторые входы которого соединены с первыми выходами блока формирования данных, второй выход которого соединен с первым входом логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом второго счетчика, а выход - со вторым входом первого логического элемента и с инверсным входом второго логического элемента.

Указанная совокупность признаков позволяет упростить схему таймера, особенно при последовательном формировании временных интервалов, длительности которых находятся в широком диапазоне. Упрощение схемы достигается за счет сокращения разрядности блока сравнения и блока формирования данных при сохранении диапазона формируемых временных интервалов.

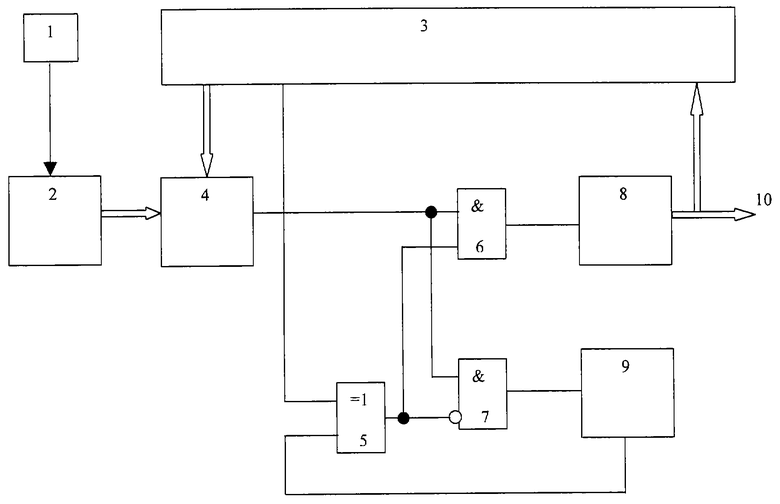

На чертеже приведена структурная схема таймера.

Таймер содержит генератор 1 импульсов, первый счетчик 2 импульсов, блок 3 формирования данных, блок 4 сравнения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, первый 6 и второй 7 элементы И, блок 8 формирования команд, второй счетчик 9 импульсов, выходы 10 устройства.

Выход генератора 1 импульсов соединен с входом первого счетчика 2 импульсов, выходы разрядов которого соединены с первыми входами блока 4 сравнения, вторые входы которого подключены к первым выходам блока 3 формирования данных, второй выход которого соединен с первым входом логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5. Выход блока 4 сравнения соединен с первым входом логического элемента И 6 и с прямым входом логического элемента И 7, инверсный вход которого подключен к выходу логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 и к второму входу логического элемента И 6, выход которого соединен с входом блока 8 формирования команд, выходы которого подключены к входам блока 3 формирования данных и являются выходами 10 устройства. Выход логического элемента И 7 соединен с входом второго счетчика 9 импульсов, выход которого подключен к первому входу логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5.

Рассмотрим работу устройства на примере формирования двух временных интервалов и соответствующих им команд. В исходном положении счетчики 2 и 9 импульсов находятся в нулевом состоянии (цепь обнуления для простоты не показана). Блок 3 формирования данных находится в нулевом адресе, при котором на его первых выходах выставлен код, соответствующий первому временному интервалу, имеющему малую длительность. На втором выходе блока 3 выставлен сигнал логической 1, который поступает на первый вход логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5, на второй вход которого поступает сигнал логического 0 с выхода второго счетчика 9 импульсов. В результате этого на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 устанавливается сигнал логической 1, поступающий на соответствующий вход элемента И 6 и на инверсный вход элемента И 7. Таким образом, разрешается прохождение сигнала через элемент И 6 на вход блока 8 формирования команд и запрещается прохождение сигнала через элемент И 7 на вход второго счетчика 9, предназначенного для формирования второго временного интервала, имеющего большую длительность. Тактовые импульсы, формируемые генератором 1, поступают на вход счетчика 2, который после снятия сигнала обнуления начинает отсчет времени формирования первой команды. При совпадении кодов с выходов разрядов счетчика 2 и с первых выходов блока 3 формирования данных срабатывает блок 4 сравнения, единичный сигнал с выхода которого проходит через элемент И 6 и поступает на вход блока 8 формирования команд, где формируется первая команда, поступающая на выход 10 устройства и на вход блока 3 формирования данных. По срезу импульса первой команды происходит обнуление счетчиков (цепь обнуления для простоты не показана) и переключение блока 3 в следующий адрес. В результате этого на первых выходах блока 3 устанавливается код, соответствующий периоду счетных сигналов, которыми будет заполняться счетчик 9, для чего на втором выходе блока 3 выставляется сигнал логического 0. Под действием этого сигнала на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 устанавливается сигнал логического 0, блокирующий элемент И 6 и разрешающий прохождение сигнала через элемент И 7. После окончания импульса обнуления возобновляется работа счетчика 2. При совпадении кодов на входах блока 4 сравнения происходит вновь его срабатывание, при котором на его выходе устанавливается единичный сигнал, длительность которого равна половине периода следования импульсов на младшем разряде счетчика 2. Указанный сигнал, проходя через элемент И 7, выполняет роль счетного сигнала для счетчика 9 и изменяет его состояние. Поскольку информация на выходах блока 3 не меняется, далее начинается циклический процесс формирования единичных сигналов на выходе блока 4, которые, проходя через элемент И 7, заполняют счетчик 9. Такая работа устройства продолжается до тех пор, пока после очередного импульса счетчик 9 не достигнет переполнения, при котором на его выходе сформируется сигнал логической 1, благодаря которому на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 установится сигнал логической 1, блокирующий элемент И 7 и разрешающий прохождение сигнала через элемент И 6. Очередной сигнал логической 1 с выхода блока 4 через элемент И 6 поступает на вход блока 8, где формируется вторая команда, поступающая на выход 10 устройства и на вход блока 3. По срезу импульса второй команды происходит обнуление счетчиков и переключение блока 3 в следующий адрес, которому соответствует новая информация на его выходах. Далее работа таймера может продолжаться аналогичным образом. Описание работы таймера показывает, что при формировании второго временного интервала, имеющего большую длительность, с помощью блоков 3 и 4 контролируется не сама длительность временного интервала, а период счетных сигналов, с помощью которых он формируется, для чего требуется меньшее количество разрядов блоков 3 и 4. Следует также отметить, что счетчик 9, в соответствии с программой блока 3, может находиться в нулевом состоянии как во время формирования одного короткого интервала, так и нескольких, после чего начать свою работу. Таким образом достигается дополнительное увеличение диапазона формируемых временных интервалов.

В целях подтверждения осуществимости заявляемого объекта и достижения технического результата изготовлен и испытан лабораторный макет таймера, выполненный по приведенной на чертеже схеме. Проведенные испытания показали осуществимость заявляемого таймера и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАЙМЕР | 2001 |

|

RU2199177C1 |

| ПРОГРАММНЫЙ ТАЙМЕР | 2001 |

|

RU2215367C2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207717C2 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2213191C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207718C1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ПАРАМЕТРОВ | 1999 |

|

RU2180450C2 |

| ЭЛЕКТРОННЫЙ КОДОВЫЙ ЗАМОК | 2001 |

|

RU2215107C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КОДОВЫМ ЗАМКОМ | 2001 |

|

RU2191878C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

Изобретение относится к импульсной технике. Технический результат заключается в упрощении схемы при последовательном формировании временных интервалов, длительности которых находятся в широком диапазоне. Таймер содержит генератор импульсов 1, первый и второй счетчики импульсов 2 и 9, блок формирования данных 3, блок сравнения 4, логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, первый и второй логические элементы И 6 и 7, блок формирования команд 8, выходы устройства 10. 1 ил.

Таймер, содержащий последовательно соединенные генератор импульсов и счетчик, выходы которого соединены с первыми входами блока сравнения, выход которого соединен с первым входом логического элемента И, выход которого соединен с входом блока формирования команд, выходы которого соединены с входами блока формирования данных и являются выходами устройства, отличающийся тем, что дополнительно введен логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй логический элемент И, один вход которого - инверсный, и второй счетчик, вход которого соединен с выходом второго логического элемента И, прямой вход которого соединен с выходом блока сравнения, вторые входы которого соединены с первыми выходами блока формирования данных, второй выход которого соединен с первым входом логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом второго счетчика, а выход - со вторым входом первого логического элемента И и с инверсным входом второго логического элемента И.

| Устройство для программного управления | 1982 |

|

SU1080120A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1991 |

|

SU1769611A1 |

| Многоканальный таймер | 1986 |

|

SU1345326A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

2003-09-27—Публикация

2001-12-13—Подача