Изобретение относится к вычислительной технике, может быть использовано для сопряжения двух устройств обработки данных и является усовершенствованием устройства по авт.св. № 1291996;

Цель изобретения - повьшение быстродействия: за счет исключения множег ства команд занесения адреса и совмещения во времени работы микропрограммного автомата с операциями занесения информации в регистр данных.

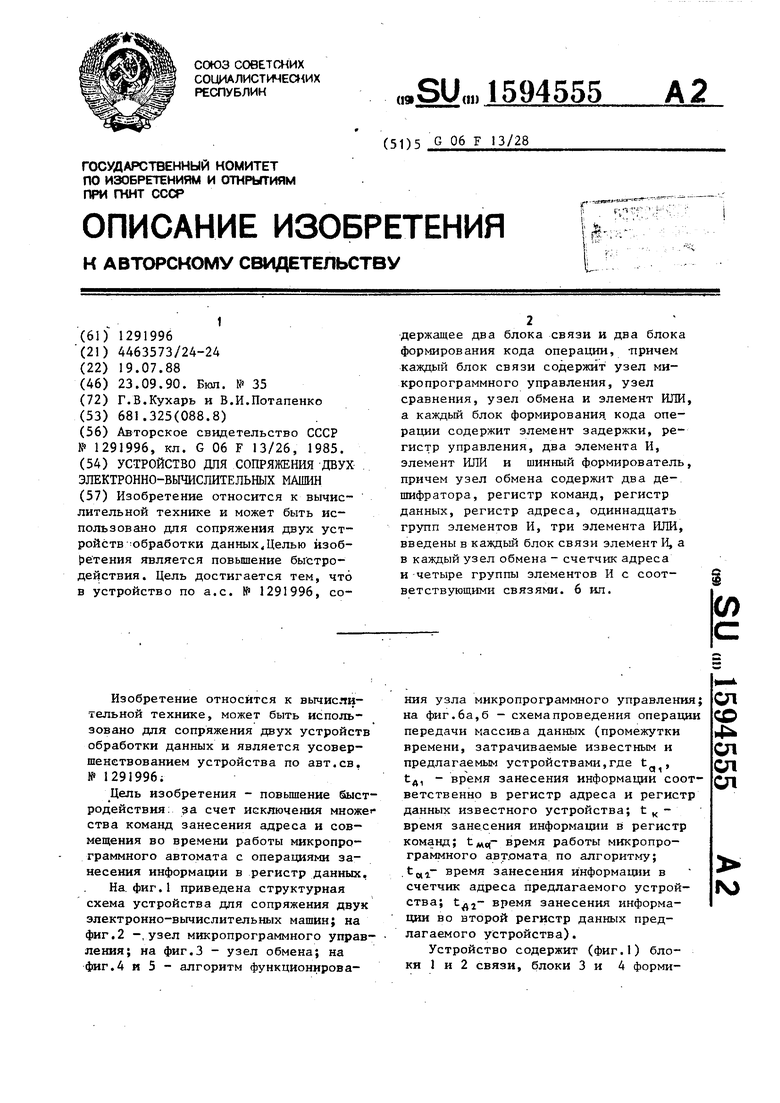

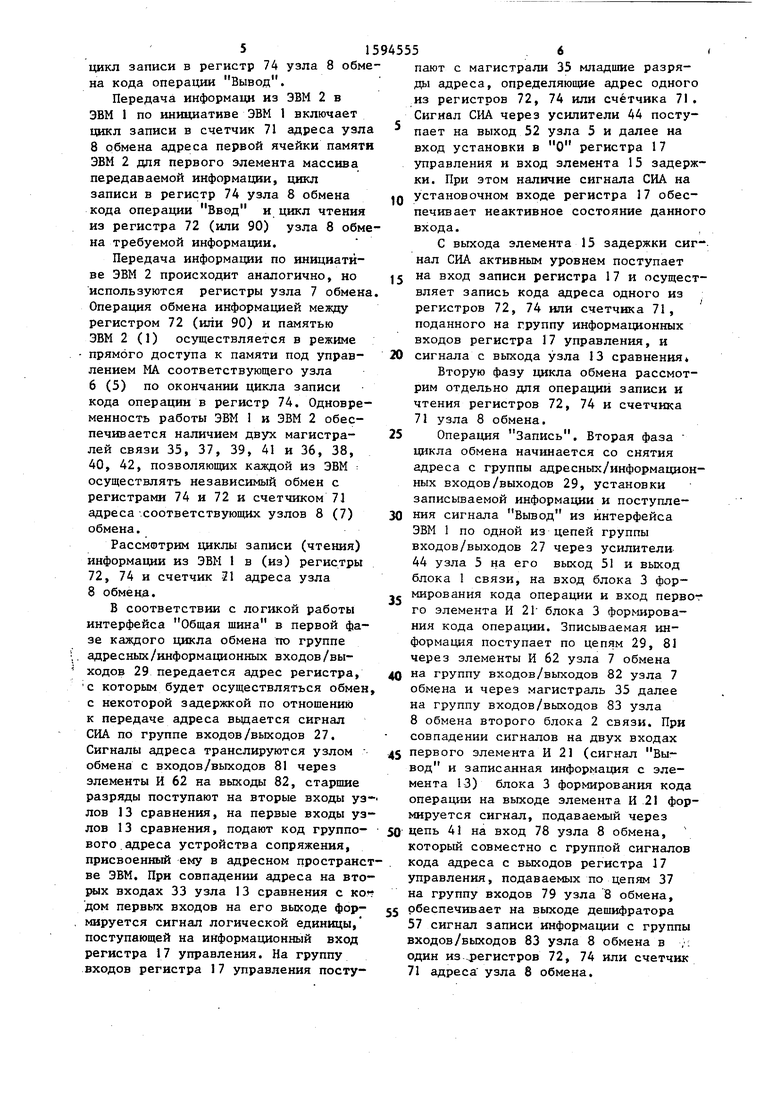

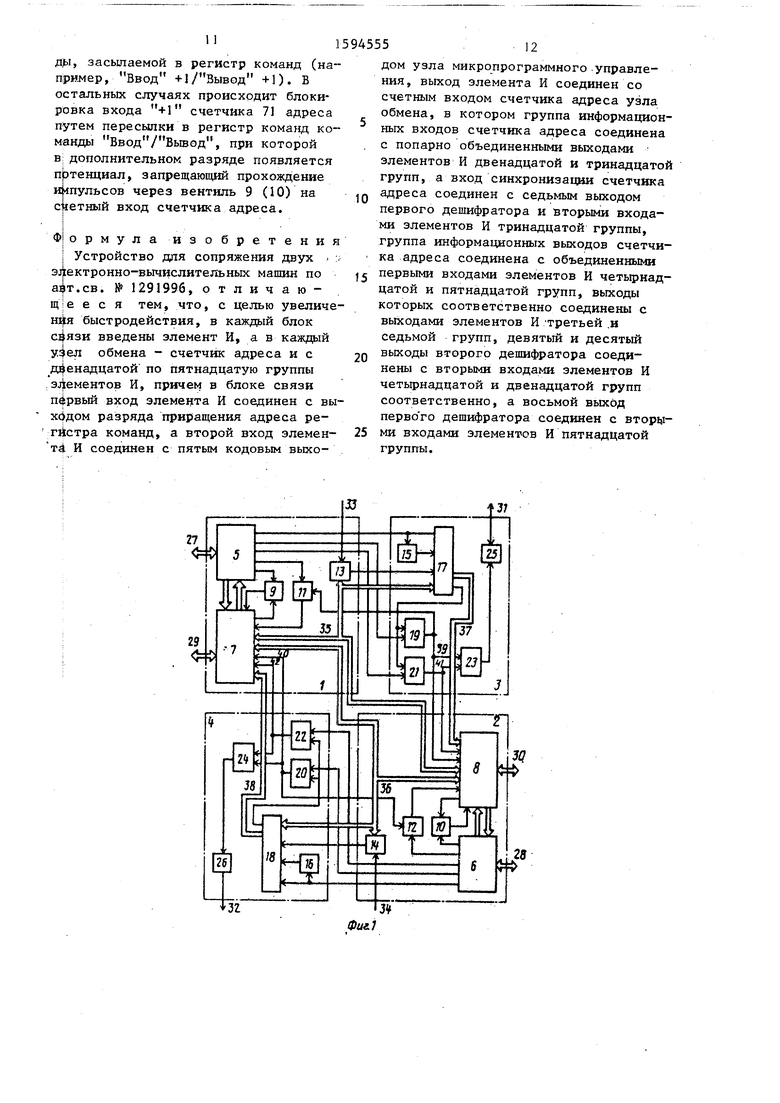

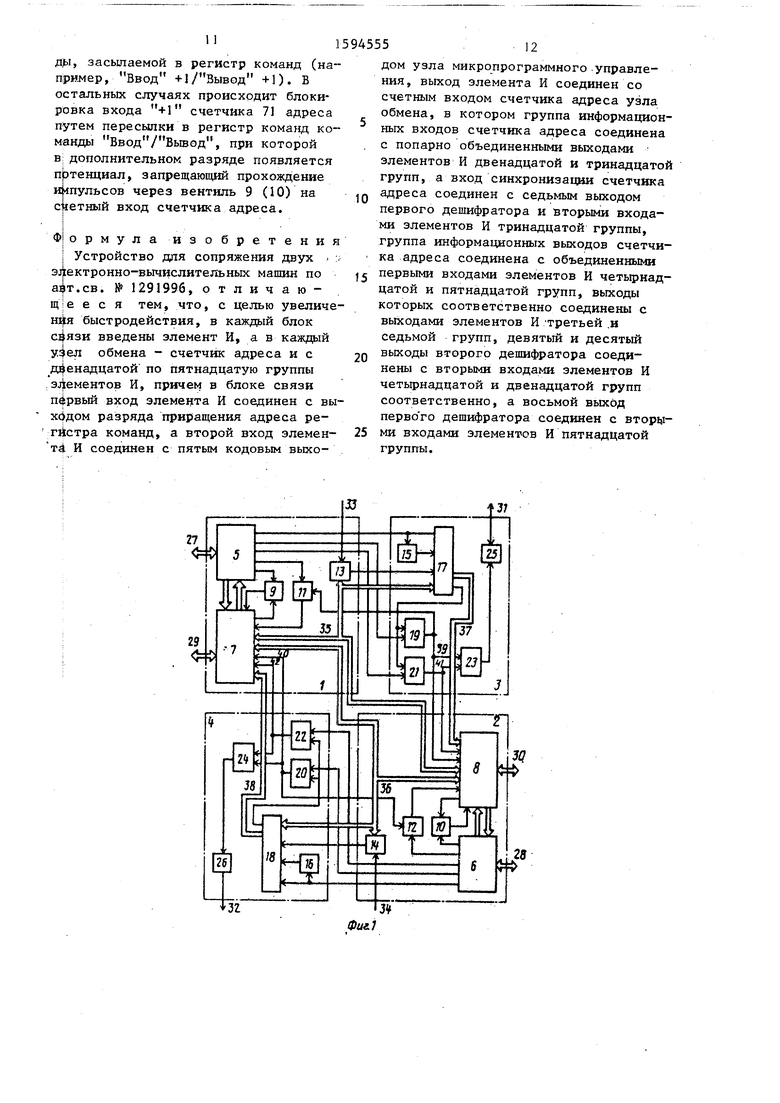

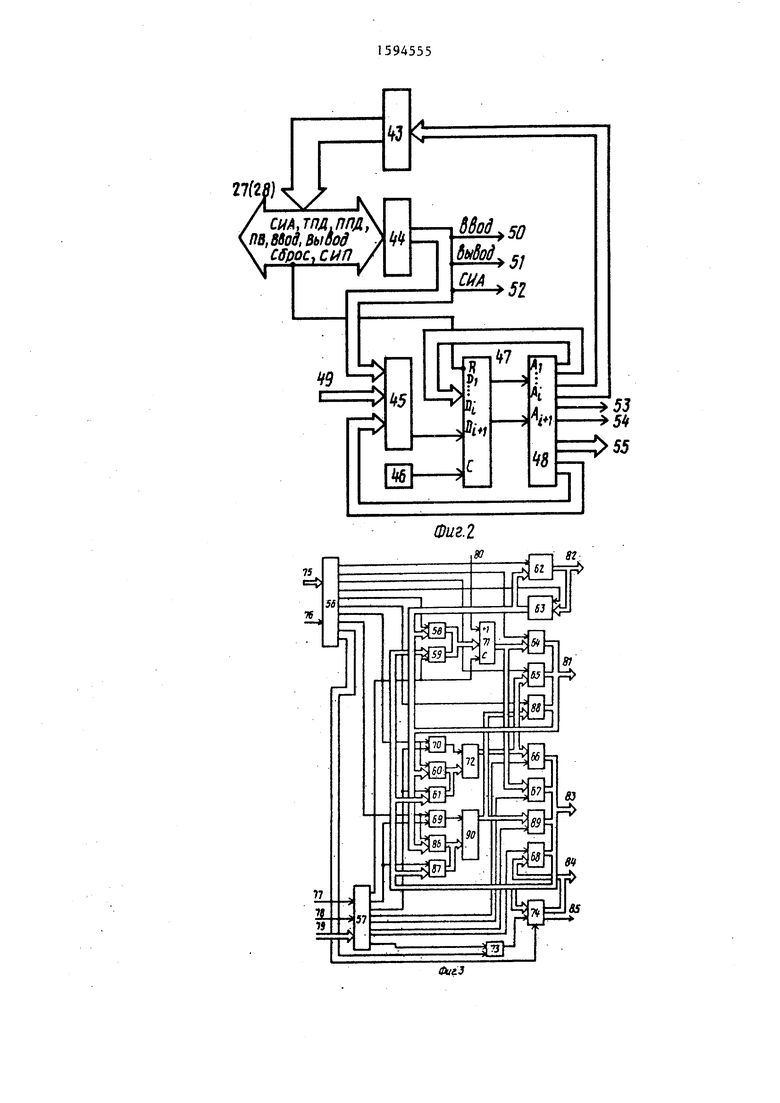

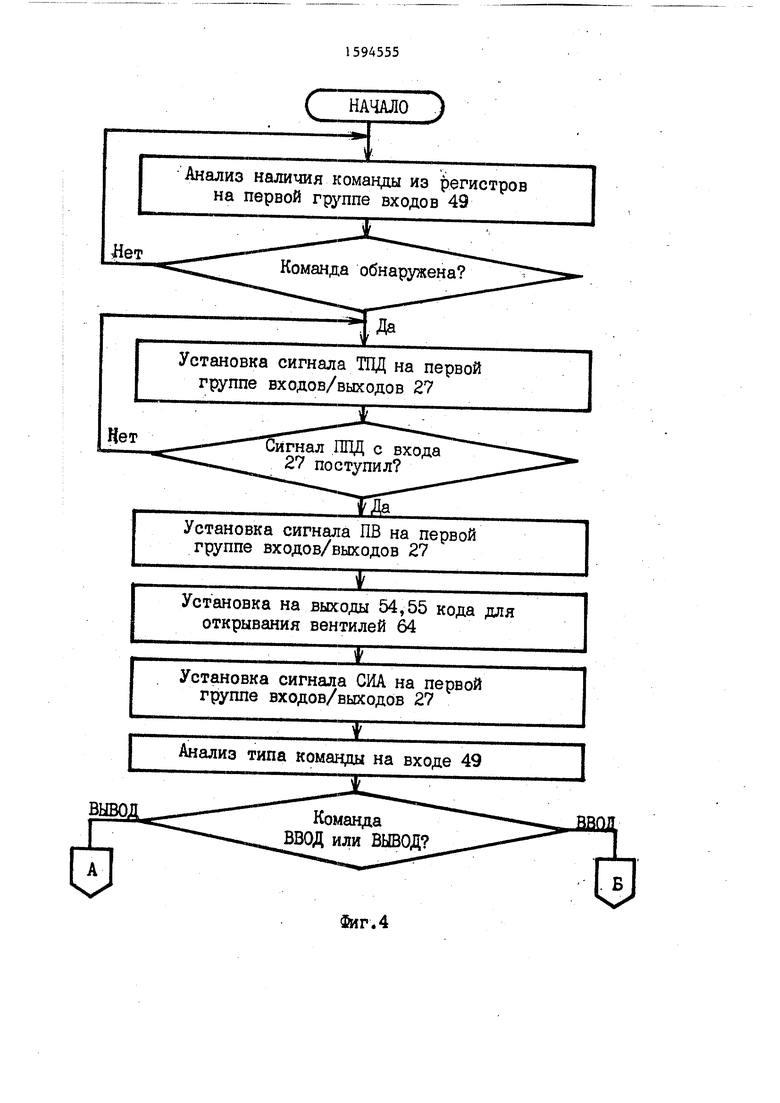

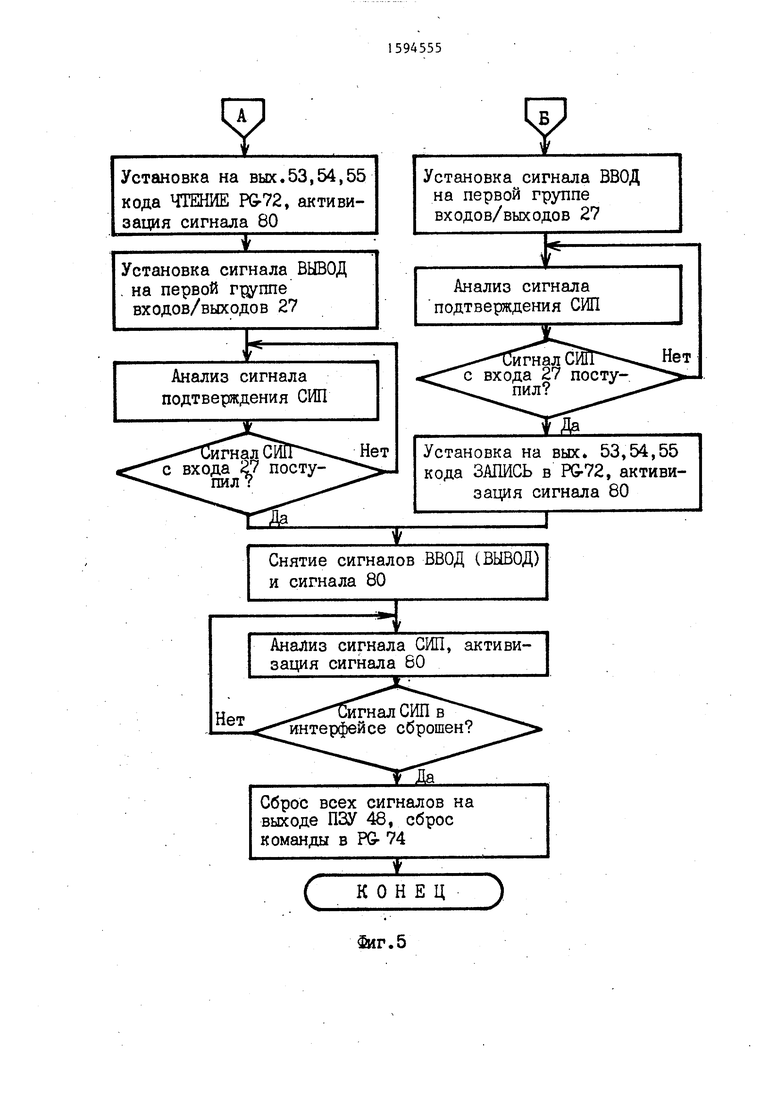

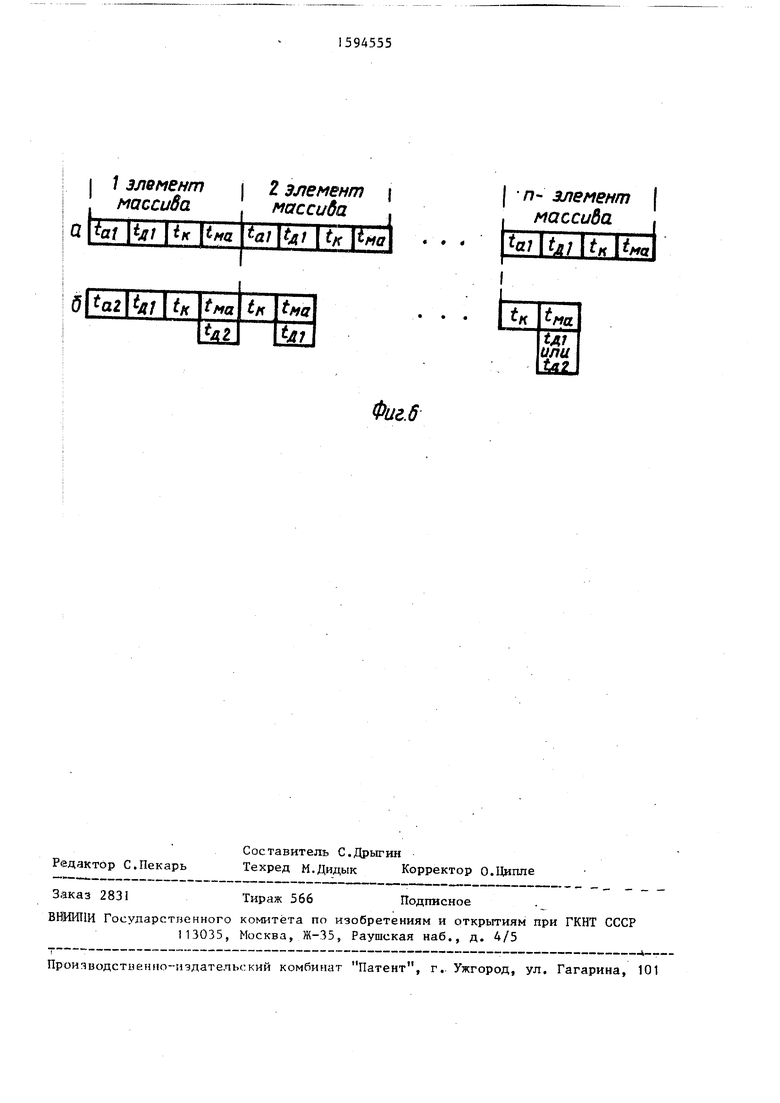

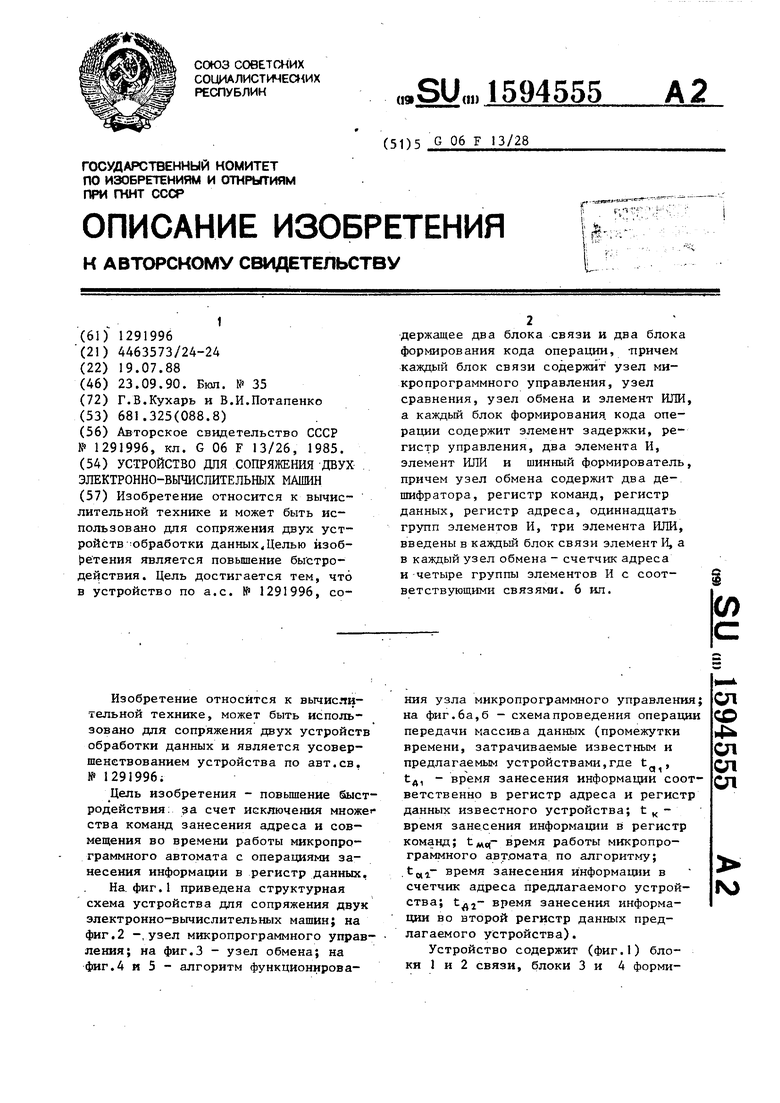

На. фиг.I приведена структурная схема устройства для сопряжения двук электронно-вычислительных машин; на фиг.2 -,узел микропрограммного управления; иа фиг.З - узел обмена; на фиг.4 и 5 - алгоритм функционирования узла микропрограммного управления; на фиг.6а,б - схемапроведения операции передачи массива данных (промежутки времени, затрачиваемые известным и предлагаемьп устройствами,где t , t, - время занесения информации соответственно в регистр адреса и регистр данных известного устройства; t - время занесения информации в регистр команд; t,,- время работы микропрограммного автомата по алгоритму; .tg,- время занесения информации в счетчик адреса предлагаемого устройства; время занесения информации во второй регистр данных предлагаемого устройства).

Устройство содержит (фиг.1) блоки 1 и 2 связи, блоки 3 и 4 формисд

со

4 СП

ел сд

1Ч

рования к од а операции, у злы 5и бмикро- программного управления, узлы 7 и 8 обмена информацией, элементы И 9 и 10, первый 11 и второй 12 элементы ИЛИ, узлы 13 и 1Л сравнения, элементы 15 и 16 задержки, регистры 17 и 18 управления, вторые элементы И 19 и 20, первые элементы И 21 и 22 третий 23 и четвертый 24 элементы ИЛИ, шинные формирователи 25 и 26, группы 27 и 28 командных входов/выходов блоков связи, группы 29 и 30 адресных/информационных входов/выходов блоков связи, вькоды 31 и 32 шинных формирователей, входы 33 и 34 группового адреса, линии 35 и 36 группы входов/выходов первого и второго блоков связи, линии 37 и 38

В начальный момент ЭВМ 1 и ЭВМ 2 в группах сигналов управления интерфейсом формируют сигналы Сброс, поступающие по одной из цепей входов/выходов 27 (28) блока связи на вход установки в О регистра 47 адреса микрокоманд (РАМ), и обеспечивают на выходах РАМ 47 адрес первой

группы выходов первого и второго бло- 20 микрокоманды рабочей микропрограммы.

ков формирования кода операции, линии 39 и 40 выходов первого и второго : блоков формирования кода операции (цепь кода операции Ввод), линии 41 и 42 выходов первого и второго блоков формирования кода операции (цепь кода операции Вывод).

Узел микропрограммного управления содержит (фиг,2) буферные усилители 43 и 44, мультиплексор 45, задающий генератор 46, регистр 47 адреса микрокоманд, постоянное запоминающее устройство (ПЗУ) 48, rpiynny входов 49 узла микропрограммного управления, вькоды 50-54 узла микропрограммного управления, группу выходов 55 узла микропрограммного управления.

Узел обмена содержит (фиг.З) дешифратор 56, дешифратор 57 команд, группу элементов И 58-68, элементы ИЛИ 69 и 70, счетчик 71 адреса, ре- гистр 72 данных, элемент ИЛИ 73, регистр 74 команд, вторую группу входов 75 узла обмена, первый вход 76 узла обмена, третий 77 и второй 78 входы узла обмена, первую группу входов 79 узла обмена, четвертый вход 80 узла обмена, первую 81, вторую 82 и третью 83 группы входов/выходов узла обмена, группу вькодов 84 узла обмена, вькод 85 узла обмена, группы элементов И 86-89, регистр 90 адреса

(второй регистр данных).

л

Работу устройства рассмотрим на примере использования его для содря- жения двух универсальных. ЭВМ типа Электроника-60, имеющих интерфейс типа Общая шина.

Узел 5 (6) представляет собой микропрограммный автомат (МА), реализован ный на регистре 47 (элементы памяти автомата), постоянном запоминающем .

25 устройстве (ПЗУ) 48 (память микропрограмм автомата), мультиплексоре 45 (элемент, обеспечивающий условные переходы автомата), при этом синхронизация автомата осуществляется за30 дающим генератором 46, формирующим импульсную последовательность, подаваемую на динамический управляющий вход РАМ 47 о

В исходном состоянии МА на выхода

35 53-55 формирует код, поступающий на входы 73 и 76 узла 7 (8) обмена и вход элемента И 9. Этот код обеспе чивает на выходе дешифратора 56 сигнал, открьшающий элементы И 62. При

40 этом сигналы с магистрали 29 (30) через группу входов/выходов 81 узла 7 (8) обмена через элементы И 62 поступают на группу входов/выходов 82: узла обмена.

45

50

55

Подготовка устройства сопряжения к работе и передаче информации осуществляется циклами записи (чтения) информации в (из) регистры 72 (90), 74 и счетчик 71 адреса узла 8 (7) обмена.

Передача первого слова информации из ЭВМ 1 и ЭВМ 2 по инициативе ЭВМ 1 включает цикл записи в счетчик 71 адреса узла 8 обмена адреса первой ячейки памяти ЭВМ 2 для первого зле- мента массива передаваемой информа щш, цикл записи в регистр 72 (или 90 узла 8 обмена передаваемых даиньк и

4

0

5

При этом входы/выходы 27 и 28 подключают к группам сигналов управления интерфейсом соответственно от первой и второй ЭВМ.

На входы 29 и 30 подают группы сигналов адреса данных соответственно от первой и второй ЭВМ. Выходы 31 и 32. шинных формирователей соединяют с цепями СИП интерфейса ЭВМ 1 и ЭВМ 2.

В начальный момент ЭВМ 1 и ЭВМ 2 в группах сигналов управления интерфейсом формируют сигналы Сброс, поступающие по одной из цепей входов/выходов 27 (28) блока связи на вход установки в О регистра 47 адреса микрокоманд (РАМ), и обеспечивают на выходах РАМ 47 адрес первой

0 микрокоманды рабочей микропрограммы.

Узел 5 (6) представляет собой микропрограммный автомат (МА), реализованный на регистре 47 (элементы памяти автомата), постоянном запоминающем ..

устройстве (ПЗУ) 48 (память микропрограмм автомата), мультиплексоре 45 (элемент, обеспечивающий условные переходы автомата), при этом синхронизация автомата осуществляется задающим генератором 46, формирующим импульсную последовательность, подаваемую на динамический управляющий вход РАМ 47 о

В исходном состоянии МА на выходах

53-55 формирует код, поступающий на входы 73 и 76 узла 7 (8) обмена и вход элемента И 9. Этот код обеспечивает на выходе дешифратора 56 сигнал, открьшающий элементы И 62. При

этом сигналы с магистрали 29 (30) через группу входов/выходов 81 узла 7 (8) обмена через элементы И 62 поступают на группу входов/выходов 82: узла обмена.

Подготовка устройства сопряжения к работе и передаче информации осуществляется циклами записи (чтения) информации в (из) регистры 72 (90), 74 и счетчик 71 адреса узла 8 (7) обмена.

Передача первого слова информации из ЭВМ 1 и ЭВМ 2 по инициативе ЭВМ 1 включает цикл записи в счетчик 71 адреса узла 8 обмена адреса первой ячейки памяти ЭВМ 2 для первого зле- , мента массива передаваемой информа щш, цикл записи в регистр 72 (или 90) узла 8 обмена передаваемых даиньк и

51594555

в регистр 74 узла 8 обме- Вывод.

цикл записи

на кода операции

Передача информади из ЭВМ 2 в ЭВМ 1 по инициативе ЭВМ 1 включает цикл записи в счетчик 71 адреса узла 8 обмена адреса первой ячейки памяти ЭВМ 2 для первого элемента массива передаваемой информации, цикл записи в регистр 74 узла 8 обмена кода операции Ввод и цикл чтения из регистра 72 (или 90) узла 8 обмена требуемой информации.

Передача информации по инициативе ЭВМ 2 происходит аналогично, но используются регистры узла 7 обмена. Операция обмена информацией между регистром 72 (или 90) и памятью ЭВМ 2 (1) осуществляется в режиме

прямого доступа к памяти под управлением МА соответствующего узла 6 (5) по окончании цикла записи кода операции в регистр 74. Одновременность работы ЭВМ I и ЭВМ 2 обеспечивается наличием двух магистралей связи 35, 37, 39, 41 и 36, 38, 40, 42, позволяющих каждой из ЭВМ : осуществлять независимый обмен с регистрами 74 и 72 и счетчиком 71 адреса .соответствующих узлов 8 (7) обмена.

Рассмотрим циклы записи (чтения) информации из ЭВМ 1 в (из) регистры 72, 74 и счетчик 21 адреса узла 8 обмена.

В соответствии с логикой работы интерфейса Общая щина в первой фазе каждого цикла обмена по группе

адресных/информационных входов/выходов 29 передается адрес регистра,

С которым будет осуществляться обмен, с некоторой задержкой по отнощению к передаче адреса вьщается сигнал СИЛ по группе входов/выходов 27. Сигналы адреса транслируются узлом обмена с входов/выходов 81 через элементы И 62 на выходы 82, старшие разряды поступают на вторые входы уз- лов 13 сравнения, на первые входы узлов 13 сравнения, подают код группового, адреса устройства сопряжения, присвоенный ему в адресном пространстве ЭВМ. При совпадении адреса на вторых входах 33 узла 13 сравнения с ког дом первых входов на его выходе формируется сигнал логической единицы, поступающей на информационный вход регистра 17 управления. На группу входов регистра 17 управления посту10

15

20

25

в ми г ни че

40 на об на со

45 пе во ме оп ми

50 це ко

. ко уп на

55 об 57 вх од 71

30

35

0

5

0

5

пают с магистрали 35 младшие разряды адреса, определяющие адрес одного из регистров 72, 74 или счётчика 71. Сигнал СИЛ через усилители 44 поступает на выход 52 узла 5 и далее на вход установки в О регистра 17 управления и вход элемента 15 задержки. При этом наличие сигнала СИЛ на установочном входе регистра 17 обеспечивает неактивное состояние данного входа.

С выхода элемента 15 задержки сигнал СИЛ активным уровнем поступает на вход записи регистра 17 и осуществляет запись кода адреса одного из регистров 72, 74 или счетчика 71, поданного на группу информационных входов регистра 17 управления, и сигнала с выхода узла 13 сравнения

Вторую фазу цикла обмена рассмотрим отдельно для операций записи и чтения регистров 72, 74 и счетчика 71 узла 8 обмена.

Операция Запись. Вторая фаза - цикла обмена начинается со снятия адреса с группы адресных/информационных входов/выходов 29, установки записываемой информации и поступления сигнала Вывод из интерфейса ЭВМ 1 по одной из цепей группы входов/выходов 27 через усилители 44 узла 5 на его выход 51 и выход блока 1 связи, на вход блока 3 формирования кода операции и вход первого элемента И 21 блока 3 формирования кода операции. Вписываемая информация поступает по цепям 29, 81 через элементы И 62 узла 7 обмена

0 на группу входов/выходов 82 узла 7 обмена и через магистраль 35 далее на группу входов/выходов 83 узла 8 обмена второго блока 2 связи. При совпадении сигналов на двух входах

5 первого элемента И 21 (сигнал Вывод и записанная информация с элемента 13) блока 3 формирования кода операции на выходе элемента И 21 формируется сигнал, подаваемый через

0 цепь 41 на вход 78 узла 8 обмена, который совместно с группой сигналов

кода адреса с выходов регистра 17 управления, подаваемых по цепям 37 на группу входов 79 узла 8 обмена,

5 обеспечивает на выходе дешифратора 57 сигнал записи информации с группы входов/выходов 83 узла 8 обмена в ,: один из .регистров 72, 74 или счетчик 71 адреса узла 3 обмена.

0

5

ды записи одного из регистров или прямо на вход О счет щка

Номер регистра или счетчика адре- са обеспечивается кодом, подаваемым с выходов регистра 17 управления по цепям 37 на группы входов 79 узла 8 обмена, и сигналом на входе 78„ Сигналы с выхода дешифратора 57 (сиг налы записи) обеспечивают открытие одной из групп элементов И 59 и (з1 и подачу информации на регистры 72 и 74 и счетчик 71. Одновременно через соответствующие элементы ИЛИ 70 и 73 сигналы записи поступают на вхо72 „ 74

71

адреса и осуществляют запись информации в выбранный узел. Формирование сигнала ответа (СИП) в интерфейсе ЭВМ осуществляется элементом ШШ 23 и шинным формирователем 25, с въко- да которого сигнал СИП подается в интерфейс ЭВМ.

ЭВМJполучив сигнал СИП.от устройства, снимает сигнал Вывод, что приводит к снятию сигнала записи, формируемого дешифратором 57.

Снятие сигнала Вывод обеспечивает снятие сигнала СИП, формируемого элементом ИЛИ 23 и шинным формирователем 25 о

Фаза Вывод завершается снятием сигнала СИЛ на входах/выходах 27 первого блока 1 связи. При этом на выходе установки в О регистра 17 управления устанавливается активный уровень и регистр 17 сбрасьшается в нулевое состояние, обеспечивая сняти разрешающего сигнала на входе первого элемента И 21

Это вызывает формирование на выходе элемента И 21 логического нуля, что приводит к установке дешифратора 57 узла обмена в нейтральное состояние .

Операция Чтение g Вторая фаза цикла обмена начинается со снятия адреса с группы адресных/информа1злон ных входов/выходов 29 и поступления сигнала Ввод из интерфейса ЭВМ по одной из цепей группы входов/выходов 27 через усилители 44 узла 5 на выход 50 узла управления и далее на вход второго элемента И 19 блока 3 формирования кода операции, С второго элемента И 19 сигнал совпадения (сигнал Ввод и записанная информация с элемента 13) поступает на вход элемента ИЛИ 11 блока 1 связ на один из входов элемента ИЛИ 23 и

0

5

0

5

0

5

0

5

0

5

по цепи 39 на вход 77 узла 8 обмена. С выхода элемента ИЛИ 11 сигнал поступает на вход 76 узла 7 обмена первого блока связи и обеспечивает формирование на выходе дешифратора 56 узла 7 обмена сигнала, открывающего элементы И 63 и блокирующего элементы. И 62. Далее процессы аналогичны операции Запись, за исключением того, что код на дешифратор 57 узла 8 обмена, подается совместно по цепям 37, 39 и дешифратор 57 узла 8 обмена формирует один из сигналов (сигнал чтения), открывающий один из элементов И 66- 68 и обеспечивающий трансляцию содержимого одного из регистров 72, 74 или счетчика 71 адреса на группу входов/выходов 83 узла 8 обмена и далее через группу входов/выходов 82 узла 7 обмена, элементы И 63, группу входов/выходов 81 узла 7 обмена, цепь 29 в интерфейс ЭВМ 1.

Порядок функционирова ния МА. После установки РАМ 4 в нулевое состояние из ПЗУ 48 выбирается первая микрокоманда микропрограммы, обеспечивающей логику функционирования узла 7 (8).

На фиг.4 и 5 приведен алгоритм - функционирования узла 7 (8) для ЭВМ типа Электроника-60.

Выполнение микропрограммы начинается с анализа сигналов, поступающих из регистра 74 по цепям 84 и 85 и представляющих код команды для МА на группе входов 49 узла 6 (5), и сигнала управления, поступающего на первый вход элемента И 9. При обнаружении кода одной из команд (Ввод или Вывод) МА осуществляет выдачу из ПЗУ 48 через усилители 43 по одной из цепей входов/выходов 27 (28) сигнала ТПД, обеспечивая требование на доступ к интерфейсу ЭВМ 2 (1). Поступление сигнала подтверждения ШЩ от ЭВМ 2(1) по одной из цепей группы входов/выходов 27 (28) через усилители 44 иа мультиплексор 45 обеспечивает ветвление микропрограммы и установку на выходе ПЗУ 48 сигнала ПВ, поступающего через усилители 43 на интерфейс ЭВМ 2 (1). Данный сигнал сохраняется МА до завершения операций передачи информации в (из) память ЭВМ.

Передача информации в (из) ЭВМ начинается с установки на выходах 55 и 54 узла 6 (5) кода, поступаюего соответственно на группу входов 5 узла 8 обмена и через элемент ЛИ 12 на вход 76 узла 8 обмена и .: беспечивающего на выходе дешифратоа 56 сигнал,открывающей элемент 64. При этом содержимое счетчики j 1 адреса поступает через группу вхо- ов/выходов 81 на магистраль 30 (29) адрес/данные ЭВМ 2 (1) и интерпреируется ЭВМ как адрес ячейки, с которой будет осуществляться работа. Затем на выходе ПЗУ 48 формируется сигнал СИЛ, поступающий через усилители 43, входы/выходы 28 (27) в интерфейс ЭВМ 2 (1). После этого МА через мультнплек- сор 45 осуществляет анализ типа команды на группе входов 49 и переходит к выполнению операций Ввод и Вывод. При обнаружении команды Вывод МА на выходах 55, 54 и 53 формирует код, поступающий соответственно на входы 75 и 76 узла 8 обмена и через элемент И 10 на вход 80 узла 8 обмена. Этот код обеспечивает на выходе дешифратора 56 снятие сигнала, открывающего элемент И 64, и появление сигнала, отк1 тающего элемент И 65 и увеличивающего содержимое счетчика 71 адреса, на цепи 53, входе элемента И 10 и входе 80 узла 8 обмена.

При этом содержимое регистра 72 данных поступает через группу вхо-с- дов/выходов 81 узла 8 (7) обмена в ЭВМ 2 (1), а содержимое счетчика 71 адреса увеличивается на единицу. Затем из ПЗУ 48 через усилители 43 на входы/выходы 27 (28) в ЭВМ выдается сигнал Вывод . затем МА осуществляет ожидание от ЭВМ 2 (1) сигнала подтверждения СИП, который поступает от ЭВМ 2 (1) по одной из цепей через усилители 44 к мультиплексору 45. При поступлении сигнала СИП МА снимает с выхода ПЗУ 48 ранее сформированный сигнал Вьшод на выход 28 (27). Затем МА осуществляет анализ сигнала СИП, поступающего из интерфейса ЭВМ 2, одновременно повторно активизирует сигнал иа входе 80, увеличивая срдержимое счетчика 71 на единицу. При сбросе в интерфейсе ЭВМ сигнала СИП МА осуществляет сброс всех ранее сформированных сигналов (конед вЬтолнения цикла) и возвращается в исходное состояние. При этом на выходах 55 и

4555. 10

54 формирует код, обеспечивающий появление на выходе дешифратора 56 сигнала сброса регистра 74 команд. При обнаружении на входах 49 команды Ввод МА осуществляет вьщачу из ПЗУ через усилители 43 сигнала Ввод на входы/вьпсоды 28 (27) устройства. Поступление от ЭВМ сигнала СИП по одной из цепей входов/выходон 27 (28) через усилители 44 к мультиплексору 45 означает, что на цепи 30 (29) подана требуемая информация. МА осуществляет формирование на выходе ПЗУ 48 и на выходах 55 и 54 кода, обеспечивающего снятие сигнала, открьтающего элемент И 64, и появление на выходе дешифратора 56 сигна10

15

0

5

0

5

0

5

0

5

ла, открьшающего элемент И 60 и через элемент ИЛИ 70 записьшающего в регистр 72 данных информацию с входов/выходов 81. Одновременно активизируется сигнал на входе 80, обеспечивая увеличение содержимого счетчика адреса на единицу. Далее МА завершает вьшолнение операции Ввод аналогично завершению операции Вьшод.

Во .время выполнения МА операции Ввод или Вьюод ЭВМ I производит аналогично описанному цикл записи (чтения) информации в (из) второй регистр 90 данных.

Передача адреса регистра 90 и формирование управляющих сигналов на выходе блока формирования кода операции происходит аналогично первой фазе цикла обмена.

Во второй фазе цикла обмена операции Запись.и Чтение происходит аналогично операциям с регистром 72 данных.

Одновременно с рассмотренными операциями, вьтолняемыми первой ЭВМ, аналогичным образом осуществляются операции обмена по инициативе второй ЭВМ.

При этом передача информации между блоками связи осуществляется по магистрали 36, управляющая информа-. ция передается по линиям 38, 30 и 42, т.е. осуществляется одновременная передача информационных слов от первой и втЬрой ЭВМ с одновременным увеличением на два содержимого счетчика 71 адреса.

Увеличение на два содержимого счетчика 71 адреса происходит только при пересьшкё массива информации после выполнения определенной коман

ДМ, засылаемой в регистр команд (например, Ввод +1/ Вывод +1). В остальных случаях происходит блокировка входа +1 счетчика 71 адреса путем пересылки в регистр команд команды Ввод / Вывод, при которой В; дополнительном разряде появляется пртенциал, запрещающий прохождение импульсов через вентиль 9 (10) на с|1етный вход счетчика адреса.

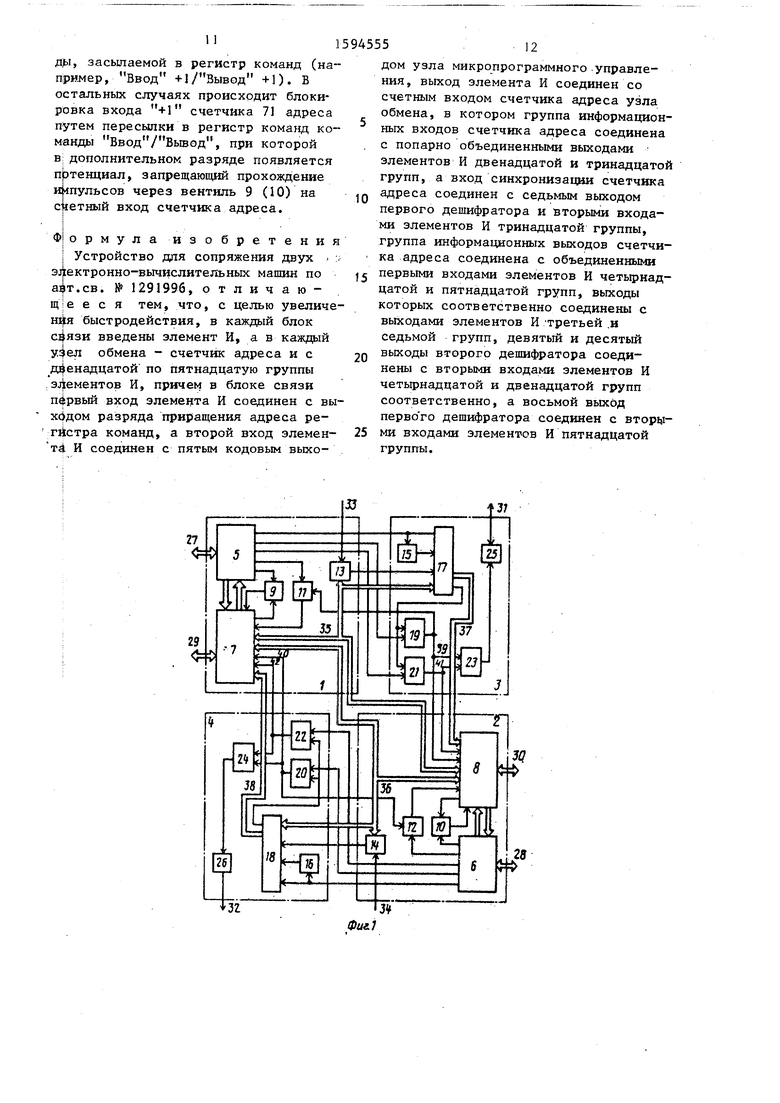

Ф|ормула изобретения I Устройство для сопряжения двух . ;. э;)1ектронно-вычислительных машин по .св. № 1291996, отличаю- е с я тем, что, с целью увеличе- быстродействия, в каждый блок с4язи введены элемент И, а в каждый у4ел обмена - счетчик адреса и с двенадцатой по пятнадцатую группы .элементов И, причем в блоке связи первый вход элемента И соединен с выходом разряда приращения адреса регистра команд, а второй вход элемен- т4 И соединен с пятым кодовым выхо12

0

дом узла микропрограммного управления, выход элемента И соединен со счетным входом счетчика адреса узла обмена, в котором группа информационных входов счетчика адреса соединена с попарно объединенными выходами элементов И двенадцатой и тринадцатой групп, а вход синхронизации счетчика адреса соединен с седьмым выходом первого дешифратора и вторыми входами элементов И тринадцатой группы, группа информационных выходов счетчи- ка адреса соединена с объединенными

5 первыми входами элементов И четырнадцатой и пятнадцатой групп, выходы которых соответственно соединены с выходами элементов И /третьей .и седьмой групп, девятый и десятый

Q выходы второго дешифратора соединены с вторыми входами элементов И четырнадцатой и двенадцатой групп соответственно, а восьмой выход перво го дешифратора соединен с BTopw5 ми входами элементов И пятнадцатой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительных машин | 1988 |

|

SU1580385A1 |

| Устройство для сопряжения двух электронно-вычислительных машин | 1985 |

|

SU1291996A1 |

| Устройство для сопряжения ЭВМ | 1991 |

|

SU1837306A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1989 |

|

SU1777144A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для контроля и регистрации асинхронных сигналов интерфейса | 1982 |

|

SU1084803A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения двух устройств обработки данных. Целью изобретения является повышение быстродействия. Цель достигается тем, что в устройство по а.с. N 1291996, содержащее два блока связи и два блока формирования кода операции, причем каждый блок связи содержит узел микропрограммного управления, узел сравнения, узел обмена и элемент ИЛИ, а каждый блок формирования кода операции содержит элемент задержки, регистр управления, два элемента И, элемент ИЛИ и шинный формирователь, причем узел обмена содержит два дешифратора, регистр команд, регистр данных, регистр адреса, одиннадцать групп элементов И, три элемента ИЛИ, введены в каждый блок связи элемент И, в каждый узел обмена счетчик адреса и четыре группы элементов И с соответствующими связями. 6 ил.

27(28)

7 к гп

, СИА,ГПДППА

.пв,8бод,вывод Сброс,

Фиг.2

НАЧАЛО

Анализ наличия команды из {регистров на первой группе входов 49

Установка сигнала ТПД на первой группе входов/выходов 27

Установка сигнала ПВ на первой группе входов/выходов 27

IT

Установка на вых:оды 54,55 кода для открывания вентилей 64

Установка сигнала СИЛ на первой группе входов/выходов 27

Анализ типа на входе 49

Фиг. 4

Установка на вых.53,54,55

кода ЧТЕШЕ Р&72, активизация сигнала 80

Установка сигнала ВЫВОД . на первой гщппе входов/выходов 27

Анализ сигнала подтверждения СИП

Нет

игнал СИП в интерфейсе сброшен

Установка сигнала ВВОД на первой группе

входов/выходов 27

Анализ сигнала подтверждения СИП

гнал CL с входа 27 поступил

Нет

Установка на вых 53,54,55 кода ЗАПИСЬ в PG-72, активизация сигнала 80

Фиг.5

2 элемент массива

MilELEEl

п- элемент массива

51Ш717Л

Фиг.6

| Устройство для сопряжения двух электронно-вычислительных машин | 1985 |

|

SU1291996A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-23—Публикация

1988-07-19—Подача