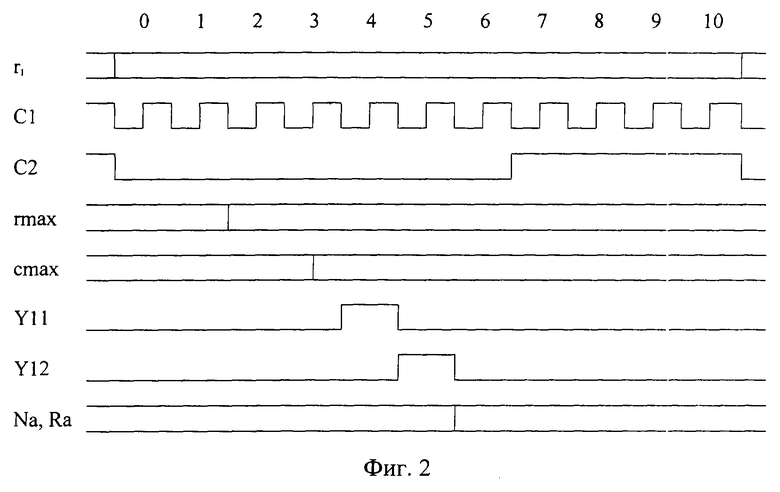

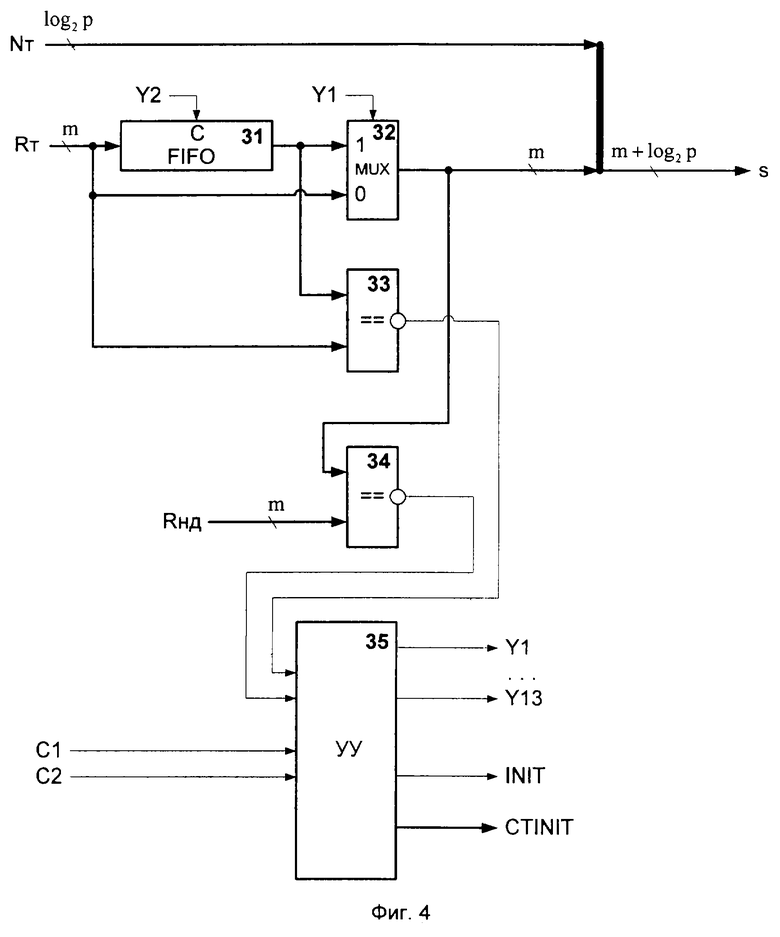

Изобретение относится к системам телекоммуникаций и вычислительной техники и применяется для исправления ошибок синхронизации, возникающих в каналах передачи или воспроизведения информации со вставками/выпадениями бит. Техническим результатом является более точная локализация в потоке данных из канала ошибок синхронизации типа вставок/выпадений бит в условиях наличия в окрестностях этих ошибок дополнительных аддитивных ошибок. Технический результат достигается за счет того, что устройство исправления ошибок синхронизации в потоке данных содержит последовательно-параллельный преобразователь, первый буфер FIFO, регистр сдвига, схему формирования локаторов, первый вычитатель, мажоритарную схему, первый сумматор, первый компаратор, буферное запоминающее устройство, первый счетчик, второй счетчик, схему блокировки записи. 3 з.п. ф-лы, 10 ил.

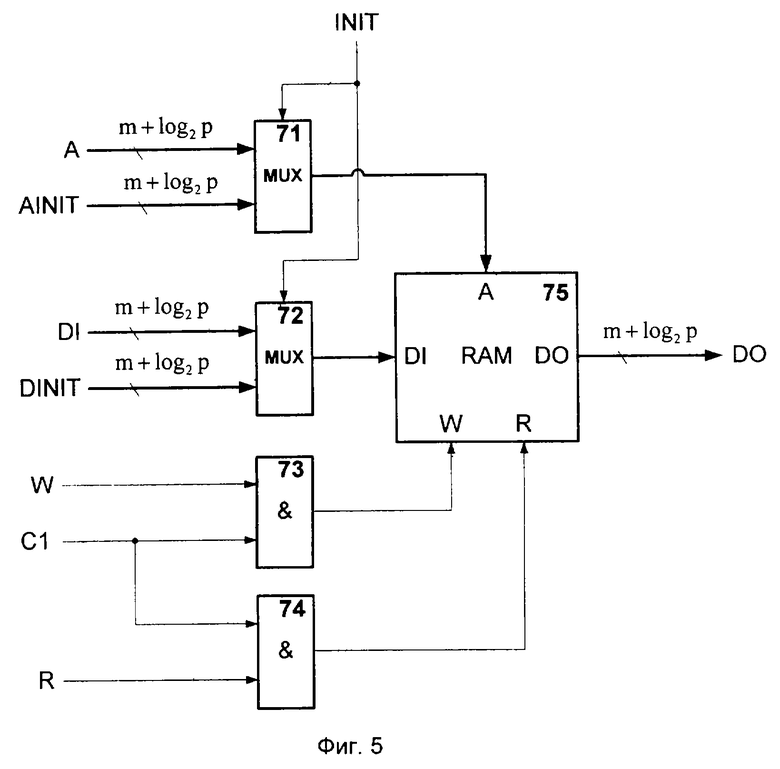

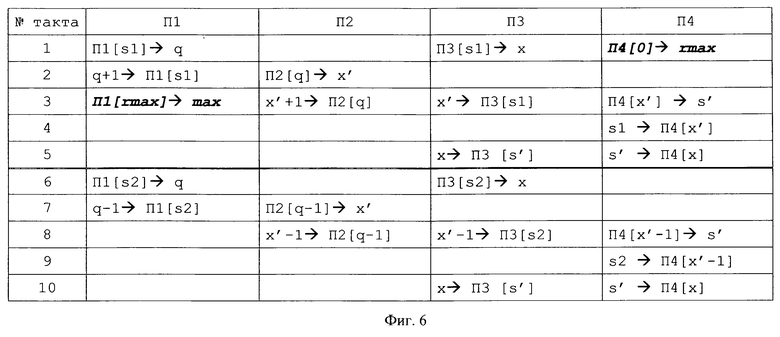

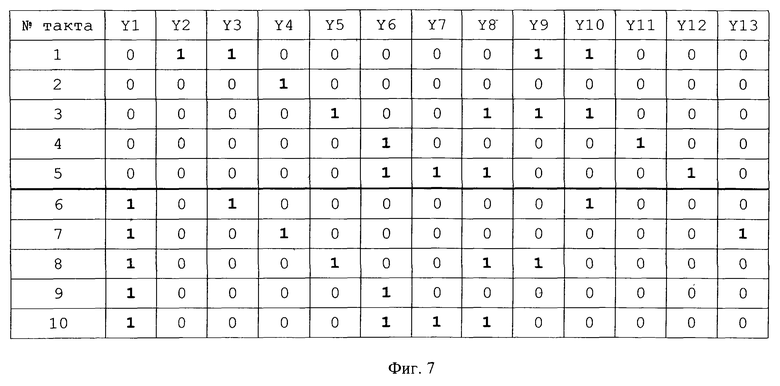

1. Устройство исправления ошибок синхронизации в потоке данных, содержащее последовательно-параллельный преобразователь, первый буфер FTFO, регистр сдвига, буферное запоминающее устройство, причем вход последовательно-параллельного преобразователя является входом "Входные данные" устройства исправления ошибок синхронизации в потоке данных, выход регистра сдвига соединен со входом данных записи буферного запоминающего устройства, тактовый вход последовательно-параллельного преобразователя является вторым тактовым входом "Такт С2" устройства исправления ошибок синхронизации в потоке данных, отличающееся тем, что в устройство введены схема формирования локаторов, мажоритарная схема, первый вычитатель, первый сумматор, первый компаратор, первый счетчик, второй счетчик, схема блокировки записи, причем первый тактовый вход мажоритарной схемы является первым тактовым входом "Такт С1" устройства исправления ошибок синхронизации в потоке данных, тактовый вход первого буфера FIFO, тактовый вход регистра сдвига, тактовый вход первого счетчика, второй тактовый вход мажоритарной схемы, тактовый вход схемы блокировки записи соединены с шиной второго тактового входа "Такт С2" устройства исправления ошибок синхронизации в потоке данных, выход переноса первого счетчика соединен с тактовым входом второго счетчика, выход параллельных данных последовательно-параллельного преобразователя соединен со входом данных схемы формирования локаторов, выход последовательных данных последовательно-параллельного преобразователя соединен со входом данных первого буфера FIFO, выход данных первого буфера FIFO соединен со входом данных регистра сдвига, выход схемы формирования локаторов соединен с первым входом первого вычитателя, выход первого вычитателя соединен с первым входом данных мажоритарной схемы, первый выход мажоритарной схемы соединен с первым входом первого сумматора, выход данных первого счетчика соединен со вторым входом данных мажоритарной схемы и вторым входом первого компаратора, второй выход мажоритарной схемы соединен с первым входом первого компаратора, выход второго счетчика соединен со вторым входом первого вычитателя и вторым входом первого сумматора, выход первого сумматора соединен с адресным входом схемы блокировки записи и входом адреса записи буферного запоминающего устройства, выход первого компаратора соединен с входом записи схемы блокировки записи, выход разрешения записи схемы блокировки записи соединен со входом стробирования записи буферного запоминающего устройства, выход данных буферного запоминающего устройства является выходом "Выходные данные" устройства исправления ошибок синхронизации в потоке данных, вход адреса чтения буферного запоминающего устройства является входом "Адрес чтения выходных данных" устройства исправления ошибок синхронизации в потоке данных, вход стробирования чтения буферного запоминающего устройства является входом "Строб чтения выходных данных" устройства исправления ошибок синхронизации в потоке данных.2. Устройство по п.1, отличающееся тем, что мажоритарная схема содержит устройство управления, второй буфер FIFO, третий буфер FIFO, четвертый буфер FIFO, первый мультиплексор, второй мультиплексор, третий мультиплексор, четвертый мультиплексор, пятый мультиплексор, шестой мультиплексор, седьмой мультиплексор, восьмой мультиплексор, второй компаратор, третий компаратор, четвертый компаратор, первый регистр, второй регистр, третий регистр, четвертый регистр, пятый регистр, шестой регистр, первый блок памяти, второй блок памяти, третий блок памяти, четвертый блок памяти, первую схему инкремента/декремента, вторую схему инкремента/декремента, причем вход данных второго буфера FIFO, второй вход первого мультиплексора, второй вход второго компаратора соединены с шиной первого входа данных мажоритарной схемы, старшие разряды второго входа второго мультиплексора и старшие разряды первого входа пятого мультиплексора соединены с шиной второго входа данных мажоритарной схемы, выход второго буфера FIFO соединен с первым входом первого мультиплексора и первым входом второго компаратора, выход первого мультиплексора соединен с первым входом третьего компаратора, младшими разрядами второго входа второго мультиплексора и младшими разрядами первого входа пятого мультиплексора, второй вход третьего компаратора соединен с шиной константы "Кнд", инверсный выход второго компаратора соединен с первым управляющим входом устройства управления, инверсный выход третьего компаратора соединен со вторым управляющим входом устройства управления, первый тактовый вход мажоритарной схемы является первым тактовым входом устройства управления, второй тактовый вход мажоритарной схемы является вторым тактовым входом устройства управления, первый выход устройства управления соединен с управляющим входом первого мультиплексора, управляющим входом четвертого мультиплексора, входом выбора операции первой схемы инкремента/декремента, входом выбора операции второй схемы инкремента/декремента, второй выход устройства управления соединен с тактовым входом второго буфера FIFO, управляющим входом седьмого мультиплексора, тактовым входом шестого регистра, третий выход устройства управления соединен с входом чтения третьего блока памяти, тактовым входом четвертого регистра, четвертый выход устройства управления соединен с входом записи первого блока памяти, входом чтения второго блока памяти, тактовым входом третьего регистра, пятый выход устройства управления соединен с управляющим входом второго мультиплексора, входом записи второго блока памяти, тактовым входом пятого регистра, шестой выход устройства управления соединен с входом записи четвертого блока памяти, седьмой выход устройства управления соединен с управляющим входом шестого мультиплексора, восьмой выход устройства управления соединен с входом записи третьего блока памяти, девятый выход устройства управления соединен с входом чтения четвертого блока памяти, десятый выход устройства управления соединен с входом чтения первого блока памяти, тактовым входом второго регистра, одиннадцатый выход устройства управления соединен с тактовым входом третьего буфера FIFO, тактовым входом четвертого буфера FIFO, двенадцатый выход устройства управления соединен с тактовым входом первого регистра, тринадцатый выход устройства управления соединен с управляющим входом третьего мультиплексора, четырнадцатый выход устройства управления соединен с входом признака инициализации первого блока памяти, входом признака инициализации второго блока памяти, входом признака инициализации третьего блока памяти, входом признака инициализации четвертого блока памяти, пятнадцатый выход устройства управления соединен с входом адреса инициализации первого блока памяти, входом адреса инициализации второго блока памяти, входом данных инициализации и входом адреса инициализации третьего блока памяти, входом данных инициализации и входом адреса инициализации четвертого блока памяти, вход данных инициализации первого блока памяти соединен с шиной константы "О", вход данных инициализации второго блока памяти соединен с шиной константы "О", выход второго мультиплексора соединен с входом адреса первого блока памяти, выход данных первого блока памяти соединен с входом данных второго регистра, выход второго регистра соединен с входом данных первой схемы инкремента/декремента, входом данных четвертого буфера FIFO, вторым входом четвертого компаратора, первым входом третьего мультиплексора, выход первой схемы инкремента/декремента соединен с вторым входом третьего мультиплексора, входом данных первого блока памяти, выход третьего мультиплексора соединен с входом адреса второго блока памяти, выход данных второго блока памяти соединен с входом данных третьего регистра, выход третьего регистра соединен с входом данных второй схемы инкремента/декремента, первым входом четвертого мультиплексора, выход второй схемы инкремента/декремента соединен с вторым входом четвертого мультиплексора, входом данных второго блока памяти, выход четвертого мультиплексора соединен с первым входом шестого мультиплексора, выход пятого мультиплексора соединен с входом адреса третьего блока памяти, входом данных четвертого блока памяти, выход данных третьего блока памяти соединен с входом данных четвертого регистра, выход четвертого регистра соединен со вторым входом шестого мультиплексора, выход шестого мультиплексора соединен с первым входом седьмого мультиплексора, входом данных третьего блока памяти, второй вход седьмого мультиплексора соединен с шиной константы "О", выход седьмого мультиплексора соединен с входом адреса четвертого блока памяти, выход данных четвертого блока памяти соединен с входом данных пятого регистра, входом данных шестого регистра, выход пятого регистра соединен с вторым входом пятого мультиплексора, выход шестого регистра соединен с первым входом второго мультиплексора, входом данных третьего буфера FIFO, вторым входом восьмого мультиплексора, выход третьего буфера FIFO соединен с первым входом восьмого мультиплексора, выход четвертого буфера FIFO соединен с первым входом четвертого компаратора, выход четвертого компаратора соединен с управляющим входом восьмого мультиплексора, выход восьмого мультиплексора соединен с входом данных первого регистра, младшие разряды выхода первого регистра являются первым выходом мажоритарной схемы, старшие разряды выхода первого регистра являются вторым выходом мажоритарной схемы.3. Устройство по п.2, отличающееся тем, что каждый блок памяти содержит девятый мультиплексор, десятый мультиплексор, первый логический элемент И, второй логический элемент И, оперативное запоминающее устройство, причем первый вход девятого мультиплексора является входом адреса блока памяти, первый вход десятого мультиплексора является входом данных блока памяти, второй вход девятого мультиплексора является входом адреса инициализации блока памяти, второй вход десятого мультиплексора является входом данных инициализации блока памяти, первый вход первого логического элемента И является входом записи блока памяти, второй вход второго логического элемента И является входом чтения блока памяти, второй вход первого логического элемента И, первый вход второго логического элемента И соединены с шиной первого тактового входа мажоритарной схемы, управляющий вход девятого мультиплексора и управляющий вход десятого мультиплексора соединены с шиной входа признака инициализации блока памяти, выход девятого мультиплексора соединен с входом адреса оперативного запоминающего устройства, выход десятого мультиплексора соединен с входом данных оперативного запоминающего устройства, выход первого логического элемента И соединен с входом стробирования записи оперативного запоминающего устройства, выход второго логического элемента И соединен с входом стробирования чтения оперативного запоминающего устройства, выход данных оперативного запоминающего устройства является выходом данных блока памяти.4. Устройство по п.1, отличающееся тем, что схема блокировки записи содержит третий логический элемент И, пятый компаратор, четвертый логический элемент И, пятый логический элемент И, седьмой регистр, второй вычитатель, схему деления на два, третий вычитатель, восьмой регистр, шестой компаратор, JK-триггер, логический элемент ИЛИ, причем первый вход третьего логического элемента И является входом записи схемы блокировки записи, второй вход третьего логического элемента И является тактовым входом схемы блокировки записи, первый вход второго вычитателя, вход данных седьмого регистра, второй вход шестого компаратора соединены с шиной входа адреса схемы блокировки записи, выход третьего логического элемента И соединен с первым входом четвертого логического элемента И, тактовым входом седьмого регистра, первым входом пятого логического элемента И, тактовым входом JK-триггера, выход седьмого регистра соединен с вторым входом второго вычитателя, вторым входом третьего вычитателя, выход второго вычитателя соединен с первым входом пятого компаратора, входом схемы деления на два, выход схемы деления на два соединен с первым входом третьего вычитателя, выход третьего вычитателя соединен с входом данных восьмого регистра, выход восьмого регистра соединен с первым входом шестого компаратора, второй вход пятого компаратора соединен с шиной константы "О", прямой выход пятого компаратора соединен с вторым входом пятого логического элемента И, J-входом JK-триггера, инверсный выход пятого компаратора соединен с вторым входом четвертого логического элемента И, выход пятого логического элемента И соединен с тактовым входом восьмого регистра, выход шестого компаратора соединен с входом К JK-триггера, вторым входом логического элемента ИЛИ, инверсный выход JK-триггера соединен с первым входом логического элемента ИЛИ, выход логического элемента ИЛИ соединен с третьим входом четвертого логического элемента И, выход четвертого логического элемента И является выходом разрешения записи схемы блокировки записи.