Изобретение относится к схеме интерфейса для передачи данных через последовательный интерфейс от процессора и к процессору и к способу передачи данных между последовательным интерфейсом и процессором.

Заявленное изобретение предназначено для последовательной, в особенности беспроводной передачи данных к процессору, размещенному, например, на карте с микросхемой (чип-карте). В особенности заявленное изобретение пригодно для беспроводной передачи данных между устройством считывания с карт и бесконтактной картой с микросхемой, содержащей процессор.

В этих случаях использования процессор следует разгружать, чтобы иметь возможность применять процессор с более низкой тактовой частотой. Тем самым должно снижаться потребление тока (в современных процессорах потребление тока пропорционально тактовой частоте). Кроме того, процессор максимально часто и на максимально возможное время должен переключаться в так называемый неактивный или дежурный режим, в котором процессор не работает и поэтому потребляет значительно меньше тока.

В соответствии с современным уровнем техники передача данных между последовательным интерфейсом и процессором производится посредством параллельно-последовательного и соответственно последовательно-параллельного преобразования через так называемый Универсальный асинхронный приемопередатчик (УАПП). Последний реализуется обычно посредством сдвигового регистра на одной стороне, к которой подключен, например, приемопередатчик для беспроводной передачи. В этот сдвиговый регистр может осуществляться побитная запись (при приеме) и соответственно побитное считывание (при передаче).

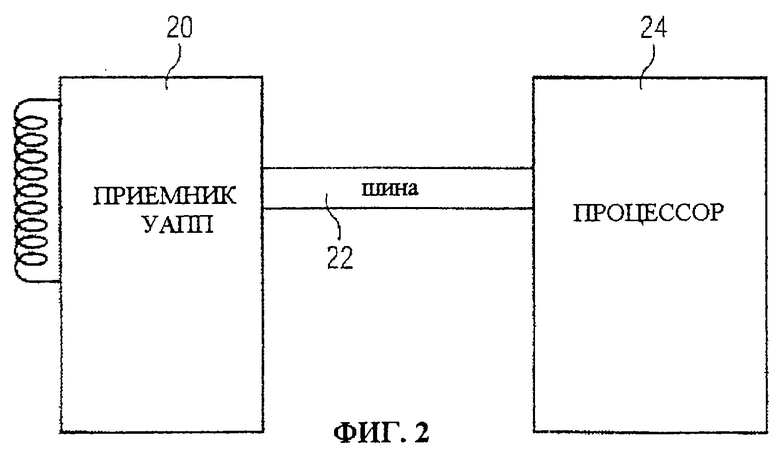

Процессор на другой стороне УАПП должен получать от УАПП данные параллельно и синхронно во времени согласно применяемому протоколу передачи данных и соответственно предоставлять ему эти данные (см. фиг.1 и 2). Это предъявляет довольно высокие требования к возможностям обработки данных процессором в реальном времени. Такие высокие требования к возможностям обработки данных в реальном времени вступают в противоречие с требованием, состоящим в том, что процессор должен потреблять как можно меньший ток и быть в максимальной степени экономичным. Именно в случае бесконтактных карт с микросхемами необходимо иметь возможность применения процессоров, которые в максимальной степени просты, тактируются с наиболее низкой возможной частотой и поэтому потребляют очень малый ток и являются весьма дешевыми. Однако такие процессоры могут не выполнять упомянутые выше требования.

Поэтому в настоящее время в случае бесконтактных карт с микросхемами используют способ, при котором последовательная информация побитно считывается с процессора с вывода последовательного интерфейса и соответственно записывается на вывод последовательного интерфейса. Эта задача, однако, требует очень большого времени вычислений процессора, так что вновь возникает необходимость использования процессора с более высоким быстродействием.

Поэтому задачей настоящего изобретения является создание схемы интерфейса для передачи данных через последовательный интерфейс от процессора и к процессору, в которой передача данных может производиться без нагрузки процессора. Кроме того, задачей настоящего изобретения является создание соответствующего способа, обеспечивающего передачу данных между последовательным интерфейсом и процессором.

В соответствии с изобретением эта задача решается с помощью схемы интерфейса, в которой между последовательным интерфейсом и процессором включено запоминающее устройство (ЗУ), рассчитанное на несколько длин слов шины или процессора (например, байт).

Указанная задача решается также способом, при котором данные принимаются последовательно побитно и считываются в ЗУ, и от процессора вновь там побитно считываются, или соответственно от процессора побайтно записываются в ЗУ и оттуда побитно передаются.

При этом особенно предпочтительно, если запись в ЗУ и считывание из ЗУ может производиться по слову или побитно. Для этого особенно предпочтительно, что ЗУ имеет указатель записи и указатель считывания, которые могут отдельно адресовать каждый бит или каждое слово (например, байт).

Для дополнительной экономии тока предпочтительно, если процессор имеет режим экономии тока (неактивный или дежурный режим) с минимальным потреблением тока.

Кроме того, предпочтительным является введение в ЗУ блока сравнения. Тем самым можно дополнительно разгрузить процессор.

Предпочтительным является также то, что блок сравнения может содержать простую логическую схему, которая автоматически сравнивает каждый принятый бит с содержимым ячейки памяти в ЗУ, в которую должен быть записан принимаемый бит.

Для дополнительного упрощения схемы ЗУ может быть интегрировано в модуле процессора или в модуле приемника. Дополнительное упрощение схемы также возможно в том случае, если ЗУ реализуется ячейками оперативного ЗУ (ОЗУ) из обычного ОЗУ в адресной области процессора.

Для дополнительной разгрузки процессора можно дополнительно к ЗУ предусмотреть модуль контрольной суммы. Дополнительно к модулю контрольной суммы можно также предусмотреть блок сравнения, который сравнивает контрольную сумму принятых данных с ожидаемой предварительно вычисленной контрольной суммой. Таким путем можно обеспечить дополнительную разгрузку процессора.

Предпочтительно ЗУ может быть выполнено в форме кольцевой структуры и/или снабжено устройством обнаружения переполнения, которое при наступающем переполнении ЗУ активизирует процессор. Тем самым можно избежать потерь данных вследствие перезаписи в ЗУ.

В способе, соответствующем изобретению, для разгрузки процессора предпочтительно может быть предусмотрено, что указатели записи и считывания могут приводиться в действие автоматически, без запуска процессора.

Существенно более высокую гибкость программирования предоставляет способ, при котором процессор может свободно устанавливать указатели записи и считывания ЗУ.

Еще более значительная программно-техническая гибкость предоставляется способом, при котором процессор обрабатывает отдельные ячейки памяти ЗУ как составные части собственной адресной области и тем самым может по свободному выбору осуществлять в них запись и считывание.

Дополнительная разгрузка процессора может обеспечиваться тем, что предусматривается автоматическое сравнение данных, причем ожидаемые данные должны быть сохранены в соответствующей позиции в ЗУ, и посредством простой логической схемы каждый принимаемый бит сравнивается с данными в ячейке памяти ЗУ, в которую он записывается.

При этом указатель записи предпочтительно может выдавать как адресацию ожидаемого бита, с которым должно осуществляться сравнение, так и адресацию принимаемого бита, который в текущий момент должен записываться в ЗУ. Таким путем обеспечивается упрощение программирования и построения схемы.

При этом можно, предпочтительно после сравнения всех битов байта, установить определенный бит, соотнесенный с этим байтом, в "0", если все биты были равны, и установить в "1" в противном случае. При этом особенно предпочтительно, если со стороны процессора можно обращаться к упомянутым соотнесенным битам побайтно. Путем маскирования информации сравнения можно с высоким быстродействием и простотой оценить вновь принимаемую последовательность битов.

Предпочтительным образом процессор может при этом по время передачи данных переключиться в экономичный режим потребления тока (неактивный или дежурный режим). При этом особенно предпочтительным является то, что при наступлении переполнения ЗУ процессор активизируется.

Вместо требующего относительно высоких затрат сравнения отдельных битов можно также предусмотреть автоматическое сравнение данных, при котором автоматически сравнивается контрольная сумма принимаемых данных с предварительно вычисленной контрольной суммой ожидаемых данных.

Таким путем процессор может быть дополнительно разгружен за счет того, что сравнение, например, серийного номера бесконтактной карты с микросхемой может производиться автоматически, без поддержки процессором, во время приема данных.

Для предлагаемого изобретения могут быть разработаны протоколы, которые обеспечивают передачу долей байта (например, только 3 битов).

До сих пор не было известно ни применение ЗУ емкостью в несколько слов в последовательном интерфейсе карт с микросхемами, ни применение таких автоматических схем и способов сравнения в комбинации с процессорами.

Изобретение описывается ниже на примерах осуществления, иллюстрируемых чертежами, на которых представлено следующее:

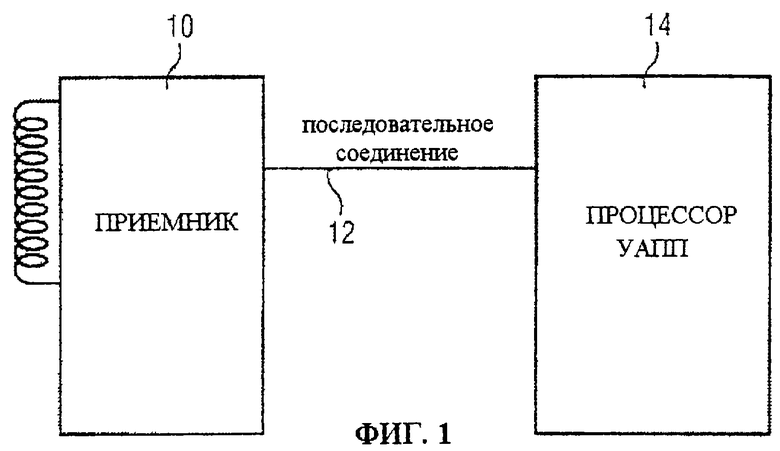

фиг. 1 - решение, соответствующее уровню техники, состоящее в последовательной передаче между модулем приема и модулем процессора,

фиг.2 - решение, соответствующее уровню техники, состоящее в подключении модуля приема к шине процессора,

фиг.3 - решение, соответствующее изобретению, предусматривающее последовательную передачу данных между модулем приема и модулем процессора,

фиг.4 - решение, соответствующее изобретению, предусматривающее подключение модуля приема к шине процессора,

фиг.5 - соответствующее изобретению ЗУ обратного магазинного типа (FiFo) со схемой сравнения для проверки правильности ожидаемых данных,

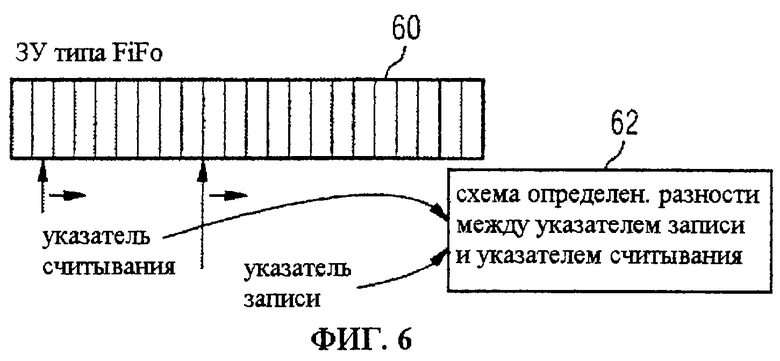

фиг. 6 - принципиальное представление ЗУ обратного магазинного типа (FiFo),

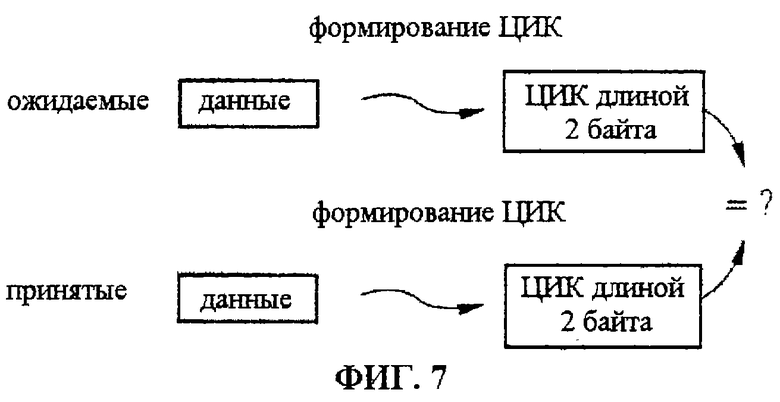

фиг. 7 - соответствующее изобретению сравнение данных посредством формирования контрольной суммы,

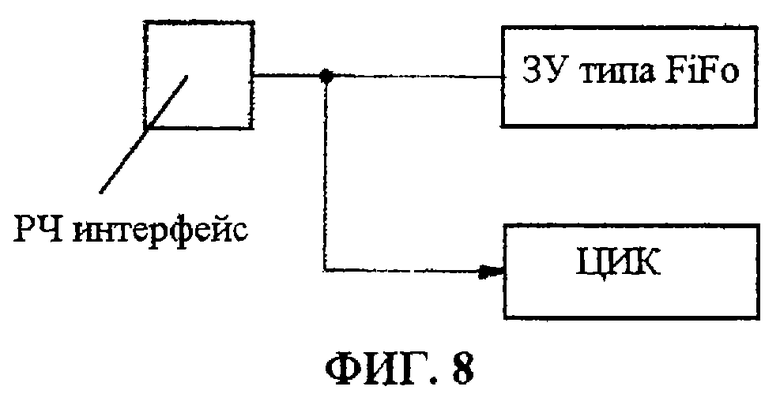

фиг. 8 - формирование контрольной суммы параллельно к загрузке данных в ЗУ обратного магазинного типа (FiFo).

Фиг. 1 и 2 иллюстрируют проблемы, свойственные предшествующему уровню техники. Приемник 10 через свое последовательное соединение 12 может соединяться с модулем 14 процессора, в котором в этом случае еще предусматривается схема Универсального асинхронного приемопередатчика (УАПП). Другое решение, соответствующее предшествующему уровню техники, предусматривает модуль приемника 20, который сам содержит схему УАПП, и в этом случае шина данных 22 процессора 24 соединяется с ним.

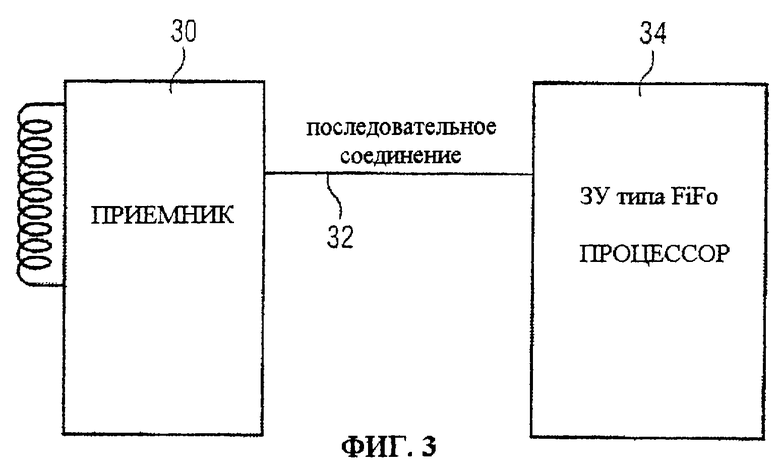

На фиг.3 и 4 представлено решение, соответствующее изобретению. На фиг.3 представлен модуль 30 приемника с последовательным интерфейсом. Через последовательное соединение 32 модуль 30 приемника соединяется с модулем 34 процессора. Однако вместо схемы УАПП в модуле 34 процессора предусмотрено запоминающее устройство обратного магазинного типа, действующее в порядке поступления данных по принципу "первым пришел - первым обслужен" (ЗУ типа FiFo). Таким образом, вместо схемы УАПП применяется структура FiFo, например, с 32 байтами. При этом в случае приема данных, данные побитно записываются в ЗУ обратного магазинного типа. Как только один байт заполнен, в ЗУ обратного магазинного типа автоматически побитно заполняется следующий байт, пока блок данных не дойдет до конца. Передача происходит аналогично приему, т. е. данные считываются побитно из ЗУ обратного магазинного типа, байт за байтом. Как процесс приема, так и процесс передачи может осуществляться независимо от процессора. Предпочтительно процессор может при этом находиться в неактивном или дежурном режиме (т.е. в режиме экономии тока с пренебрежимо малым потреблением тока). Процессор может побайтно последовательно считывать содержимое ЗУ обратного магазинного типа и соответственно побайтно записывать в него последовательные данные. С помощью указателя записи и указателя считывания можно каждый бит в ЗУ обратного магазинного типа адресовать отдельно. Тем самым можно передать или принять и неполные байты, например, только 3 бита. В то же время требования к возможностям обработки процессора в реальном времени существенно ниже, чем в случае решения, соответствующего предшествующему уровню техники со схемой УАПП.

Альтернативно ЗУ обратного магазинного типа может также применяться ЗУ магазинного типа, действующее по принципу "последним пришел - первым обслужен" (ЗУ типа LiFo). При этом порядок следования принимаемых и передаваемых данных является обратным. Это может приниматься во внимание при программировании и даже оказаться желательньм. Следующие формы выполнения можно применять, разумеется, аналогично для ЗУ типа LiFo.

ЗУ обратного магазинного типа (FiFo) в предлагаемой форме выполнения по фиг.3 интегрируется в модуле процессора. ЗУ обратного магазинного типа может при этом быть реализовано даже с использованием ячеек ОЗУ из обычного рабочего ОЗУ в адресной области процессора (например, во внутреннем ОЗУ). Для этого не требуются дополнительные схемы ЗУ.

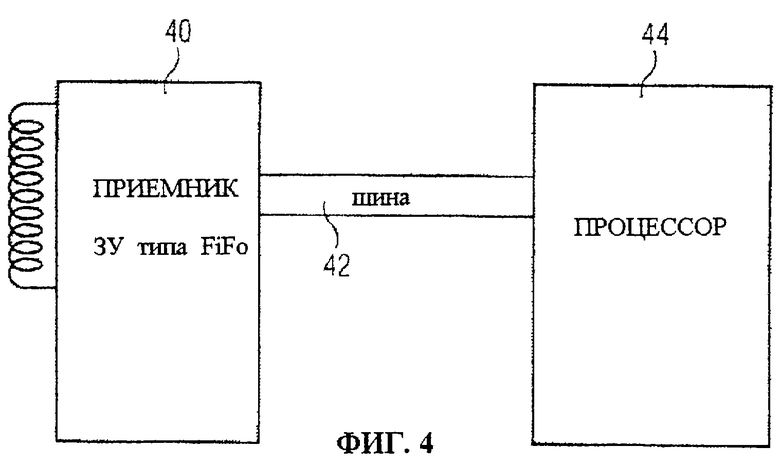

На фиг.4 представлен еще один вариант осуществления изобретения. При этом ЗУ обратного магазинного типа интегрирован в модуле 40 приемника. Последний связан посредством шины 42 процессора с модулем 44 процессора.

Как в форме выполнения изобретения по фиг.3, так и в форме выполнения по фиг. 4 можно предусмотреть, что в ЗУ обратного магазинного типа может осуществляться запись и считывание от процессора только последовательно. Свободный по выбору доступ процессора к ЗУ обратного магазинного типа тем самым исключается. Это существенным образом способствует повышению защищенности данных, если необходимо воспрепятствовать попыткам одного приложения путем манипулирования изменить данные другого приложения.

Существенно более гибкое программирование, однако, возможно, если процессор может свободно устанавливать указатель записи и указатель считывания ЗУ обратного магазинного типа. Тем самым можно оказывать влияние на то, в какой позиции (для какого именно бита) процессор осуществляет параллельное считывание или соответственно запись, а также на то, в какой позиции (для какого именно бита) беспроводный интерфейс осуществляет последовательную запись или считывание.

Дополнительное повышение гибкости доступа обеспечивается тем, что процессор рассматривает отдельные биты ЗУ обратного магазинного типа в качестве составных частей своей логической области адресации и может записывать или соответственно считывать их свободно по выбору и независимо от указателя записи и указателя считывания. Это решение особенно пригодно во взаимосвязи с реализацией ЗУ обратного магазинного типа посредством физических ячеек ОЗУ из обычного рабочего ЗУ процессора.

В каждой из описанных форм выполнения ЗУ обратного магазинного типа дополнительно может предусматриваться схема сравнения в ЗУ обратного магазинного типа или автоматическая проверка контрольной суммы.

Дополнительно к ЗУ обратного магазинного типа, может также предусматриваться схема УАПП, соответствующая предшествующему уровню техники, чтобы, например, иметь возможность обработки протоколов большой длины (в случае ЗУ обратного магазинного типа на 32 байта, например, протокол длиной 40 байтов).

Особенно предпочтительным является конфигурирование ЗУ обратного магазинного типа в виде кольцевой структуры. Тогда при наступающем переполнении ЗУ обратного магазинного типа можно активизировать процессор, чтобы осуществить обработку этих данных из ЗУ обратного магазинного типа.

В случае необходимости ЗУ обратного магазинного типа может приводиться в действие как классическая схема УАПП, соответствующая предшествующему уровню техники.

ЗУ обратного магазинного типа, разумеется, может быть реализовано и с процессорами, не имеющими экономичного режима потребления тока.

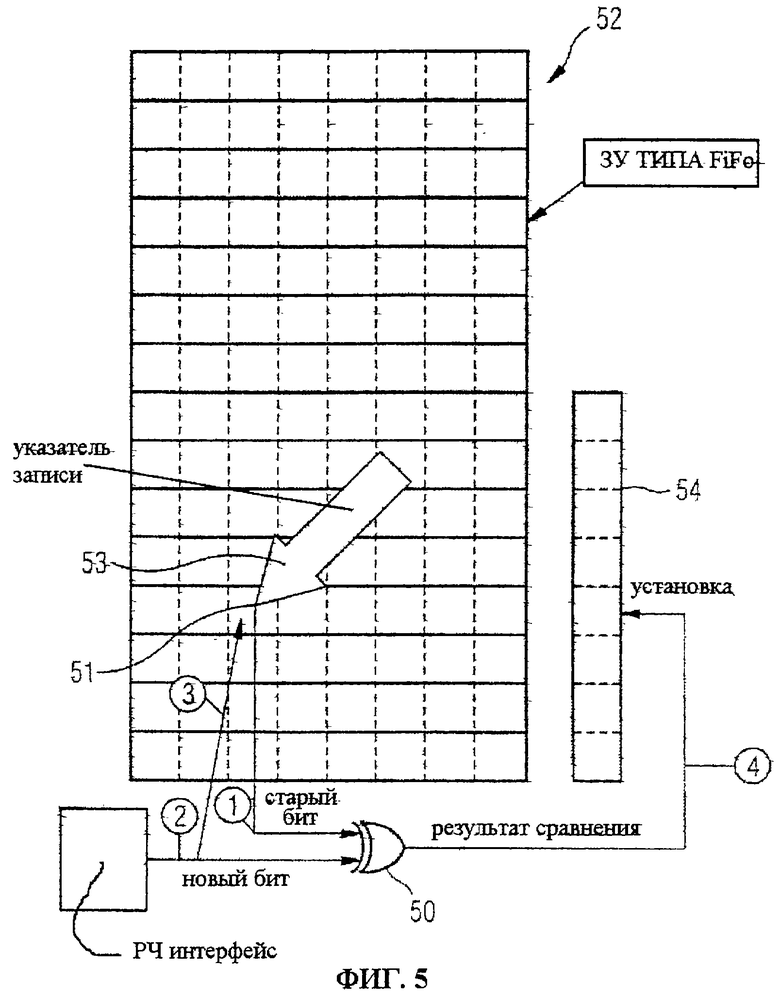

Для дополнительной разгрузки процессора в схеме интерфейса может быть реализован автоматический блок сравнения. Тем самым процессор освобождается от задачи сравнения принимаемых данных с ожидаемыми данными (например, для аутентификации). В соответствии с изобретением эти задачи решаются с помощью ЗУ обратного магазинного типа с встроенным блоком сравнения, как показано на фиг.5. Тем самым можно дополнительно снизить требования к производительности процессора и, следовательно, его потребление тока. В любом случае также возможно использовать более экономичный процессор.

Показанная на фиг. 5 схема сравнения требует использования ожидаемых данных, например, серийного номера или пароля в ЗУ обратного магазинного типа. Простая логическая схема 50 автоматически сравнивает каждый принятый бит (новый бит, 2) с содержимым ячейки 41 памяти в ЗУ обратного магазинного типа 52, на место которого этот принятый бит должен быть записан. Тем самым указатель записи 53 служит как для адресации ожидаемого бита (1), с которым должно осуществляться сравнение, так и для адресации позиции записи принимаемого бита (2), который в данный момент должен записываться в ЗУ обратного магазинного типа (--> 3). Новые биты при этом выдаются с радиочастотного интерфейса приемопередающего блока.

После того как проведено сравнение всех битов байта и они записаны в ЗУ 52 обратного магазинного типа, и если все биты были равны, то соотнесенный с этим байтом бит в специальном регистре 54 сравнения устанавливается в "0", а в противном случае он устанавливается в "1". Функция при этом состоит в том, что регистр 54 перед началом операции сравнения устанавливается в "0", а логическая схема 50, как только возникает состояние "старый бит ≠ новый бит", устанавливает в "1" соответствующую ячейку памяти регистра 54 в "1". Затем осуществляется побитовая обработка следующего байта, пока весь блок данных не будет обработан. За счет маскирования информации сравнения можно просто и с высоким быстродействием оценить новую принятую последовательность битов.

Эта схема сравнения может в общем случае применяться и в связи со схемой УАПП, соответствующей предшествующему уровню техники. Таким путем можно также реализовать автоматическое сравнение без использования ЗУ обратного магазинного типа.

Принцип функционирования ЗУ обратного магазинного типа представлен на фиг. 6. ЗУ обратного магазинного типа состоит из ряда ячеек памяти, которые циклически адресуются указателем считывания и указателем записи. При записи в ЗУ обратного магазинного типа подлежащее записи слово записывается в позиции, на которую указывает указатель записи, при этом указатель записи получает приращение на одну позицию. При считывании проверяется, не равен ли указатель записи указателю считывания. После того как слово считывается из ячейки памяти, на которую указывает указатель считывания, указатель считывания получает приращение. Если указатель записи равен указателю считывания, то ЗУ типа обратного магазинного типа (FiFo) является пустым. Это устанавливается посредством соответствующей схемы 62 определения разности. Затем либо выдается значение "0", либо сообщение, что считывание невозможно. Так как схема 62 определения разности таким образом постоянно указывает число битов в ЗУ обратного магазинного типа, то эта схема может также применяться, чтобы перед переполнением ЗУ обратного магазинного типа активизировать процессор и запустить обработку данных, чтобы тем самым вновь создать свободное место в ЗУ обратного магазинного типа.

Еще одна возможность для сравнения данных в соответствии с изобретением состоит в автоматическом определении контрольной суммы принимаемых данных, например, согласно способу проверки с использованием циклического избыточного кода (ЦИК), которая сравнивается с контрольной суммой ожидаемых данных, вычисленной предварительно (например, во время инициализации). Этот способ, однако, не так эффективен, как иллюстрируемый с помощью фиг.5, предусматривающий сравнение в ЗУ обратного магазинного типа, так как должны сравниваться контрольные суммы принимаемых данных и ожидаемых данных от процессора. Это, следовательно, вновь приводит к дополнительной нагрузке процессора. Кроме того, должна иметься по крайней мере одна битовая ошибка на блок данных, чтобы последний можно было надежно распознать. Кроме того, соответствующая логическая схема должна обеспечивать различение между данными и командами, так как в противном случае контрольная сумма принимаемых данных при определенных обстоятельствах будет сформирована по командам иным, чем в случае формирования контрольной суммы ожидаемых данных. Это поясняется ниже со ссылками на фиг.7 и 8 следующим образом.

Из ожидаемых данных вычисляется контрольная суммам ЦИК. Она состоит из двух байтов. После этого из принимаемых данных также формируется контрольная сумма в соответствии со способом ЦИК. В этом случае должны сравниваться только контрольные суммы проверки ЦИК длиной 2 байта, а не все данные. Сравнение этих коротких контрольных сумм проверки ЦИК из двух байтов обладает существенно более высоким быстродействием, чем сравнение всех данных. Контрольная сумма ожидаемых данных может быть рассчитана уже заранее. Как показано на фиг.8, существует также возможность вводить принимаемые данные одновременно в ЗУ обратного магазинного типа и в логическую схему проверки контрольной суммы. Это позволяет формировать контрольные суммы в реальном времени, так что процессор должен проводить в реальном времени только сравнение контрольных сумм, требующее малого времени вычислений.

Таким способом можно, путем добавления ЗУ обратного магазинного типа, а также в необходимом случае устройства сравнения или генератора контрольной суммы, который автоматически формирует контрольную сумму для принимаемых данных, существенным образом разгрузить процессор, по сравнению с известным принципом, лежащим в основе использования УАПП. Тем самым можно существенно снизить частоту и потребление тока процессора. Более низкое потребление тока означает в случае бесконтактных карт с микросхемами, в частности, большие дальности действия.

Особенно предпочтительным в данном случае является то, что процессор во время передачи, приема и других операций, в которых он не участвует, может быть переведен в экономичный режим потребления тока. Процессор может, например, после того как он завершил подготовку к передаче/приему, переключиться в экономичный режим потребления тока и оставаться в этом режиме до завершения передачи/приема. Обычно требуемая для процессора энергия может быть сэкономлена или предоставлена в распоряжение для аппаратных средств передачи и соответственно приема. Кроме того, в режиме передачи и соответственно приема на передаваемый беспроводным способом сигнал не накладываются никакие пики питающей энергии от процессора. Более низкое потребление тока и более эффективное распределение энергии на карте с микросхемой, а также более благоприятный режим для передаваемого сигнала обеспечивают увеличение дальности действия.

Кроме того, функция передачи может инициироваться с управлением по времени, когда процессор находится в экономичном режиме потребления тока. Дополнительно может быть реализована функция автоматического приема. При этом в течение экономичного режима потребления тока процессора после передачи можно автоматически осуществлять переключение в режим приема, исключая необходимость активизации процессора.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕТЕВОЙ ИНТЕРФЕЙС | 2014 |

|

RU2686016C2 |

| АБОНЕНТСКИЙ ПУНКТ В СИСТЕМЕ БЕСПРОВОДНОЙ ЦИФРОВОЙ ТЕЛЕФОННОЙ СВЯЗИ | 1990 |

|

RU2154360C2 |

| Интерфейс передачи данных | 2018 |

|

RU2682435C1 |

| АБОНЕНТСКИЙ ПУНКТ В АБОНЕНТСКОЙ СИСТЕМЕ БЕСПРОВОДНОЙ СВЯЗИ | 1990 |

|

RU2138122C1 |

| СИНХРОННО-АСИНХРОННЫЙ И АСИНХРОННО-СИНХРОННЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2097929C1 |

| КОНТРОЛЛЕР СВЯЗИ С ПОМОЩЬЮ ИНФРАКРАСНОГО НАПРАВЛЕННОГО ИЗЛУЧЕНИЯ С МНОЖЕСТВОМ ПРОТОКОЛОВ | 1995 |

|

RU2126593C1 |

| СПОСОБ ОБРАБОТКИ СИГНАЛОВ СВЯЗИ В АБОНЕНТСКОМ ПУНКТЕ БЕСПРОВОДНОЙ СИСТЕМЫ ЭЛЕКТРОСВЯЗИ | 1990 |

|

RU2159007C2 |

| ИНТЕРФЕЙС ТРАНСПОРТНОГО ПРОЦЕССОРА ДЛЯ ЦИФРОВОЙ ТЕЛЕВИЗИОННОЙ СИСТЕМЫ | 1995 |

|

RU2144742C1 |

| СПОСОБ ОБЕСПЕЧЕНИЯ ПЕРЕДАЧИ ИНФОРМАЦИИ МЕЖДУ ЭЛЕКТРОННЫМ УСТРОЙСТВОМ И АККУМУЛЯТОРОМ, УСТРОЙСТВО, СОДЕРЖАЩЕЕ ЭЛЕКТРОННОЕ УСТРОЙСТВО И АККУМУЛЯТОР, И АККУМУЛЯТОР, ОБЕСПЕЧИВАЮЩИЙ ПЕРЕДАЧУ ИНФОРМАЦИИ | 2000 |

|

RU2245576C2 |

| УСТРОЙСТВО И СПОСОБ КОММУТАЦИИ ДЛЯ АСИНХРОННОГО РЕЖИМА ПЕРЕДАЧИ | 1998 |

|

RU2233036C2 |

Изобретение относится к вычислительной технике, в частности к схемам интерфейса. Техническим результатом является создание способа и схемы, обеспечивающих передачу данных между последовательным интерфейсом и процессором без нагрузки процессора. Для этого в схеме интерфейса между последовательным интерфейсом и процессором включено запоминающее устройство (ЗУ). Согласно способу данные принимаются побитно последовательно и считываются в ЗУ, а оттуда считываются процессором побайтно, или соответственно процессором побайтно записываются в ЗУ и оттуда побитно передаются. 2 с. и 21 з.п. ф-лы, 8 ил.

| СЧИТЫВАТЕЛЬ ФИЛЬМОВ К КОДОВОМУ ТЕОДОЛИТУ | 0 |

|

SU290172A1 |

| ЖИГАРЕВ А.Н | |||

| и др | |||

| Основы компьютерной грамоты | |||

| - Л.: Машиностроение, 1987, с.66-68, первый абзац | |||

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1989 |

|

RU2047920C1 |

| ПОТЕМКИН И.С | |||

| Функциональные узлы цифровой автоматики | |||

| - М.: Энергоатомиздат, 1988, с.211 | |||

| КАГАН Б.М | |||

| Электронные вычислительные машины и системы | |||

| - М.: Энергоатомиздат, 1981, с.108, последний абзац, с.109, третий абзац | |||

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

Авторы

Даты

2004-02-27—Публикация

1999-08-05—Подача