Изобретение относится к импульсной технике и может быть использовано для формирования импульсов управления на диодной нагрузке.

Известен интегральный формирователь на однотипных транзисторах, содержащий фазорасщепитель и двухтактный выходной каскад, верхнее плечо которого выполнено на составном транзисторе [1].

Однако это устройство не обеспечивает необходимую амплитуду и симметрию выходных импульсов относительно шин питания из-за повышенного остаточного напряжения на составном транзисторе верхнего плеча двухтактного выходного каскада, а также имеет повышенные потери мощности в динамическом режиме вследствие протекания сквозных токов.

Наиболее близким к изобретению по технической сущности является интегральный формирователь, содержащий первый и второй транзисторы n-р-n типа, эмиттер первого транзистора соединен с первой шиной питания, а коллектор соединен с эмиттером и базой второго транзистора соответственно через первый и второй диоды в прямом включении, коллектор второго транзистора соединен с второй шиной питания, его эмиттер соединен с выходной шиной, а база через первый токозадающий элемент соединена с второй шиной питания [2].

Однако известный формирователь характеризуется большой потребляемой мощностью и невысоким быстродействием из-за ограниченного усиления выходных транзисторов.

Целью изобретения является повышение быстродействия при одновременном снижении потребляемой мощности и обеспечение симметрии выходных импульсов.

Поставленная цель достигается тем, что в известный интегральный формирователь, содержащий первый и второй транзисторы n-р-n типа, эмиттер первого транзистора соединен с первой шиной питания, а коллектор соединен с эмиттером и базой второго транзистора соответственно через первый и второй диоды в прямом включении, коллектор второго транзистора соединен с второй шиной питания, его эмиттер соединен с выходной шиной, а база через первый токозадающий элемент соединена с второй шиной питания, введены третий и четвертый транзисторы n-р-n типа и второй токозадающий элемент, база третьего транзистора соединена с входной шиной, эмиттер подключен к базе первого транзистора, а коллектор соединен с базой четвертого транзистора и через второй токозадающий элемент подключен к второй шине питания, эмиттер четвертого транзистора соединен с базой второго транзистора, а коллектор - с второй шиной питания (при этом первый и второй токозадающие элементы выполнены на транзисторах р-n-р типа).

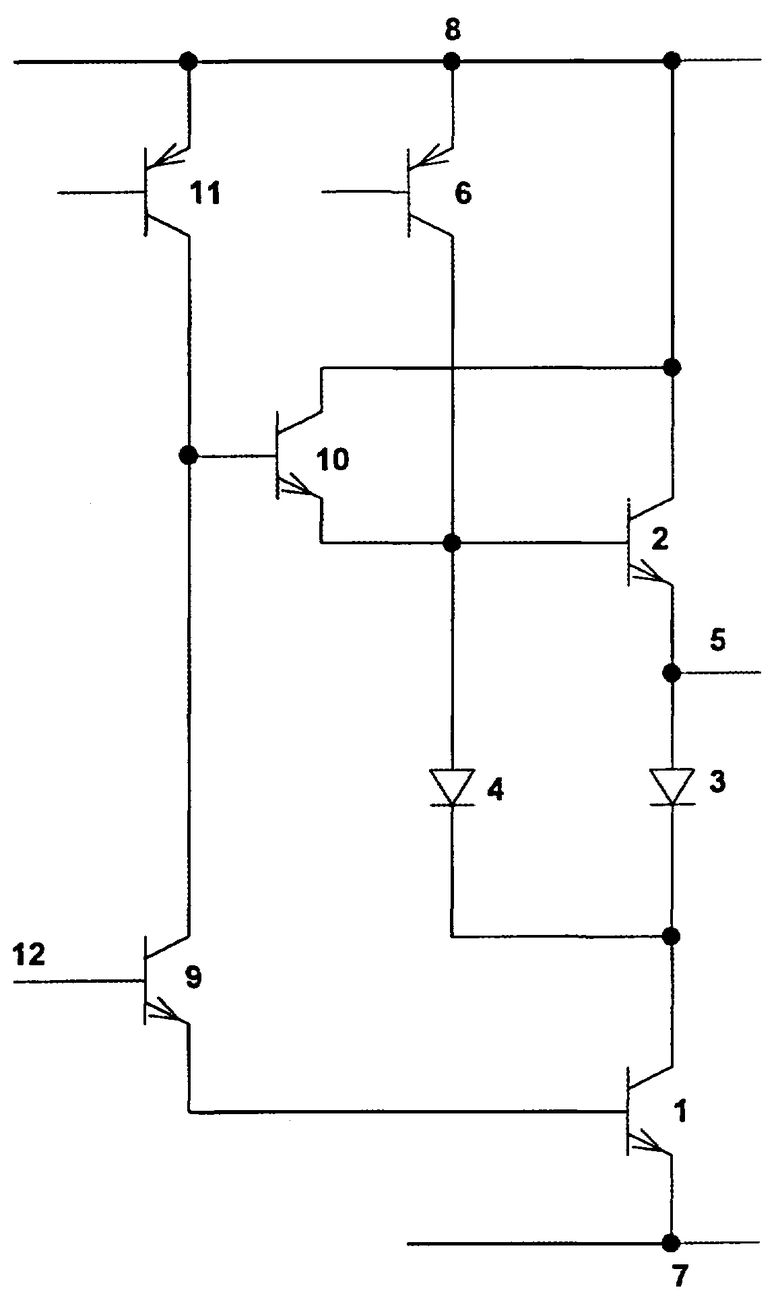

На чертеже представлена принципиальная электрическая схема предлагаемого интегрального формирователя.

Интегральный формирователь содержит первый и второй транзисторы 1 и 2 n-p-n типа, первый и второй диоды 3 и 4, выходную шину 5, первый токозадающий элемент 6, первую шину 7 питания, вторую шину 8 питания, третий и четвертый транзисторы 9 и 10 n-p-n типа, второй токозадающий элемент 11 и входную шину 12.

Интегральный формирователь работает следующим образом. При наличии на входной шине 12 сигнала высокого уровня первый и третий транзисторы 1 и 9 открыты и насыщены. Ток нагрузки протекает через прямосмещенный первый диод 3 и насыщенный первый транзистор 1. Ток от первого токозадающего элемента 6 протекает через второй диод 4 и через первый транзистор 1. Легко заметить, что второй и четвертый транзисторы 2 и 10 закрыты, поскольку смещения на их эмиттерных переходах примерно нулевые, т.е. ниже порога их отпирания. Уровень напряжения на выходной шине 5 определяется напряжением на первой шине 7 питания за вычетом напряжения насыщения коллектор-эмиттер первого транзистора 1 и напряжения на прямосмещенном первом диоде 3.

Запирающий сигнал на входной шине 12 интегрального формирователя приводит к запиранию первого и третьего транзисторов 1 и 9. Токи от первого и второго токозадающих элементов 6 и 11 начинают повышать потенциалы на базах второго и четвертого транзисторов 2, 10, причем скорость изменения потенциалов определяется силой тока токозадающего элемента и эквивалентной емкостью соответствующего узла по отношению к шинам питания. Второй транзистор 2 является выходным, рассчитан на сравнительно большой рабочий ток, поэтому очевидно, что эквивалентная емкость, приведенная к базе второго транзистора 2, значительно превышает емкость, приведенную к базе четвертого транзистора 10, рассчитанного на относительно малый рабочий ток. Вследствие этого четвертый и второй транзисторы 10 и 2 на этапе формирования положительного перепада напряжения на выходе работают как составной транзистор, более высокая крутизна которого (по сравнению с одиночным транзистором в прототипе) позволяет повысить быстродействие при заданном уровне потребляемой мощности. На заключительном этапе формирования выходного напряжения высокого уровня четвертый транзистор 10 запирается, и ток нагрузки определяется уже одиночным выходным транзистором - вторым транзистором 2. Установившееся значение напряжения высокого уровня на выходной шине 5 определяется напряжением на второй шине 8 питания за вычетом падения напряжения на первом токозадающем элементе 6 (в рассматриваемом примере реализации - это напряжение коллектор-эмиттер насыщения р-n-р транзистора) и на прямосмещенном эмиттерном переходе второго транзистора 2, то есть обеспечивается симметрия выходных сигналов относительно напряжений на шинах питания.

При подаче на входную шину 12 формирователя отпирающего сигнала потенциал на базе четвертого транзистора 10 снижается быстрее, чем потенциал на базе второго транзистора 2 (за счет соответствующего выбора режимных токов в формирователе). В результате четвертый транзистор 10 на стадии формирования отрицательного перепада напряжения на выходной шине 5 оказывается в режиме отсечки. Второй транзистор 2 также выключен, поскольку работает при нулевом смещении эмиттерного перехода. Таким образом, сквозной ток в двухтактном выходном каскаде формирователя не возникает, что обеспечивает максимальное быстродействие (ресурс активных элементов не тратится на бесполезные сквозные токи) и минимальную потребляемую мощность.

Новизна предлагаемого изобретения заключается в том, что в интегральный формирователь введены дополнительные элементы, обеспечивающие формирование положительного перепада напряжения в два этапа: 1) ускоренное нарастание за счет каскадного соединения второго и четвертого транзисторов и 2) дополнительное увеличение выходного уровня напряжения после выключения четвертого транзистора вторым транзистором и первым токозадающим элементом. За счет соответствующих связей, а также за счет выполнения токозадающих элементов на р-n-р транзисторах в предложенном формирователе достигается повышение быстродействия, сопоставимое со схемой на составных транзисторах, исключены сквозные токи и обеспечивается высокая степень симметрии выходных импульсов.

Технический результат изобретения реализуется лишь при совокупном использовании его отличительных признаков.

Неочевидность предлагаемого изобретения можно проиллюстрировать тем, что, например, реализация первого и второго транзисторов в прототипе в виде составных транзисторов хотя и позволяет повысить быстродействие, но уменьшает амплитуду выходных импульсов за счет большего (по сравнению с одиночными транзисторами) остаточного напряжения коллектор-эмиттер у составных транзисторов. По сути, предложение сводится к тому, что в известное техническое решение (прототип), в котором фазировка плеч двухтактного выходного каскада уже обеспечена, введен дополнительный каскад в виде фазорасщепителя. Именно это в совокупности с выполнением токозадающих элементов на р-n-р транзисторах и позволило решить задачу, а именно: повысить быстродействие при заданной потребляемой мощности, исключить сквозные токи, обеспечить высокую степень симметрии выходных импульсов и максимальный коэффициент использования напряжений источников питания.

Источники информации

1. Аналоговые и цифровые интегральные схемы. С.В. Якубовский, Н.А. Барканов, Б.П. Кудряшов и др. /Под ред. С.В. Якубовского. - М.: Сов. радио, 1979, с.59, рис. 3.8.

2. Гребен А.Б. Проектирование аналоговых интегральных схем. Пер. с англ. - М.: Энергия, 1976, с.131, рис. 6-7, б.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНАЯ СХЕМА ЗАДЕРЖКИ ВКЛЮЧЕНИЯ | 2014 |

|

RU2547616C1 |

| Формирователь импульсов (его варианты) | 1980 |

|

SU974562A1 |

| Формирователь импульсов управления | 1987 |

|

SU1522387A2 |

| Дифференциальный усилитель | 1988 |

|

SU1569942A1 |

| Логический вентиль | 1980 |

|

SU940308A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Динамический логический элемент | 1979 |

|

SU822370A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2005 |

|

RU2287219C1 |

| Формирователь импульсов | 1987 |

|

SU1614104A1 |

| ИНТЕГРАЛЬНЫЙ ФОРМИРОВАТЕЛЬ | 2011 |

|

RU2474044C1 |

Изобретение относится к импульсной технике для формирования импульсов управления на диодной нагрузке. Технический результат заключается в повышении быстродействия при снижении потребляемой мощности и симметрии выходных ипульсов. Интегральный формирователь содержит первый и второй транзисторы (Т) (1) и (2) n-p-n типа, эмиттер Т (1) соединен с первой шиной питания (ШП) (7), а коллектор соединен с эмиттером и базой Т (2) соответственно через первый и второй диоды (3) и (4) в прямом включении, коллектор Т (2) соединен с ШП (8), его эмиттер соединен с выходной шиной, а база через первый токозадающий элемент (ТЭ) (6) соединена с ШП (8). Введены третий и четвертый Т (9) и (10) n-p-n типа и второй ТЭ (11), база Т (9) соединена с входной шиной, эмиттер подключен к базе Т (1), а коллектор соединен с базой Т (10) и через второй ТЭ (11) подключен к ШП (8), эмиттер Т (10) соединен с базой Т (2), а коллектор - с ШП (8). При этом первый и второй ТЭ (6) и (11) выполнены на Т р-n-р типа. 1 ил.

Интегральный формирователь, содержащий первый и второй транзисторы n-р-n типа, эмиттер первого транзистора соединен с первой шиной питания, а коллектор соединен с эмиттером и базой второго транзистора соответственно через первый и второй диоды в прямом включении, коллектор второго транзистора соединен со второй шиной питания, его эмиттер соединен с выходной шиной, а база через первый токозадающий элемент соединена со второй шиной питания, отличающийся тем, что введены третий и четвертый транзисторы n-р-n типа и второй токозадающий элемент, база третьего транзистора соединена с входной шиной, эмиттер подключен к базе первого транзистора, а коллектор соединен с базой четвертого транзистора и через второй токозадающий элемент подключен ко второй шине питания, эмиттер четвертого транзистора соединен с базой второго транзистора, а коллектор - со второй шиной питания, при этом первый и второй токозадающие элементы выполнены на транзисторах р-n-р типа.

| US 4442409, 10.04.1984 | |||

| УСИЛИТЕЛЬ МОЩНОСТИ | 1972 |

|

SU434564A1 |

| GB 1091434, 15.11.1967 | |||

| US 3573645, 06.04.1971 | |||

| ГРЕБЕН А.Б | |||

| Проектированное аналоговых интегральных схем | |||

| - М.: Энергия, 1976, с.131, рис | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| БЕЗЛАДНОВ И.Л | |||

| и др | |||

| Проектирование транзисторных усилителей звуковых частот | |||

| /Под ред | |||

| Н.Л.Безладнова | |||

| - М.: Связь, 1978, с.197, рис | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

2004-06-27—Публикация

2002-07-30—Подача