Предлагаемое изобретение относится к импульсной технике и может быть использовано для формирования импульсов управления на емкостной и на диодной нагрузке.

Известен интегральный формирователь на однотипных транзисторах, содержащий фазорасщепитель и двухтактный выходной каскад, верхнее плечо которого выполнено на составном транзисторе [1].

Однако это устройство характеризуется недостаточным выходным напряжением высокого уровня из-за повышенного остаточного напряжения на составном транзисторе верхнего плеча двухтактного выходного каскада.

Наиболее близким к предлагаемому изобретению по технической сущности является интегральный формирователь, содержащий предварительный каскад, первый выход которого соединен с базой выходного транзистора нижнего плеча двухтактного выходного каскада, второй выход предварительного каскада соединен с выходом первого источника тока и с базой первого транзистора n-p-n типа, эмиттер которого соединен с выходом второго источника тока и с базой второго транзистора n-p-n типа, при этом первый и второй транзисторы являются составным выходным транзистором верхнего плеча двухтактного выходного каскада, коллекторы первого и второго транзисторов соединены с положительной шиной источника питания, эмиттер второго транзистора соединен с соответствующим выводом выходного транзистора и с выходной шиной формирователя импульсов [2].

Однако известный формирователь имеет повышенную потребляемую мощность из-за наличия второго источника тока, который обеспечивает увеличение выходного напряжения высокого уровня.

Техническим результатом предлагаемого изобретения является снижение потребляемой мощности.

Технический результат достигается тем, что в известном интегральном формирователе, содержащем предварительный каскад, первый выход которого соединен с базой выходного транзистора нижнего плеча двухтактного выходного каскада, второй выход предварительного каскада соединен с выходом первого источника тока и с базой первого транзистора n-p-n типа, эмиттер которого соединен с выходом второго источника тока и с базой второго транзистора n-p-n типа, при этом первый и второй транзисторы являются составным выходным транзистором верхнего плеча двухтактного выходного каскада, коллекторы первого и второго транзисторов соединены с положительной шиной источника питания, эмиттер второго транзистора соединен с соответствующим выводом выходного транзистора и с выходной шиной формирователя импульсов, первый источник тока выполнен на латеральном транзисторе p-n-p типа, при этом коллектор латерального транзистора является выходом первого источника тока, а выходом второго источника тока является дополнительная область p-типа, расположенная внутри изолированного n-кармана латерального транзистора между его коллектором и границей изолирующей p-области данного n-кармана.

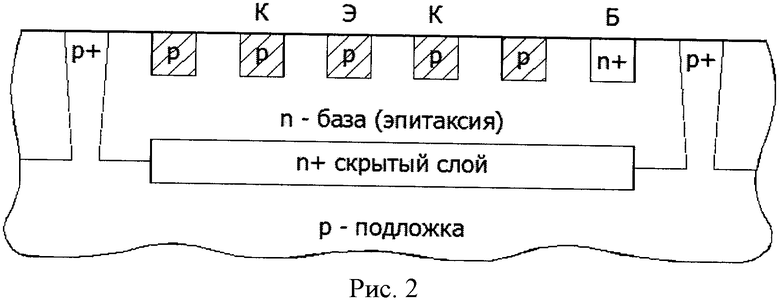

На рис.1 представлена принципиальная электрическая схема предлагаемого интегрального формирователя.

Интегральный формирователь содержит предварительный каскад 1, выходной транзистор 2 нижнего плеча двухтактного выходного каскада, первый источник 3 тока, первый транзистор 4 n-p-n типа, второй источник 5 тока, второй транзистор 6 n-p-n типа, первый и второй транзисторы 4 и 6 образуют составной выходной транзистор 7 верхнего плеча двухтактного выходного каскада.

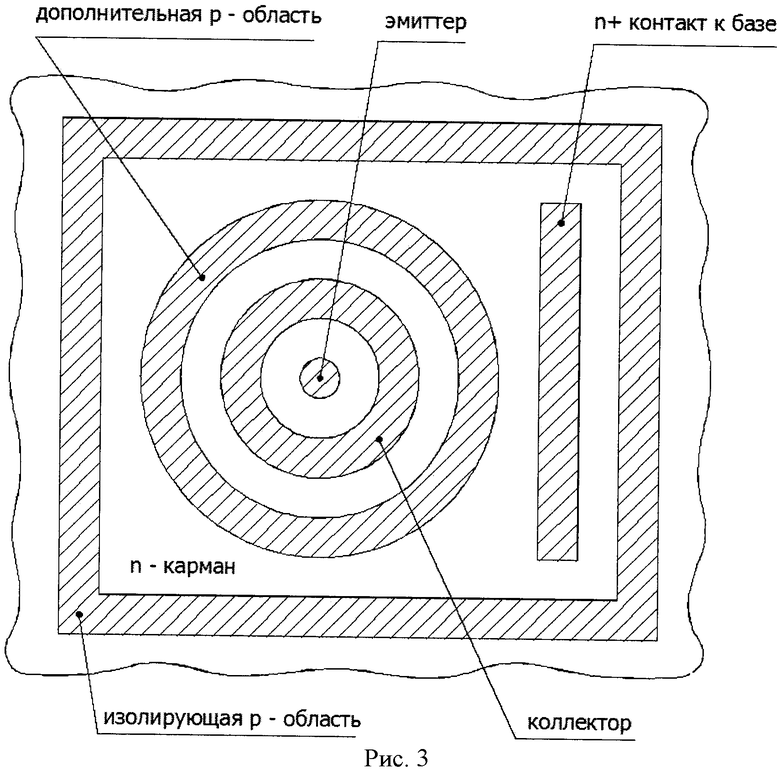

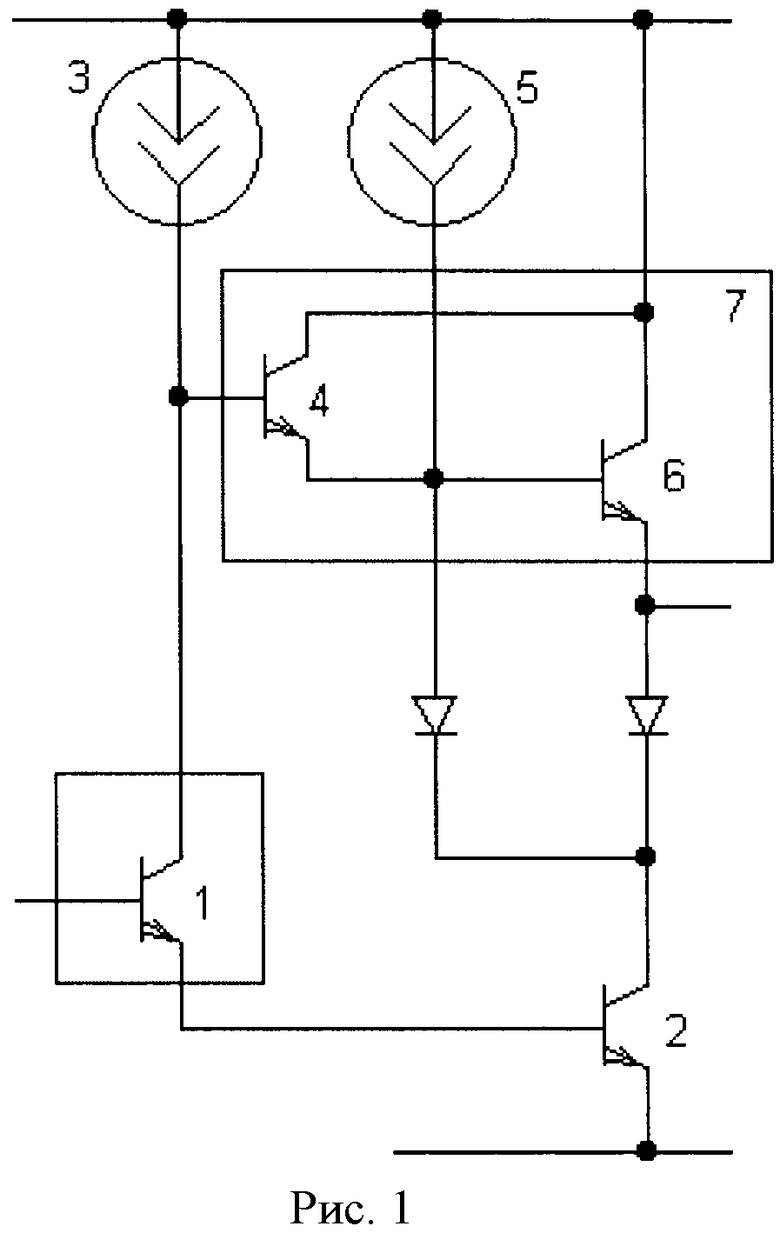

На рис.2 и рис.3 представлена конструкция первого и второго источников тока.

Вся конструкция расположена внутри n-кармана, изолированного от p-подложки и от соседних областей полупроводникового кристалла изолирующими p-n переходами. Конструкция включает n+-скрытый слой, n+-область для подключения базового контакта, n-эпитаксиальную область, выполняющую роль базовой области латеральной структуры, p-область эмиттера, p-область коллектора, например, в виде кольца и дополнительную p-область, окружающую p-область коллектора.

Интегральный формирователь работает следующим образом. При наличии отпирающего сигнала на входе предварительного каскада 1 составной выходной транзистор 7 верхнего плеча закрыт, а выходной транзистор 2 нижнего плеча насыщен. На выходе интегрального формирователя действует напряжение низкого уровня. Латеральный транзистор, на котором выполнен первый источник тока 3, работает в активном режиме, т.е. его эмиттерный переход смещен прямо, а коллекторный переход - обратно. Выходной ток первого источника тока 3 практически равен току эмиттера латерального транзистора. Дополнительная p-область смещена обратно, и ее ток практически равен нулю.

При формировании на входе предварительного каскада 1 запирающего перепада напряжения выходной транзистор 2 выключается, под действием тока первого источника тока 3 на базе первого транзистора 4 формируется положительный перепад напряжения, который передается на выход интегрального формирователя составным выходным транзистором 7, работающим в режиме повторителя напряжения. Переходный процесс на базе первого транзистора 4 завершается, когда латеральный транзистор первого источника тока 3 насыщается. При этом его коллекторный переход смещается прямо и начинает инжектировать в базовую n-область неосновные носители в направлении обратносмещенной дополнительной p-области. Неосновные носители, достигающие дополнительной p-области, захватываются электрическим полем обратно смещенного p-n перехода, и возникает электрический ток, который протекает в базу транзистора 6. Таким образом, на последнем этапе формирования положительного перепада выходного напряжения дополнительная p-область выполняет функции коллектора дополнительного латерального транзистора второго источника тока 5, эмиттером которого является коллектор латерального транзистора первого источника тока 3. Дополнительный латеральный транзистор работает в трех режимах:

1) в режиме отсечки - когда латеральный транзистор первого источника тока 3 находится в активном режиме, при этом ток второго источника тока 5 равен нулю;

2) в нормальном активном режиме - когда латеральный транзистор первого источника тока входит в насыщение; ток второго источника тока 5 в этом случае определяется током эмиттера латерального транзистора первого источника тока 3;

3) в режиме насыщения - на последнем этапе формирования выходного напряжения высокого уровня.

В итоге цепь формирования положительного перепада выходного напряжения при прочих равных условиях потребляет от источника питания такой же ток, как и в схеме аналога. При этом предложенный формирователь обеспечивает такое же выходное напряжение высокого уровня, как и прототип.

Новизна предлагаемого изобретения заключается в том, что в латеральный транзистор p-n-p типа, на котором выполнен первый источник тока, введена дополнительная область p-типа, которая является выходом второго источника тока. В результате, достигается уменьшение потребляемого тока. Действительно, при работе латерального транзистора первого источника тока в активном режиме второй источник тока выключен и ток не потребляет, а при насыщении латерального транзистора первого источника тока его коллектор, по сути, превращается в эмиттер латерального транзистора второго источника тока, функции коллектора которого выполняет дополнительная область p-типа. Предложенная конструкция источников тока обеспечивает потребление тока, соответствующее одиночному латеральному транзистору, и двухэтапный процесс заряда емкости нагрузки: сначала большим эмиттерным током составного транзистора, а на последнем этапе - эмиттерным током одиночного выходного транзистора, обеспечивая увеличение выходного напряжения высокого уровня примерно на 0,7 В, как в прототипе.

Технический результат предлагаемого изобретения реализуется лишь при совокупном использовании его отличительных признаков.

Введенная дополнительная область p-типа может рассматриваться, например, как второй коллектор в латеральном транзисторе p-n-p типа. Многоколлекторные латеральные транзисторы известны, однако, в таких транзисторах коллекторы практически равноценны, и такой транзистор, в первом приближении, может рассматриваться как ряд одноколлекторных с соответствующими параметрами. При этом потребляемая мощность будет такой же, как в прототипе. В предложенном техническом решении второй коллектор расположен по линии инжекции носителей заряда эмиттером за первым коллектором, поэтому ток второго коллектора появляется только тогда, когда первый коллектор смещается в прямом направлении, причем ток второго коллектора определяется тем же током эмиттера, что и ток первого коллектора.

Источники информации

1. Цифровые и аналоговые интегральные микросхемы: Справочник/ С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др.; Под ред. С.В.Якубовского. - М.: Радио и связь, 1990, с.35, рис.2.8.

2. Патент №2231919 (РФ). МКИ Н03К 5/02. Интегральный формирователь / П.А.Дик, А.И.Гольдшер, Ю.П.Докучаев, В.Р.Кучерский - опубл. 2004, Бюл. №18.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ ФОРМИРОВАТЕЛЬ | 2002 |

|

RU2231919C2 |

| ИНТЕГРАЛЬНАЯ СХЕМА ЗАДЕРЖКИ ВКЛЮЧЕНИЯ | 2014 |

|

RU2547616C1 |

| МОЩНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2017322C1 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2004 |

|

RU2274947C2 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Интегральный формирователь импульсов | 1987 |

|

SU1547044A1 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 1996 |

|

RU2115223C1 |

| УСИЛИТЕЛЬ МОЩНОСТИ | 1990 |

|

RU1748611C |

| МОЩНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2092969C1 |

| Устройство для преобразования входного двоичного сигнала в телеграфный сигнал | 1983 |

|

SU1125765A1 |

Предлагаемое изобретение относится к импульсной технике и может быть использовано для формирования импульсов управления на емкостной и на диодной нагрузке. Техническим результатом предлагаемого изобретения является снижение потребляемой мощности. В интегральном формирователе, содержащем предварительный каскад, первый выход которого соединен с базой выходного транзистора нижнего плеча двухтактного выходного каскада, второй выход предварительного каскада соединен с выходом первого источника тока и с базой первого транзистора n-p-n типа, эмиттер которого соединен с выходом второго источника тока и с базой второго транзистора n-p-n типа, коллекторы первого и второго транзисторов соединены с положительной шиной источника питания, эмиттер второго транзистора соединен с соответствующим выводом выходного транзистора и с выходной шиной формирователя импульсов, первый источник тока выполнен на латеральном транзисторе p-n-р типа, при этом коллектор латерального транзистора является выходом первого источника тока, а выходом второго источника тока является дополнительная область р-типа, расположенная внутри изолированного n-кармана латерального транзистора между его коллектором и границей изолирующей р-области данного n-кармана. 3 ил.

Интегральный формирователь, содержащий предварительный каскад, первый выход которого соединен с базой выходного транзистора нижнего плеча двухтактного выходного каскада, второй выход предварительного каскада соединен с выходом первого источника тока и с базой первого транзистора n-р-n-типа, эмиттер которого соединен с выходом второго источника тока и с базой второго транзистора n-p-n-типа, коллекторы первого и второго транзисторов соединены с положительной шиной источника питания, эмиттер второго транзистора соединен с соответствующим выводом выходного транзистора и с выходной шиной формирователя импульсов, отличающийся тем, что первый источник тока выполнен на латеральном транзисторе р-n-р-типа, при этом коллектор латерального транзистора является выходом первого источника тока, а выходом второго источника тока является дополнительная область р-типа, расположенная внутри изолированного n-кармана латерального транзистора между его коллектором и границей изолирующей р-области данного n-кармана.

| ИНТЕГРАЛЬНЫЙ ФОРМИРОВАТЕЛЬ | 2002 |

|

RU2231919C2 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСНОГО ТОКА | 1991 |

|

RU2074510C1 |

| Интегральный формирователь импульсов | 1987 |

|

SU1547044A1 |

| Шланговое соединение | 0 |

|

SU88A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

Авторы

Даты

2013-01-27—Публикация

2011-08-17—Подача