Определенные формы электронных схем, особенно интегральные схемы, предназначенные для использования в карточках с микросхемами, требуют высокой степени защиты информации, содержащейся на карточках, или зашифрованных данных. Эта информация, подлежащая защите, должна быть защищена как от анализа посторонними лицами, так и от манипуляции данными.

Предлагалось обеспечить такая защиту различными путями. Например, интегральные схемы снабжали металлическими оболочками, например, из серебра или титана, благодаря чему можно предотвратить считывание информации из интегральных схем с помощью рентгеновских лучей. Кроме того, хорошо зарекомендовало себя размещение на самой верхней схемной плоскости интегральной схемы проводящей дорожки в качестве защитного экранирующего проводника и контроль таких его физических свойств, как сопротивление, емкость и т.д. При установлении факта изменения такого свойства, например, вследствие короткого замыкания, заземления или разъединения при нежелательном контроле или манипулировании вырабатывается сигнал тревоги. Подобная схема защиты известна из патента США 5389738. Однако подобные типы схем защиты оказываются недостаточно эффективными, так как ожидаемые физические свойства можно имитировать подходящими внешними мерами, вследствие чего схема защиты не сможет установить факт внешнего вмешательства путем наблюдения или манипулирования и, следовательно, невозможно будет выработать соответствующие меры противодействия.

В основе изобретения лежит задача создания схемы защиты для интегральных схем, которая обеспечивает более эффективную защиту от нежелательного наблюдения или манипулирования.

Эта задача решается в схеме защиты для интегральных схем с помощью признаков, приведенных в пункте 1 формулы изобретения. Предпочтительные дальнейшие варианты осуществления изобретения приведены в зависимых пунктах формулы изобретения.

Соответствующая изобретению схема защиты размещена по меньшей мере на одной схемной плоскости сверху или снизу интегральной схемы. При этом такая схема защиты имеет один или несколько печатных проводников, нагруженных изменяющимися во времени или различными сигналами. Эти сигналы передаются посредством печатных проводников и затем анализируются одним или несколькими детекторами, при этом соответствующий принятый анализируемый сигнал сравнивается с опорным сигналом, который представляет собой ожидаемый сигнал. Если один или несколько детекторов устанавливают значительное отклонение, то соответствующий детектор вырабатывает сигнал тревоги, который переводит интегральную схему в режим защиты. В этом режиме, например, содержимое ячеек памяти может стираться, в результате чего управляющая программа и сохраненные данные невозможно будет считать и интерпретировать.

Путем применения нескольких различных сигналов, передаваемых по нескольким печатным проводникам и затем анализируемых различными детекторами, практически невозможно все инициирующие тревогу сигналы корректным образом ввести извне при попытках считывания или манипулирования и имитировать для детекторов наличие этих сигналов. Если, например, в интегральной схеме верхний слой механически удаляется для обеспечения возможности наблюдения расположенных ниже схемных плоскостей интегральной схемы, то в первую очередь затрагиваются расположенные сверху печатные проводники схемы защиты с последующим изменением или прерыванием передачи сигналов, что устанавливается с помощью одного или нескольких детекторов. Это имеет место и в том случае, когда с помощью миниатюрных игл осуществляется доступ к отдельным печатным проводникам, результатом чего являются изменения, например, формы сигнала, ослабления сигнала и т.п. Все такие изменения приведут теперь к регулярному распознаванию ошибочного состояния различными детекторами.

Таким образом, в соответствии с изобретением должен имитироваться не один единственный сигнал, а множество различных сигналов. С учетом очень ограниченных пространственных характеристик интегральной схемы практически невозможно такое множество имитированных сигналов подвести конкретным образом к различным детекторам. Тем самым обеспечивается практически всеобъемлющая защита интегральной схемы с помощью расположенной над ней защитной схемы.

Предпочтительно интегральная схема окружена в многослойной конфигурации одной схемой защиты сверху и одной схемой защиты снизу, что позволяет с помощью схем защиты исключить возможность наблюдения и манипулирования как сверху, так и снизу относительно интегральной схемы.

Предпочтительным является такое выполнение детекторов, при котором они при оценке передаваемых сигналов осуществляют анализ их целостности, что, в особенности, может осуществляться в форме проверки циклическими избыточным кодом (ЦИК), перекрестного сравнения суммы, контроля четности или других способов сравнения характеристик сигналов. Путем такого сравнения целостности передаваемого сигнала со значением целостности ожидаемого сигнала, называемого также опорным сигналом, появляется возможность предотвратить манипуляции со схемой защиты, при которой детектор по существу оказывается в состояния короткого замыкания, при этом один и тот же сигнал как в качестве опорного сигнала, так и в качестве передаваемого сигнала, подается на детектор, осуществляющий чистую проверку идентификации для установления ошибочного состояния.

Различные сигналы, которые подаются в различные печатные проводники, могут быть выработаны одним общим генератором сигналов или множеством отдельных генераторов сигналов. Предпочтительно такие один или несколько генераторов соединены с детекторами в таком смысле, что соответствующий детектор получает от относящегося к нему генератора информацию о характере ожидаемого сигнала, т.е. опорный сигнал. Тем самым имеется возможность того, что генераторы динамически изменяют выдаваемые ими сигналы и сообщают об этих изменениях детекторам, что дополнительно затрудняет имитацию сигналов при съеме информации, так как теперь учитывается изменение во времени сигналов.

Особенно предпочтительным оказался вариант, при котором печатные проводники проходят через несколько схемных плоскостей (уровней интеграции) интегральной схемы, благодаря чему обеспечивается существенно улучшенное экранирование защищаемой интегральной схемы, а также существенно затрудняется визуальный контроль структуры схемы защиты в нескольких схемных плоскостях и тем самым визуальный контроль вида и способа генерирования, подачи сигналов и детектирования различных сигналов и, следовательно, исключается возможность имитации сигналов извне. Поэтому каждое изменение в схеме защиты при вмешательстве извне приводит к обнаружению ошибочного состояния, так как имитация, вследствие чрезвычайно сложной трехмерной структуры выполнения печатных проводников и их трассировки, крайне сложна или практически исключена. Тем самым ясно, что одна схемная плоскость схемы защиты защищает от анализа другую схемную плоскость схемы защиты. Следовательно, в результате может быть создана чрезвычайно эффективная и надежная схема защиты для интегральных схем.

В соответствии с предпочтительным вариантом осуществления схемы защиты печатные проводники схемы защиты выполнены таким образом, что они обеспечивают для защищаемой интегральной схемы по существу идеальное полное плоскостное покрытие, так что если смотреть через защитную схему на интегральную схему, то отсутствует возможность непосредственного доступа к защитной схеме, например, посредством отверстий или иным подобным путем, без повреждения при этом печатного проводника защитной схемы. Это распространенное или полное покрытие обеспечивается именно за счет выполнения печатного проводника через несколько схемных плоскостей или в нескольких схемных плоскостях особенно простым и надежным способом, так как печатные проводники в одной плоскости могут быть размещены на достаточных расстояниях один от другого, и за счет этого предотвращается возможность перекрестных искажений, а промежуток между печатными проводниками может покрываться печатными проводниками в других схемных плоскостях схемы защиты, в результате чего обеспечивается полное покрытие интегральной схемы или существенных частей такой интегральной схемы.

Если теперь попытаться, например, путем сверления отверстия получить доступ к интегральной схеме, то это приведет к повреждению одного из печатных проводников, что обусловит изменение сигнала. Если печатный проводник выполнен с очень малой шириной печатного проводника, которая соответствует величине такого отверстия или меньше, то сверление такого отверстия приведет к прерыванию печатного проводника и тем самым к надежно обнаруживаемому ошибочному сигналу. Также возможно, что подобное отверстие приведет к короткому замыканию между различными печатными проводниками, что в виде существенного провала сигнала очень надежно распознается соответствующими детекторами как ошибочный сигнал. При этом ширина печатного проводника предпочтительно выбрана таким образом, что она соответствует при определенной применяемой технологии микросхем минимальной ширине печатного проводника. За счет такого выполнения печатных проводников, с одной стороны - в виде очень узких печатных проводников, а с другой стороны - распространяющихся через различные схемные плоскости и в максимальной степени покрывающих плоскости, обеспечивается очень высокая степень защитного действия против механического внедрения в схему защиты. Такое внедрение может осуществляться путем сверления отверстий или снятия слоев схемы.

Согласно предпочтительной форме выполнения изобретения детектор или детекторы схемы защиты размещены в одной схемной плоскости ниже самой верхней схемной плоскости с печатными проводниками схемы защиты и защищены этими печатными проводниками от нежелательного доступа. Благодаря такому систематическому построению обеспечивается каскадно действующая защита за счет печатных проводников схем защиты для детекторов схемы защиты и за счет печатных проводников с детекторами - для интегральной схемы.

Такая конфигурация благодаря защите, обеспечиваемой вышерасположенными проводниками, препятствует наблюдению или манипулированию детектором или детекторами, что исключает возможность воздействия, при котором можно было бы минуя печатные проводники вводить сигналы непосредственно в детекторы.

Соответствующим образом оказалось предпочтительным расположение генератора или генераторов в одной схемной плоскости, которая защищается расположенными над ней печатными проводниками защитной схемы. Таким образом, указанное размещение детекторов и соответственно генераторов схемы защиты оказалось существенным средством повышения защитного действия схемы защиты по отношению к неправомерному доступу.

Если различные сигналы вырабатываются полностью независимо один от другого, например, независимыми генераторами, то это гарантирует, что эти сигналы существенным образом различаются по их характеристикам изменения сигнала, поскольку они систематически не зависят один от другого, и поэтому могут имитироваться только с чрезвычайно высокими затратами и с чрезвычайными трудностями. Это усугубляется тем, что множество различных сигналов целенаправленно должны вводиться в конкретные печатные проводники, соответствующие конкретным детекторам, что при весьма ограниченных пространственных габаритах интегральной схемы со схемой защиты является практически невозможным. Следовательно, подобная схема защиты является особенно эффективной для защиты интегральной схемы.

В одном из вариантов осуществления изобретения одному печатному проводнику поставлены в соответствие несколько детекторов, которые снимают сигнал в печатном проводнике в положении, определенном для соответствующего детектора, и контролируют его. При таком выполнении печатный проводник разделяется на несколько участков печатного проводника, которые контролируются соответствующими им детекторами. Тем самым эти участки печатного проводника берут на себя функции контролируемого печатного проводника. Кроме того, при многократном наблюдении всего печатного проводника с различными участками печатного проводника гарантируется то, что если бы проникновение в этот участок печатного проводника с использованием подходящих мер предосторожности не было установлено посредством одного детектора, то все же другие или часть других детекторов во всем печатном проводнике установили бы изменение в контролируемом сигнале и смогли бы выработать сигнал тревоги. Тем самым за счет избыточности в использовании детекторов для одного печатного проводника обеспечивается повышенное защитное действие схемы защиты.

В общем, следует стремиться к тому, чтобы предусмотреть по возможности большее количество сигнальных проводников и по возможности большее количество генераторов сигналов и соответственно детекторов, которые затрудняют возможность неправомерного доступа в форме реконфигурирования уже из-за большого их числа. В зависимости от габаритов интегральной схемы этот подход, однако, имеет определенные пределы, так как использование множества отдельных сигналов связано с высокими затратами на аппаратные средства, что приводит к значительному удорожанию схемы при использовании мер защиты.

Поэтому в другом варианте осуществления изобретения вышеописанный способ выработки сигналов защиты использует мультиплексор и демультиплексор. Благодаря этому при использовании способа временного мультиплексирования различные печатные проводники защитного экрана в различные моменты времени соединяются с одинаковыми выходами генераторов и входами детекторов. В таком способе число генераторов и детекторов меньше числа экранирующих сегментов.

Дополнительное преимущество данного выполнения можно усмотреть в том, что число опорных проводников, которые снабжают детекторы опорным сигналом от соответствующего генератора, также сокращается, что приводит к существенной экономии площади микросхемы.

Мультиплексор и демультиплексор могут работать либо при центральном управлении, либо их состояние зависит только от числа прошедших тактовых циклов общей системы тактирования. Особенно предпочтительным является случайное или псевдослучайное управление каналами мультиплексора. Истинно случайное управление требует текущей синхронизации мультиплексора и демультиплексора с помощью специальных управляющих сигналов. Псевдослучайное управление допускает локальную выработку идентичных управляющих сигналов в непосредственной близости от мультиплексора и демультиплексора.

Согласно особенно предпочтительному варианту осуществления схемы защиты, в случае использования множества детекторов, они выполнены с перекрестными связями друг с другом. Тем самым обеспечивается то, что как только один детектор обнаружил некорректное состояние и, тем самым, неразрешенный доступ к интегральной схеме, интегральная схема управляется таким образом, что она переводится во всеобщий режим защиты. За счет перекрестных связей также возможно то, что отдельные детекторы проверяют работоспособность других детекторов или только наличие других детекторов в рамках функции подтверждения приема или в рамках функции самоконтроля и тем самым распознают неразрешенный доступ к схеме защиты и соответственно к интегральной схеме и инициируют соответствующий режим защиты интегральной схемы.

Также предпочтительным является то, что, наряду с детекторами, генераторы также связаны перекрестными связями, за счет чего можно распознать отказ генератора или попытку доступа к генератору. Кроме того, перекрестные связи генераторов с детекторами обеспечивают то, что генераторы сообщают относящимся к ним детекторам информацию о выдаваемых ими сигналах, например о характеристике изменения во времени, об уровне, о форме и т.п. Это позволяет существенно повысить вариабельность различных сигналов и тем самым степень свободы схемы защиты, что затрудняет доступ и, следовательно, существенно повышает защитное действие схемы защиты по отношению к скрытным попыткам доступа к интегральной схеме.

В основе соответствующей изобретению схемы защиты лежит, таким образом, основополагающий принцип, состоящий в том, что компоненты схемы защиты следует располагать не локально концентрированным образом, а распределять их децентрализованно, по значительной пространственной области, выполнять их в разнообразных формах и дифференцированным образом. Это приводит к тому, что выработка и передача по печатным проводникам, а также контроль сигналов распределяются между многочисленными избыточными элементами, что приводит к более высокой защищенности по отношению к скрытному наблюдению или манипулированию схемой защиты и соответственно защищаемой интегральной схемой.

Соответствующие изобретению схемы защиты для интегральных схем и их преимущества поясняются ниже на примерах осуществления, иллюстрируемых чертежами, на которых представлено следующее:

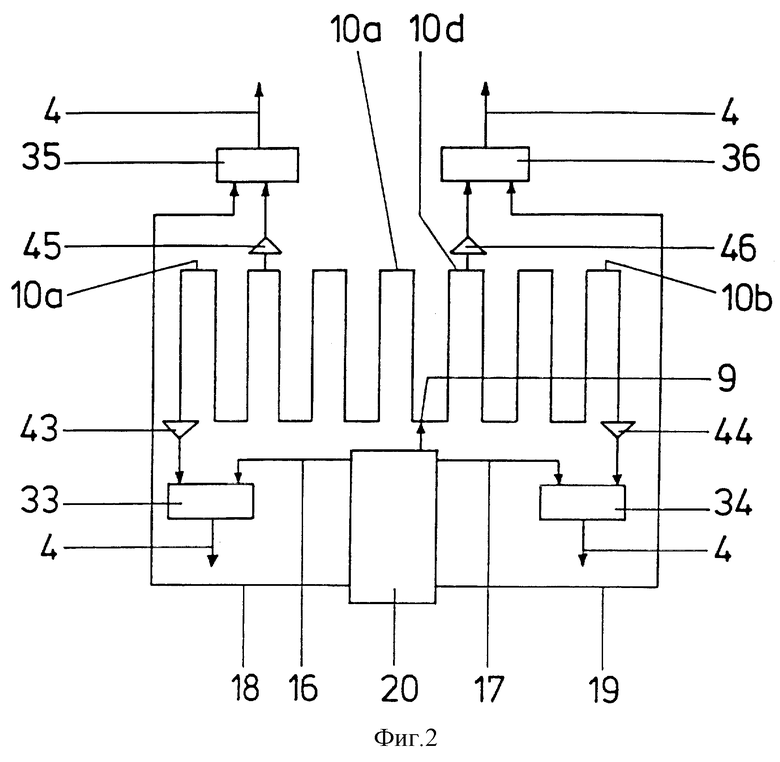

фиг.1 - структурная схема соответствующей изобретению схемы защиты, содержащей по одному генератору сигнала и по одному детектору сигнала на печатный проводник;

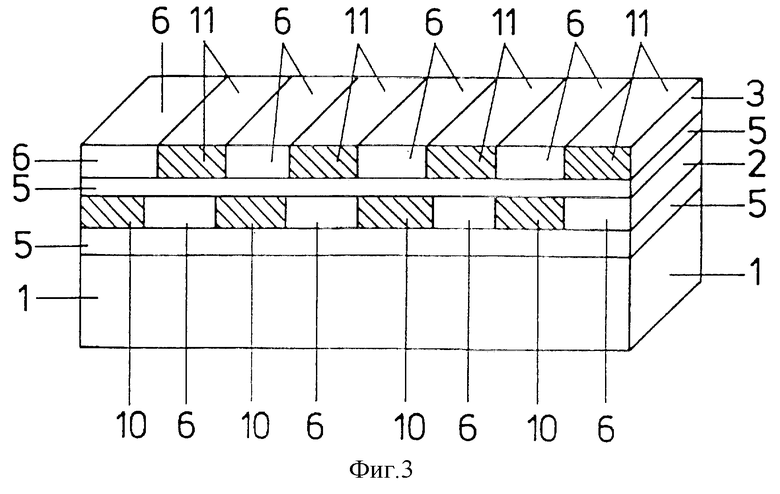

фиг.2 - структурная схема другого варианта осуществления схемы защиты;

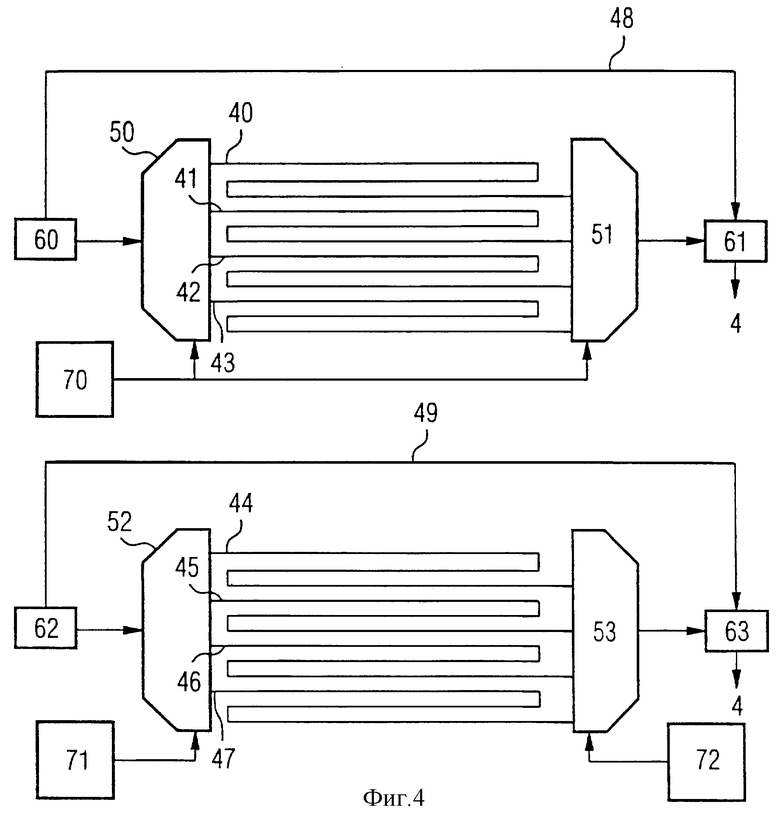

фиг.3 - вид в разрезе интегральной схемы со схемой защиты;

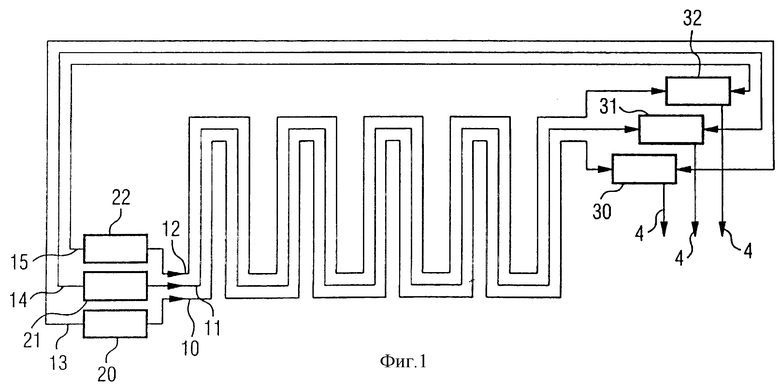

фиг.4 - структурная схема еще одного варианта осуществления соответствующей изобретению схемы защиты с блоками демультиплексора/мультиплексора.

Фиг.1 схематично иллюстрирует построение схемы защиты для интегральной схемы. На чертеже показаны три разделенных один от другого параллельно проходящих печатных проводника 10, 11, 12. Эти печатные проводники 10, 11, 12 проходят в форме меандра и покрывают определенную область в плоскости интегральной схемы.

Печатные проводники 10, 11, 12 связаны с соответствующими генераторами 20, 21, 22 сигналов. Посредством генераторов 20, 21, 22 сигналов в печатные проводники 10, 11, 12 вводятся независимые один от другого и поэтому принципиально различные сигналы. Введенные сигналы проходят по печатным проводникам 10, 11, 12, и на конце печатных проводников 10, 11, 12 они анализируются с помощью относящегося к каждому печатному проводнику детектора 30, 31, 32.

В рамках этого анализа принятые по печатным проводникам 10, 11, 12 различные сигналы сравниваются с опорными сигналами, переданными по соединительным проводникам 13, 14, 15 между генераторами 20, 21, 22 и относящимися к ним детекторами 30, 31, 32. Опорные сигналы либо непосредственно представляют собой сигналы в том виде, как они должны выглядеть после прохождения печатных проводников 10, 11, 12, или они выдают необходимую информацию, чтобы из них можно было получить информацию, требуемую для опорных сигналов.

Оценка производится в детекторах 30, 31, 32, причем опорные сигналы сравниваются с поступающими сигналами, содержащимися в печатных проводниках 10, 11, 12. При установлении различия генерируется сигнал тревоги в качестве управляющего сигнала для интегральной схемы и передается на интегральную схему через проводник 4 тревожной сигнализации, относящийся к каждому детектору 30, 31, 32.

С помощью такого сигнала тревоги интегральная схема затем переводится в состояние, которое определяется как режим защиты. В этом режиме защиты, например, содержимое ячеек памяти больше не может быть считано, так как, например, непосредственно перед переходом в режим защиты оно полностью стирается и тем самым содержащаяся в них информация необратимым образом теряется. Поэтому становится невозможным считать или изменить важную информацию интегральной схемы, содержащуюся в памяти программы или данных, например ключи кодирования, или персональные идентификационные номера, или персональные данные пользователя.

За счет множественного децентрализованного выполнения печатных проводников 10, 11, 12, генераторов 20, 21, 22 сигналов и детекторов 30, 31, 32 такую схему защиты можно лишь с большим трудом ввести в заблуждение путем подачи извне сигналов, чтобы получить более подробную информацию о защищаемой интегральной схеме, например, с использованием процессов послойного демонтажа интегральной схемы или процессов сверления отверстий и т.п.

Вследствие необходимости имитировать не один сигнал, а одновременно множество различных сигналов в различных позициях для различных детекторов, которые размещены в весьма ограниченной пространственно области, практически невозможно осуществить доступ к интегральной схеме без обнаружения изменения состояния сигналов и, следовательно, ошибочного состояния, т.е. доступ к защитной схеме с защищаемой интегральной схемой. Если детектор 30 установит ошибочное состояние для относящегося к нему сигнала в печатном проводнике 10, то он независимо от других детекторов 31, 32 выдаст сигнал тревоги через проводник 4 тревожной сигнализации и тем самым инициирует режим защиты.

За счет меандровой параллельной конфигурации печатных проводников 10, 11, 12 обеспечивается в значительной мере замкнутая плоскостная структура печатных проводников, которая защищает расположенную под ней интегральную схему или по меньшей мере ее участок от доступа посредством этих печатных проводников 10, 11, 12. Если кто-нибудь попытается механическими средствами добраться до расположенной под печатными проводниками 10, 11, 12 интегральной схемы, то это неизбежно приведет к повреждению одного из печатных проводников 10, 11, 12 или даже к полному разрыву, что приведет к значительному изменению сигналов, передаваемых по этому печатному проводнику. Это значительное изменение идентифицируется как ошибочное состояние соответствующим детектором 30, 31, 32, относящимся к данному печатному проводнику, и выдается соответствующий сигнал тревоги.

Печатные проводники 10, 11, 12 выполнены с такой малой шириной печатного проводника, что любое просверливание отверстия для преодоления защитного действия схемных плоскостей 2, 3 схемы защиты приведет к прерыванию печатного проводника. Для этого необходимо выбрать расстояние между отдельными печатными проводниками 10, 11, 12 очень малым и печатный проводник нанести в виде узкого меандра в схемной плоскости или плоскостях. Тем самым обеспечивается абсолютно надежное прерывание при попытках несанкционированного наблюдения или манипулирования, противодействие которым обеспечивает схема защиты, при этом сигнал в таком прерванном печатном проводнике 10, 11, 12 полностью прерывается и интерпретируется как попытка доступа. Сигналы, генерируемые генераторами 20, 21, 22, представляют собой специальные, чаще всего цифровые, но также и аналоговые сигналы, которые обеспечивают проявление в явном виде изменения в пути передачи по печатному проводнику 10, 11, 12.

На фиг.2 схематично представлено выполнение другой схемы защиты. Здесь имеется единственная взаимосвязывающая структура печатных проводников, которая имеет точку 9 ввода для сигнала, сформированного одним генератором 20 сигнала, в структуру печатных проводников.

В структуре печатных проводников предусмотрены четыре позиции для ответвления сигнала, передаваемого по структуре печатных проводников. Каждая из этих позиций ответвления снабжена усилителем 43, 44, 45, 46 для усиления ответвленного сигнала. Эти усиленные сигналы затем подводятся к детекторам 33, 34, 35 и 36. Структура печатных проводников образует в зависимости от соответствующей точки съема печатный проводник 10а, который представляет собой структуру печатного проводника между точкой 9 ввода сигнала и точкой съема усилителя 43 для детектора 33; печатный проводник 10b между точкой 9 ввода сигнала и точкой съема, определяемой усилителем 44, для детектора 34; печатный проводник 10с между точкой 9 ввода сигнала и точкой съема для усилителя 45 для детектора 35 и печатный проводник 10d между точкой 9 ввода сигнала и точкой схема для усилителя 46 к детектору 36.

Каждый из детекторов работает независимо от других детекторов и может посредством своего проводника 4 тревожной сигнализации управлять интегральной схемой таким образом, чтобы она переводилась в режим защиты.

Генератор 20 через соединительные проводники 16, 17, 18, 19 связан с детекторами 33, 34, 35, 36 и передает этим детекторам конкретную информацию для опорных сигналов для контроля печатных проводников 10а, 10b, 10с, 10d. Генератор выбирает случайным образом с использованием программного управления тип введенного сигнала и сигнализирует по соответствующим соединительным проводникам 16, 17, 18, 19 детекторам о форме введенного сигнала. Детекторы 33, 34, 35, 36 оценивают сигнал, подведенный к ним по соединительным проводникам 16, 17, 18, 19, сравнивая его с сигналом, подведенным от точек съема, в печатных проводниках 10а, 10b, 10с, 10d. Если имеет место значительное различие, т.е. устанавливается ошибочное состояние, то каждый детектор 33, 34, 35, 36 независимо от других выдает сигнал тревоги по своему проводнику 4 тревожной сигнализации и тем самым переводит интегральную схему в режим защиты.

За счет перекрывающегося взаимосвязанного выполнения печатных проводников 109а, 10b, 10с и 10d обеспечивается то, что попытка внедрения в печатный проводник системы печатных проводников приводит не только к изменению в одном печатном проводнике 10а, 10b, 10с, 10d, но и к изменению сигналов в нескольких печатных проводниках 10а, 10b, 10с, 10d одновременно. Тем самым в случае нежелательного наблюдения или манипулирования не только сигнал одного детектора, но и сигналы нескольких, а предпочтительно всех детекторов данной системы печатных проводников должны нагружаться имитированным и корректным сигналом. Этот сигнал должен по своей форме и своему виду, а также по своим характеристикам изменения по времени соответствовать опорному сигналу, который по соединительным проводникам 16, 17, 18, 19 передается от генератора 20 к детекторам 33, 34, 35, 36 непосредственно или опосредованно. При этом ясно, что показанный на чертеже генератор 20 имеет возможность динамического изменения своего вводимого в точку 9 ввода сигнала с использованием программного управления и тем самым в существенной степени исключать возможность наблюдения или манипулирования схемой защиты и, следовательно, защищаемой посредством этой схемы защиты интегральной схемой 1.

На фиг.3 показано схематичное построение интегральной схемы 1 с расположенной над ней схемой защиты. В варианте по фиг.3 отсутствует соответствующая схема защиты на нижней стороне интегральной схемы. Такая вторая схема защиты на другой стороне интегральной схемы 1 имеет такое же строение, что и приведенная на чертеже схема защиты.

Схема защиты размещена сверху интегральной схемы 1. Она имеет две расположенные одна над другой схемные плоскости 2, 3, которые отделены посредством изоляционного слоя 5 друг от друга и от защищаемой интегральной схемы. С помощью такого изоляционного слоя исключается короткое замыкание между печатными проводниками 10, 11 и интегральной схемой 1.

В первой схемной плоскости 2 выполнены печатные проводники 10 в виде полос, отделенных одна от другой изоляционными промежутками 6 в виде полос. Печатные проводники 10 расположены параллельно друг другу в первой схемной плоскости 2. Над схемной плоскостью 2 расположена вторая схемная плоскость 3, в которой размещены соответствующие выполненные в виде полос параллельные друг другу печатные проводники 11. Эти печатные проводники 11 также отделены один от другого изоляционными промежутками 6 и тем самым изолированы один относительно другого. Печатные проводники 10 размещены таким образом, что они при взаимодействии с печатными проводниками 11 полностью покрывают, защищаемую интегральную схему. Такое полное покрытие достигается в том случае, когда при наблюдении через первую и вторую схемные плоскости 2 каждая точка защищаемой интегральной схемы 1 перекрывается либо печатными проводниками 10, либо печатными проводниками 11, или перекрывается как печатными проводниками 10, так и печатными проводниками 11.

Если постороннее лицо попытается получить доступ к защищаемой интегральной схеме 1, то для этого потребуется преодолеть защитную схему и при этом проникнуть через схемные плоскости 2, 3, что привело бы, вследствие полного покрытия, к повреждению по меньшей мере одного из печатных проводников 10, 11. Такое повреждение, которое может представлять собой, например, полное прерывание печатных проводников или короткое замыкание между печатными проводниками в схемной плоскости 2, 3 или между схемными плоскостями 2, 3 или может состоять в частичном разрушении печатного проводника 10, 11, приводит к отчетливому изменению передаваемого сигнала, который по сравнению с ожидаемым опорным сигналом интерпретируется посредством соответствующего детектора как сигнал ошибки и, следовательно, устанавливается факт внедрения в схему защиты и соответственно в защищаемую интегральную схему 1, что приводит к выдаче сигнала тревоги в интегральную схему 1. Посредством этого сигнала тревоги интегральная схема 1 переводится затем в режим защиты.

В первой схемной плоскости 2 размещены не показанные здесь генераторы 20, 21, 22 и соответственно не показанные здесь детекторы 30-36, защищенные расположенной над ними схемной плоскостью 3 с соответственно расположенными печатными проводниками 11. В частности, такое расположение распределяется по всей первой схемной плоскости 2, что явным образом ограничивает возможности преодоления действия схемы защиты.

На фиг.4 показан пример выполнения еще одного варианта изобретения, содержащий восемь печатных проводников 40...47. Эти восемь печатных проводников 40-47 подразделены на две группы по четыре печатных проводника 40-43 и соответственно 44-47. Каждой из этих групп соответствует только один генератор 60 и соответственно генератор 62 сигналов и один детектор 61 и соответственно детектор 63 сигналов. Сигналы генераторов 60, 62 сигналов подаются в группы печатных проводников 40...43 и соответственно 44...47 через демультиплексор 50 и соответственно демультиплексор 52, и переданные посредством печатных проводников сигналы подаются через мультиплексор 51 и соответственно мультиплексор 53 на детектор 61 и соответственно детектор 63 сигналов.

Чтобы иметь возможность подвести к детекторам 61, 63 сигналов требуемые опорные сигналы, в этой форме выполнения изобретения необходимо использовать только один соединительный проводник 48 и соответственно соединительный проводник 49 на группу печатных проводников. Детекторы 61, 63 сигналов и в этом варианте обеспечивают индикацию посредством проводника 4 тревожной сигнализации, когда принятый через мультиплексор 51, 53 сигнал не согласован с ожидаемым сигналом.

В показанном на чертеже примере выполнения с двумя группами печатных проводников 40...43 и соответственно 44...47 представлены две различные возможности управления демультиплексорами 50, 52 и мультиплексорами 51, 53. В случае показанной в верхней части фиг.2 группы печатных проводников 40...43 демультиплексор 50 и мультиплексор 51 управляются совместно от истинного генератора 70 случайных чисел для выбора одного из печатных проводников 40...43. В случае показанной в нижней части чертежа группы печатных проводников 44...47 соответствующий демультиплексор 52 и соответствующий мультиплексор 53 управляются от двух отдельных, однако выполненных сходным образом генераторов 71, 72 псевдослучайных чисел, которые, вследствие их одинакового выполнения, при совместном тактировании выдают одинаковые случайных числа в одинаковые моменты времени. В принципе также возможно с помощью тактового сигнала управлять непосредственно демультиплексорами 50, 52 и мультиплексорами 51, 53, что хотя и проще схемотехнически, однако более критично с точки зрения обеспечения защиты.

При заданной площади микросхемы на основе вышеописанного соответствующего изобретению дальнейшего развития заявленной схемы защиты можно найти хороший компромисс между по возможности полным покрытием поверхности микросхемы по возможности узкими и расположенными в непосредственной близости один от другого печатными проводниками и стремлением к возможно меньшим схемотехническим затратам.

Изобретение относится к схеме защиты для интегральной схемы (1). Его использование позволяет получить технический результат в виде эффективной защиты интегральных схем от нежелательного наблюдения или манипулирования. Технический результат достигается за счет того, что схема защиты размещена, предпочтительно, на нескольких съемных плоскостях (2), (3) снизу и/или сверху интегральной схемы (1) и имеет несколько печатных проводников (10), (11), которые нагружаются различными сигналами одного или нескольких генераторов сигналов. Эти различные сигналы после передачи посредством печатных проводников (10), (11) анализируются одним или несколькими детекторами, при этом принятые детекторами сигналы сравниваются с опорными сигналами, и при установлении значительного различия в интегральную схему выдается сигнал тревоги. На основе этого сигнала тревоги интегральная схема переводится в режим защиты, в котором анализ или манипулирование интегральной схемой становится практически невозможным. 12 з.п. ф-лы, 4 ил.

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

Авторы

Даты

2004-07-10—Публикация

1999-11-04—Подача