Изобретение относится к области импульсной техники и может быть использовано в устройствах вычислительной техники и систем управления.

Известен трехстабильный счетный триггер (см. авторское свидетельство СССР №1736320, МКИ Н 03 К 3/037, “Трехстабильный счетный триггер”, Л.Б.Егоров, Г.И.Шишкин, опубл. 28.05.90. Бюл. №24), содержащий трехстабильную триггерную ячейку, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, два логических элемента, два резистора, конденсатор, два диода, две шины питания, входную и две выходные шины. При этом тактовый вход трехстабильной триггерной ячейки подключен к входной шине, первый и второй выходы - соответственно к первому и второму входам первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, третий выход - к одной из выходных шин и к первому входу первого логического элемента, второй вход которого соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход через первый резистор - с первым информационным входом трехстабильной триггерной ячейки и с первой обкладкой конденсатора. Вторая обкладка конденсатора соединена с анодом первого диода, с катодом второго диода, со вторым информационным входом трехстабильной триггерной ячейки и с первым выводом второго резистора, катод первого и анод второго диодов соединены соответственно с первой и второй шинами питания, сопротивление второго резистора, по меньшей мере, на порядок больше сопротивления первого резистора. Логические элементы выполнены в виде элементов ИЛИ-НЕ, трехстабильная триггерная ячейка выполнена на первом и втором тактируемых уровнем D-триггерах, D-входы соединены соответственно с первым и вторым информационными входами трехстабильной триггерной ячейки, тактовые входы - с ее тактовым входом и со вторым и первым входами соответственно первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, инверсные выходы - соответственно со вторым и первым выходами трехстабильной триггерной ячейки, прямые выходы - соответственно с другой выходной шиной и с третьим выходом трехстабильной триггерной ячейки. Выход первого элемента ИЛИ-НЕ соединен с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - со вторым выводом второго резистора.

Недостатком указанного счетного триггера является сложность устройства.

Известен трехстабильный счетный триггер (см. патент РФ №2093955 от 16.04.93, МПК6 Н 03 К 3/29, “Трехстабильный счетный триггер (вариант 2)”, Шишкин Г.И., Дикарев И.И., опубл. 20.10.97. Бюл. №29), содержащий первый и второй двухстабильные триггеры, первые входы которых соединены с шиной счетных сигналов, инверсный выход первого двухстабильного триггера соединен с первым входом элемента И-НЕ, выход которого соединен с первой выходной шиной, вторую выходную шину, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два коммутатора, три резистора и конденсатор. Двухстабильные триггеры выполнены по КМОП-технологии в виде тактируемых D-триггеров, первые входы которых являются тактовыми, прямой выход первого из которых соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с прямым входом первого коммутатора. Выход первого коммутатора через первый резистор соединен с первым выводом второго резистора и с первой обкладкой конденсатора, вторая обкладка которого соединена с информационным входом второго D-триггера и через третий резистор - с выходом второго коммутатора. Инверсный вход второго коммутатора соединен со второй выходной шиной и с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом второго D-триггера и со вторым входом элемента И-НЕ. Выход элемента И-НЕ соединен с инверсным входом первого коммутатора, управляющий вход которого соединен с управляющим входом второго коммутатора и с шиной счетных сигналов. Информационный вход первого D-триггера соединен со вторым выводом второго резистора.

Трехстабильный счетный триггер является наиболее близким по технической сущности к заявленному устройству и взят в качестве прототипа.

Недостатком прототипа является сложность устройства.

Задачей, решаемой предлагаемым изобретением, является создание трехстабильного счетного триггера, отличающегося простотой схемной реализации.

Технический результат достигается тем, что в трехстабильный счетный триггер, содержащий первый элемент И-НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, три резистора, конденсатор, шину счетных сигналов, две выходные шины и двухстабильный триггер, выполненный по КМОП-технологии в виде тактируемого D-триггера, тактовый вход которого соединен с шиной счетных сигналов, информационный вход - с первым выводом первого резистора и с первой обкладкой конденсатора, а инверсный выход - с первым входом первого элемента И-НЕ, выход которого соединен с первой выходной шиной. Новым является то, что введены второй и третий элементы И-НЕ, первый вход второго элемента И-НЕ соединен с шиной счетных сигналов и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом тактируемого D-триггера, со второй выходной шиной и со вторым входом второго элемента И-НЕ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен со вторым выводом первого резистора, вторая обкладка конденсатора через второй резистор подключена к выходу третьего элемента И-НЕ и к первому выводу третьего резистора, второй вывод которого соединен со вторым входом первого элемента И-НЕ, выход которого соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом второго элемента И-НЕ.

Указанная совокупность признаков позволяет упростить трехстабильный счетный триггер.

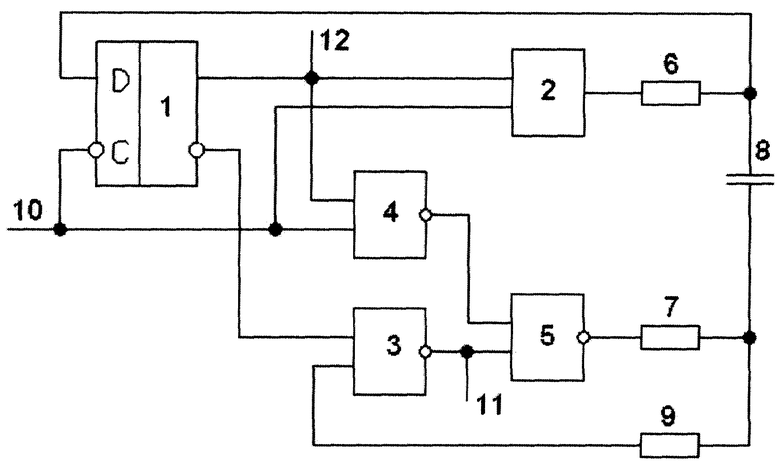

Принципиальная схема трехстабильного счетного триггера приведена на чертеже.

Трехстабильный счетный триггер содержит тактируемый D-триггер 1, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, первый, второй и третий элементы И-НЕ 3, 4, 5 соответственно, первый, второй, третий резисторы 6, 7, 9 соответственно, конденсатор 8, шину счетных сигналов 10, первую и вторую выходные шины 11, 12 соответственно.

Тактовый вход D-триггера 1 соединен с шиной счетных сигналов 10, с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и с первым входом второго элемента И-НЕ 4, второй вход которого соединен со второй выходной шиной 12, со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и с прямым выходом D-триггера 1, инверсный выход которого соединен с первым входом первого элемента И-НЕ 3, второй вход которого соединен со вторым выводом третьего резистора 9, первый вывод которого соединен с первым выводом второго резистора 7 и со второй обкладкой конденсатора 8, первая обкладка которого соединена с первым выводом первого резистора 6 и с информационным входом D-триггера 1, второй вывод первого резистора 6 соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2, второй вывод второго резистора 7 соединен с выходом третьего элемента И-НЕ 5, второй вход которого соединен с выходом второго элемента И-НЕ 4, а первый вход - с выходом первого элемента И-НЕ 3 и с первой выходной шиной 11.

Трехстабильный счетный триггер работает следующим образом.

В первом (исходном) состоянии D-триггер 1 находится в состоянии логического “0”, конденсатор 8 разряжен. Во время отсутствия счетного импульса на шине счетных сигналов 10 присутствует сигнал логического “0”, следовательно, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 присутствует сигнал логического “0”, на выходах элементов И-НЕ 3, 4 - сигнал логической “1”, а на выходе элемента И-НЕ 5 - сигнал логического “0”. На выходных шинах 11, 12 присутствуют сигналы логической “1” и логического “0” соответственно. Устройство находится в режиме хранения информации.

При поступлении первого счетного импульса D-триггер 1 становится “нечувствительным” к сигналу на его информационном входе, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 появляется сигнал логической “1”. Конденсатор 8 заряжается, при этом его положительно заряженная обкладка подключена к информационному входу D-триггера 1, на выходе элемента И-НЕ 5 присутствует сигнал логического “0”. После окончания первого счетного импульса сигнал на информационном входе устанавливает D-триггер 1 в состояние логической “1”, что приводит к появлению сигнала логической “1” на первом входе элемента И-НЕ 3, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 поддерживается сигнал логической “1”, на выходных шинах 11, 12 присутствуют сигналы логической “1”. Устройство находится в режиме хранения информации.

При поступлении второго счетного импульса на шину счетных сигналов 10 D-триггер 1 становится “нечувствительным” к сигналу на его информационном входе, на выходе элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и И-НЕ 4 устанавливаются сигналы логического “0”, а на выходе элемента И-НЕ 5 - сигнал логической “1”. Конденсатор 8 начинает перезаряжаться через резисторы 7 и 8, и после окончания процесса перезарядки его положительно заряженная обкладка соединена с первым выводом резистора 7. После окончания второго счетного импульса D-триггер 1 устанавливается в состояние логического “0”, следовательно, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 поддерживается сигнал логического “0”, на входах элемента И-НЕ 3 устанавливаются сигналы логической “1”, а на его выходе - сигнал логического “0”. Поэтому на выходе элемента И-НЕ 5 поддерживается сигнал логической “1”, а на выходных шинах 11, 12 присутствуют сигналы логического “0” и логической “1” соответственно.

При поступлении третьего счетного импульса на выходе элемента И-НЕ 5 поддерживается сигнал логической “1”, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 устанавливается сигнал логической “1”, что приводит к разряду конденсатора 8. К моменту окончания третьего счетного импульса конденсатор 8 должен полностью разрядиться, поэтому сразу же после его окончания на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 устанавливается сигнал логического “0” и D-триггер 1 устанавливается в состояние логического “0”. Это приводит к появлению сигнала логического “0” на втором входе элемента И-НЕ 3 и, следовательно, сигнала логической “1” на его выходе. Так как на выходе элемента И-НЕ 4 поддерживается сигнал логической “1”, то на выходе элемента И-НЕ 5 устанавливается сигнал логического “0”, а на выходных шинах 11, 12 присутствуют сигналы логической “1” и логического “0” соответственно. Таким образом, после поступления на вход трехстабильного счетного триггера третьего счетного импульса устройство возвращается в первое (исходное) состояние.

Рассмотрение работы устройства показывает, что при нормальном его функционировании состояние, при котором на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и И-НЕ 5 присутствуют сигналы логической “1”, исключено. При переходе устройства в это состояние в результате воздействия импульса помехи на его выходных шинах 11, 12 присутствуют сигналы логической “1” и логического “0” соответственно, т.е. сигналы исходного состояния.

При рассмотрении процессов восстановления состояния устройства после воздействия помехи следует отметить, что для формирования сигналов управления требуемого уровня сопротивление резистора 7 должно быть на порядок меньше сопротивления резистора 6.

Рассмотрим в качестве примера процессы, происходящие в устройстве, до воздействия помехи находившемся во втором состоянии, в котором конденсатор 8 заряжен и его положительно заряженная обкладка соединена с информационным входом D-триггера 1, установленному в состояние логической “1”. Предположим, что после окончания воздействия импульса помехи, D-триггер 1 устанавливается в состояние логической “1”, а на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и И-НЕ 5 присутствуют сигналы логического “0”, соответствующие первому состоянию устройства. Конденсатор 8 начнет разряжаться, а на информационном входе D-триггера 1 появляется сигнал, близкий к уровню напряжения питания, на втором входе элемента И-НЕ 3 - сигнал, близкий к логическому “0”. D-триггер 1 переключится в состояние логической “1”, что приведет к появлению сигнала логической “1” на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2, т.е. состояние устройства восстановится.

Если после воздействия импульса помехи устройство перешло в третье состояние, при котором на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и И-НЕ 5 присутствуют сигналы логического “0” и логической “1” соответственно, то начинается перезаряд конденсатора 8. Поскольку сопротивление резистора 7 на порядок меньше сопротивления резистора 6, на информационном входе D-триггера 1 установится напряжение ≈2Е (Е - напряжение питания), которое переключит его в состояние логической “1”. На втором входе элемента И-НЕ 3 установится напряжение ≈Е. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 так же, как и на выходе элемента И-НЕ 5, установятся сигналы логической “1”. Конденсатор 8 начинает разряжаться через выход элемента И-НЕ 5 и резистор 7, резистор 9 и входной защитный диод элемента D-триггера 1. При этом напряжение на втором входе элемента И-НЕ 3 близко к логическому “0” и на выходе элемента И-НЕ 5 появляется сигнал логического “0”, т.е. устройство восстанавливает свое состояние.

Резистор 9 препятствует быстрому разряду конденсатора 8 через защитный входной диод элемента И-НЕ 3 и D-триггера 1 (Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. - Л.: Энергоатомиздат, 1986, с.65, рис.6-4) при перерывах питания. Сопротивление резистора 9 должно быть достаточно большим (целесообразно выбрать его больше сопротивления резистора 7).

Изготовлен лабораторный макет трехстабильного счетного триггера, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта. Макет был выполнен на микросхемах серии 564.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2237970C1 |

| ТРЕХСТАБИЛЬНЫЙ СЧЕТНЫЙ ТРИГГЕР (ВАРИАНТЫ) | 1993 |

|

RU2093955C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2237969C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250558C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2237354C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2224357C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1993 |

|

RU2040111C1 |

| ТРОИЧНОЕ СЧЕТНОЕ УСТРОЙСТВО | 2002 |

|

RU2231921C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1996 |

|

RU2123232C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1990 |

|

SU1753920A1 |

Изобретение относится к области импульсной техники и может быть использовано в устройствах вычислительной техники и систем управления. Техническим результатом является упрощение трехстабильного счетного триггера. Технический результат достигается за счет того, что трехстабильный счетный триггер содержит тактируемый D-триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, три элемента И-НЕ, три резистора, конденсатор, шину счетных сигналов, первую и вторую выходные шины. 1 ил.

Трехстабильный счетный триггер, содержащий первый элемент И-НЕ, элемент Исключающее ИЛИ, три резистора, конденсатор, шину счетных сигналов, две выходные шины и двухстабильный триггер, выполненный по КМОП-технологии в виде тактируемого D-триггера, тактовый вход которого соединен с шиной счетных сигналов, информационный вход - с первым выводом первого резистора и с первой обкладкой конденсатора, а инверсный выход - с первым входом первого элемента И-НЕ, выход которого соединен с первой выходной шиной, отличающийся тем, что введены второй и третий элементы И-НЕ, первый вход второго элемента И-НЕ соединен с шиной счетных сигналов и с первым входом элемента Исключающее ИЛИ, второй вход которого соединен с прямым выходом тактируемого D-триггера, со второй выходной шиной и со вторым входом второго элемента И-НЕ, выход элемента Исключающее ИЛИ соединен со вторым выводом первого резистора, вторая обкладка конденсатора через второй резистор подключена к выходу третьего элемента И-НЕ и к первому выводу третьего резистора, второй вывод которого соединен со вторым входом первого элемента И-НЕ, выход которого соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом второго элемента И-НЕ.

| ТРЕХСТАБИЛЬНЫЙ СЧЕТНЫЙ ТРИГГЕР (ВАРИАНТЫ) | 1993 |

|

RU2093955C1 |

| SU 1736320 A1, 27.08.2001 | |||

| SU 1701090 A1, 10.09.1997 | |||

| SU 1612940 A1, 27.08.2001 | |||

| JP 2001044805 A, 16.02.2001. | |||

Авторы

Даты

2004-09-27—Публикация

2002-11-26—Подача