Изобретение относится к области импульсной техники и может быть использовано в счетных устройствах вычислительной техники и систем управления.

Известен трехстабильный счетный триггер (см. а.с. СССР №585591, кл. Н 03 К 3/286, опубл. 25.12.77. Бюл. №47), выбранный в качестве аналога изобретения и содержащий три RS-триггера, каждый из которых выполнен на трехвходовом и двухвходовом логических элементах И-НЕ с перекрестными связями, схему управления, содержащую три трехвходовых выходных логических элемента И-НЕ, а также содержит три выхода и шину счетных сигналов. Выходы двухвходовых элементов И-НЕ являются первыми выходами соответствующих RS-триггеров. Первые и вторые входы двухвходовых элементов И-НЕ являются, соответственно, первыми и вторыми входами соответствующих RS-триггеров. Первые и вторые входы трехвходовых элементов И-НЕ являются, соответственно, третьими и четвертыми входами соответствующих RS-триггеров. Первые входы первого, второго и третьего трехвходовых выходных элементов И-НЕ являются, соответственно, первым, вторым и третьим входами схемы управления. Вторые входы первого, второго и третьего трехвходовых выходных элементов И-НЕ являются, соответственно, четвертым, пятым и шестым входами схемы управления. Третьи входы первого, второго и третьего трехвходовых выходных элементов И-НЕ являются, соответственно, седьмым, восьмым и девятым входами схемы управления. Выходы первого, второго и третьего трехвходовых выходных элементов И-НЕ являются, соответственно, первым, вторым и третьим выходами схемы управления. Первые выходы каждого из RS-триггеров соединены, соответственно, с первым, вторым и третьим входами схемы управления, выходы которой являются соответствующими выходами устройства. Первые входы RS-триггеров соединены с шиной счетных сигналов. Вторые входы первого и третьего RS-триггеров соединены между собой. Вторые входы первого, второго и третьего RS-триггеров соединены с третьими входами, соответственно, третьего, первого и второго RS-триггеров. Четвертый вход первого RS-триггера соединен с четвертым и шестым входами схемы управления и с ее вторым выходом. Четвертый вход второго RS-триггера соединен с пятым и седьмым входами схемы управления и с ее третьим выходом. Четвертый вход третьего RS-триггера соединен с восьмым и девятым входами схемы управления и с ее первым выходом.

Недостатком известного триггера является низкая помехоустойчивость, вследствие отсутствия мер защиты триггерных структур, входящих в его состав, от внешних импульсных помех.

Известно триггерное устройство (см. патент РФ №2093955 от 16.04.93, МПК: Н 03 К 3/29, "Трехстабильный счетный триггер", вариант 2, Шишкин Г.И., Дикарев И.И., опубл. 20.10.97. Бюл. №29), выбранное в качестве прототипа и содержащее первый и второй двухстабильные триггеры, первые входы которых соединены с шиной счетных сигналов, инверсный выход первого двухстабильного триггера соединен с первым входом элемента И-НЕ, выход которого соединен с первой выходной шиной, вторую выходную шину, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два коммутатора, три резистора и конденсатор. Двухстабильные триггеры выполнены по КМОП-технологии в виде тактируемых D-триггеров, первые входы которых являются тактовыми, прямой выход первого из которых соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с прямым входом первого коммутатора. Выход первого коммутатора через первый резистор соединен с первым выводом второго резистора и с первой обкладкой конденсатора, вторая обкладка которого соединена с информационным входом второго D-триггера и через третий резистор - с выходом второго коммутатора. Инверсный вход второго коммутатора соединен со второй выходной шиной и с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом второго D-триггера и со вторым входом элемента И-НЕ. Выход элемента И-НЕ соединен с инверсным входом первого коммутатора, управляющий вход которого соединен с управляющим входом второго коммутатора и с шиной счетных сигналов. Информационный вход первого D-триггера соединен со вторым выводом второго резистора.

Первым недостатком прототипа является низкая помехоустойчивость вследствие большой цены возможного сбоя под действием внешних помех по шине счетных сигналов и по шине питания. При поступлении каждого второго счетного импульса в триггерном устройстве происходит перезаряд конденсатора, и если вместо второго счетного импульса поступит импульс помехи ограниченной длительности, то конденсатор может успеть только разрядится. Это соответствует возврату триггерного устройства из второго устойчивого состояния в первое устойчивое состояние. Это соответствует потере двух счетных импульсов.

Вторым недостатком является невозможность обеспечения работы триггерного устройства в однопеременном троичном коде из-за невозможности переключения устройства при переполнении из режима сложения в режим вычитания и обратно.

Задачей, решаемой заявляемым изобретением, является создание триггерного устройства, обладающего повышенной помехоустойчивостью к воздействию внешних помех и возможностью работы в однопеременном троичном коде.

Технический результат заключается в повышении помехоустойчивости и обеспечении работы в однопеременном троичном коде.

Это достигается тем, что в триггерное устройство, содержащее шину счетных сигналов, первую и вторую выходные шины, первый и второй коммутаторы, первый элемент И-НЕ, первый, второй, третий резисторы и первый конденсатор, первый и второй двухстабильные триггеры, выполненные по КМОП-технологии в виде тактируемых D-триггеров, тактовые входы которых объединены между собой и соединены с управляющими входами первого и второго коммутаторов, первый вход второго коммутатора соединен с выходом первого элемента И-НЕ, первый вход которого подключен к инверсному выходу первого D-триггера, прямой выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен со второй выходной шиной, а второй вход - с прямым выходом второго D-триггера и со вторым входом второго коммутатора, выход которого соединен с первым выводом первого резистора, первый вывод первого конденсатора через второй резистор соединен с первым выводом третьего резистора и информационным входом первого D-триггера. Новым является то, что дополнительно введены первый элемент ИЛИ-НЕ, первый и второй инверторы, четвертый резистор и второй конденсатор, третий коммутатор, второй и третий элементы И-НЕ, выход последнего из которых соединен с тактовыми входами первого и второго D-триггеров, первый его вход - с выходом первого инвертора, второй его вход - с выходом второго инвертора и с первым входом второго элемента И-НЕ, второй вход которого соединен с входом первого инвертора и выходом третьего коммутатора, первый вход которого соединен со вторым входом первого коммутатора и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, в который введен третий вход, соединенный с шиной управления и со вторыми входами первого элемента И-НЕ, элемента ИЛИ-НЕ и с управляющим входом третьего коммутатора, второй вход которого подключен к первому входу элемента ИЛИ-НЕ и к инверсному выходу второго D-триггера, информационный вход которого соединен со вторым выводом первого резистора и через четвертый резистор и второй конденсатор соединен с общей шиной, второй вывод первого конденсатора соединен с общей шиной, выход элемента ИЛИ-НЕ соединен с первым входом первого коммутатора, выход которого подключен ко второму выводу третьего резистора, шина счетных сигналов соединена с входом второго инвертора, выход второго элемента И-НЕ соединен с первой выходной шиной.

Указанная совокупность признаков позволяет повысить помехоустойчивость к воздействию внешних помех путем уменьшения цены возможного сбоя за счет исключения перезаряда конденсатора при поступлении счетных импульсов и обеспечить работу данного устройства в однопеременном троичном коде за счет переключения триггерного устройства при переполнении из режима сложения в режим вычитания и обратно.

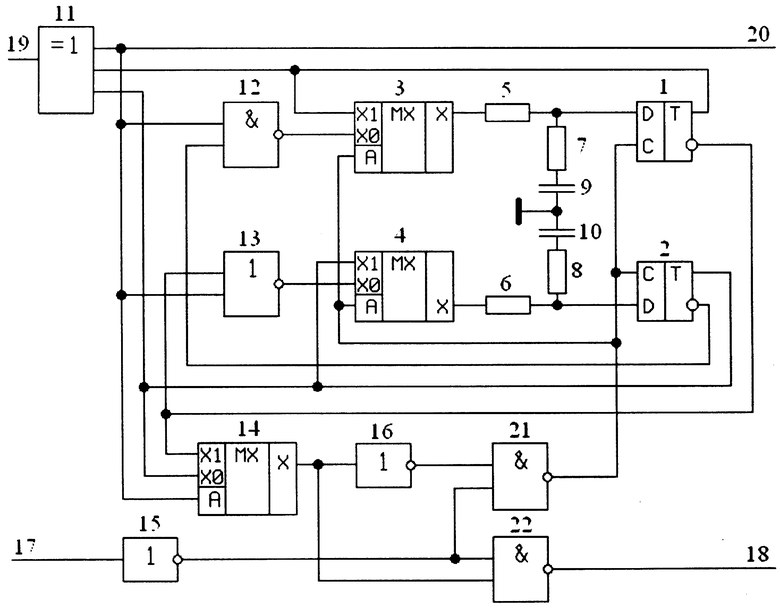

На чертеже приведена принципиальная схема триггерного устройства. Триггерное устройство содержит два тактируемых двухстабильных D-триггера 1 и 2, выполненных по КМОП-технологии, три коммутатора 3, 4, 14 четыре резистора 5, 6, 7, 8, два конденсатора 9, 10, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11, три элемента И-НЕ 12, 21, 22, элемент ИЛИ-НЕ 13, два инвертора 15, 16, шину счетных сигналов 17, две выходные шины 18, 19 и шину управления 20.

Тактовые входы D-триггеров 1 и 2 объединены и подключены к объединенным управляющим входам коммутаторов 3 и 4 и к выходу элемента И-НЕ 21. Выход коммутатора 3 через резистор 5 соединен с информационным входом D-триггера 1 и со вторым выводом резистора 7, первый вывод которого соединен через конденсатор 9 с общей шиной. Прямой выход D-триггера 1 подключен ко вторым входам коммутатора 3 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11, первый вход которого подключен ко второму и первому входам коммутаторов 4 и 14 соответственно, и к прямому выходу D-триггера 2. Информационный вход D-триггера 2 через резистор 6 соединен со вторым выводом конденсатора 10, первый вывод которого соединен с общей шиной. Инверсный выход D-триггера 2 подключен к первому входу элемента И-НЕ 12, второй вход которого соединен с управляющим входом коммутатора 14, со вторым входом элемента ИЛИ-НЕ 13, с шиной управления 20 и с третьим входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11, выход которого подключен к выходной шине 19. Выход инвертора 16 соединен с первым входом элемента И-НЕ 21, второй вход которого подключен к первому входу элемента И-НЕ 22 и к выходу инвертора 15, вход которого соединен с шиной счетных сигналов 17. Выход коммутатора 14 подключен к входу инвертора 16 и второму входу элемента И-НЕ 22, выход которого соединен с выходной шиной 18. Второй вход коммутатора 14 подключен к инверсному выходу D-триггера 1 и к первому входу элемента ИЛИ-НЕ 13, выход которого соединен с первым входом коммутатора 4, выход которого через резистор 6 соединен с информационным входом D-триггера 1.

Триггерное устройство представляет собой один разряд счетчика в однопеременном троичном коде. Для построения многоразрядного счетчика необходимо соединить выходную шину 19 последующего разряда с шиной управления 20 предыдущего разряда, а шину счетных сигналов 17 последующего разряда - с выходной шиной 18 предыдущего разряда.

Триггерное устройство работает следующим образом.

В первом (исходном) состоянии, в режиме хранения информации, D-триггеры 1 и 2 находятся в состоянии логического "0". На шине управления 20 всех разрядов счетчика присутствует сигнал логического "0", следовательно, на выход коммутатора 14 подключен к своему первому входу Х0, на котором присутствует сигнал логического "0". Сигнал логического "0" с выхода коммутатора 14 поступает на второй вход элемента И-НЕ 22 и запрещает прохождение счетных сигналов на выходную шину 18 и, с помощью инвертора 16, разрешает их прохождение через элемент И-НЕ 21. Во время отсутствия счетного импульса на шине счетных сигналов 17 присутствует сигнал логической "1", следовательно, на выходе инвертора 15 - сигнал логического "0", а на выходах элемента И-НЕ 21 - сигнал логической "1". При отсутствии счетных импульсов на тактовых входах D-триггеров 1, 2 и входах управления коммутаторов 3 и 4, сохраняется сигнал логической "1", разрешающий запись данных в D-триггеры 1, 2 с их информационных входов. Выходы коммутаторов 3, 4 подключены к своим вторым входам Х1, которые соединены с прямыми выходами D-триггеров 1, 2, удерживаемых в состоянии логического "0" сигналами на их информационных входах с помощью разряженных конденсаторов 9, 10. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 и выходной шине 19 присутствуют сигналы логического "0". Если под действием внешней помехи D-триггер 1 установится в состояние логической "1", то на выходе коммутатора 3 будет сформирован сигнал логической "1", а конденсатор 9 начнет заряжаться через резистор 5, при этом его положительно заряженная обкладка подключена через резистор 7 к информационному входу D-триггера 1. Если за время действия импульса помехи напряжение на конденсаторе 5 не достигнет порога переключения D-триггера 1 в состояние логической "1", то по окончании импульса помехи D-триггер 1 возвратится в состояние логического "0". Аналогичным образом происходит восстановление других состояний D-триггеров 1,2.

При поступлении первого счетного импульса (сигнал логического "0" на шине счетных сигналов 17) на выходе инвертора 15 появляется сигнал логической "1", а на выходе элемента И-НЕ 21, на входах управления коммутаторов 3, 4 и на тактовых входах D-триггеров 1,2 - сигнал логического "0". D-триггеры 1, 2 становятся "нечувствительными" к сигналам на их информационных входах и находятся в состоянии логического "0". Выходы коммутаторов 3, 4 подключаются к своим первым входам Х0, на которых присутствуют сигналы логической "1" и логического "0" соответственно. На выходах коммутаторов 3, 4 устанавливаются сигналы логической "1" и логического "0" соответственно. Конденсатор 9 начинает заряжаться, при этом длительность счетного импульса должна быть достаточной для его заряда до напряжения логической "1". После окончания первого счетного импульса (сигнал логической "1" на шине счетных сигналов

17) D-триггеры 1, 2 установятся в состояния логической "1" и логического "0" соответственно, а входе Х1 коммутатора 14 появится сигнал логического "0". На выходных шинах 18 и 19 установятся сигналы логической "1", а на шине управления 20 - сигнал логического "0". На выходах элементов И-НЕ 12 и ИЛИ-НЕ 13 и, следовательно, входах Х0 коммутаторов 3, 4 установятся сигналы логической "1", а на входах Х1 коммутаторов 3, 4 - сигналы логической "1" и логического "0", соответственно. Триггерное устройство переходит в режим хранения информации.

При поступлении второго счетного импульса D-триггеры 1, 2 находятся в состояниях логической "1" и логического "0" соответственно, на шине управления 20 поддерживается сигнал логического "0", а на выходе элемента И-НЕ 21 появляется сигнал логического "0". Выходы коммутаторов 3, 4 подключаются к своим первым входам Х0, на которых присутствуют сигналы логической "1". Конденсатор 10 начинает заряжаться, при этом длительность счетного импульса должна быть достаточной для его заряда до напряжения логической "1". По окончании второго счетного импульса D-триггер 2 устанавливается в состояние логической "1", при этом на выходной шине 19 устанавливается сигнал логического "0". На выходе коммутатора 14, подключенном к входу Х0, устанавливается сигнал логической "1", разрешающий прохождение через элемент И-НЕ 22 следующих счетных импульсов на выходную шину 18 с шины счетных сигналов 17. Резисторы 7, 8 препятствует быстрому разряду конденсаторов 9, 10 соответственно, через защитные входные диоды D-триггеров 1 и 2 соответственно, при перерывах питания (Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. - Л.: Энергоатомиздат, 1986, с.65, рис.6-4). Сопротивление резисторов 7 и 8 должно быть достаточно большим.

При поступлении третьего счетного импульса D-триггеры 1, 2 находятся в состоянии логической "1". На шине управления 20 поддерживается сигнал логического "0", с выхода коммутатора 14 подается сигнал логической "1", разрешающий прохождение третьего счетного импульса на выходную шину 18. Сигнал логического "0" на выходе инвертора 16 запрещает прохождение счетного импульса через элемент И-НЕ 21, поэтому в течение действия третьего счетного сигнала D-триггеры 1, 2 сохраняют состояние логической "1". После окончания третьего счетного импульса в триггерном устройстве старшего разряда счетчика D-триггеры 1, 2 окажутся в состояниях логической "1" и логического "0" соответственно, а на шине 19 формируется сигнал логической "1". На шине управления 20 младшего разряда счетчика формируется сигнал логической "1", переключающий триггерное устройство младшего разряда счетчика из режима сложения в режим вычитания. На выходной шине 19 триггерного устройства младшего разряда счетчика появляется сигнал логической "1", а на входе Х0 коммутатора 4 - сигнал логического "0". На управляющем входе коммутатора 14 появляется сигнал логической "1", подключающий выход к входу Х1, следовательно, на выходе коммутатора 14 появляется уровень логического "0", запрещающий прохождение счетных импульсов на шину 18. Триггерное устройство остается в режиме хранения информации.

При поступлении четвертого счетного импульса D-триггеры 1, 2 триггерного устройства младшего разряда счетчика находятся в состоянии логической "1". На шине управления 20 и выходных шинах 18, 19 присутствуют сигналы логической "1", а на выходе элемента И-НЕ 21 четвертый счетный импульс устанавливает сигнал логического "0". На входах управления коммутаторов 3, 4 устанавливается сигнал логического "0", что вызывает подключение выходов коммутаторов 3, 4 к своим первым входам Х0, на которых присутствуют сигналы логической "1" и логического "0" соответственно. Конденсатор 10 разряжается через резистор 6 и выход коммутатора 4 до напряжения логического "0". После окончания четвертого счетного импульса D-триггеры 1, 2 устанавливаются в состояния логической "1" и логического "0" соответственно, а на выходной шине 19 появляется сигнал логического "0". Триггерное устройство переходит в режим хранения информации.

При поступлении пятого счетного импульса D-триггеры 1, 2 находятся в состояниях логической "1" и логического "0" соответственно, а на шине управления 20 поддерживается сигнал логической "1". На выходе элемента И-НЕ 21 появляется сигнал логического "0" и конденсатор 9 начинает разряжаться через резистор 5 и выход коммутатора 3 до напряжения логического "0". Таким образом, после окончания пятого счетного импульса D-триггеры 1, 2 устанавливаются в состояния логического "0", что вызывает появление на входе Х1 коммутатора 14 (и его выходе) сигнала логической "1", разрешающего прохождение следующего (шестого) счетного сигнала на выходную шину 18. На выходных шинах 18, 19 устанавливается сигналы логической "1".

Шестой счетный сигнал, не изменяя состояния триггерного устройства младшего разряда счетчика, проходит на счетную шину 17 его старшего разряда. Это приводит к установке D-триггеров 1, 2 старшего разряда счетчика в состояния логической "1", а на выходной шине 19 появляется сигнал логического "0". Устройство возвратилось в исходное состояние.

Таким образом, данное триггерное устройство работает в режиме сложения или в режиме вычитания в зависимости от сигнала на шине управления 20, и в каждом из этих режимов проходит три счетных импульса с шины счетных сигналов 17, определяющих устойчивое состояние D-триггеров 1 и 2. Следовательно, обеспечивается работа триггерного устройства в однопеременном троичном коде, а также повышается его помехоустойчивость к воздействию внешних помех путем уменьшения цены возможного сбоя за счет отсутствия перезаряда конденсаторов 9 и 10.

Изготовлен лабораторный макет триггерного устройства, испытания которого подтвердили работоспособность и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2237970C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2237969C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2237354C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2224357C2 |

| ТРЕХСТАБИЛЬНЫЙ СЧЕТНЫЙ ТРИГГЕР | 2002 |

|

RU2237351C2 |

| ТРЕХСТАБИЛЬНЫЙ СЧЕТНЫЙ ТРИГГЕР (ВАРИАНТЫ) | 1993 |

|

RU2093955C1 |

| ТРОИЧНОЕ СЧЕТНОЕ УСТРОЙСТВО | 2002 |

|

RU2231921C2 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036555C1 |

| ПОМЕХОСТОЙКОЕ ТРИГГЕРНОЕ УСТРОЙСТВО | 1995 |

|

RU2106056C1 |

| МУЛЬТИВИБРАТОР | 2003 |

|

RU2237353C1 |

Изобретение относится к области импульсной техники. Технический результат заключается в повышении помехоустойчивости и обеспечении работы в однопеременном троичном коде. Триггерное устройство содержит два тактируемых двухстабильных D-триггера (1, 2), коммутаторы (3, 4, 14), резисторы (Р) (5, 6, 7, 8), конденсаторы (9, 10), элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (11), элементы И-НЕ (12, 21, 22), ИЛИ-НЕ (13), инверторы (15, 16), шину счетных сигналов (17), выходные шины (18, 19), и шину управления (20). Устойчивость к воздействию внешних помех достигается за счет исключения перезаряда конденсатора при поступлении счетных импульсов, а обеспечение работы в однопеременном троичном коде - за счет переключения триггерного устройства при переполнении из режима слежения в режим вычитания и обратно. 1 ил.

Триггерное устройство, содержащее шину счетных сигналов, первую и вторую выходные шины, первый и второй коммутаторы, первый элемент И-НЕ, первый, второй, третий резисторы и первый конденсатор, первый и второй двухстабильные триггеры, выполненные по КМОП-технологии в виде тактируемых D-триггеров, тактовые входы которых объединены между собой и соединены с управляющими входами первого и второго коммутаторов, первый вход второго коммутатора соединен с выходом первого элемента И-НЕ, первый вход которого подключен к инверсному выходу первого D-триггера, прямой выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен со второй выходной шиной, а второй вход - с прямым выходом второго D-триггера и со вторым входом второго коммутатора, выход которого соединен с первым выводом первого резистора, первый вывод первого конденсатора через второй резистор соединен с первым выводом третьего резистора и информационным входом первого D-триггера, отличающееся тем, что введены первый элемент ИЛИ-НЕ, первый и второй инверторы, четвертый резистор и второй конденсатор, третий коммутатор, второй и третий элементы И-НЕ, выход последнего из которых соединен с тактовыми входами первого и второго D-триггеров, первый его вход - с выходом первого инвертора, второй его вход - с выходом второго инвертора и с первым входом второго элемента И-НЕ, второй вход которого соединен с входом первого инвертора и выходом третьего коммутатора, первый вход которого соединен со вторым входом первого коммутатора и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, в который введен третий вход, соединенный с шиной управления и со вторыми входами первого элемента И-НЕ, элемента ИЛИ-НЕ и с управляющим входом третьего коммутатора, второй вход которого подключен к первому входу элемента ИЛИ-НЕ и к инверсному выходу второго D-триггера, информационный вход которого соединен со вторым выводом первого резистора и через четвертый резистор и второй конденсатор соединен с общей шиной, второй вывод первого конденсатора соединен с общей шиной, выход элемента ИЛИ-НЕ соединен с первым входом первого коммутатора, выход которого подключен ко второму выводу третьего резистора, шина счетных сигналов соединена с входом второго инвертора, выход второго элемента И-НЕ соединен с первой выходной шиной.

| ТРЕХСТАБИЛЬНЫЙ СЧЕТНЫЙ ТРИГГЕР (ВАРИАНТЫ) | 1993 |

|

RU2093955C1 |

| Трехстабильный счетный триггер | 1975 |

|

SU585591A1 |

| Счетный элемент с контролем | 1990 |

|

SU1765889A1 |

| US 6100739, 08.08.2000 | |||

| БУКРЕЕВ И.Н., и др., Микроэлектронные схемы цифровых устройств, Москва, Радио и связь, 1990, с.257, рис.6.24а. | |||

Авторы

Даты

2005-04-20—Публикация

2003-09-22—Подача