множимого соответственно, а выход первого элемента И t -го одноразрядного норма-пизатора соединен с пе вым выходом i -го одноразрядного нормализатора, три входа второго эл мента И L -го одноразрядного норма лизатора соединены с L +2 Ц разрядами регистра обратного код множимого соответственно, а выход второго элемента И i -го одноразрядного нормализатора соединен с первым входом элемента ИЛИ L -го одноразрядного нормализатора, три входа третьего элемента И i,-ro одноразрядного нормализатора соединены cri+IJ.LlJ разрядами регистра обратного кода множимого соответственно, а выход третьего эл мента И L -го одноразрядного норма лизатора соединен с вторым входом элемента ИЛИ i -го одноразрядного нормализатора, выход которого соединен с вторым выходом L -го однора:зрядного нормализатора, выходы блока анализа старшего разряда и (h+t) одноразрядных нормализаторов соединены соответственно с входами регистра обратного кода множимого, информационные входы регистра множи мого, регистра обратного кода множимого и регистру множителя соединены соответственно с входами прямо го золотого 1-кода множимого, инверсного значения, золотого 1-кода множимого, прямого золотого 1-кода множителя,, являющимися первыми тремя входами устройства, четвертый и пятый входы которого, являющиеся соответственно входом Пуск и входом синхронизации, соединены с первым и вторым входами дешифратора ми роопераций программного блока управ ления собтветственно, входы разреше ния записи информации регистра множимого, регистра обратного кода мно жимого и регистра множителя соединены с первым выходом дешифратора микроопераций программного блока уп равления, вход разрешения записи ча тично нормализованной информации регистра обратного kc«a множимого соединен с вторым выходом дешифрато ра микроопераций программного блока управления, вход сдвига регистра множителя, управляющий вход табличного умножителя соединены с третьим выходом дешифратора микроопераций .программного блока управления, вы5.9 ход третьего младшего разряда регистра множителя соединен с третьим информационнымвходом табличного умножителя, выход которого соединен с вторыми входами элементов И четвертой группы и с третьим входом дешифратора микроопераций программного блока управления, выходы второго блока контроля соединены с .четвертым входом дешифратора микроопераций программного блока управления, а входы первого и третьего блоков контроля соединены с вторым входом элемента И, первый вход которого соединен с четвертым выходом дешифратора микроопераций программного блока управления, а выход соединен с первым выходом устройстваТ выходы элементов И четьфех групп соединены с входами элемента ИЛИ, выход которого соединен с первым входом сумматора, которьй содержит .регистр суммы, блок информации, реГистр коррекции, элемент И, элемент ИЛИ, регистр переносов, блок конца суммирования, полусумматор, блок контроля сумматора, выход и вход которого соединены соответственно с первым выходом сумматора, являющимся BTopbiM выходом устройства, и первым выходом полусумматора, первый и второй входы которого соединены соответственно с первым входом ре- . гистра суммы и первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента И, первый и второй входыкоторого соединены соответственно с выходом регистра коррекции и выходом регистра суммы, выход элемента ИЛИ соединен с вторым входом регистра переносов, первьй вход которого соединен с первым . входом сумматора, выход регистра . переносов соединен с входом блока конца суммирования, выход которого соединен с выходом регистра суммы с. рторым выходом сумматора, являющимся третьим выходом устройства, с входом блока конца информации, выход которого соединен с четвертым выходом сумматора, и с входом блока нормализации, выход которого соединен с вторым входом регистра суммы, управляющие входы регистра суммы соединены с третьим, пятым и шестым выходами дешифратора микроопераций программного блока управления соответственно, управляющие входы регистра

переносов соединены с девятым выходами дешифратора микроопераций программного блока управления соответственно, управляющий вход элемента И сумматора соединен с восьмым выходом дешифратора микроопераций прог . граммного блока управления, управляюпщй вход полусумматора соединен с седьмым выходом дешифратора микроопераций программного блока управления, а третий и четвертьм выходы

сумматора соединены с пятым и шестым входами дешифратора микроопераций программного блока управления соотвенственно, причем в программном блоке управления седьмой и восьмой входы дешифратора микроопераций соединены с первым и вторым выходами неполного дешифратора соответственно, вход которого соединен с выходом счетчика, вход которого соединен с девятым выходом дешифратора микроопераций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1986 |

|

SU1339551A1 |

| Устройство для умножения | 1983 |

|

SU1200280A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| КОНВЕЙЕРНЫЙ АРИФМЕТИЧЕСКИЙ УМНОЖИТЕЛЬ | 2013 |

|

RU2546072C1 |

| Устройство для вычисления сумм произведений | 1973 |

|

SU480077A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее регистр множимого, регистр множителя, табличный умножитель, первый и второй блоки контроля, сумматор, содержащий блок нормализации, а также три группы элементов И, первые входы которых соединены с входом первого блока контроля и с выходом регистра множимого, а вторые входы - с выходом табличного умножителя, первый и второй информационные входы которого соединены соответственно с выходами двух младших разрядов регистра множителя, выход которого соединен с входом второго блока контроля, о т л и ч аю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены регистр обратного ко да множимого, третий блок контроля, четвертая группа элементов И, элемент ИЛИ, элемент И, программный блок управления, вьтолненный на дешифраторе микроопераций, неполном дешифраторе и счетчике, и блок преобразования золотого 1-кода множимого в обратный код, включающий в себя блок анализа старшего разряда, вьтолненный на триггере, элементе И, элементе НЕ, элементе ИЛИ, и (ш-1) одноразрядных нормализаторов, каждый из которых вьшолнен на трех элементах И и элементе ИЛИ, выход регистра обратного кода множимого соединен с входом третьего блока контроля, с первыми входами элементов И четвертой группы и с входом блока преобразования золотого 1-кода множимого в обратный код,причем первый и второй входы элемента И блока анализа старшего, разряда соединены -2J и -3j разрядами регистра обратного кода множимого, а третий вход элемента И блока анализа старшего разряда соединен с инверсным выходом триггера, выход элемента И блока анализа старшего разряда соединен с первым СО X) выходом блока анализа старшего разряда и с входом элемента НЕ, выход которого соединен с первым входом сд элемента ИЛИ, второй вход которого со соединен с прямым выходом триггера, первый вход которого сЬединен с шиной нулевого потенциала, а второй с первым выходом дешифратора микроопераций программного блока управления, выход элемента ШШ блока анапит за старшего разряда соединен с вторым выходом блока анализа старшего разреда, три входа первого элемента И 1-го одноразрядного нормализатора соединены с fl) , l-lj, 1-2, разрядами регистра обратного кода

1

Изобретение относится к вычислительной технике, предназначено для умножения многоразрядных параллельных золотых 1-кодов и может быть использовано в отказоустойчивых про цессорах обработки данных.

Известно устройство для умножения на три разряда множителя, содержащее регистр множимого, регистр множителя, дополнительный регистр, группу клапанов, сумматор, схему управления умножением на три разряда C1JI .

Недостатком устройства является невозможность умножения золотых 1-кодов, обладающих высокой ошибкообнаруживающей способностью, используемой для контроля операции умножения.

Наиболее близким по технической сущности к-изобретению является устройство для умножения, содержаще регистр множимого, регистр множителя, первый и второй блоки контроля, блок таблицы умножения, сумматор и три греппы элементов И, первые входы которых соединены с выходом регистра множимого и выходом первого .блока контроля, а вторые входы - с выходом блока таблицы умножения,первого и второй входы которого соединен с выходами двух младших разрядов регистра множителя, выход которого соединен с входом блока контроля 2

Недостатком устройства является низкое быстродействие его работы при умножении аолотых 1-кодов, обусловленное большим количеством тактов сложения частичных произведений с текущей суммой частичных произведений.

Цель изобретения - увеличение быстродействия работы устройства при умножении чисел в золотой 1системе счисления за счет умножения множимого одновременно на 3 разря-. да множителя.

Поставленная цель достигается тем, что в устройство для умножения, содержащее регистр множимого, регистр множителя, первый и второй блоки контроля, табличный умножитель сумматор, содержащий блок нормализации, а также три группы элементов И, первые входы которьпс соединены с выходом регистра множимого и входом первого блока контроля, а вторые входы - с вькодом табличного умножителя, первый и второй информационные входы которого соединены соответственно с выходами двух мпад- ших разрядов регистра множителя, выход которого соединен с входом второго блока контроля, I введены регистр обратного кода множимого, третий блок контроля, элемент И,, четвертая группа элементов И, элемент ИЛИ, программный блок управления, вьшол, ненный на дешифраторе микроопераций, неполном дешифраторе и счетчике, и блок преобразования золотого 1-кода множимого в обратный код, включающий в себя блок анализа стар шего разряда, выполненный на триггере, элементе И, элементе НЕ, элементе ИЛИ, и (и +1) одноразрядных нормализаторов, каждый из которых вьшолнен на трех элементах И и эле3

менте РШИ, выход регистра обратного кода множимого соединен с входом третьего блока контроля, с первыми входами элементов И четвертой группы и с входом блока преобразования золотого 1-кода множимого в обратный код, причем первьй и второй входы элемента И блока анализа старшего разряда соединены cfrt -2J разрядами регистра обратного кода множимого, а третий вход элемента/И блока анализа старшего разряда соединен с инверсным выходом триггера,

,выход элемента И блока анализа старшего разряда и с входом элемента НЕ, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с прямым выходом триггера, первый вход которого соединен с шиной нулевого потенциала, а второй - с. первым выходом дешифратора микроопераций программного блока управления, выход элемента ИЛИ блока анализа старшего разряда соединен с вторым выходом блока анализа старшего разряда, три входа первого элемента И L -го одноразрядного нормализатора соединен , ( t 2J разрядами регистра обратного кода множимого соответственно, а выход первого элемента И L -го одноразрядного нормализатора соединен с первым выходом L -го одноразрядного нормализатора, три входа второго элемента И L -го одноразрядного нормализатора соединены , + 1J, 1 J разрядами регистра обратного кода множимого соответственно, а выход второго элемента И L -го одноразрядного нормализатора соединен с первым входом элемента ИЛИ

L -го одноразрядного нормализатора, три входа третьего элемента И i-ro одноразрядного нормализатора соединены с LL +1J, си , LL-IJ разрядами регистра обратного кода множимого соответственно, а выход третьего

.элемента И L-го одноразрядного нормализатора соединен с вторым входом элемента ИЛИ L го одноразрядного нормализатора, выход которого соединен с вторым выходом t-го одноразрядного нормализатора, выходы блока анализа старшего разряда и(и +1 одноразрядных нормализаторов соединены с входами регистра обратного кода множимого, информационные регистра множимого.

30в594

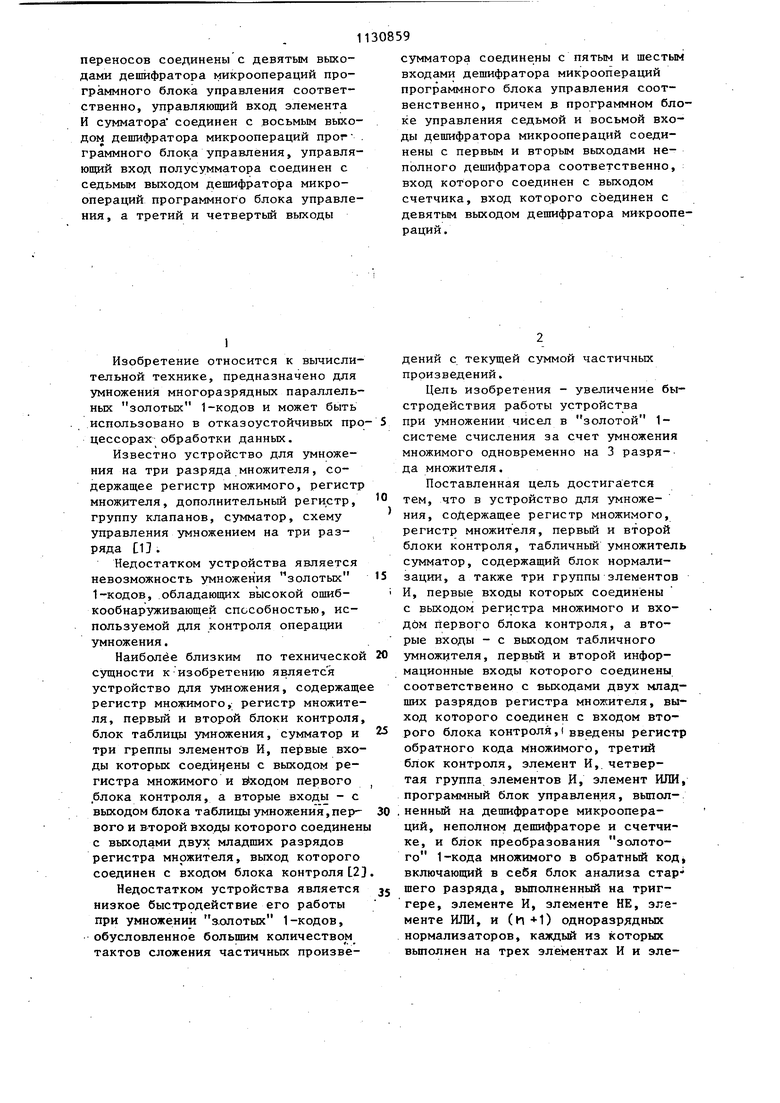

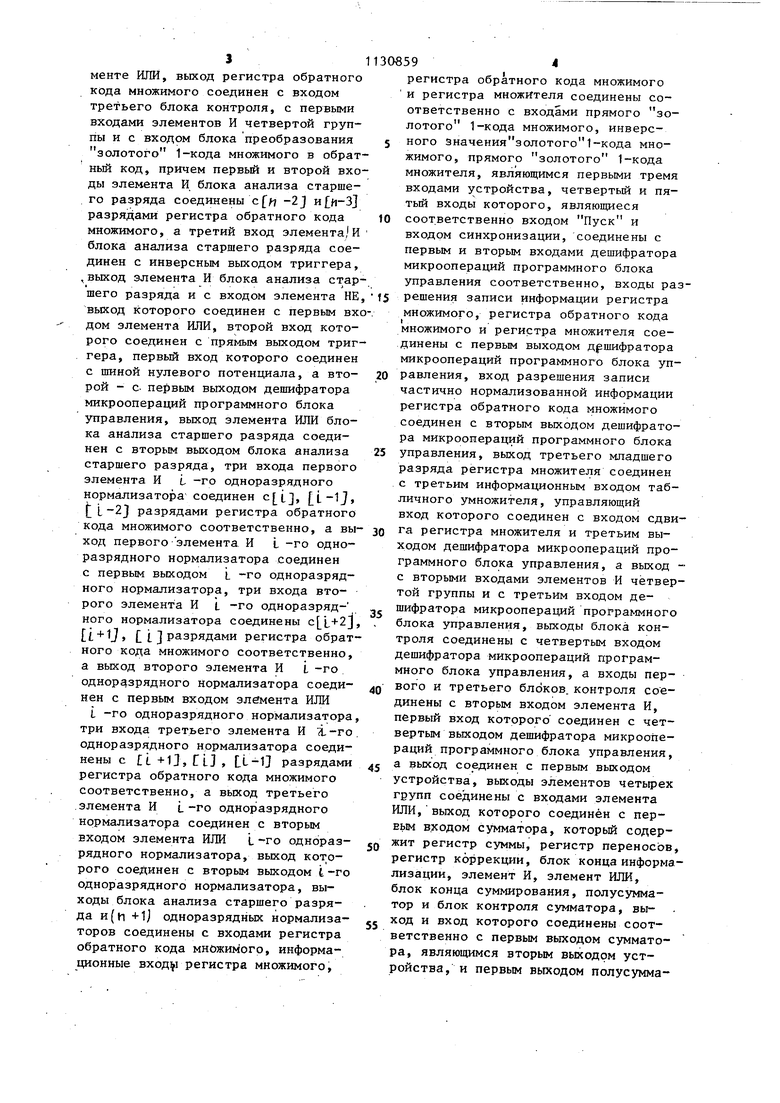

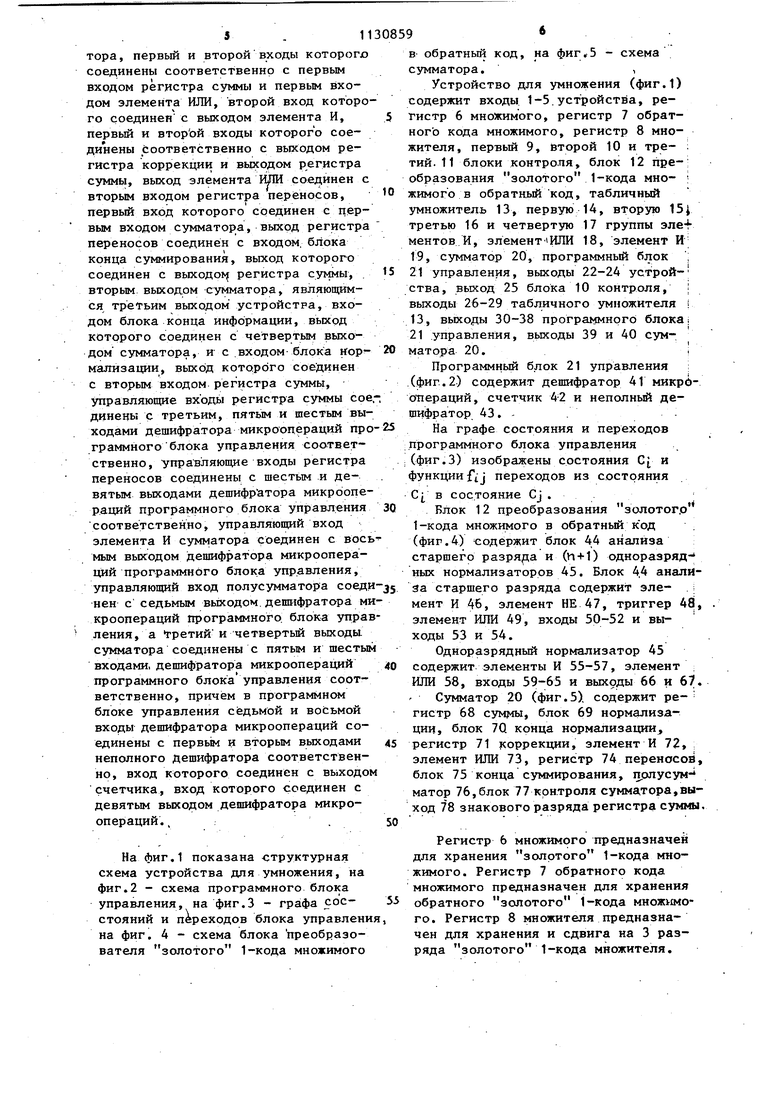

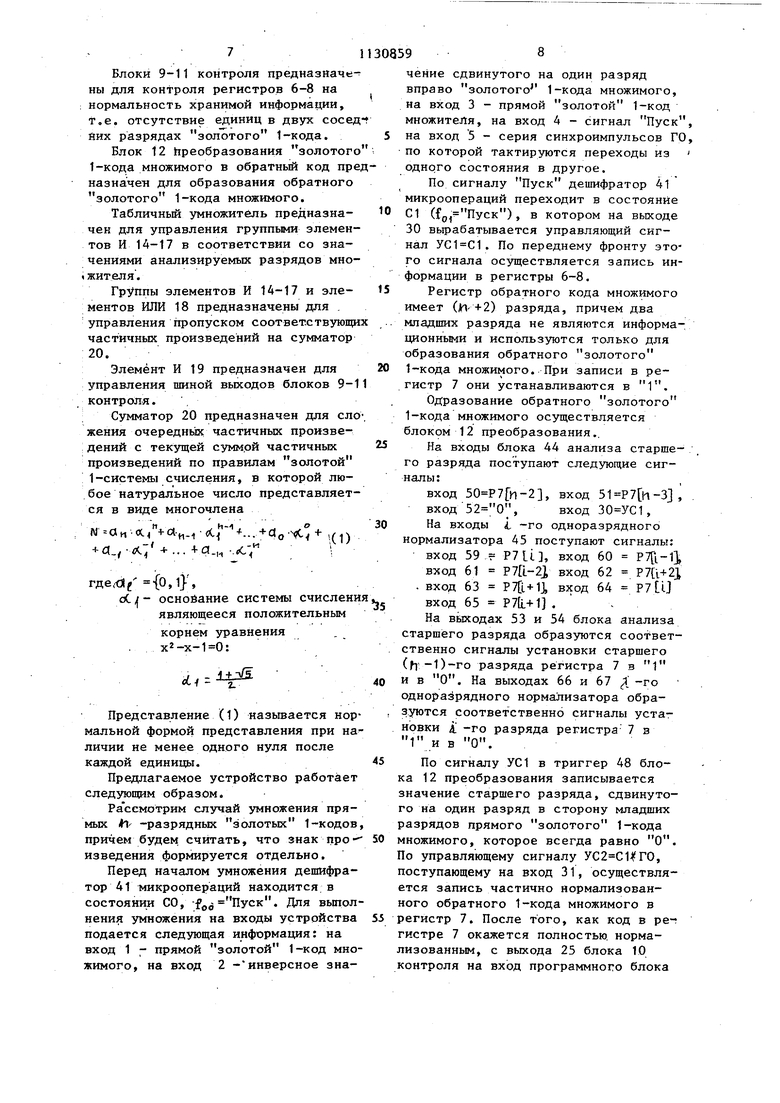

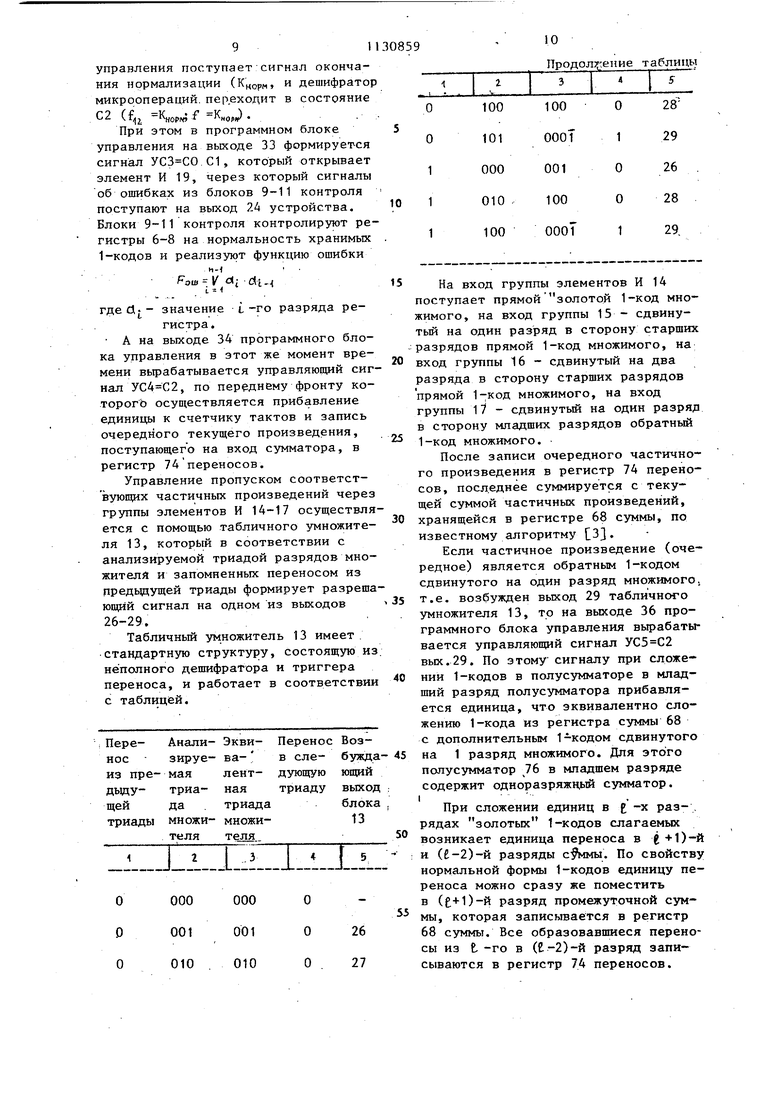

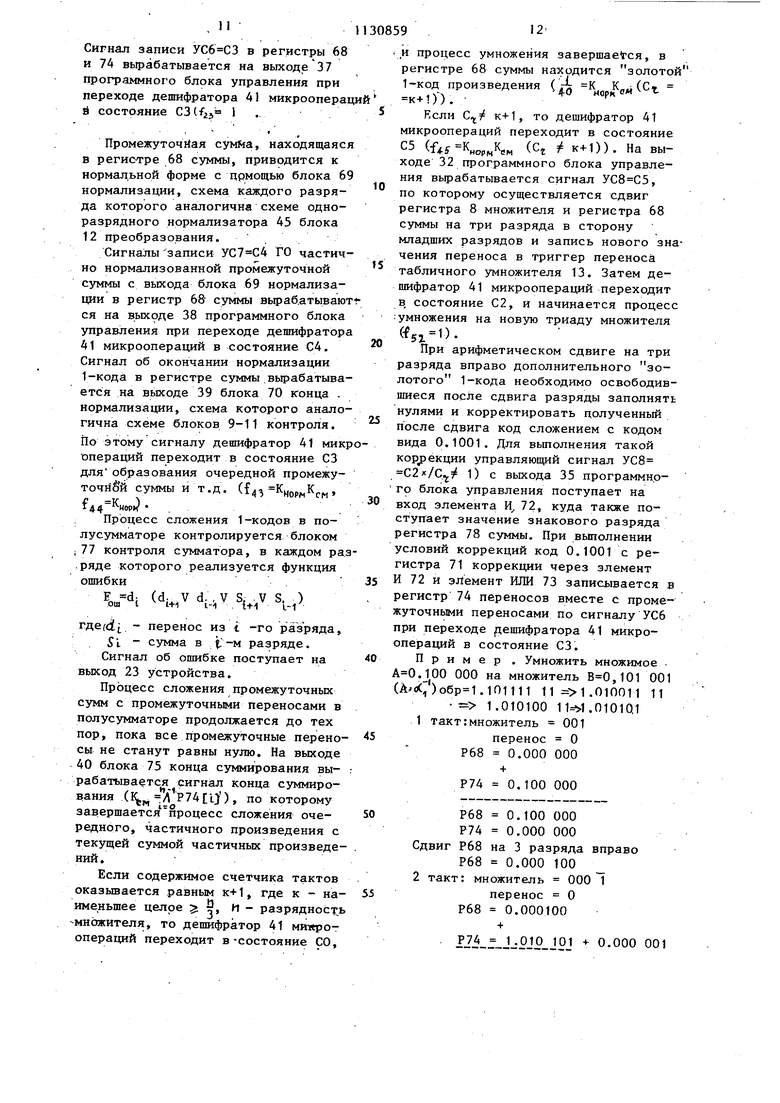

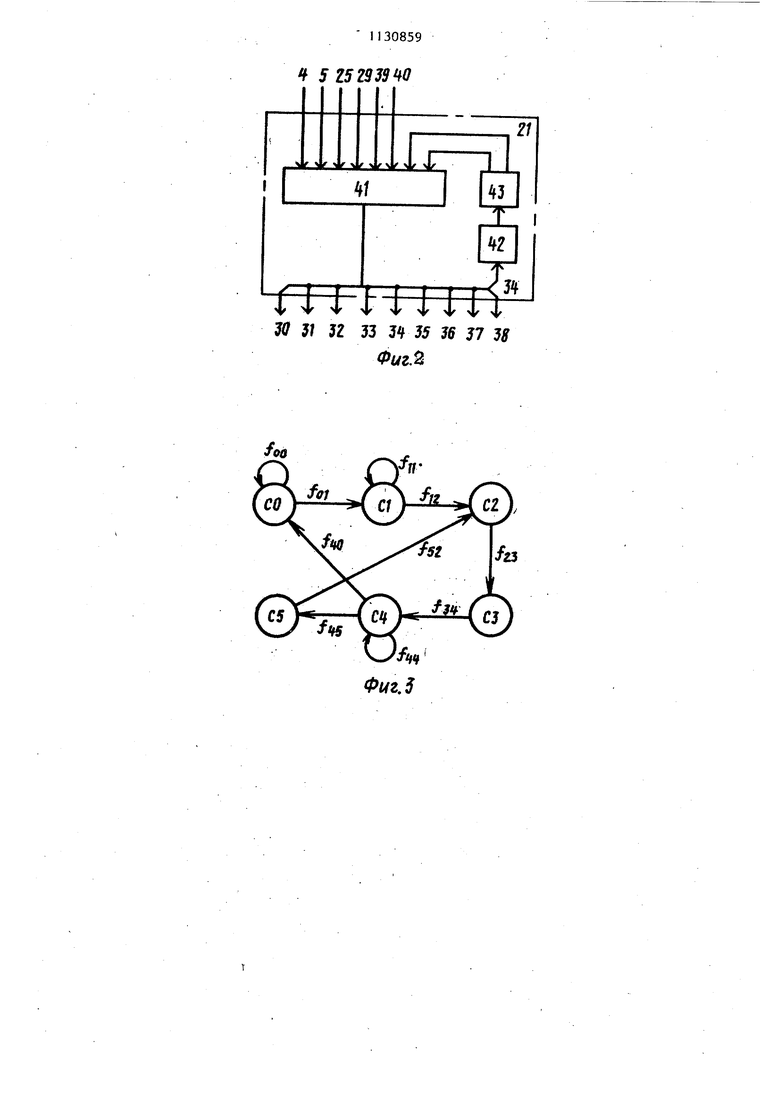

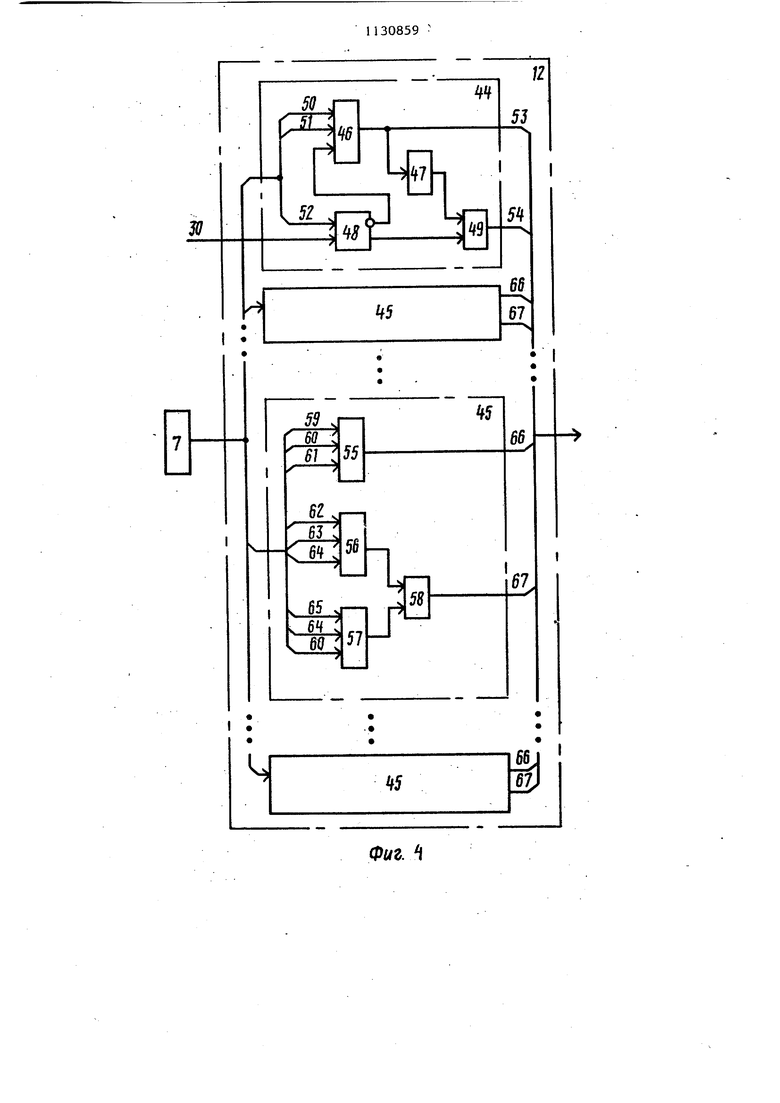

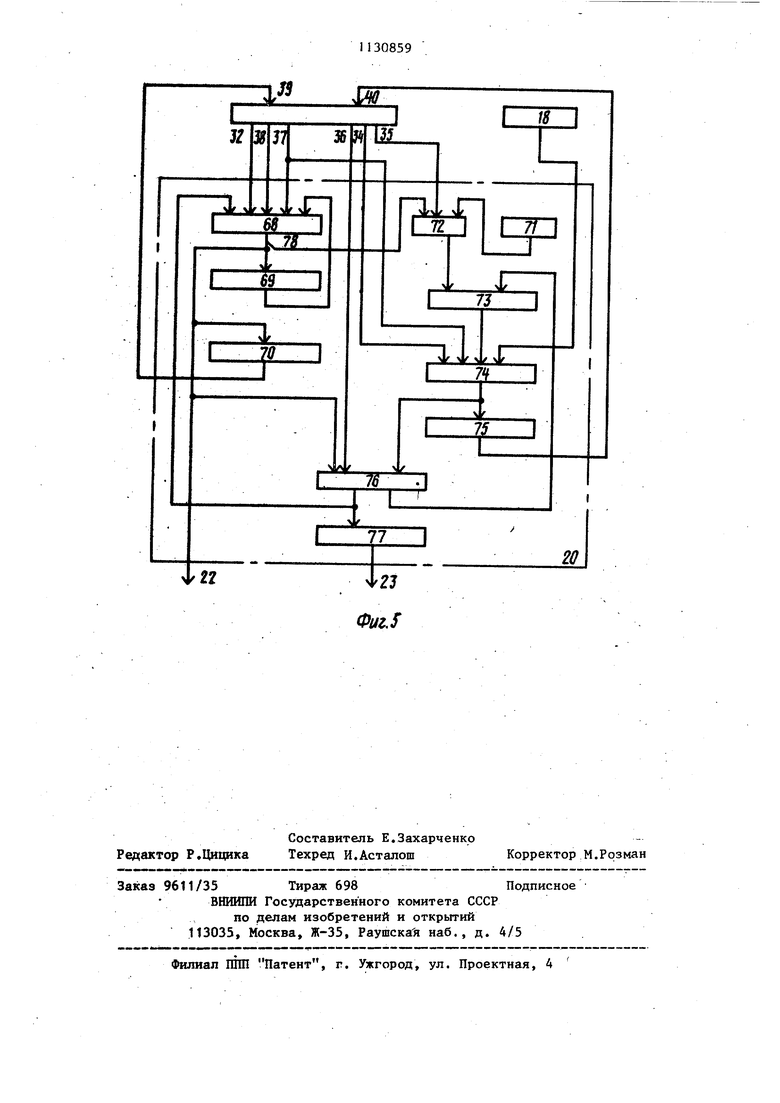

регистра обратного кода множимого и регистра множителя соединены соответственно с входами прямого золотого 1-кода множимого, инверс5 ного значения золотого 1-кода множимого, прямого золотого 1-кода множителя, являющимся первыми тремя входами устройства, четвертый и пятый входы которого, являющиеся соответственно входом Пуск и входом синхронизации, соединены с первым и вторым входами дешифратора микроопераций программного блока управления соответственно, входы разрешения записи информации регистра множимого, регистра обратного кода множимого и регистра множителя соединены с первым выходом дешифратора микроопераций программного блока управления, вход разрешения записи частично нормализованной информации регистра обратного кода множимого соединен с вторым выходом дешифратора микроопераций программного блока управления, выход третьего младшего разряда регистра множителя соединен с третьим информационным входом табличного умножителя, управляющий вход которого соединен с входом сдвига регистра множителя и третьим выходом дешифратора микроопераций программного блока управления, а выход с вторыми входами элементов И четвертой группы и с третьим входом дешифратора микроопераций программного блока управления, выходы блока контроля соединены с четвертым входом дешифратора микроопераций программного блока управления, а входы первого и третьего блоков, контроля соединены с вторым входом элемента И, первый вход которого соединен с четвертым выходом дешифратора микроопераций программного блока управления, а выход соединен с первым выходом устройства, выходы элементов четырех групп соединены с входами элемента ИЛИ,выход которого соединён с первь1м входом сумматора, которьй содержит регистр суммы, регистр переносов, регистр коррекции, блок конца информализации, элемент И, элемент ИЛИ, блок конца суммирования, полусумматор и блок контроля сумматора, выход и вход которого соединены соответственно с первым выходом сумматора, являющимся вторым выходом устройства, и первым выходом полусумматора, первый и второйвходы которого соединены соответственно с первым входом регистра суммы и первым входом элемента ИЛИ, второй вход которо го соединен с выходом элемента И, первый и второй входы которого соединены соответственно с выходом регистра коррекции и выходом регистра суммы, выход элемента ИЛИ соединен с вторым входом регистра пер1еносов, первый вход которого соединен с первым входом сумматора, выход регистра переносов соединён с входом, блока конца суммирования, выход которого соединен с вькодо регистра , вторым, выходом сумматора, являющимся третьим выходом устройства, входом блока конца информации, выход которого соединен с четвертым выходом сумматора, и с .входом-блока нормализации, выход которого соединен с вторьш входом регистра суммы, управляющие входы регистра суммы со динены с третьим, пятым и шестым вы ходами дешифратора микрооп.ераций пр граммного блока управления соответственно, управляющие входы регистра переносов соединены с шестым и девятым выходами дешифратора микроопе раций программного блока управления соответственно, управляющий вход элемента И сумматора соединен с вос мым выходом дешифратора микроопераций программного блока управления, управляющий вход полусумматора соед нен с седьмым выходом дешифратора м кроопераций программного блока упра ления, а третийи четвертый выходы сумматора соединены с пятьм и шесты входами, дешифратора микроопераций программного блока управления соответственно, причем в программном блоке управления седьмой и восьмой входы дешифратора микроопераций соединены с первь1м и вторым выходами неполного Дешифратора соответственно, вход которого соединен с выходо счетчика, вход которого соединен с девятым выходом дешифратора микроопераций. ,. На фиг.1 показана структурная схема устройства дпя умножения, на фиг.2 - схема программного блока управления, на фиг.3 - графа сосстояний и переходов блока управлени на фиг. 4 - схема блока преобразователя золотого 1-кода множимого в- обратный код, на фиг.-5 - схема сумматора., Устройство для умножения (фиг.1) содеряшт входы 1-5.устройства, регистр 6 множимого, регистр 7 обратного кода множимого, регистр 8 множителя, первый 9, второй 10 и тре- ; тий. 11 блоки контроля, блок 12 lipe-; образования золотого 1-кода мно- : жимого в обратный код, табличный умножитель 13, первую 14, вторую 15 третью 16 и четвертую 17 группы эле-f ментов И, элемент ИЛИ 18, элемент И 19, сумматор 20, программный блок ; 21 управления, выходы 22-24 устройства, выход 25 блока 10 контроля, выходы 26-29 табличного умножителя i 13, выходы 30-38 программного блока, 21 .управления, выходы 39 и 40 сумматора 20. Программный блок 21 управления ; .(фиг.2) содержит дешифратор 41 микрбонераций, счетчик 4-2 и неполный дешифратор 43 .На графе состояния и переходов .программного блока управления (фиг.З) изображены состояния G и функции ft j переходов из состояния С в сос.тояние Cj . . Блок 12 преобразования золотогр 1-кода множимого в обратный код (фиг.4) содержит блок 44 анализа старшего разряда и (п + 1) одноразряд- ных нормализаторов 45. Блок 44 анализа старшего разряда содержит эле- i мент И 46, элемент НЕ 47, триггер 48, элемент ИЛИ 49, входы 50-52 и выходы 53 и 54. Одноразрядный нормализатор 45 содержит элементы И 55-57, элемент ШШ 58, входы 59-65 и выхрды 66 и 67. Сумматор 20 (фиг.5), содержит ре- гистр 68 суммы, блок 69 нормализации, блок 7Q конца нормализации, регистр 71 коррекции, элемент И 72, элемент ИЛИ 73, регистр 74 переносоа, блок 75 конца суммирования, прлусум- матор 76,блок 77 контроля суммятора,выход 78 знакового разряда регистра суммы. Регистр 6 множимого предназначен для хранения золотого 1-кода множимого. Регистр 7 обратного кода множимого предназначен для хранения обратного золотого 1-кода множимого. Регистр 8 множителя предназначен для хранения и сдвига на 3 разряда золотого 1-кода множителя. 7 Блоки 9-11 контроля предназначены для контроля регистров 6-8 на : нормальность хранимой информации, т,е, отсутствие единиц в двух сосед йих разрядах золотого 1-кода. Блок 12 йреобразования золотого 1-кода множимого в обратный код пре назначен для образования обратного золотого 1-кода множимого. Табличный умножитель предназначен для управления группыми элементов И 14-17 в соответствии со значениями анализируемых разрядов мно(жителя. Группы элементов И 14-17 и элементов ИЛИ 18 предназначены для , управления пропуском соответствующ частичных произведений на сумматор 20. Элемент И 19 предназначен для управления шиной выходов блоков 9контроля. : Сумматор 20 предназначен для ел жения очередных частичных произведений с текущей суммой частичных произведений по правилам золотой 1-системы счисления, В которой любое натуральное число представляет ся в виде многочлена . J и-1 .«.j4a..-(, ...+do-s c + ,(,) .-л;+ ...+а-„ -.; где,,l}, основание системы счислен являющееся положительным корнем уравнения х2-х-1 0: i -Представление (1) назьтается нор мальной формой представления при на личии не менее одного нуля после каждой единицы. Предлагаемое устройство работает следующим образом. Рассмотрим случай умножения прямых ih -разрядньк золотых 1-кодов причем будем считать, что знак про изведения формируется отдельно. Перед началом умножения дешифратор 41 микроопераций находится в состоянии СО, . Для выпол нения умножения на входы устройства подается следующая информация: на вход 1 - прямой золотой 1-код мно жимого, на вход 2 -инверсное зна9чение сдвинутого на один разряд вправо золотого 1-кода множимого, на вход 3 - прямой золотой 1-код множителя, на вход 4 - сигнал Пуск, на вход 5 - серия синхроимпульсов ГО, по которой тактируются переходы из одного состояния в другое. По сигналу Пуск дешифратор 4l микроопераций переходит в состояние С1 (), в котором на выходе 30 вьфабатывается управляющий сигнал . По переднему фронту этого сигнала осуществляется запись информации в регистры 6-8. Регистр обратного кода множимого имеет (И- +2) разряда, причем два младших разряда не являются информационными и используются только для образования обратного золотого 1-кода множимого. При записи в регистр 7 они устанавливаются в 1. Одразование обратного золотого 1-кода множимого осуществляется блоком 12 преобразования.. На входы блока 44 анализа старшего разряда поступают следующие си1- налы: вход , вход . вход52 0, вход , На входы i -го одноразрядного нормализатора 45 поступают сигналы: вход 59 P7Li., вход 60 , вход 61 P7U-2J, вход 62 . вход 63 , вход 64 P/tlJ вход 65 - Р7Ь.+ 1 .На вькодах 53 и 54 блока анализа старшего разряда образуются соответственно сигналы установки старшего (fr-1)-го разряда регистра 7 в 1 и в О. На выходах 66 и 67 Д -го одноразрядного нормализатора образуются соответственно сигналы установки А -го разряда регистра 7 в 1 и в О. По сигналу УС1 в триггер 48 блоа 12 преобразования записывается начение старшего разряда, сдвинутоо на один разряд в сторону младших азрядов прямого золотого 1-кода ножимого, которое всегда равно О. о управляющему сигналу , оступающему на вход 31, осуществлятся запись частично нормализованого обратного 1-кода множимого в егистр 7. После того, как код в ре-г истре 7 окажется полностью, нормаизованным, с выхода 25 блока 10 онтроля на вход программного блока 9 управления поступает сигнал окончания нормализации (Кцорм, и дешифрато микроопераций, пер.еходит в состояние 2 (f KHO(W f HOI) . При этом в программном блоке управления на выходе 33 формируется сигнал С1, который открывает элемент И 19, через который сигналы об ошибках из блоков 9-11 контроля поступают на выход 24 устройства. Блоки 9-11 контроля контролируют ре гистры 6-8 на нормальность хранимых 1-кодов и реализуют функцию ошибки h-1 . FOW V(idi, где Д.- значение i,-го разряда регистра i А на выходе 34 программного блока управления в этот же момент времени вырабатывается управляюгций сиг нал 2, по переднему фронту которого осуществляется прибавление единицы к счетчику тактов и запись очередного текущего произведения, поступающего на вход сумматора, в регистр 74 переносов. Управление пропуском соответствующих частичных произведений через группы элементов И 14-17 осуществля ется с помощью табличного умножителя 13, который в соответствии с анализируемой триадой разрядов множителя и запомненных переносом из предьщущей триады формирует разреша ющий сигнал на одном из выходов 26-29. Табличньй умножитель 13 имеет . стандартную структуру, состоящую из неполного дешифратора и триггера переноса, и работает в соответствии с таблицей. Пере- Анали- Экви- ПереносВознос - зируе- ва- в еле-бужда из пре- мая лент- дующуюющий дьщу- триа- ная триадувыход щей да . триадаблока триады множи- множи- 13 теля теля i..I-i..l..i-Lf.. 9 1Тродол: ;епие таблицы На вход группы элементов И 14 поступает прямой золотой 1-код множимого, на вход группы 15 - сдвинутый на один разряд в сторону старших разрядов прямой 1-код множимого, на вход группы 16 - сдвинутый на два разряда в сторону старших разрядов прямой 1-код множимого, на вход группы 17 - сдвинутый на один разряд в сторону младших разрядов обратный 1-код множимого. После записи очередного частичного произведения в регистр 74 переносов, последнее суммируется с текущей суммой частичных произведений, хранящейся в регистре 68 суммы, по известному алгоритму СЗД. Если частичное произведение (очередное) является обратным 1-кодом сдвинутого на один разряд множимого, т.е. возбужден выход 29 табличного умножителя 13, то на выходе 36 программного блока управления вырабатывается управляющий сигнал вых.29. По этому сигналу при сложении 1-кодов в полусумматоре в младший разряд полусумматора прибавляется единица, что эквивалентно сложению 1-кода из регистра суммы 68 с дополнительным 1-кодом сдвинутого на 1 разряд множимого. Для этого полусумматор 76 в младшем разряде содержит одноразряжный сумматор. При сложении единиц в -х раз- . рядах золотых 1-кодов слагаемых возникает единица переноса в g +1)-й н (-2)-и разряды . По свойству нормальной формы 1-кодов единицу переноса можно сразу же поместить в (+1)-й разряд промежуточной суммы, которая записывается в регистр 68 суммы. Все образовавшиеся переносы из t-го в (-2)-и разряд записываются в регистр 74 переносов. Сигнал записи в регистры 68 и 74 вырабатывается на выходе 37 программного блока управления при переходе дешифратора 41 микрооперац и состояние С3(2з 1 . Промежуточная сумйа, находящаяся в регис-тре 68 суммы, приводится к нормальной форме с црмощью блока 69 нормализации, схема каждого разряда которого аналогична схеме одноразрядного нормализатора 45 блока 12 преобразования. Сигналызаписи ГО частично нормализованной промежуточной суммы с выхода блока 69 нормализации в регистр 68 суммы вьфабдтывают ся на выходе 38 программного блока управления при переходе дешифратора 41 микроопераций в состояние С4. Сигнал об окончании нормализации 1-кода в регистре суммы .вырабатывается на выходе 39 блока 70 конца . нормализации, схема которого аналогична схеме блоков 9-11 контроля. По этому сигналу дешифратор 41 мик операций переходит в состояние СЗ для образования очередной промежуТОЧЙ§Й суммы и т.д. (43 НОР|Ч СМ г -If 1 144 W .. Процесс сложения 1-кодов в полусумматоре контролируется блоком i 77 контроля сумматора, в каждом ра .ряде которого реализуется функция ошибки F di (d. V d. , V S. .V S. ) ОШ t l-H 1-1 . t-H 1-1 гдег4 - перенос из t -го разряда, Si - сумма в i-м разряде. Сигнал об ошибке поступает на выход 23 устройства. Процесс сложения промежуточных сумм с промежуточными переносами в полусумматоре продолжается до тех пор, пока все промежуточные переносы не станут равны нулю. На выходе 40 блока 75 конца суммирования вырабатывается сигнал конца суммирования (Bi,XP74fl}), по которому завершается процесс сложения очередного, частичного произведения с текущей суммой частичных произведеЕсли содержимое счетчика тактов оказьшается равным к+1, где к - наименьшее целое 9, И - разрядности -множителя, то дешифратор 41 микроопераций переходит в-состояние СО, ,и процесс умножения завершаемся, в регистре 68 суммы находится золотой 1-код произведения ( К К„ (С к+1)). Если С, к+1, то дешифратор 41 микроопераций переходит в состояние С5 ( КН„Р„К,„ (Ct 7 к-И)). На выходе 32 программного блока управления вырабатывается сигнал , по которому осуществляется сдвиг регистра 8 множителя и регистра 68 суммы на три разряда в сторону младших разрядов и запись нового значения переноса в триггер переноса табличного умножителя 13. Затем дешифратор 41 микроопераций переходит ц состояние С2, и начинается процесс умножения на новую триаду множителя ()При арифметическом сдвиге на три разряда вправо дополнительного золотого 1-кода необходимо освободившиеся после сдвига разряды заполнять нулями и корректировать полученный после сдвига код сложением с кодом вида 0.1001. Для вьтолнения такой коррекции управляющий сигнал УС8 С2х/с 1) с вькода 35 программнргр блока управления поступает на вход элемента И, 72, куда также поступает значение знакового разряда регистра 78 суммы. При вьтолнении условий коррекций код 0.1001 с регистра 71 коррекции через элемент И 72 и элемент ИЛИ 73 записывается в регистр 74 переносов вместе с промежуточными переносами по сигналу УС6 при переходе ;ешифратора 41 микроопераций в состояние СЗ. Пример . Умножить множимое .100 000 на множитель ,101 001 ((;).1П1111 11 1.010011 11 - 1.010100 .010101 1 такт:множитель 001 перенос О Р68 0.000 000 + Р74 0.100 000 Р68 0.100 000 Р74 0.000 000 Сдвиг Р68 на 3 разряда вправо Р68 0.000 100 2 такт: множитель 000 1 перенос О Р68 0.000100 -f . Р74 1.010 101 - 0.000 001 P68 1.011 010 1.100 010 + P74 0.000 001 P68 1.100 011 1.100 100,P Сдвиг P68 на 3 разряда Р68 1.000 100 3 такт: множитель 00 перенос 1 Р68 1.000 100 Р74 0.100 000 Р68 1.100 100 + Р74 0.100 100 Р68 000 + Р74 0.001 001 Р68 0.010 001 + Р74 0.000 010 Р68 0.010 011 0.010 100 Р74 0.000 000 Р68 0.010 100 - результат. При умножении 48-разрядных золотых 1-кодов минимальное быстродействие золотого устройства увеличивается в 1,37 раза по сравнению с известным устройством. Таким образом, введение новых блоков и функциональных связей по- зволяет увеличить быстродействие работы устройства при умножении чисел в золотой 1-системе счисления.

Ч 5 25293940

30 j; JZ 33 3 55 36 37 38 Фиг.

I I

IL

64

6t)

Фиг.

Фиг. 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Соловьев Г.И | |||

| Арифметические устройства ЭВМ | |||

| М., Энергия, 1978, с | |||

| Заслонка для русской печи | 1919 |

|

SU145A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-23—Публикация

1983-09-30—Подача