Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для создания арифметико-логических устройств, для создания быстродействующих и экономичных цифровых устройств суммирования и вычитания чисел в прямых кодах.

Известна "Схема цифрового сумматора" (№ 99109089/09, от 04.07.1997 г.), позволяющая выполнять операцию сложения чисел в двоичной системе счисления.

Известно "Устройство для сложения" (№ 4892584/24, от 19.12.1990 г.), которое вычисляет сумму двоичных чисел.

В качестве прототипа выбрано "Устройство для вычисления модуля М-мерного вектора" (95104370/09, от 01.03.1995. Бюл N 15, 1997г.), которое выполняет операции суммирования и вычитания над М-мерными векторами.

Недостатком предложенных технических решений является низкая скорость выполнения операций сложения и вычитания, избыточность аппаратных средств устройства, сложный алгоритм работы.

Параллельный сумматор-вычитатель на элементах нейронной логики выполняет арифметические операции: суммирование и вычитание двоичных чисел в прямых кодах.

Технической задачей предлагаемого решения является повышение скорости выполнения арифметических операций, повышение надежности работы сумматора-вычитателя, уменьшение аппаратных средств, что ведет к упрощению комбинационных схем устройства, упрощение алгоритма работы устройства.

Решение задачи осуществляется тем, что параллельный сумматор-вычитатель на элементах нейронной логики, содержащий блок коммутации и сумматоров-вычитателей, блок управления, отличающиеся тем, что дополнительно введены: блок ввода чисел, блок регистра первого числа, блок регистра второго числа, блок регистра результата, причем информационный выход блока ввода чисел соединены с первым информационным входом блока регистра второго числа и с первым информационным входом блока регистра первого числа, второй информационный вход которого соединен с третьим информационным выходом блока управления, второй информационный выход которого соединен со вторым информационным входом блок регистра второго числа, информационный выход которого соединен со вторым информационным входом блок коммутации и сумматоров-вычитателей, первый информационный вход которого соединен с информационным выходом блока регистра первого числа, управляющий выход блока ввода чисел соединен с управляющим входом блока коммутации и сумматоров-вычитателей, информационный выход которого соединен с первым информационным входом блока регистра результата, второй информационный вход которого соединен с первым информационным выходом блока управления, первый и второй управляющие входы "СБРОС" и "ПУСК" блока управления являются внешними входами параллельного сумматора-вычитателя на элементах нейронной логики.

БВЧ - блок ввода чисел служит для ввода двоичных кодов операндов, знака операции и определения признака операции.

БРгПЧ - блок регистра первого числа служит для хранения двоичных кодов первого числа при выполнении арифметических операций.

БКСВ – блок коммутации и сумматоров-вычитателей двоичных чисел служит для выполнения операций суммирования и вычитания.

БРгВЧ - блок регистра второго числа служит для хранения двоичных кодов второго числа при выполнении арифметических операций.

БРгР - блок регистра результата служит для хранения суммы при сложении и разности при вычитании чисел, а также знака результата.

БУ - блок служит для управления устройством.

Алгоритм сложения чисел в прямых кодах позволяет получить результат в прямом коде. Сумма и разность двоичных чисел вычисляется в прямых кодах при параллельном сложении и вычитании кодов операндов. Знаковые разряды чисел и код операции определяют, какую операцию необходимо выполнить над числами с помощью операции суммы по модулю два. Если знаки одинаковые, то результат будет нуль, в этом случае выполняется арифметическая операция сложения. В противном случае результат будет единица, при этом выполняется операция вычитания. При суммировании результату присваивается знак первого числа. При вычитании результату присваивается знак большего по модулю числа.

На фиг. 1 изображена структурная схема параллельного сумматора-вычитателя на элементах нейронной логики.

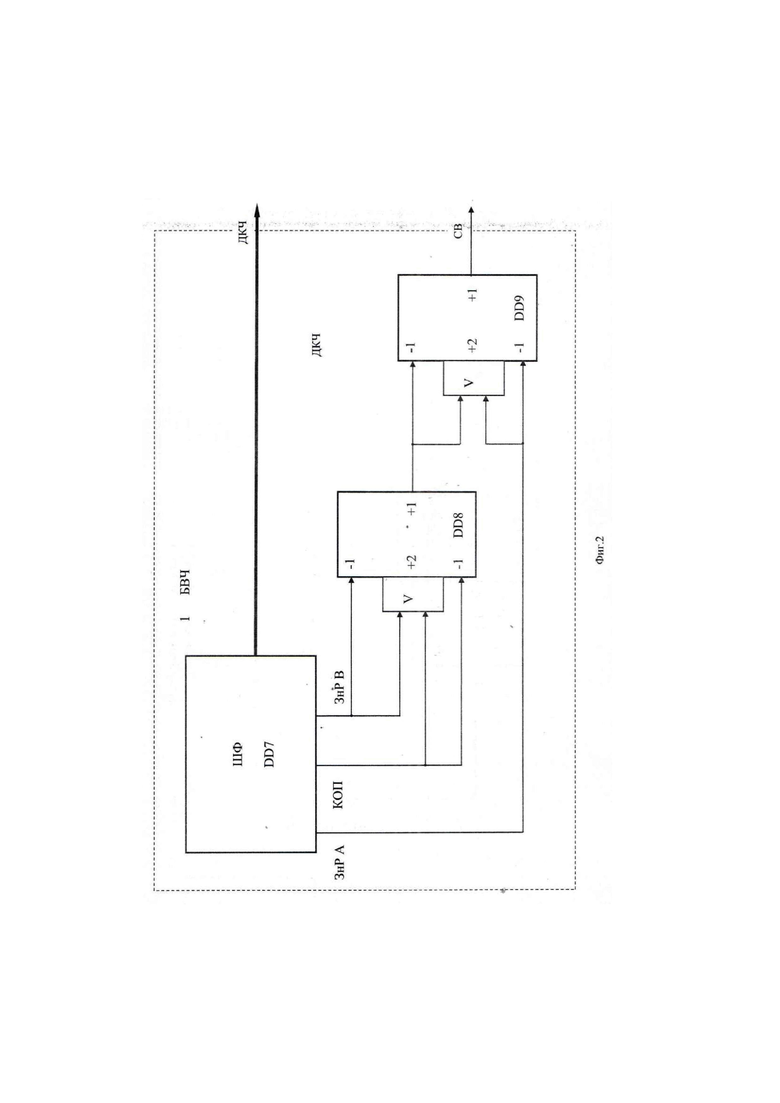

На фиг. 2 представлен вариант технической реализации блока ввода чисел.

На фиг. 3 представлена структурная схема определения знака результата, схема коммутации, сумматор-вычитатель.

На фиг. 4 показана структурная схема параллельного сумматора-вычитателя, схема определения знака результата.

На фиг. 5 представлен вариант технической реализации схемы определения знака результата.

На фиг. 6 представлен вариант технической реализации схемы коммутации и сумматор-вычитатель.

На фиг. 7 представлен вариант технической реализации блока регистра первого числа и блока регистра второго числа.

На фиг. 8 представлен вариант технической реализации блока регистра результата.

На фиг. 9 показана содержательная ГСА работы устройства.

На фиг. 10 показана размеченная ГСА работы устройства.

Параллельный сумматор-вычитатель на элементах нейронной логики содержит: блок ввода чисел, блок регистра первого числа, блок коммутации и сумматоров-вычитателей, блок регистра второго числа, блок регистра результата, блок управления, пороговые и нейроподобные элементы (фиг. 1).

Для описания алгоритма работы блока 6 управления используются следующие идентификаторы.

1. ДКЧ – двоичный код числа.

2. ДПЧ - двоичный код первого числа.

3. ДПЧ - двоичный код второго числа.

4. Ai – двоичный разряд первого числа.

5. Bi – двоичный разряд второго числа.

6. ЗмЗнР – заём из знакового разряда первого числа.

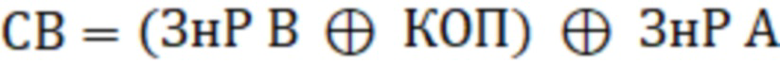

7. СВ – признак операции сигнал суммирования или вычитания.

8. РЕЗ – двоичные разряды результата.

9. УП – информационный сигнал управления блока регистра результата, включающий в себя сигналы: обнуления, синхронизации, разрешения записи, хранения, выдачи.

10. Pi+1/Zi+1 – сигнал переноса в старшие разряды при сложении или заёма из старших разрядов двоичных чисел при вычитании.

11. СУП – информационный сигнал управления работой блока регистра второго числа, включающий в себя сигналы: обнуления, синхронизации, разрешения записи, хранения, выдачи.

12. СУ – информационный сигнал управления работой блока регистра первого числа, включающий в себя сигналы: обнуления, синхронизации, разрешения записи, хранения, выдачи.

13. ЗнРА –- знаковый разряд первого числа.

14. ЗнРВ – знаковый разряд второго числа.

15. КОП – код операции.

16. БК – блок коммутации.

17. СУМ-ВЫЧ – сумматор-вычитатель.

18. Si – разряд суммы.

19. Ri – разряд разности

20. Pi – перенос в старший разряд при суммировании.

21. Zi – заём из старшего разряда при вычитании.

22. СБРОС – сигнал сброса (обнуления) всех комбинационных блоков параллельного сумматора-вычитателя.

23. ПУСК – сигнал начало работы сумматора-вычитателя.

Работа алгоритма упpавления устройства.

Содержательная ГСА упpавления приведена на фиг.9 и отражает работу блока упpавления (фиг.1).

В блоках 2 и 3 алгоритма по сигналам "У00" и "СБРОС:=1" выполняется установка в нулевое состояние всех элементов памяти устройства.

В блоке 4 алгоритма по команде "ПУСК" происходит установка в рабочее состояние всех блоков устройства (фиг.1).

В блоке 5 алгоритма с помощью шифратора ШР осуществляется ввод в сумматор-вычитатель десятичных чисел А10, В10 со своими знаками ЗнА, ЗнВ (фиг.2).

В блоке 6 алгоритма по операции суммы по модулю два знаковых разрядов чисел Зн Р В, Зн Р А и кода операции КОП определяется признак операции сигнал суммирование или вычитание СВ. Если сигнал СВ=0, то вычисляется сумма чисел, если СВ=1, то это выполняется операция вычитания чисел (фиг.2).

суммы по модулю два знаковых разрядов чисел Зн Р В, Зн Р А и кода операции КОП определяется признак операции сигнал суммирование или вычитание СВ. Если сигнал СВ=0, то вычисляется сумма чисел, если СВ=1, то это выполняется операция вычитания чисел (фиг.2).

В блоке 7 алгоритма по командам: БРгПч:=ДКЧ, БРгВч:=ДКЧ, БКСВ:=СВ осуществляется загрузка в регистры блоков первого числа БРгПЧ, второго числа БРгВЧ двоичных кодов чисел ДКЧ и подача в блок коммутации и сумматоров-вычитателей БКСВ сигнала признака операции суммирования или вычитания СВ (фиг. 1, 3, 4).

В блоке 8 алгоритма по командам: БКСВ:=ДПЧ, БКСВ:=ДВЧ осуществляется подача в блок коммутации и сумматоров-вычитателей БКСВ двоичных разрядов первого ДПЧ и второго ДВЧ чисел (фиг. 4).

В блоке 9 алгоритма по командам: СУМ-ВЫЧ:=An, СУМ-ВЫЧ:=Bn, СУМ-ВЫЧ:=СВ на входы схемы сумматора-вычитателя СУМ-ВЫЧ осуществляется подача двоичных разрядов первого An и второго Bn чисел, и сигнала признака операции суммирования или вычитания СВ (фиг.4).

В блоке 10 алгоритма по командам: СОЗР:=ЗнР А, СОЗР:=ЗнР В, СОЗР:=СВ, СОЗР:=ЗмЗнР на входы схемы определения знака результата СОЗР поступают знаковые разряды первого ЗнР А числа, второго ЗнР В числа, сигнала признака операции суммирования или вычитания СВ, сигнал заёма из знакового разряда ЗмЗнР (фиг.5).

В блоке 11 алгоритма анализируется признак операции сигнал суммирование или вычитание СВ (фиг.2). Если признак операции СВ равен нулю, то выполняется операция сложение по модулю двоичных чисел. При этом осуществляется переход на блок 13 алгоритма. Если признак СВ равен единице, то выполняется операция вычитания из первого An числа второе Bn. При этом осуществляется переход на блок 12 алгоритма.

В блоке 12 алгоритма анализируется сигнал заёма из знакового разряда ЗмЗнР. Этот сигнал формируется при выполнении операции вычитании, от меньшего по модулю числа вычитается большее. В этом случае сигнал заёма из знакового разряда ЗмЗнР равен единице при этом осуществляется переход на 15 алгоритма. Если сигнал заёма из знакового разряда ЗмЗнР равен нулю, то выполняется операция суммирование чисел или от большего числа по модулю вычитается меньшее, в этом случае осуществляется переход на блок 14 алгоритма.

В блоке 13 алгоритма по команде РЕЗ:= ДПЧ + ДВЧ выполняется операция сложение первого ДПЧ и второго ДВЧ двоичных чисел. По команде Зн РЕЗ:= ЗнР A знаковому разряду результата присваивается знаковый разряд первого числа.

В блоке 14 алгоритма по команде РЕЗ:= ДПЧ - ДВЧ выполняется операция вычитание от первого большего ДПЧ числа второго меньшего ДВЧ числа. По команде Зн РЕЗ:= ЗнР A знаковому разряду результата присваивается знаковый разряд первого числа.

В блоке 15 алгоритма по команде РЕЗ:= ДВЧ - ДПЧ выполняется операция вычитание от второго большего ДВЧ числа первого меньшего ДПЧ числа. По команде Зн РЕЗ:= ЗнР В знаковому разряду результата присваивается знаковый разряд второго числа.

В блоке 16 алгоритма по команде БРгР:=РЕЗ происходит запись окончательного результата РЕЗ в блок регистра результата. По команде БРгР:=Зн РЕЗ осуществляется запись знакового разряда результата ЗнР в блок регистра результата (фиг.1).

Блок 17 алгоритма является конечным блоком алгоритма.

Работа параллельного сумматора-вычитателя на элементах нейронной логики заключается в следующем.

Внешние упpавляющие сигналы "Пуск" и "Сбpос" поступают в блок 6 упpавления. С выхода шифратора поступают в регистры первого и второго числа двоичные коды ДКЧ. На сумматоре по модулю два определяется признак выполнения операции суммирования или вычитания сигнал СВ. Если числа имеют одинаковые знаки, а код операции равен плюсу, то вычисляется сумма чисел, результату присваивается знак первого числа. Если числа имеют одинаковые знаки, а код операции равен минусу, то вычисляется разность чисел, результату присваивается знак большего числа. Если числа имеют разные знаки, а код операции равен плюсу, то вычисляется разность чисел, результату присваивается знак большего числа. Если числа имеют разные знаки, а код операции равен минусу, то вычисляется сумма чисел, результату присваивается знак первого числа. Предлагаемое арифметическое устройство выполняет операции суммирования и вычитания в параллельном формате. Определяется перенос в старшие разряды при суммировании. Вычисляется заём из старших разрядов в младшие при вычитании.

Блок 1 ввода чисел содержит шифратор ШФ DD7, сумматоры по модулю два DD8 и DD9 (фиг.2). Этот блок позволяет вводить двоичные числа. С выхода шифратора формируются двоичные коды чисел ДКЧ со своими знаками: ЗнРА, ЗнРВ. Знаковые разряды чисел и код операции с выхода шифратора поступают на входы сумматоров по модулю два DD8 и DD9. Сигнал суммирования-вычитания СВ формируется на выходе элемента DD9. Сумматоры по модулю два выполнены на нейроподобных элементах. Выходной сигнал вычисляется по формуле:

(1)

(1)

Выходными сигналами блока 1 ввода чисел являются двоичные коды операндов ДКЧ, представленные в прямых кодах и признак операции суммирование-вычитание СВ (фиг.2).

Блок 2 регистра первого числа содержит n–двоичных триггеров Трn, где n - количество разрядов входного числа. Этот блок предназначен для хранения двоичного кода первого числа. Перед началом работы сумматора-вычитателя по приходу из блока 6 информационного сигнала СУ происходит обнуление всех триггеров блока (фиг. 1, 7).

Блок 3 коммутации и сумматоров-вычитателей содержит схему определения знака результата DD13, схемы сумматоров-вычитателей DD14 - DD16 (фиг.3, 4). Этот блок выполняет арифметические операции суммирования и вычитания, определяет знаковый разряд результата. На вход блока поступают модули n-разрядных двоичных первого ДПЧ и второго ДВЧ чисел, признак операции суммирования-вычитания сигнал СВ, который поступает параллельно на все входы схем. Если сигнал СВ равен нулю, то схемы блока выполняют суммирование двоичных чисел, если этот сигнал равен единице, то выполняется поразрядная операция вычитания. На входы каждой схемы сумматора-вычитателя СУМ-ВЫЧi поступают одноименные двоичные разряды чисел Ai и Bi, признак операции сигнал СВ, перенос Pi из младших разрядов в старшие и заём Zi из старших разрядов в младшие. На схему определения знака результата СОЗР поступают знаковые разряды первого ЗнР А и второго ЗнР В двоичных чисел, сигнал суммирования–вычитания СВ (фиг.3). Сигнал заёма из знакового разряда ЗмЗнР поступает на вход первого сумматора-вычитателя СУМ-ВЫЧ1, который выполняет операции со старшими разрядами входных чисел. Этот сигнал формируется при вычитании чисел. Если заём ЗмЗнР равен нулю, то первое двоичное число по модулю больше второго, в этом случае менять местами входные числа не надо. Если сигнал заёма равен единице, в этом случае происходит вычитание от меньшего числа по модулю большего, то для получения разности необходимо поменять местами входные числа. Информационный сигнал результата РЕЗ является выходным сигналом блока (фиг.3, 4).

Схема определения знака результата СОЗР определяет знаковый разряд результата. В структуру схемы входят пороговые элементы DD17 – DD21 (фиг.5). Входные сигналы: признак операции суммирования-вычитания СВ и заём из знакового разряда первого числа поступают на вход схемы СУМ-ВЫЧ1, где суммируются старшие разряды, поступают на вход порогового элемента ПЭ DD17, который выполняет функцию логической схемы И. Сигнал с выхода порогового элемента DD17 поступает на прямой управляющий вход порогового элемента ПЭ DD20, который выполняет функцию логической схемы И и на вход порогового элемента DD18, который выполняет функцию инвертора. Сигнал с выхода инвертора поступает на прямой управляющий вход порогового элемента ПЭ DD19, который выполняет функцию логической схемы И. Выходные сигналы пороговых элементов DD19 и DD20 поступают на входы порогового элемента ПЭ DD21, который выполняет функцию логической схемы ИЛИ. Если сигнал суммирования-вычитания СВ равен нулю, то выполняется арифметическая операция суммирование двоичных чисел. Входные числа An и Bn суммируются по модулю, знаку суммы присваивается знак первого числа. An. Выходной сигнал порогового элемента DD17 будет равен нулю. Пороговый элемент ПЭ DD20 будет запет, на выходе будет нулевое значение. Пороговый элемент DD19 будет открыт, так как сигнал с выхода DD17 поступит на управляющий вход через инвертор DD18. Первым входом порогового элемента DD19 является знаковый разряд первого числа ЗнР A, который через отрытый пороговый элемент DD19 поступит на первый вход порогового элемента DD21 – схемы ИЛИ. Знаковый разряд результата ЗнР РЕЗ – выход логической схемы ИЛИ элемента DD21, будет равен знаковому разрядe первого числа ЗнР A. Если сигнал суммирования-вычитания СВ равен единице, то выполняется арифметическая операция вычитание двоичных чисел, от большего по модулю вычитается меньшее. Определяющим сигналом в сравнении модулей чисел является сигнал заёма из знакового разряда первого числа ЗмЗнР. Знаку разности присваивается знак большего числа. Если сигнал заёма ЗмЗнР равен нулю, то первое число по модулю больше второго, в этом случае вычисляется разность между числами An и Bn. Выходной сигнал порогового элемента DD17 будет равен нулю. Пороговый элемент ПЭ DD20 будет запет, на выходе будет нулевое значение. Пороговый элемент DD19 будет открыт, так как сигнал с выхода DD17 поступит на управляющий вход через инвертор DD18. Первым входом порогового элемента DD19 является знаковый разряд первого числа ЗнР A, который через отрытый пороговый элемент DD19 поступит на первый вход порогового элемента DD21 – схемы ИЛИ. Знаковый разряд результата ЗнР РЕЗ – выход логической схемы ИЛИ элемента DD21, будет равен знаковому разряду большего числа ЗнРA. Если сигнал заёма ЗмЗнР равен единице, то первое число по модулю меньше второго, в этом случае вычисляется разность между числами Bn и An. Выходной сигнал порогового элемента DD17 будет равен единице. Пороговый элемент ПЭ DD20 будет открыт, на выходе будет единичное значение. Пороговый элемент DD19 будет заперт, так как сигнал с выхода DD17 поступит на управляющий вход через инвертор DD18. Вторым входом порогового элемента DD20 является знаковый разряд второго большего числа ЗнР B, который через отрытый пороговый элемент DD20 поступит на второй вход порогового элемента DD21 – схемы ИЛИ. Знаковый разряд результата ЗнР РЕЗ – выход логической схемы ИЛИ элемента DD21, будет равен знаковому разряду большего второго числа ЗнР B (фиг.5).

Схема коммутации меняет местами входные двоичные разряды при выполнении операции вычитания, если от меньшего по модулю числа вычитается большее, вследствие которого формируется сигнал заёма из знакового разряда первого числа ЗмЗнР. После анализа этого сигнала и выполнения перестановки чисел вследствие этого от большего второго числа по модулю вычитается меньшее первое. В структуру схемы входят пороговые элементы DD22 – DD28 (фиг.6). Входные сигналы: заём из знакового разряда первого числа ЗмЗнР и двоичные разряды чисел Ai и Bi поступают на входы схем сумматоров-вычитателей СУМ-ВЫЧi, где выполняется операция вычитания от большего меньшего по модулю одноименных разрядов двоичных чисел. Сигнал заёма заёма из знакового разряда первого числа ЗмЗнР параллельно поступает на входы пороговых элементов ПЭ DD22 и DD26, которые выполняют функции инверторов и на входы пороговых элементов ПЭ DD24 и DD27, которые выполняют функции логических схем И. Двоичные разряды первого числа Ai поступают на первые входы пороговых элементов ПЭ DD23 и DD27, второго числа Bi поступают на вторые входы пороговых элементов ПЭ DD24 и DD28, которые выполняют функции логических схем И. Пороговый элемент ПЭ DD25 выполняет функцию логической схемы ИЛИ. Если сигнал заёма из знакового разряда первого числа ЗмЗнР равен нулевому значению, то пороговые элементы DD24 и DD27 будут заперты. Пороговые элементы DD23 и DD28 будут открыты, т.к. на их входы нулевой управляющий сигнал поступает через инверторы DD22 и DD26. В этом случае двоичный сигнал первого числа Ai через открытый элемент DD23 и пороговый элемент DD 25 (логическую схему ИЛИ) поступит на первый вход нейроподобного элемента DD31, выполняющего логическую функцию суммы по модулю два. Двоичный сигнал второго числа Bi через открытый элемент DD28 поступит на четвертый вход порогового элемента DD32, выполняющего логическую функцию И. Если сигнал заёма из знакового разряда первого числа ЗмЗнР равен единичному значению, то пороговые элементы DD23 и DD28 будут заперты, т.к. на их входы единичный управляющий сигнал поступает через инверторы DD22 и DD26. Пороговые элементы DD24 и DD27 будут открыты, В этом случае двоичный сигнал второго числа Bi через открытый элемент DD24 и пороговый элемент DD25 поступит на первый вход нейроподобного элемента DD31. Двоичный сигнал первого числа Ai через открытый элемент DD27 поступит на третий вход порогового элемента DD32. В итоге происходит перестановка двоичных разрядов первое меньшее становиться вторым, второе большее становиться первым для выполнения арифметической операции вычитания (фиг.6).

Полный одноразрядный сумматор предназначен для сложения трёх одноразрядных двоичных чисел (фиг.6). Устройство имеет три входа: двоичные разряды Ai, Bi, результат переноса Pi+1 предыдущего сумматора, и два выхода: результата сложения Si и сигнала переноса в старший разряд Pi.

Таблица 1 истинности отображает функционирования полного одноразрядного сумматора.

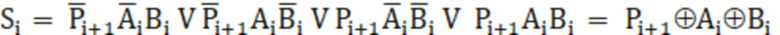

Из таблицы 1 сумма Si чисел определяется формулой

(1)

(1)

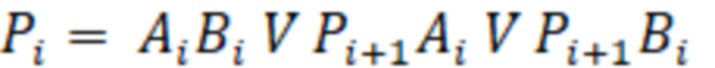

Перенос Pi из младшего разряда в старший при сложении чисел определяется формулой

(2)

(2)

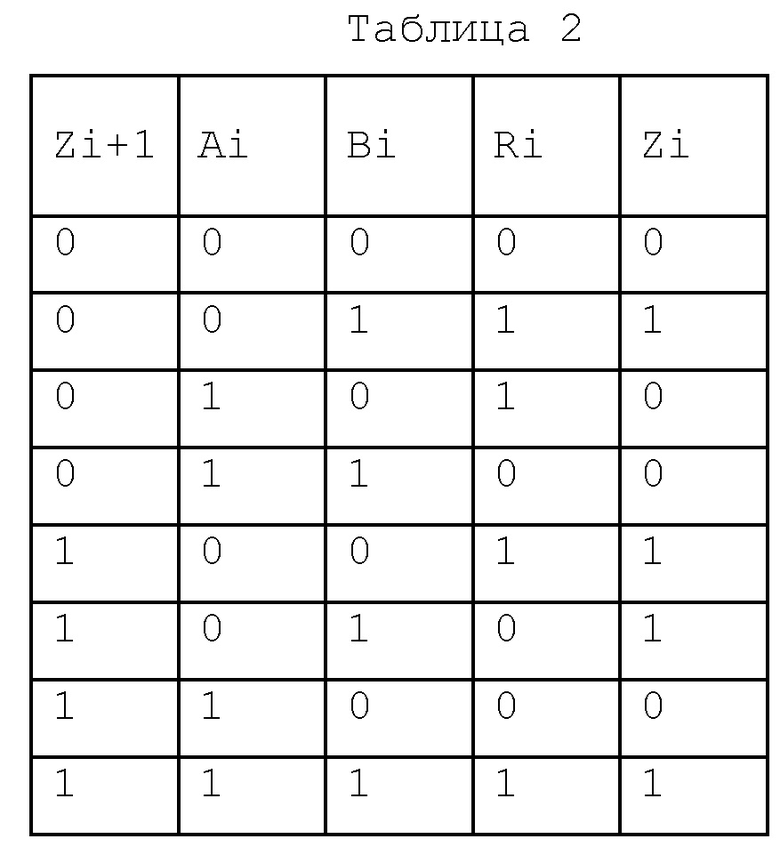

Работа полного одноразрядного вычитателя описывается таблицей 2 истинности, в которой отображены: заём Zi+1, поступающий из соседнего более младшего разряда, уменьшаемое Аi, вычитаемое Вi, разность Ri, заём Zi, возникающий в данном i-том разряде.

Из таблицы 2 разность чисел  определяется формулой

определяется формулой

(3)

(3)

Заём Zi из старшего разряда в младший определяется формулой

(4)

(4)

Формулы, по которым вычисляются сумма  и разность

и разность  одинаковые, два сумматора по модулю два, выполнены на нейроподобных элементах DD29 и DD30 (фиг.6). При выполнении операции сложение перенос

одинаковые, два сумматора по модулю два, выполнены на нейроподобных элементах DD29 и DD30 (фиг.6). При выполнении операции сложение перенос  из младшего разряда в старший выполнен на нейроподобном элементе DD31 и пороговом элементе DD32. Нейроподобный элемент DD31 выполняет функцию повторителя двоичного разряда

из младшего разряда в старший выполнен на нейроподобном элементе DD31 и пороговом элементе DD32. Нейроподобный элемент DD31 выполняет функцию повторителя двоичного разряда  , который подаётся на первый вход элемента. На второй вход нейроподобного элемента D31 подаётся признак операции СВ. Если выполняется операция суммирование, сигнал СВ равен нулю. На выходе нейроподобного элемента DD31 будет значение

, который подаётся на первый вход элемента. На второй вход нейроподобного элемента D31 подаётся признак операции СВ. Если выполняется операция суммирование, сигнал СВ равен нулю. На выходе нейроподобного элемента DD31 будет значение  . Перенос

. Перенос  вычисляется пороговым элементом DD32. При выполнении операции вычитание двоичных разрядов сигнал СВ равен единице. Нейроподобный элемент DD31 выполняет операцию инвертора, на выходе которого выполняется функция

вычисляется пороговым элементом DD32. При выполнении операции вычитание двоичных разрядов сигнал СВ равен единице. Нейроподобный элемент DD31 выполняет операцию инвертора, на выходе которого выполняется функция . Заём

. Заём  из старшего разряда в младший вычисляется на пороговом элементе DD32.

из старшего разряда в младший вычисляется на пороговом элементе DD32.

Работа сумматора-вычитателя заключается в следующем. На входы нейроподобного элемента DD29 подаются двоичные разряды  и

и  . Этот нейроподобный элемент выполняет операцию суммирования входных двоичных разрядов. На выходе сумматора DD29 вычисляется сумма двоичных разрядов

. Этот нейроподобный элемент выполняет операцию суммирования входных двоичных разрядов. На выходе сумматора DD29 вычисляется сумма двоичных разрядов  и

и  . Результат суммы поступает на первый вход нейроподобного элемента DD30. На второй вход этого элемента поступает двоичный разряд переноса

. Результат суммы поступает на первый вход нейроподобного элемента DD30. На второй вход этого элемента поступает двоичный разряд переноса  из младшего разряда в старший. На выходе нейроподобного элемента DD30 вычисляется сумма

из младшего разряда в старший. На выходе нейроподобного элемента DD30 вычисляется сумма  и разность

и разность  входных двоичных разрядов

входных двоичных разрядов и

и  по формуле

по формуле  . На входы нейроподобного элемента DD31 подается двоичные разряды

. На входы нейроподобного элемента DD31 подается двоичные разряды  или

или и признак выполнения арифметической операции суммирования или вычитания сигнал

и признак выполнения арифметической операции суммирования или вычитания сигнал  . Если сигнал

. Если сигнал  равен нулю, то выполняется операция суммирование двоичных чисел. Если сигнал

равен нулю, то выполняется операция суммирование двоичных чисел. Если сигнал  равен единице, то выполняется операция вычитания двоичных чисел. При выполнении операции суммирование нейроподобный элемент DD31 выполняет операцию повторителя, на выходе формируется сигнал

равен единице, то выполняется операция вычитания двоичных чисел. При выполнении операции суммирование нейроподобный элемент DD31 выполняет операцию повторителя, на выходе формируется сигнал  по формуле

по формуле  . При выполнении операции вычитания нейроподобный элемент DD31 выполняет операцию отрицание, на выходе инвертора формируется сигнал

. При выполнении операции вычитания нейроподобный элемент DD31 выполняет операцию отрицание, на выходе инвертора формируется сигнал  по формуле

по формуле  . Пороговый элемент DD32 вычисляет перенос

. Пороговый элемент DD32 вычисляет перенос  из младшего разряда в старший по формуле

из младшего разряда в старший по формуле  . При выполнении операции вычитания на пороговом элементе DD32 вычисляется заём

. При выполнении операции вычитания на пороговом элементе DD32 вычисляется заём  из старшего разряда в младший по формуле

из старшего разряда в младший по формуле  (фиг.6).

(фиг.6).

Блок 4 регистра второго числа содержит n – двоичных триггеров Трn, где n - количество разрядов входного числа. Этот блок предназначен для хранения двоичного кода второго числа. Перед началом работы сумматора-вычитателя по приходу из блока 6 информационного сигнала СУП происходит обнуление всех триггеров блока (фиг.1, 7).

Блок 5 регистра результата содержит n триггеров Тn, где n - количество разрядов необходимое для получения результата. Входным информационным сигналом блока является сигнал управления УП, поступающий из блока 6 управления. Перед началом работы сумматора-вычитателя происходит обнуление регистра блока. По сигналу разрешения записи регистр блока принимают входную информацию для записи и хранения. Двоичные разряды результата записываются параллельно в регистр блока (фиг.1,8).

Размеченная ГСА работы устройства приведена на фиг.10 где обозначено:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поразрядного вычисления логических и арифметических операций | 2020 |

|

RU2739343C1 |

| Параллельно-последовательный сумматор-вычитатель старшими разрядами вперед на нейронах | 2019 |

|

RU2708501C1 |

| Параллельный сумматор-вычитатель на нейроподобных элементах | 2023 |

|

RU2805774C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Сумматор-вычислитель на элементах нейронной логики | 2019 |

|

RU2715177C1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

Изобретение относится к техническим средствам информатики и вычислительной техники. Технический результат - повышение быстродействия, надежности работы, уменьшение избыточности аппаратных средств, упрощение алгоритма работы блока управления устройства. Параллельный сумматор-вычитатель на элементах нейронной логики содержит: блок ввода чисел, блок регистра первого числа, блок коммутации и сумматоров-вычитателей, блок регистра второго числа, блок регистра результата, блок управления, пороговые и нейроподобные элементы. Новым в устройстве является то, что арифметические операции на сумматоре-вычитателе выполняются в параллельном формате в прямых кодах, определение по модулю большего числа происходит при вычитании чисел схемой коммутации, перенос при суммировании и заём при вычитании двоичных чисел определяется на пороговом элементе, применены элементы нейронной и пороговой логики. 10 ил., 2 табл.

Параллельный сумматор-вычитатель на элементах нейронной логики, содержащий блок коммутации и сумматоров-вычитателей, блок управления, отличающийся тем, что дополнительно введены: блок ввода чисел, блок регистра первого числа, блок регистра второго числа, блок регистра результата, причем информационный выход блока ввода чисел, на котором формируется двоичный код входного числа, соединен с первым информационным входом блока регистра первого числа и с первым информационным входом блока регистра второго числа, второй информационный вход блока регистра первого числа, на котором формируются сигналы: установки в нулевое состояние, синхронизации работы двоичных триггеров, разрешения для записи, хранения и выдачи двоичного кода, соединен с третьим информационным выходом блока управления, второй информационный выход блока управления, на котором формируются сигналы: установки в нулевое состояние, синхронизации работы двоичных триггеров, разрешения для записи, хранения и выдачи двоичного кода, соединен со вторым информационным входом блока регистра второго числа, информационный выход блока регистра первого числа, на котором формируется двоичный код и знаковый разряд первого числа, соединен с первым информационным входом блока коммутации и сумматоров-вычитателей, информационный выход блока регистра второго числа, на котором формируется двоичный код и знаковый разряд второго числа, соединен со вторым информационным входом блока коммутации и сумматоров-вычитателей, информационный выход блока коммутации и сумматоров-вычитателей, на котором формируется двоичный код и знаковый разряд результата, соединен с первым информационным входом блока регистра результата, управляющий выход блока ввода чисел, на котором формируется признак операции сигнала суммирования или вычитания, соединен с управляющим входом блока коммутации и сумматоров-вычитателей, первый информационный выход блока управления, на котором формируются сигналы: установки в нулевое состояние, синхронизации работы двоичных триггеров, разрешения для записи, хранения и выдачи двоичного кода, соединен со вторым информационным входом блока регистра результата, первый и второй управляющие входы "СБРОС" и "ПУСК" блока управления являются внешними входами параллельного сумматора-вычитателя на элементах нейронной логики.

| Сумматор-вычислитель на элементах нейронной логики | 2019 |

|

RU2715177C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| US 5581661 A, 03.12.1996. | |||

Авторы

Даты

2022-09-21—Публикация

2020-09-04—Подача