Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для создания быстродействующих, специализированных и высокопроизводительных цифровых модулей, выполняющих арифметические операции сложения и вычитания. Достоинством предлагаемого устройства являются широкие функциональные возможности, простая конструкции, устройство выполнено на нейроподобных и пороговых элементах, которые обеспечивают высокое быстродействие и надёжность.

Известен "Параллельный сумматор-вычитатель на нейронах" (патент №2246752, от 20.02.2005 г.), который выполняет арифметические операции сложения и вычитания чисел в двоичной системе счисления.

Известен "Параллельный сумматор-вычитатель на нейронах со сквозным переносом" (патент №2523942, от 30.05.2014 г.), который выполняет арифметические операции сложения и вычитания чисел.

В качестве прототипа выбрано "Устройство поразрядного вычисления логических и арифметических операций" (патент №2739343 от 23.12.2020 г., Бюл №36), которое выполняет операции суммирования и вычитания двоичных чисел.

Недостатком предложенных технических решений является низкая скорость выполнения операций сложения и вычитания, избыточность аппаратных средств устройства, сложный алгоритм работы.

В представленном устройстве при выполнении арифметических операций все элементы работают в полную силу. Обеспечивается максимальное быстродействие, сумматор-вычитатель не содержат аппаратурной избыточности. Эффективность конструирования подобных устройств проявляется при использовании нейроподобных элементов.

Технической задачей предлагаемого решения является увеличение скорости выполнения арифметических операций, повышение надежности работы сумматора-вычитателя, уменьшение аппаратных средств, что ведет к упрощению комбинационных схем устройства.

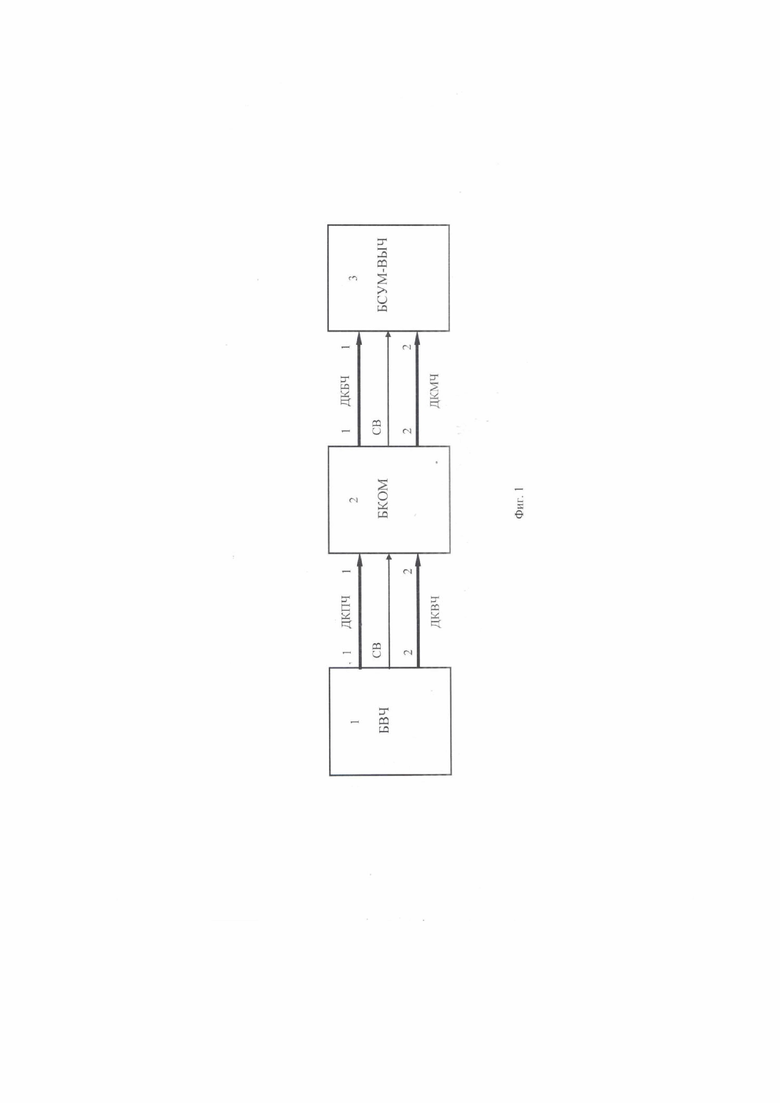

Решение задачи осуществляется тем, что параллельный сумматор-вычитатель на нейроподобных элементах, содержащий блок ввода чисел, блок компарации и блок параллельных сумматоров-вычитателей, отличающиеся тем, что дополнительно введены: блок-регистр первого числа, блок-регистр второго числа и блок-регистр результата, причем первый информационный выход блока ввода чисел, на котором формируется двоичный код и знаковый разряд первого входного числа соединен с первым информационным входом блока компарации, управляющий вход блока компарации, на котором формируется признак операции сигнал суммирования или вычитания, соединен с управляющим выходом блока ввода чисел, второй информационный выход блока ввода чисел, на котором формируется двоичный код и знаковый разряд второго входного числа соединен со вторым информационным входом блока компарации, первый информационный выход блока компарации, на котором формируется двоичный код и знаковый разряд большего по модулю числа соединен с первым информационным входом блока параллельных сумматоров-вычитателей, управляющий вход блока параллельных сумматоров-вычитателей, на котором формируется признак операции сигнал суммирования или вычитания, соединен с управляющим выходом блока компарации, второй информационный выход блока компарации, на котором формируется двоичный код меньшего по модулю числа, соединен со вторым информационным входом блока параллельных сумматоров-вычитателей.

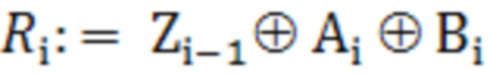

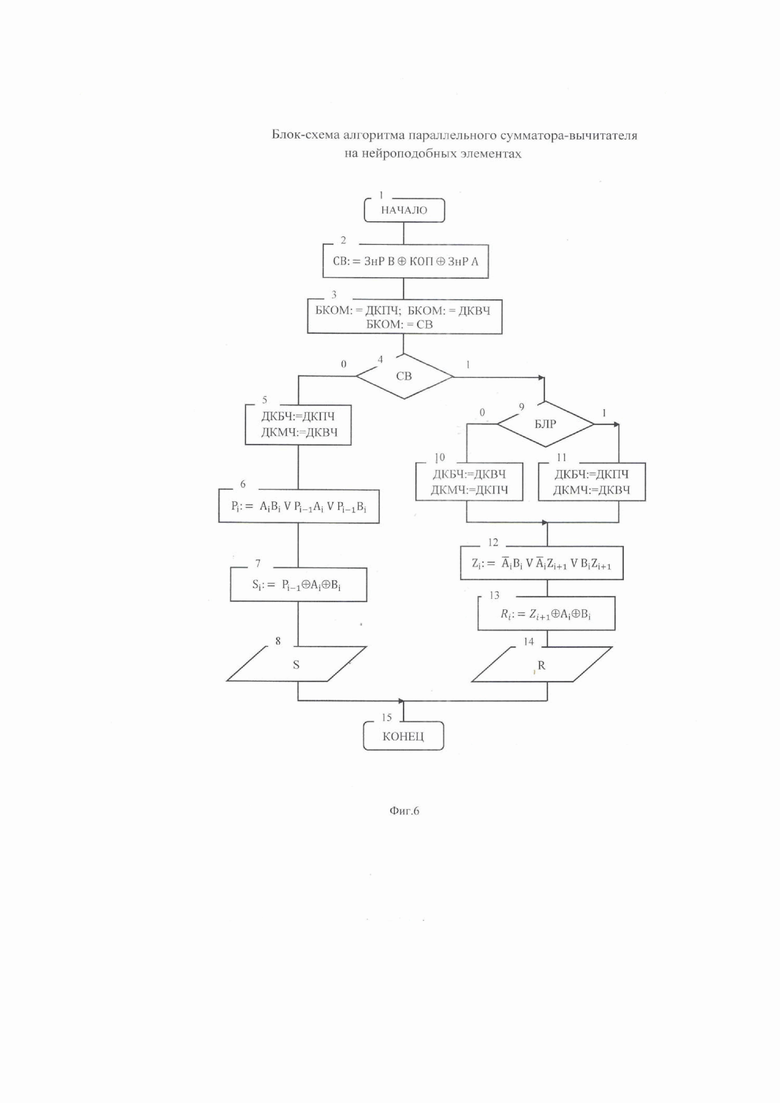

БВЧ - блок ввода чисел служит для ввода операндов и признака выполнения операций.

БКОМ - блок компарации служит для сравнения двоичных чисел, если необходимо выполнить операцию вычитания.

БСУМ-ВЫЧ - блок параллельных сумматоров-вычитателей служит для выполнения операций сложения и вычитания.

На фиг. 1 изображена структурная схема параллельного сумматора-вычитателя, выполняющего арифметические операции суммирования и вычитания.

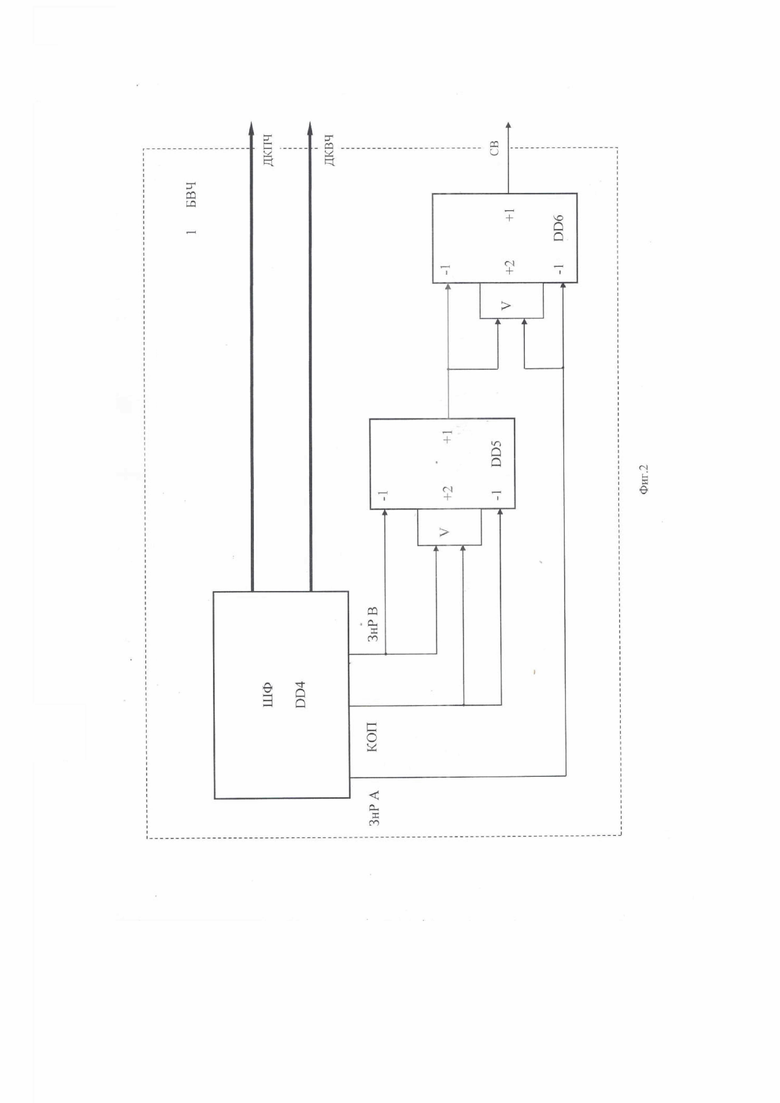

На фиг. 2 представлен вариант технической реализации блока ввода чисел и представлена функциональная схема сумматоров по модулю два, определяющие признак операции.

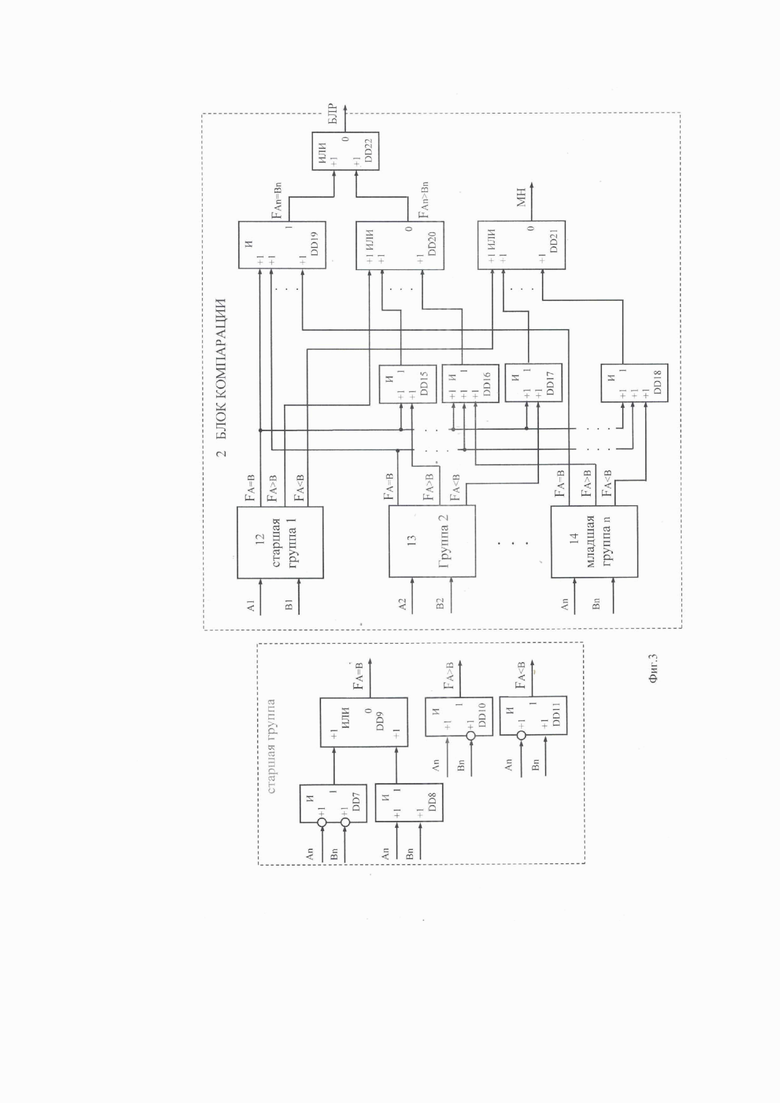

На фиг. 3 представлена функциональная схема блока компарации, которая сравнивает двоичные числа.

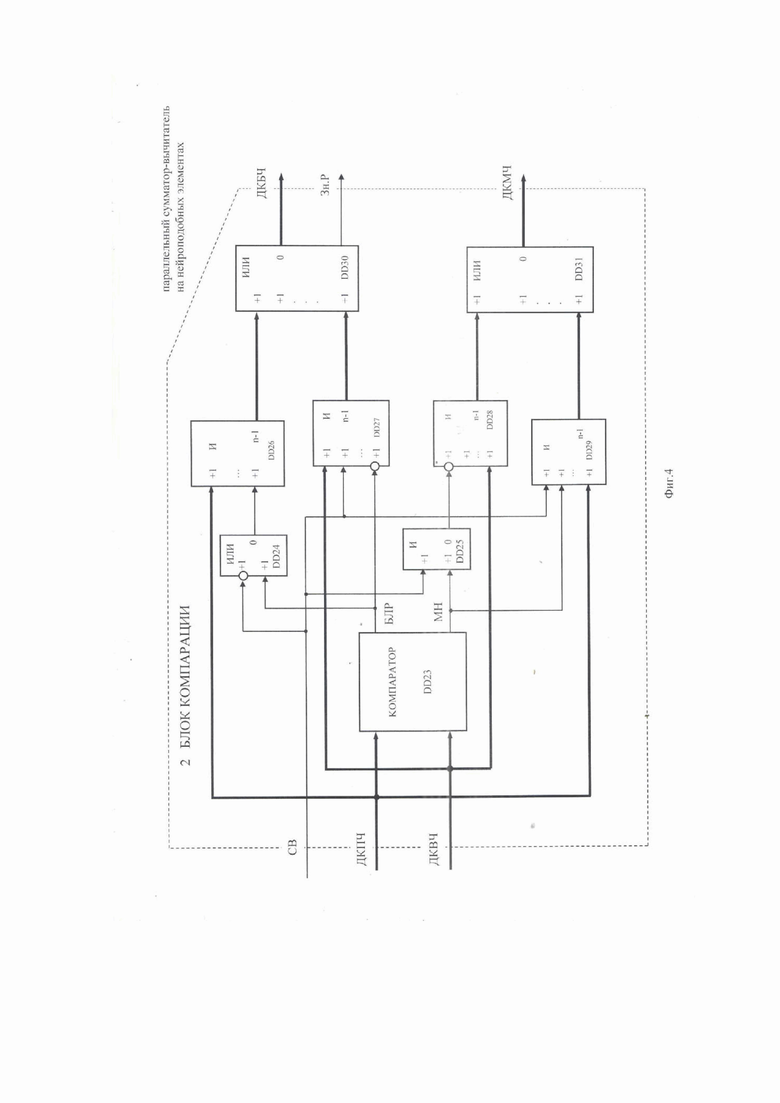

На фиг. 4 представлена функциональная схема, которая определяет отношение двоичных чисел: больше, меньше или равно.

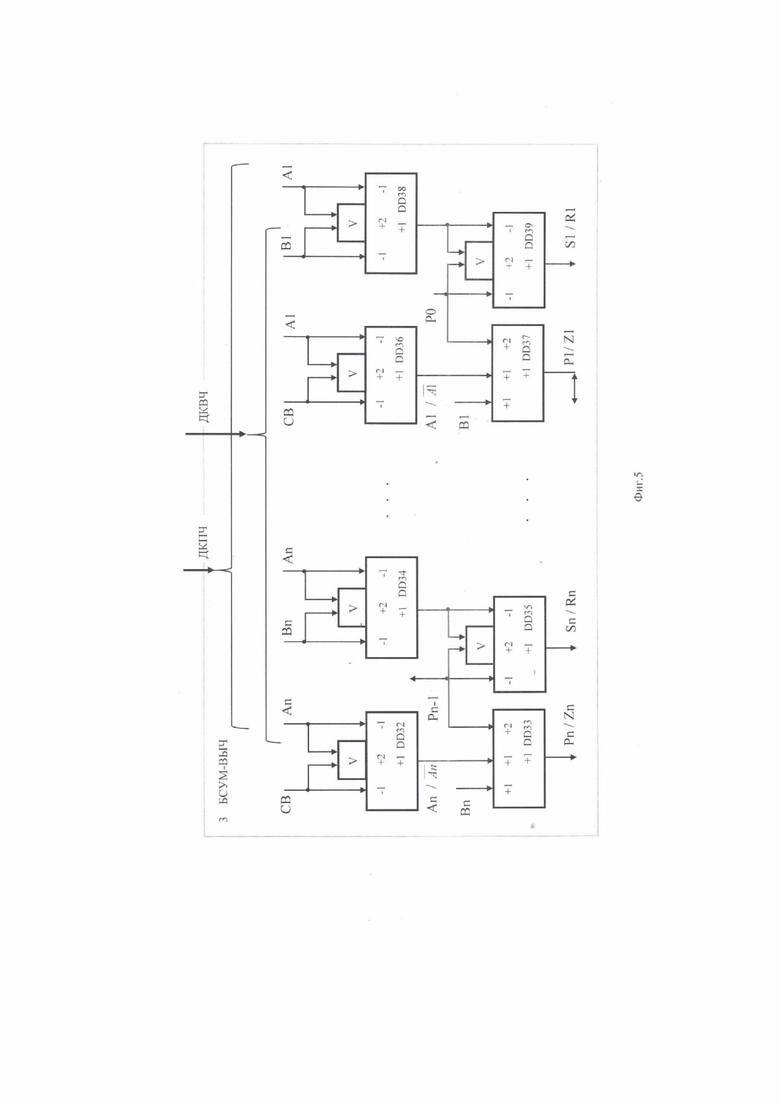

На фиг. 5 показана функциональна схема блока параллельных сумматоров-вычитателей на нейроподобных элементах.

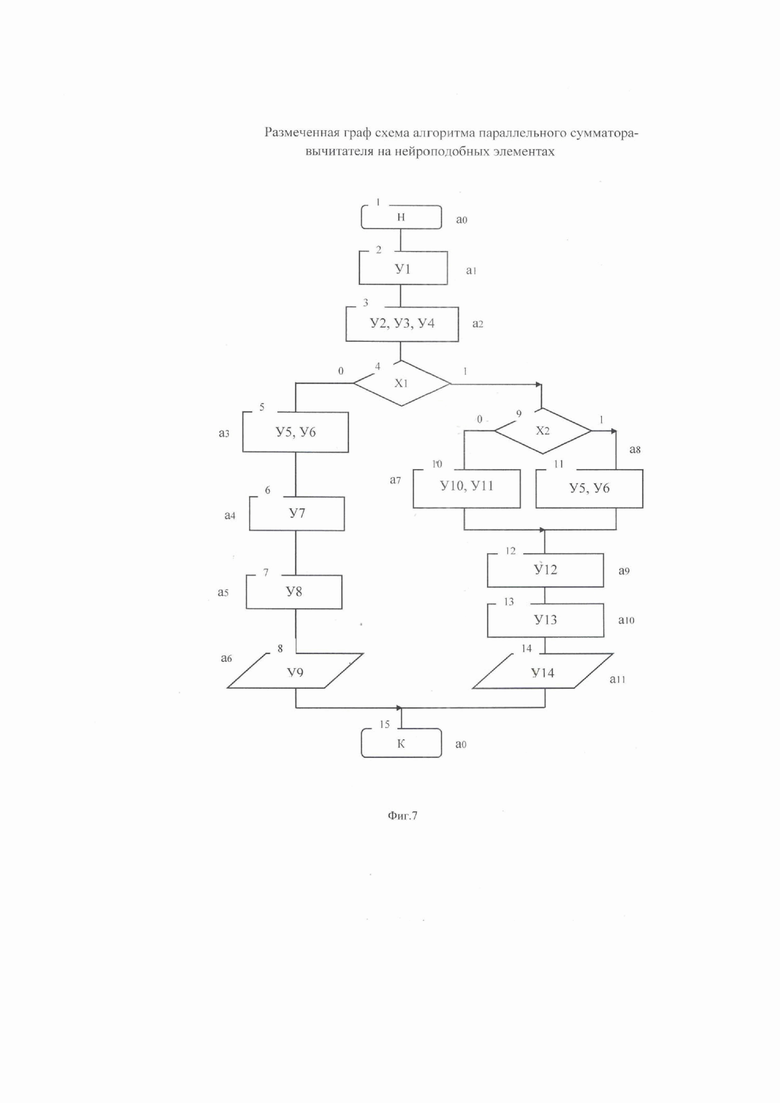

На фиг. 6 представлена содержательная граф-схема (ГСА) алгоритма работы устройства.

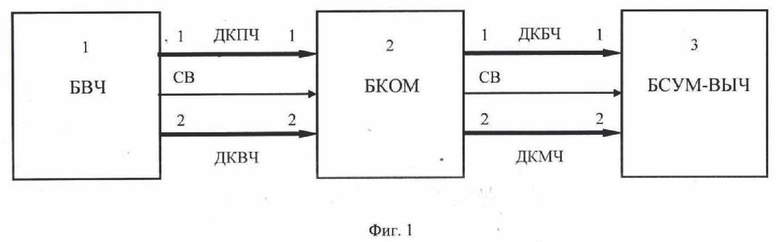

На фиг. 7 представлена размеченная ГСА работы устройства.

Параллельный сумматор-вычитатель на нейроподобных элементах содержит: блок ввода чисел, блок компарации, блок параллельных сумматоров-вычитателей, пороговые и нейроподобные элементы (фиг. 1).

Для описания алгоритма работы параллельного сумматора-вычитателя используются следующие идентификаторы.

Ai - двоичный разряд числа.

- инверсный разряд числа.

- инверсный разряд числа.

Bi - двоичный разряд числа.

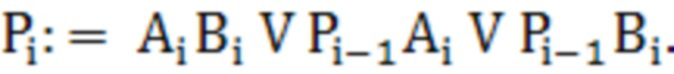

Pi-1 - перенос из младшего разряда в старший.

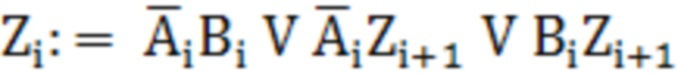

Zi+1 - заем из старшего разряда в младший.

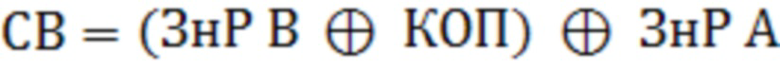

СВ - признак выполнения операций суммирования или вычитания.

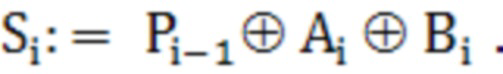

S - сумма двоичных чисел.

R - разность двоичных чисел.

Zi - заем при выполнении операции вычитания.

Pi - перенос из младшего в старший.

БЛР - результат сравнения, при котором первое число больше второго или числа равны по модулю.

МН - результат сравнения, при котором второе число больше первого.

ДКБЧ - двоичное код большего числа.

ДКМЧ - двоичное код меньшего числа.

ДКПЧ - двоичное код первого числа.

ДКВЧ - двоичное код второго числа.

ЗнР - знаковый разряд результата.

ЗнР А - знаковый разряд первого числа.

ЗнР В - знаковый разряд второго числа.

КОП - код арифметической операции.

Блок-схема алгоритма работы параллельного сумматора-вычитателя.

Содержательная ГСА управления приведена на фиг. 6 и отражает работу параллельного сумматора-вычитателя на нейроподобных элементах.

Блок 1 алгоритма является начальным.

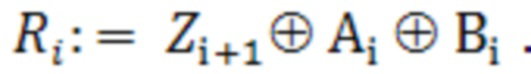

В блоке 2 алгоритма определяется признак выполнения арифметической операции суммирования или вычитания двоичных чисел - сигнал СВ по формуле  . В формуле обозначены знаковый разряд второго числа ЗнР В, код операции КОП, знаковый разряд первого числа ЗнР А и логическая операция сумма по модулю два

. В формуле обозначены знаковый разряд второго числа ЗнР В, код операции КОП, знаковый разряд первого числа ЗнР А и логическая операция сумма по модулю два  .

.

В блоке 3 алгоритма по командам: БКОМ:=ДКПЧ, БКОМ:=ДКВЧ, БКОМ:=СВ происходит подача на вход блока компарации первого ДКПЧ двоичного числа, второго ДКВЧ двоичного числа и сигнала суммирования-вычитания СВ (фиг. 1, 4).

В блоке 4 алгоритма анализируется признак выполнения операций суммирования или вычитания сигнал СВ. Если сигнал  равен нулю, то выполняется операция суммирования двоичных чисел, происходит переход из блока 4 по выходу “0” на блок 5 алгоритма. Если сигнал

равен нулю, то выполняется операция суммирования двоичных чисел, происходит переход из блока 4 по выходу “0” на блок 5 алгоритма. Если сигнал  равен единице, то выполняется операция вычитания двоичных чисел, происходит переход из блока 4 по выходу “1” на блок 9 алгоритма.

равен единице, то выполняется операция вычитания двоичных чисел, происходит переход из блока 4 по выходу “1” на блок 9 алгоритма.

В блоке 5 алгоритма по командам: ДКБЧ:=ДКПЧ, ДКМЧ:=ДКВЧ происходит подача на вход блока параллельных сумматоров-вычитателей первого ДКПЧ двоичного числа и второго ДКВЧ двоичного числа (фиг. 5).

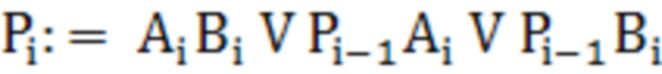

В блоке 6 алгоритма вычисляется перенос  из младшего разряда числа в старший по формуле

из младшего разряда числа в старший по формуле

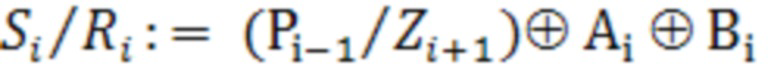

В блоке 7 алгоритма вычисляется поразрядная сумма Si двоичных чисел по формуле

В блоке 8 алгоритма выдается результат сложения S двоичных чисел.

В блоке 9 алгоритма при выполнении арифметической операции вычитания, анализируется признак БЛР большего числа или равенство чисел по модулю. Если признак БЛР большего числа или равенство чисел равен нулю, то это означает, что второе ВЧ число больше по модулю первого. В этом случае осуществляется переход из блока 9 по выходу “0” на блок 10 алгоритма. Если признак БЛР большего числа или равенство чисел равен единице, то это означает, что первое ПЧ число больше по модулю второго. В этом случае осуществляется переход из блока 9 по выходу “1” на блок 11 алгоритма (фиг. 3, 4).

В блоке 10 алгоритма по командам: ДКБЧ:=ДКВЧ, ДКМЧ:=ДКПЧ происходит подача на вход блока параллельных сумматоров-вычитателей второго ДКВЧ большего двоичного числа и первого ДКПЧ меньшего двоичного числа. В блоке параллельных сумматоров-вычитателей из большего второго вычитается меньшее первое (фиг. 5).

В блоке 11 алгоритма по командам: ДКБЧ:=ДКПЧ, ДКМЧ:=ДКВЧ происходит подача на вход блока параллельных сумматоров-вычитателей первого ДКПЧ большего двоичного числа и второго ДКВЧ меньшего двоичного числа. В блоке параллельных сумматоров-вычитателей из большего первого вычитается меньшее второе (фиг. 5).

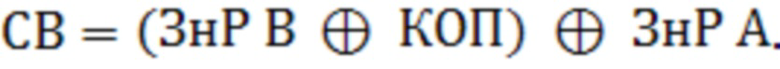

В блоке 12 алгоритма вычисляется заем из старшего разряда числа в младший по формуле  .

.

В блоке 13 алгоритма вычисляется разность Ri двоичных чисел по формуле

В блоке 14 алгоритма выдается результат вычитания R двоичных чисел.

Блок 15 алгоритма является конечным.

Работа параллельного сумматора-вычитателя на нейроподобных элементах заключается в следующем.

На сумматоре по модулю два определяется признак выполнения операции суммирования или вычитания сигнал СВ. Если числа имеют одинаковые знаки, а код операции положительный, то вычисляется сумма чисел, результату присваивается знак первого числа. Если числа имеют одинаковые знаки, а код операции отрицательный, то вычисляется разность чисел, результату присваивается знак большего числа. Если числа имеют разные знаки, а код операции положительный, то вычисляется разность чисел, результату присваивается знак большего числа. Если числа имеют разные знаки, а код операции отрицательный, то вычисляется сумма чисел, результату присваивается знак первого числа. Предлагаемое арифметическое устройство выполняет операции суммирования и вычитания в параллельном формате. Определяется перенос в старшие разряды при суммировании. Вычисляется заем из старших разрядов в младшие при вычитании.

Блок 1 ввода чисел содержит шифратор ШФ DD4, сумматоры по модулю два DD5 и DD6 (фиг. 2). Этот блок позволяет вводить двоичные числа. С выхода шифратора формируются двоичные коды первого ДКПЧ числа и второго ДКВЧ числа со своими знаками: ЗнРА, ЗнРВ. Знаковые разряды чисел и код операции с выхода шифратора поступают на входы сумматоров по модулю два DD5 и DD6. Сигнал суммирования-вычитания СВ формируется на выходе элемента DD6. Сумматоры по модулю два выполнены на нейроподобных элементах. Выходной сигнал вычисляется по формуле

Выходными сигналами блока 1 ввода чисел являются двоичные коды операндов, представленные в прямых кодах и признак операции суммирование-вычитание СВ (фиг. 2).

Блок 2 компарации выполняет функцию сравнения входных двоичных чисел. При выполнении арифметической операции вычитания необходимо сравнить входные числа по модулю. От большего числа вычесть меньшее. Сравнение чисел в блоке выполняется на последовательном многоразрядном компараторе. Вначале сравниваются старшие разряды двоичных чисел. Если числа не равны между собой, то результат сравнения определен. Если старшие разряды равны, то необходимо последовательно сравнивать очередные младшие двоичные разряды до появления неравенства в каком-либо из разрядов, в этом случае сравнение прекращается и выдается результат сравнения. На фиг. 3 представлен последовательный компаратор, который определяет большее по модулю число. Старшая группа сравнивает старшие двоичные разряды чисел. Пороговые элементы DD7, DD8 и DD9 определяют схему эквивалентности (равнозначности). Если входные разряды An и Bn равны 00 или 11, то на выходе схемы ИЛИ порогового элемента DD9 выходной сигнал FA=B будет равен 1. Если числа не равны между собой, то сигнал FA=B будет равен 0. Пороговый элемент DD10 определяет комбинацию 10, в этом случае первое число больше второго, выходной сигнал FA>B будет равен 1. Пороговый элемент DD11 определяет комбинацию 01, в этом случае первое число меньше второго, выходной сигнал FA<B будет равен 1. Блок 2 компарации состоит из n групп. На выходе каждой группы определен результат сравнения двоичных чисел. Если числа старшей группы 1 равны, то сравниваются числа группы 2 и до тех пор, пока не определиться неравенство чисел в очередной группе. Пороговые элементы DD15, DD16, DD17, DD18 - схемы И выполняют функцию электронных ключей. На выходах пороговых элементов DD19 - схема И, DD20, DD21 - схем ИЛИ определяются результаты сравнения двоичных чисел. Выходной сигнал БЛР порогового элемента DD22 - схема ИЛИ определяет результат сравнения двоичных разрядов, при котором числа равны или первое число больше второго. Выходной сигнал МН порогового элемента DD21 - схема ИЛИ определяет результат сравнения, при котором первое число меньше второго (фиг. 3).

Входными сигналами блока компарации являются: управляющий сигнал СВ, признак арифметической операции суммирования или вычитания. Этот сигнал поступает на инверсный вход порогового элемента DD24 - схема ИЛИ, на прямые управляющие входы пороговых элементов DD25, DD27, DD29 - схемы И. Информационные сигналы двоичных кодов первого ДКПЧ и второго ДКВЧ числа, которые поступают на входы компаратора DD23. Если сигнал СВ суммирование-вычитание равен нулевому значению, то выполняется арифметическая операция суммирования двоичных чисел, в этом случае сравнение чисел не производится. Пороговые элементы DD25, DD27, DD29 - схемы И будут заперты. На выходе порогового элемента DD24 будет единица, которая является управляющим входным сигналом порогового элемента DD26 - схема И. Входной двоичный код первого числа ДКПЧ через открытую схему И элемента DD26 поступит на вход порогового элемента DD30 - схема ИЛИ. Выходной сигнал элемента DD30, двоичный код большего числа ДКБЧ будет равен двоичному коду первого числа ДКПЧ. Управляющим выходом порогового элемента DD30 схема ИЛИ является сигнал знакового разряда результата ЗнР. На выходе порогового элемента DD25 будет нулевое значение, которое поступает на инверсный вход порогового элемента DD28. Элемент DD28 будет открыт. Входной двоичный код второго числа ДКВЧ через открытую схему И элемента DD28 поступит на вход порогового элемента DD31 - схема ИЛИ. Выходной сигнал элемента DD31 двоичный код меньшего числа ДКМЧ будет равен двоичному коду второго числа ДКВЧ.

Если сигнал СВ суммирование-вычитание равен единичному значению, то выполняется арифметическая операция вычитания двоичных чисел, в этом случае необходимо сравнить модули двоичных чисел. После сравнения определяется большее по модулю число, от которого вычитается меньшее. При равенстве сигнала СВ единице, который поступает на инверсный вход порогового элемента DD24 - схема ИЛИ и на прямые управляющие входы пороговых элементов DD25, DD27, DD29 - схемы И, которые будут открыты. Компаратор DD23 определяет большее по модулю входное двоичное число, имеет два выходных сигнала: больше или равны БЛР, равный единице, это означает, первое число больше второго или числа равны по модулю, меньше МН, равного единице, в этом случае второе число больше первого. Если первое число больше второго или числа равны, то выходной сигнал компаратора БЛР равен единице, тогда сигнал меньше МН равен нулю. Выходной сигнал порогового элемента DD24 - схема ИЛИ равен единице. Элемент DD26 - схема И будет открыт, на выходе элемента DD30 - схема ИЛИ будет двоичный код первого большего числа ДКПЧ. Выходной сигнал порогового элемента DD25 - схема И, равный нулю, поступает на инверсный управляющий вход порогового элемента DD28, который будет открыт, на выходе элемента DD31 - схема ИЛИ будет двоичный код второго меньшего числа ДКВЧ. Если второе число больше первого, то сигнал меньше МН равен единице, а сигнал больше или равно БЛР равен нулю. Выходной сигнал порогового элемента DD24 - схема ИЛИ будет равен нулю. Элемент DD26 - схема И будет заперт, а пороговый элемент DD27 - схема И будет открыт, т.к. сигнал больше или равен БЛР, поступит на инверсный управляющий вход этого элемента. На выходе элемента DD30 - схема ИЛИ будет двоичный код второго большего по модулю числа ДКВЧ. Выходной сигнал порогового элемента DD25 - схема И, равный единице, поступает на инверсный управляющий вход порогового элемента DD28, который будет заперт, а пороговый элемент DD29 будет открыт, т.к. сигнал МН поступает на прямой управляющий вход этого элемента. На выходе элемента DD31 - схема ИЛИ будет двоичный код первого меньшего числа ДКПЧ (фиг. 4).

Блок 3 сумматоров-вычитателей содержит схемы сумматоров-вычитателей DD32 - DD39 (фиг. 5). Этот блок выполняет арифметические операции суммирования и вычитания двоичных чисел. На вход блока поступают модули n-разрядных двоичных кодов первого ДКПЧ числа, второго ДКВЧ числа и признак операции суммирования-вычитания - сигнал СВ, который поступает параллельно на все входы схем. Если сигнал СВ суммирования-вычитания равен нулю, то вычисляется сумма двоичных чисел, если этот сигнал равен единице, то выполняется поразрядная операция вычитания. На входы каждой схемы блока сумматора-вычитателя СУМ-ВЫЧi поступают одноименные двоичные разряды чисел Ai и Bi, признак операции - сигнал СВ, перенос Pi из младших разрядов в старшие и заем Zi из старших разрядов в младшие. Одноразрядный сумматор-вычитатель состоит из трех сумматоров по модулю два DD32, DD34, DD35 и одного порогового элемента DD33. На нейроподобных элементах DD34, DD35 вычисляется сумма и разность входных двоичных чисел по формуле  . На нейроподобном элементе DD32 при суммировании, сигнал СВ, равный нулю, определяется как прямое значение первого двоичного разряда

. На нейроподобном элементе DD32 при суммировании, сигнал СВ, равный нулю, определяется как прямое значение первого двоичного разряда  . При выполнении операции вычитания определяется инверсное значение первого двоичного разряда

. При выполнении операции вычитания определяется инверсное значение первого двоичного разряда  . На выходе порогового элемента DD33 определяется перенос Pn из младших разрядов в старшие и заем Zn из старших разрядов в младшие (фиг. 5).

. На выходе порогового элемента DD33 определяется перенос Pn из младших разрядов в старшие и заем Zn из старших разрядов в младшие (фиг. 5).

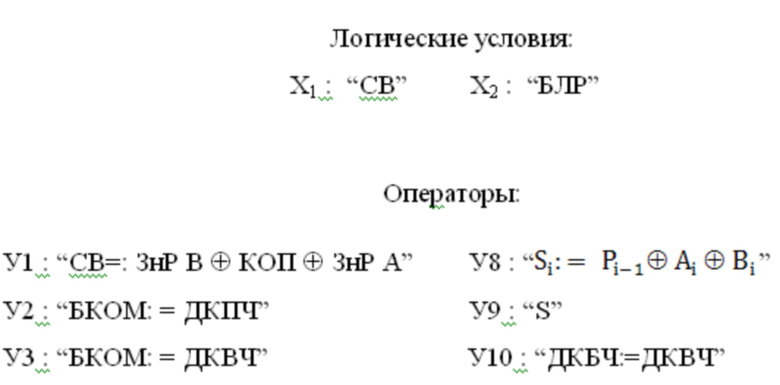

Размеченная ГСА pаботы устройства приведена на фиг. 7, где обозначено:

У4 : “БКОМ: = СВ” У11 : “ДКМЧ:=ДКПЧ”

У5 : “ДКБЧ:=ДКПЧ” У12 : “ ”

”

У6 : “ДКМЧ:=ДКВЧ” У13 : “ ”

”

У7 : “ ” У14 : “R”

” У14 : “R”

Изобретение относится к области вычислительной техники. Технический результат направлен на повышение скорости выполнения операций и повышение надежности. Параллельный сумматор-вычитатель на нейроподобных элементах, содержащий блок ввода чисел, блок компарации и блок параллельных сумматоров-вычитателей, при этом дополнительно введены: блок-регистр первого числа, блок-регистр второго числа и блок-регистр результата, причем первый информационный выход блока ввода чисел, второй информационный выход блока ввода чисел, на которых формируется двоичный код и знаковый разряд второго входного числа соединен со вторым информационным входом блока компарации, первый информационный выход блока компарации, на котором формируется двоичный код и знаковый разряд большего по модулю числа соединен с первым информационным входом блока сумматоров-вычитателей, управляющий вход блока сумматоров-вычитателей, на котором формируется признак операции сигнал суммирования или вычитания, соединен с управляющим выходом блока компарации, второй информационный выход блока компарации, на котором формируется двоичный код меньшего по модулю числа, соединен со вторым информационным входом блока сумматоров-вычитателей. 7 ил.

Параллельный сумматор-вычитатель на нейроподобных элементах, содержащий блок ввода чисел, блок компарации и блок параллельных сумматоров-вычитателей, отличающийся тем, что дополнительно введены: блок-регистр первого числа, блок-регистр второго числа и блок-регистр результата, причем первый информационный выход блока ввода чисел, на котором формируется двоичный код и знаковый разряд первого входного числа соединен с первым информационным входом блока компарации, управляющий вход блока компарации, на котором формируется признак операции сигнал суммирования или вычитания, соединен с управляющим выходом блока ввода чисел, второй информационный выход блока ввода чисел, на котором формируется двоичный код и знаковый разряд второго входного числа соединен со вторым информационным входом блока компарации, первый информационный выход блока компарации, на котором формируется двоичный код и знаковый разряд большего по модулю числа соединен с первым информационным входом блока сумматоров-вычитателей, управляющий вход блока сумматоров-вычитателей, на котором формируется признак операции сигнал суммирования или вычитания соединен с управляющим выходом блока компарации, второй информационный выход блока компарации, на котором формируется двоичный код меньшего по модулю числа, соединен со вторым информационным входом блока сумматоров-вычитателей.

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Устройство поразрядного вычисления логических и арифметических операций | 2020 |

|

RU2739343C1 |

| АДАПТИВНОЕ УПРАВЛЯЮЩЕЕ УСТРОЙСТВО, НЕЙРОПОДОБНЫЙ БАЗОВЫЙ ЭЛЕМЕНТ И СПОСОБ ОРГАНИЗАЦИИ РАБОТЫ ТАКОГО УСТРОЙСТВА | 2011 |

|

RU2475843C1 |

| НЕЙРОПОДОБНЫЙ ЭЛЕМЕНТ | 2020 |

|

RU2744361C1 |

| US 5327522 A, 05.07.1995. | |||

Авторы

Даты

2023-10-24—Публикация

2023-03-10—Подача