Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические вычислители (см., например, фиг.1 в описании изобретения к патенту РФ 2172980, кл. G 06 G 7/25, 2001 г.), которые могут быть использованы для реализации шести простых симметричных булевых функций, зависящих от шести аргументов - входных двоичных сигналов x1,..., x6∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических вычислителей, относится низкое быстродействие, поскольку для реализации упомянутых функций потребуется десять тактов вычислений.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический вычислитель (см. рис.2 в статье Савченко Ю.Г., Хмелевая А.В. О методах последовательной реализации симметричных булевых функций// Автоматика и вычислительная техника. 1974. №3. С.24-29), который содержит регистр, n-1 элементов И, n-1 элементов ИЛИ и при n=6 реализует шесть простых симметричных булевых функций, зависящих от шести аргументов - входных двоичных сигналов х1,..., х6 ∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится низкое быстродействие, поскольку для реализации упомянутых функций потребуется шесть тактов вычислений, причем минимальная длительность каждого такта определяется суммой ΔtР+5ΔtЭ, где ΔtP и ΔtЭ есть длительности задержек, вносимых соответственно регистром и каскадом параллельно срабатывающих элементов ИЛИ, И.

Техническим результатом изобретения является повышение быстродействия.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом вычислителе, содержащем пять элементов ИЛИ, пять элементов И и регистр, первый и второй входы r-го ( ) элемента ИЛИ соединены соответственно с первым и вторым входами r-го элемента И, особенность заключается в том, что в него введены шесть замыкающих и шесть размыкающих ключей, выход и вход i-го (

) элемента ИЛИ соединены соответственно с первым и вторым входами r-го элемента И, особенность заключается в том, что в него введены шесть замыкающих и шесть размыкающих ключей, выход и вход i-го ( ) размыкающего ключа соединены соответственно с выходом i-го замыкающего ключа и объединенными i-ым выходом регистра, i-ым выходом логического вычислителя, подсоединенного первым, вторым настроечными и i-ым информационным входами соответственно к управляющему входу всех ключей, входу записи регистра и входу i-го замыкающего ключа, выходы первого, второго и третьего замыкающих ключей соединены соответственно с первым, вторым входами первого и первым входом второго элементов ИЛИ, подключенных выходами соответственно к первому входу регистра и второму входу четвертого элемента ИЛИ, первый вход и выход которого соединены соответственно с выходом первого элемента И и вторым входом регистра, а выходы шестого, пятого и четвертого замыкающих ключей соединены соответственно с вторым, первым входами третьего и вторым входом второго элементов И, подключенных выходами соответственно к шестому входу регистра и первому входу пятого элемента И, второй вход и выход которого соединены соответственно с выходом третьего элемента ИЛИ и пятым входом регистра, подключенного третьим и четвертым входами соответственно к выходу четвертого элемента И и выходу пятого элемента ИЛИ.

) размыкающего ключа соединены соответственно с выходом i-го замыкающего ключа и объединенными i-ым выходом регистра, i-ым выходом логического вычислителя, подсоединенного первым, вторым настроечными и i-ым информационным входами соответственно к управляющему входу всех ключей, входу записи регистра и входу i-го замыкающего ключа, выходы первого, второго и третьего замыкающих ключей соединены соответственно с первым, вторым входами первого и первым входом второго элементов ИЛИ, подключенных выходами соответственно к первому входу регистра и второму входу четвертого элемента ИЛИ, первый вход и выход которого соединены соответственно с выходом первого элемента И и вторым входом регистра, а выходы шестого, пятого и четвертого замыкающих ключей соединены соответственно с вторым, первым входами третьего и вторым входом второго элементов И, подключенных выходами соответственно к шестому входу регистра и первому входу пятого элемента И, второй вход и выход которого соединены соответственно с выходом третьего элемента ИЛИ и пятым входом регистра, подключенного третьим и четвертым входами соответственно к выходу четвертого элемента И и выходу пятого элемента ИЛИ.

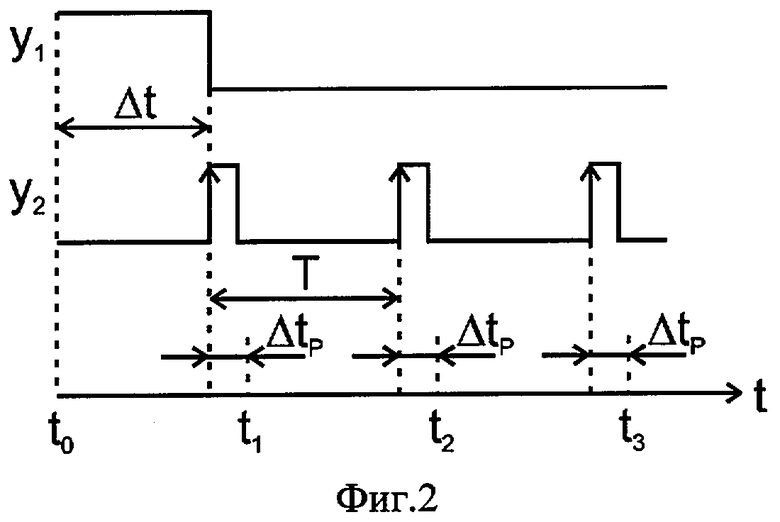

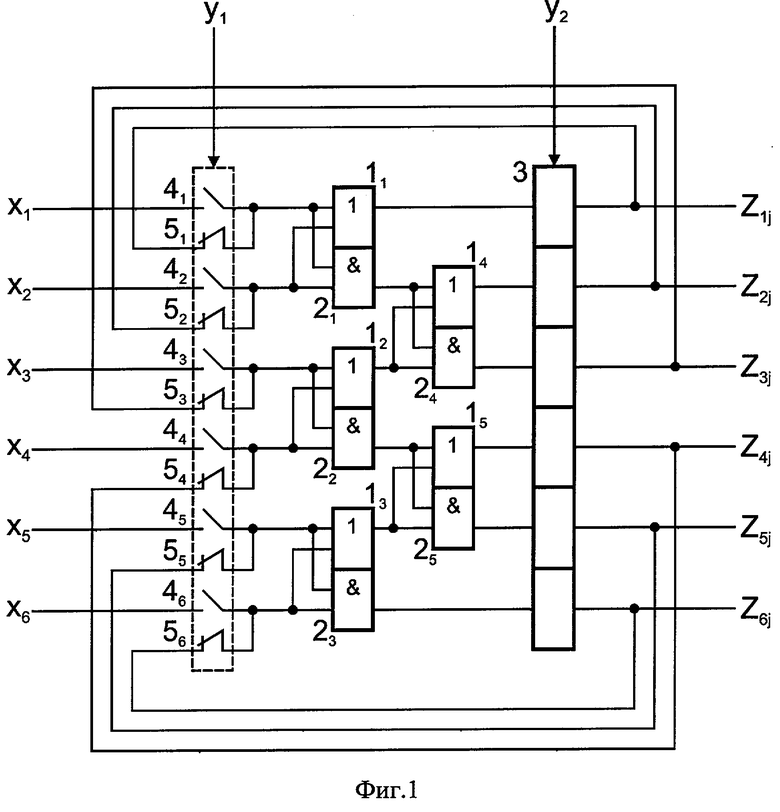

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого логического вычислителя и временные диаграммы сигналов настройки.

Логический вычислитель содержит элементы ИЛИ 11,..., 15, элементы И 21,..., 25, регистр 3, замыкающие ключи 41,..., 46, размыкающие ключи 51,..., 56, причем первый и второй входы элемента 1r ( ) соединены соответственно с первым и вторым входами элемента 2r, выход и вход ключа 5i (

) соединены соответственно с первым и вторым входами элемента 2r, выход и вход ключа 5i ( ) соединены соответственно с выходом ключа 4i и объединенными i-ым выходом регистра 3, i-ым выходом логического вычислителя, подсоединенного первым, вторым настроечными и i-ым информационным входами соответственно к управляющему входу всех ключей, входу записи регистра 3 и входу ключа 4i, выходы ключей 41, 42 и 43 соединены соответственно с первым, вторым входами элемента 11 и первым входом элемента 12, подключенных выходами соответственно к первому входу регистра 3 и второму входу элемента 14, первый вход и выход которого соединены соответственно с выходом элемента 21 и вторым входом регистра 3, а выходы ключей 46, 45 и 44 соединены соответственно с вторым, первым входами элемента 23 и вторым входом элемента 22, подключенных выходами соответственно к шестому входу регистра 3 и первому входу элемента 25, второй вход и выход которого соединены соответственно с выходом элемента 13 и пятым входом регистра 3, подключенного третьим и четвертым входами соответственно к выходу элемента 24 и выходу элемента 15.

) соединены соответственно с выходом ключа 4i и объединенными i-ым выходом регистра 3, i-ым выходом логического вычислителя, подсоединенного первым, вторым настроечными и i-ым информационным входами соответственно к управляющему входу всех ключей, входу записи регистра 3 и входу ключа 4i, выходы ключей 41, 42 и 43 соединены соответственно с первым, вторым входами элемента 11 и первым входом элемента 12, подключенных выходами соответственно к первому входу регистра 3 и второму входу элемента 14, первый вход и выход которого соединены соответственно с выходом элемента 21 и вторым входом регистра 3, а выходы ключей 46, 45 и 44 соединены соответственно с вторым, первым входами элемента 23 и вторым входом элемента 22, подключенных выходами соответственно к шестому входу регистра 3 и первому входу элемента 25, второй вход и выход которого соединены соответственно с выходом элемента 13 и пятым входом регистра 3, подключенного третьим и четвертым входами соответственно к выходу элемента 24 и выходу элемента 15.

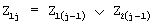

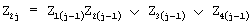

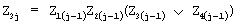

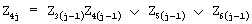

Работа предлагаемого логического вычислителя осуществляется следующим образом. На его первый,...,шестой информационные и первый, второй настроечные входы подаются соответственно двоичные сигналы х1,..., х6∈{0,1} и y1, у2∈{0,1} (фиг.2). Загрузка данных в регистр 3 происходит по положительному перепаду (из «0» в «1») сигнала на входе записи, поэтому указанный регистр может быть аппаратно реализован с помощью, например, микросхемы К531ИР18. Если на управляющем входе ключей 4i, 5i ( ) присутствует логическая «1» либо логический «0», то ключ 4i соответственно замкнут либо разомкнут, а ключ 5i соответственно разомкнут либо замкнут. Тогда сигналы на выходах вычислителя (фиг.1) будут определяться рекуррентными выражениями

) присутствует логическая «1» либо логический «0», то ключ 4i соответственно замкнут либо разомкнут, а ключ 5i соответственно разомкнут либо замкнут. Тогда сигналы на выходах вычислителя (фиг.1) будут определяться рекуррентными выражениями  ,

,  ,

,

,

,  ,

,  , где символами ∨ и · обозначены соответственно операции ИЛИ и И;

, где символами ∨ и · обозначены соответственно операции ИЛИ и И;  есть номер момента времени tj (фиг.2); Zi0=xi.

есть номер момента времени tj (фиг.2); Zi0=xi.

Длительность Δt высокого уровня сигнала у1 и период T сигнала у2 должны удовлетворять условиям Δt≥2ΔtЭ и T≥ΔtP+2ΔtЭ, где ΔtР и ΔtЭ есть длительности задержек, вносимых соответственно регистром 3 и каскадом параллельно срабатывающих элементов ИЛИ, И. Согласно приведенных рекуррентных выражений получим  , где хk1,..., хki ∈{х1,..., х6} (1≤k1<...<ki≤6); N=C6 i есть количество неповторяющихся конъюнкций xk1...xki, определяемое как число сочетаний из 6 по i. Таким образом, имеем Zi3=τi, где τi есть i-ая (

, где хk1,..., хki ∈{х1,..., х6} (1≤k1<...<ki≤6); N=C6 i есть количество неповторяющихся конъюнкций xk1...xki, определяемое как число сочетаний из 6 по i. Таким образом, имеем Zi3=τi, где τi есть i-ая ( ) простая симметричная булева функция шести аргументов.

) простая симметричная булева функция шести аргументов.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический вычислитель реализует шесть простых симметричных булевых функций, зависящих от шести аргументов - входных двоичных сигналов, и обладает более высоким по сравнению с прототипом быстродействием, так как выполняет только три такта вычислений, причем минимальная длительность каждого такта определяется суммой ΔtР+2ΔtЭ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2016 |

|

RU2630391C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2353967C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2336555C1 |

| АДРЕСНЫЙ ИДЕНТИФИКАТОР | 2002 |

|

RU2204163C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2012 |

|

RU2504826C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2016 |

|

RU2626345C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2006 |

|

RU2324219C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2282234C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2475814C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2262734C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления. Техническим результатом изобретения является повышение быстродействия. Устройство содержит пять элементов ИЛИ, пять элементов И, регистр, шесть замыкающих и шесть размыкающих ключей. 2 ил.

Логический вычислитель, предназначенный для реализации шести простых симметричных булевых функций, зависящих от шести аргументов - входных двоичных сигналов, содержащий пять элементов «ИЛИ», пять элементов «И» и регистр, причем первый и второй входы r-го ( ) элемента «ИЛИ» соединены соответственно с первым и вторым входами r-го элемента «И», отличающийся тем, что в него введены шесть замыкающих и шесть размыкающих ключей, выход и вход i-го (

) элемента «ИЛИ» соединены соответственно с первым и вторым входами r-го элемента «И», отличающийся тем, что в него введены шесть замыкающих и шесть размыкающих ключей, выход и вход i-го ( ) размыкающего ключа соединены соответственно с выходом i-го замыкающего ключа и объединенными i-м выходом регистра, i-м выходом логического вычислителя, подсоединенного первым, вторым настроечными и i-м информационным входами соответственно к управляющему входу всех ключей, входу записи регистра и входу i-го замыкающего ключа, выходы первого, второго и третьего замыкающих ключей соединены соответственно с первым, вторым входами первого и первым входом второго элементов «ИЛИ», подключенных выходами соответственно к первому входу регистра и второму входу четвертого элемента «ИЛИ», первый вход и выход которого соединены соответственно с выходом первого элемента «И» и вторым входом регистра, а выходы шестого, пятого и четвертого замыкающих ключей соединены соответственно с вторым, первым входами третьего и вторым входом второго элементов «И», подключенных выходами соответственно к шестому входу регистра и первому входу пятого элемента «И», второй вход и выход которого соединены соответственно с выходом третьего элемента «ИЛИ» и пятым входом регистра, подключенного третьим и четвертым входами соответственно к выходу четвертого элемента «И» и выходу пятого элемента «ИЛИ».

) размыкающего ключа соединены соответственно с выходом i-го замыкающего ключа и объединенными i-м выходом регистра, i-м выходом логического вычислителя, подсоединенного первым, вторым настроечными и i-м информационным входами соответственно к управляющему входу всех ключей, входу записи регистра и входу i-го замыкающего ключа, выходы первого, второго и третьего замыкающих ключей соединены соответственно с первым, вторым входами первого и первым входом второго элементов «ИЛИ», подключенных выходами соответственно к первому входу регистра и второму входу четвертого элемента «ИЛИ», первый вход и выход которого соединены соответственно с выходом первого элемента «И» и вторым входом регистра, а выходы шестого, пятого и четвертого замыкающих ключей соединены соответственно с вторым, первым входами третьего и вторым входом второго элементов «И», подключенных выходами соответственно к шестому входу регистра и первому входу пятого элемента «И», второй вход и выход которого соединены соответственно с выходом третьего элемента «ИЛИ» и пятым входом регистра, подключенного третьим и четвертым входами соответственно к выходу четвертого элемента «И» и выходу пятого элемента «ИЛИ».

| САВЧЕНКО Ю.Г., ХМЕЛЕВАЯ А.В | |||

| О методах последовательной реализации симметричных булевых функций, в: | |||

| «Автоматика и вычислительная техника», 1974, №3, с.24-29, рис.2 | |||

| РАНГОВЫЙ СЕЛЕКТОР | 2000 |

|

RU2172980C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ | 1992 |

|

RU2047892C1 |

| Устройство для вычисления симметрических булевых функций | 1988 |

|

SU1559337A1 |

| МЕТАЛЛОПОРИСТЫЙ ПРОПИТАННЫЙ КАТОД ДЛЯ МАГНЕТРОНА | 2007 |

|

RU2342732C1 |

Авторы

Даты

2005-09-20—Публикация

2004-04-09—Подача