Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические вычислители (см., например, фиг. 2 в описании изобретения к патенту РФ 2491613, кл. G06F 7/38, 2013 г.), которые реализуют параллельный набор двух простых симметричных булевых функций, зависящих от параллельного набора двух аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических вычислителей, относятся, в частности, ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация параллельного набора шести простых симметричных булевых функций, зависящих от параллельного набора шести аргументов - входных двоичных сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический вычислитель (патент РФ 2260837, кл. G06F 7/38, 2005 г.), который имеет шесть информационных входов, шесть выходов и реализует параллельный набор шести простых симметричных булевых функций, зависящих от параллельного набора шести аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся неоднородность состава и сложность реализации целевых функций, обусловленные соответственно тем, что прототип состоит из элементов пяти типов (регистра, элементов ИЛИ, элементов И, замыкающих и размыкающих ключей) и целевые функции воспроизводятся с помощью настроечных сигналов.

Техническим результатом изобретения является обеспечение однородности состава и упрощение реализации параллельного набора шести простых симметричных булевых функций, зависящих от параллельного набора шести аргументов - входных двоичных сигналов.

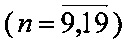

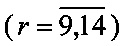

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом вычислителе, содержащем шесть информационных входов, шесть выходов, особенность заключается в том, что в него введены двадцать мажоритарных элементов, выходы j-го  и r-го

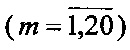

и r-го  мажоритарных элементов соединены соответственно с объединенными вторым входом (j+[j/3]+2)-го, первым входом (j+[j/3]+3)-го мажоритарных элементов и объединенными вторым входом (r+[r/10]+4)-го, первым входом (r+[r/10]+5)-го мажоритарных элементов, первый вход q-го (q∈{1,3,6,10,15}) и второй вход g-го (g∈{2,5,9,14,20}) мажоритарных элементов подключены соответственно к шине единичного и шине нулевого потенциалов, а третьи входы j-го, n-го

мажоритарных элементов соединены соответственно с объединенными вторым входом (j+[j/3]+2)-го, первым входом (j+[j/3]+3)-го мажоритарных элементов и объединенными вторым входом (r+[r/10]+4)-го, первым входом (r+[r/10]+5)-го мажоритарных элементов, первый вход q-го (q∈{1,3,6,10,15}) и второй вход g-го (g∈{2,5,9,14,20}) мажоритарных элементов подключены соответственно к шине единичного и шине нулевого потенциалов, а третьи входы j-го, n-го  и двадцатого мажоритарных элементов соединены соответственно с ([j/3]+2)-ым, ([n/5]+3)-им и шестым информационными входами логического вычислителя, i-й

и двадцатого мажоритарных элементов соединены соответственно с ([j/3]+2)-ым, ([n/5]+3)-им и шестым информационными входами логического вычислителя, i-й  выход и первый информационный вход которого подключены соответственно к выходу (i+14)-го мажоритарного элемента и объединенным второму входу первого, первому входу второго мажоритарных элементов, при этом [] есть оператор выделения целой части.

выход и первый информационный вход которого подключены соответственно к выходу (i+14)-го мажоритарного элемента и объединенным второму входу первого, первому входу второго мажоритарных элементов, при этом [] есть оператор выделения целой части.

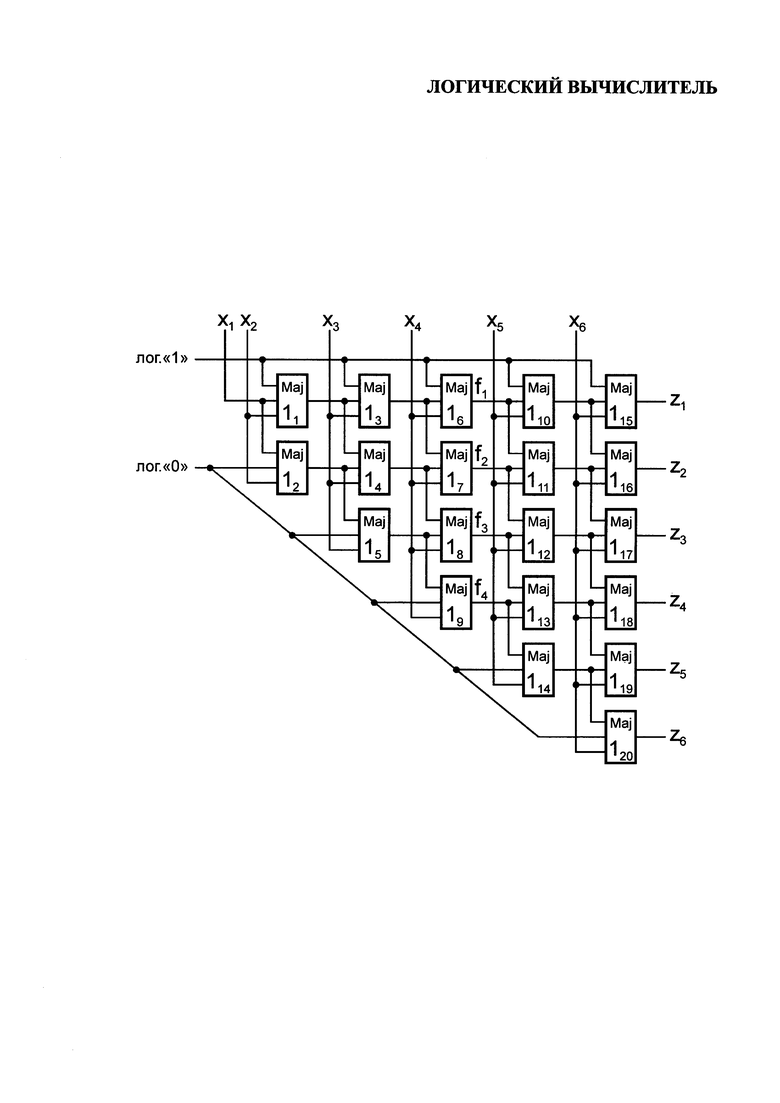

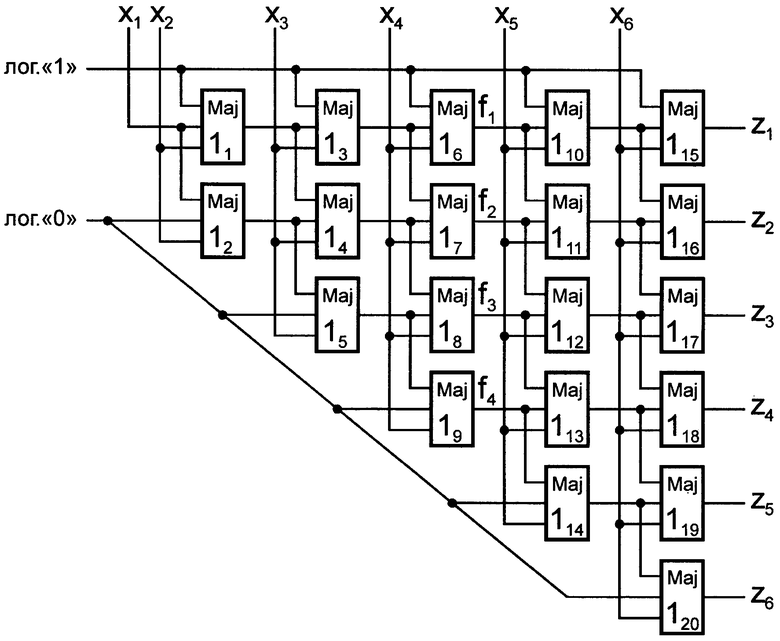

На чертеже представлена схема предлагаемого логического вычислителя. Логический вычислитель содержит мажоритарные элементы l1, …, l20, причем выходы элементов 1j  и 1r

и 1r  соединены соответственно с объединенными вторым входом элемента 1j+[j/3]+2, первым входом элемента 1j+[j/3]+3 и объединенными вторым входом элемента 1r+[r/10]+4, первым входом элемента lr+[r/10]+5, первый вход элемента 1q (q∈{1,3,6,10,15}) и второй вход элемента lg (g∈{2,5,9,14,20}) подключены соответственно к шине единичного и шине нулевого потенциалов, а третьи входы элементов 1j, 1n

соединены соответственно с объединенными вторым входом элемента 1j+[j/3]+2, первым входом элемента 1j+[j/3]+3 и объединенными вторым входом элемента 1r+[r/10]+4, первым входом элемента lr+[r/10]+5, первый вход элемента 1q (q∈{1,3,6,10,15}) и второй вход элемента lg (g∈{2,5,9,14,20}) подключены соответственно к шине единичного и шине нулевого потенциалов, а третьи входы элементов 1j, 1n  и l20 соединены соответственно с ([j/3]+2)-ым, ([j/5]+3)-им и шестым информационными входами логического вычислителя, i-й

и l20 соединены соответственно с ([j/3]+2)-ым, ([j/5]+3)-им и шестым информационными входами логического вычислителя, i-й  выход и первый информационный вход которого подключены соответственно к выходу элемента 1i+14 и объединенным второму входу элемента 11, первому входу элемента 12, при этом [] есть оператор выделения целой части.

выход и первый информационный вход которого подключены соответственно к выходу элемента 1i+14 и объединенным второму входу элемента 11, первому входу элемента 12, при этом [] есть оператор выделения целой части.

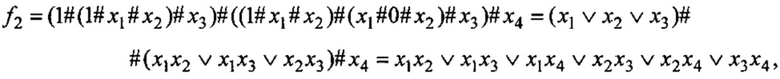

Работа предлагаемого логического вычислителя осуществляется следующим образом. На его первый, …, шестой информационные входы подаются соответственно двоичные сигналы x1, …, x6∈{0,1}. На выходе мажоритарного элемента 1m  имеем am1#am2#am3=am1am2∨am1am3∨am2am3, где am1, am2, am3 и #, ∨, ⋅ есть соответственно сигналы на его первом, втором, третьем входах и символы операций Maj, ИЛИ, И. Тогда сигналы

имеем am1#am2#am3=am1am2∨am1am3∨am2am3, где am1, am2, am3 и #, ∨, ⋅ есть соответственно сигналы на его первом, втором, третьем входах и символы операций Maj, ИЛИ, И. Тогда сигналы  (см. чертеж) будут определяться выражениями

(см. чертеж) будут определяться выражениями

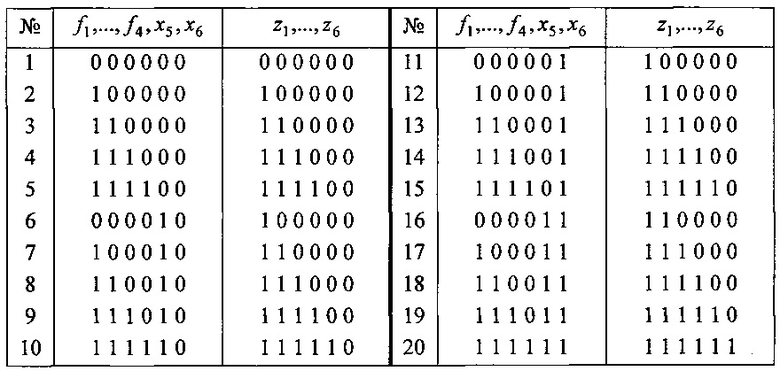

В представленной ниже таблице приведены значения сигналов на выходах предлагаемого вычислителя при всех возможных наборах значений сигналов  , x5, x6.

, x5, x6.

Таким образом, на i-ом  выходе предлагаемого вычислителя получим

выходе предлагаемого вычислителя получим  где xk1, …, xki∈{x1, …, x6}(1≤k1< … <ki≤6);

где xk1, …, xki∈{x1, …, x6}(1≤k1< … <ki≤6);  есть количество неповторяющихся конъюнкций xk1…xki, определяемое как число сочетаний из 6 по i. Следовательно, zi=τi, где τi есть i-я простая симметричная булева функция шести аргументов (см. стр. 126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974 г.).

есть количество неповторяющихся конъюнкций xk1…xki, определяемое как число сочетаний из 6 по i. Следовательно, zi=τi, где τi есть i-я простая симметричная булева функция шести аргументов (см. стр. 126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974 г.).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический вычислитель имеет однородный состав и без использования настроечных сигналов реализует параллельный набор шести простых симметричных булевых функций, зависящих от параллельного набора шести аргументов - входных двоичных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2014 |

|

RU2549158C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2016 |

|

RU2629452C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2014 |

|

RU2559708C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2015 |

|

RU2585725C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2020 |

|

RU2757830C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2019 |

|

RU2718209C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2021 |

|

RU2776920C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2015 |

|

RU2580799C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2017 |

|

RU2676888C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2015 |

|

RU2595958C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др. Технический результат заключается в обеспечении однородности состава и упрощении реализации параллельного набора шести простых симметричных булевых функций, зависящих от параллельного набора шести аргументов - входных двоичных сигналов. Логический вычислитель содержит двадцать мажоритарных элементов (11, …, 120), за счет которых обеспечиваются однородность состава и реализация целевых функций без использования настроечных сигналов. 1 ил., 1 табл.

Логический вычислитель, предназначенный для реализации параллельного набора шести простых симметричных булевых функций, зависящих от параллельного набора шести аргументов - входных двоичных сигналов, содержащий шесть информационных входов, шесть выходов и отличающийся тем, что в него введены двадцать мажоритарных элементов, причем выходы j-го  и r-го

и r-го  мажоритарных элементов соединены соответственно с объединенными вторым входом (j+[j/3]+2)-го, первым входом (j+[j/3]+3)-го мажоритарных элементов и объединенными вторым входом (r+[r/10]+4)-го, первым входом (r+[r/10]+5)-го мажоритарных элементов, первый вход q-го (q∈{1,3,6,10,15}) и второй вход g-го (g∈{2,5,9,14,20}) мажоритарных элементов подключены соответственно к шине единичного и шине нулевого потенциалов, а третьи входы j-го, n-го

мажоритарных элементов соединены соответственно с объединенными вторым входом (j+[j/3]+2)-го, первым входом (j+[j/3]+3)-го мажоритарных элементов и объединенными вторым входом (r+[r/10]+4)-го, первым входом (r+[r/10]+5)-го мажоритарных элементов, первый вход q-го (q∈{1,3,6,10,15}) и второй вход g-го (g∈{2,5,9,14,20}) мажоритарных элементов подключены соответственно к шине единичного и шине нулевого потенциалов, а третьи входы j-го, n-го  и двадцатого мажоритарных элементов соединены соответственно с ([j/3]+2)-ым, ([n/5]+3)-им и шестым информационными входами логического вычислителя, i-й

и двадцатого мажоритарных элементов соединены соответственно с ([j/3]+2)-ым, ([n/5]+3)-им и шестым информационными входами логического вычислителя, i-й  выход и первый информационный вход которого подключены соответственно к выходу (i+14)-го мажоритарного элемента и объединенным второму входу первого, первому входу второго мажоритарных элементов, при этом [] есть оператор выделения целой части.

выход и первый информационный вход которого подключены соответственно к выходу (i+14)-го мажоритарного элемента и объединенным второму входу первого, первому входу второго мажоритарных элементов, при этом [] есть оператор выделения целой части.

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2260837C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ | 1992 |

|

RU2047894C1 |

| Многофункциональный логический модуль | 1987 |

|

SU1430951A1 |

| Прибор для отмеривания сыпучих материалов в определенных весовых количествах при помощи мерника, заключенного между двумя связанными друг с другом и открывающимися поочередно задвижками | 1929 |

|

SU16904A1 |

| Огнетушитель | 0 |

|

SU91A1 |

Авторы

Даты

2017-09-07—Публикация

2016-03-09—Подача