Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические вычислители (см., например, патент РФ 2248035, кл. G06F 7/38, 2005 г.), которые реализуют любую из n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических вычислителей, относится зависимость длительности такта вычисления от количества входных двоичных сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический вычислитель (патент РФ 2336555, кл. G06F 7/57, 2008 г.), который содержит n D-триггеров, n элементов ИЛИ-НЕ, n замыкающих и n размыкающих ключей и реализует любую из n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, при отсутствии зависимости между длительностью такта вычисления и количеством последних.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся большие аппаратурные затраты, обусловленные тем, что прототип дополнительно содержит n+1 резисторов.

Техническим результатом изобретения является уменьшение аппаратурных затрат при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом вычислителе, содержащем n замыкающих, n размыкающих ключей, n D-триггеров и n элементов ИЛИ-НЕ, вторые входы которых объединены и образуют первый управляющий вход логического вычислителя, подключенного вторым управляющим и i-м

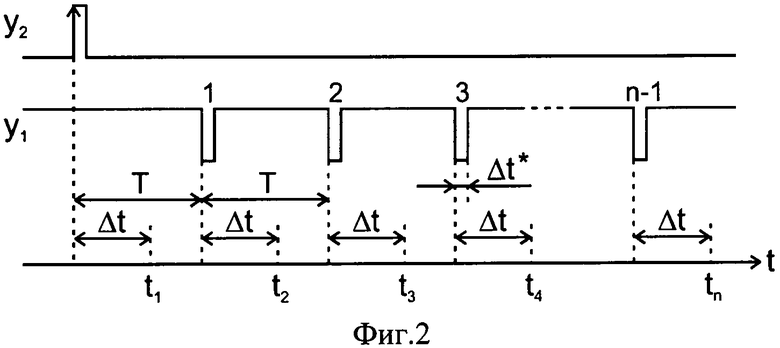

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого логического вычислителя и временные диаграммы управляющих сигналов.

Логический вычислитель содержит D-триггеры 11, …, 1n, элементы ИЛИ-НЕ 21, …, 2n, размыкающие ключи 31, …, 3n и замыкающие ключи 41, …, 4n, причем выход предыдущего размыкающего ключа соединен с входом последующего размыкающего ключа, выходы ключей 3i и 4i

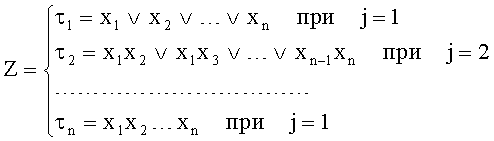

Работа предлагаемого логического вычислителя осуществляется следующим образом. На его первый, …, n-й информационные и первый, второй управляющие входы подаются соответственно двоичные сигналы х1, …, хn∈{0,1} и импульсные сигналы y1, y2∈{0,l} (фиг.2), причем период Т и длительность Δt∗ импульса сигнала y1 должны удовлетворять условиям Т>Δt и Δt∗<ΔtИЛИ-НЕ+ΔtTp, где Δt=ΔtИЛИ-НЕ+ΔtTp+ΔtКл, а ΔtИЛИ-НЕ, ΔtTp и ΔtКл есть длительности задержек, вносимых элементом ИЛИ-НЕ, D-триггером и ключом. Ключ 4i (

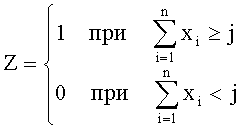

С учетом данных, приведенных в таблице, можно записать

где j есть номер момента времени tj (фиг.2). Таким образом, на выходе предлагаемого логического вычислителя получим

Здесь τ1, …, τn есть простые симметричные булевы функции (см. стр.126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974). При этом длительность такта вычисления не превышает Δt.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический вычислитель реализует любую из n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, при отсутствии зависимости между длительностью такта вычисления и количеством последних и имеет меньший по сравнению с прототипом аппаратурный состав. Дополнительным достоинством предлагаемого логического вычислителя является отсутствие имеющейся в прототипе функциональной связи с шиной единичного потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2336555C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2006 |

|

RU2324219C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2353967C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2006 |

|

RU2300138C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2282234C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2276399C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2335797C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2294009C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2260837C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2002 |

|

RU2227931C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой вычислительной техники как средство преобразования кодов. Техническим результатом является уменьшение аппаратурных затрат. Устройство содержит n D-триггеров, n элементов ИЛИ-НЕ, n размыкающих ключей и n замыкающих ключей. 2 ил., 1 табл.

Логический вычислитель, предназначенный для реализации любой из n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, содержащий n замыкающих, n размыкающих ключей, n D-триггеров и n элементов ИЛИ-НЕ, вторые входы которых объединены и образуют первый управляющий вход логического вычислителя, подключенного вторым управляющим и i-м

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2336555C1 |

| СИММЕТРИЧНЫЙ МОДУЛЬ | 2003 |

|

RU2248035C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2011 |

|

RU2445679C1 |

| US 2004236545 A1, 25.11.2004 | |||

| US 2008021942 A1, 24.01.2008. | |||

Авторы

Даты

2014-01-20—Публикация

2012-07-03—Подача